Professional Documents

Culture Documents

Set Instrucciones PDF

Uploaded by

datazo info0 ratings0% found this document useful (0 votes)

36 views3 pagesOriginal Title

Set instrucciones.pdf

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

36 views3 pagesSet Instrucciones PDF

Uploaded by

datazo infoCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 3

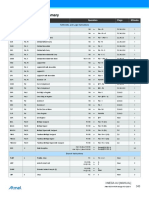

ATmega48A/PA/88A/PA/168A/PA/328/P

37. Instruction Set Summary

Mnemonics Operands Description Operation Flags #Clocks

ARITHMETIC AND LOGIC INSTRUCTIONS

ADD Rd, Rr Add two Registers Rd Rd + Rr Z,C,N,V,H 1

ADC Rd, Rr Add with Carry two Registers Rd Rd + Rr + C Z,C,N,V,H 1

ADIW Rdl,K Add Immediate to Word Rdh:Rdl Rdh:Rdl + K Z,C,N,V,S 2

SUB Rd, Rr Subtract two Registers Rd Rd - Rr Z,C,N,V,H 1

SUBI Rd, K Subtract Constant from Register Rd Rd - K Z,C,N,V,H 1

SBC Rd, Rr Subtract with Carry two Registers Rd Rd - Rr - C Z,C,N,V,H 1

SBCI Rd, K Subtract with Carry Constant from Reg. Rd Rd - K - C Z,C,N,V,H 1

SBIW Rdl,K Subtract Immediate from Word Rdh:Rdl Rdh:Rdl - K Z,C,N,V,S 2

AND Rd, Rr Logical AND Registers Rd Rd Rr Z,N,V 1

ANDI Rd, K Logical AND Register and Constant Rd Rd K Z,N,V 1

OR Rd, Rr Logical OR Registers Rd Rd v Rr Z,N,V 1

ORI Rd, K Logical OR Register and Constant Rd Rd v K Z,N,V 1

EOR Rd, Rr Exclusive OR Registers Rd Rd Rr Z,N,V 1

COM Rd One’s Complement Rd 0xFF Rd Z,C,N,V 1

NEG Rd Two’s Complement Rd 0x00 Rd Z,C,N,V,H 1

SBR Rd,K Set Bit(s) in Register Rd Rd v K Z,N,V 1

CBR Rd,K Clear Bit(s) in Register Rd Rd (0xFF - K) Z,N,V 1

INC Rd Increment Rd Rd + 1 Z,N,V 1

DEC Rd Decrement Rd Rd 1 Z,N,V 1

TST Rd Test for Zero or Minus Rd Rd Rd Z,N,V 1

CLR Rd Clear Register Rd Rd Rd Z,N,V 1

SER Rd Set Register Rd 0xFF None 1

MUL Rd, Rr Multiply Unsigned R1:R0 Rd x Rr Z,C 2

MULS Rd, Rr Multiply Signed R1:R0 Rd x Rr Z,C 2

MULSU Rd, Rr Multiply Signed with Unsigned R1:R0 Rd x Rr Z,C 2

FMUL Rd, Rr Fractional Multiply Unsigned R1:R0 (Rd x Rr) << 1 Z,C 2

FMULS Rd, Rr Fractional Multiply Signed R1:R0 (Rd x Rr) << 1 Z,C 2

FMULSU Rd, Rr Fractional Multiply Signed with Unsigned R1:R0 (Rd x Rr) << 1 Z,C 2

BRANCH INSTRUCTIONS

RJMP k Relative Jump PC PC + k + 1 None 2

IJMP Indirect Jump to (Z) PC Z None 2

JMP(1) k Direct Jump PC k None 3

RCALL k Relative Subroutine Call PC PC + k + 1 None 3

ICALL Indirect Call to (Z) PC Z None 3

CALL(1) k Direct Subroutine Call PC k None 4

RET Subroutine Return PC STACK None 4

RETI Interrupt Return PC STACK I 4

CPSE Rd,Rr Compare, Skip if Equal if (Rd = Rr) PC PC + 2 or 3 None 1/2/3

CP Rd,Rr Compare Rd Rr Z, N,V,C,H 1

CPC Rd,Rr Compare with Carry Rd Rr C Z, N,V,C,H 1

CPI Rd,K Compare Register with Immediate Rd K Z, N,V,C,H 1

SBRC Rr, b Skip if Bit in Register Cleared if (Rr(b)=0) PC PC + 2 or 3 None 1/2/3

SBRS Rr, b Skip if Bit in Register is Set if (Rr(b)=1) PC PC + 2 or 3 None 1/2/3

SBIC P, b Skip if Bit in I/O Register Cleared if (P(b)=0) PC PC + 2 or 3 None 1/2/3

SBIS P, b Skip if Bit in I/O Register is Set if (P(b)=1) PC PC + 2 or 3 None 1/2/3

BRBS s, k Branch if Status Flag Set if (SREG(s) = 1) then PCPC+k + 1 None 1/2

BRBC s, k Branch if Status Flag Cleared if (SREG(s) = 0) then PCPC+k + 1 None 1/2

BREQ k Branch if Equal if (Z = 1) then PC PC + k + 1 None 1/2

BRNE k Branch if Not Equal if (Z = 0) then PC PC + k + 1 None 1/2

BRCS k Branch if Carry Set if (C = 1) then PC PC + k + 1 None 1/2

BRCC k Branch if Carry Cleared if (C = 0) then PC PC + k + 1 None 1/2

BRSH k Branch if Same or Higher if (C = 0) then PC PC + k + 1 None 1/2

BRLO k Branch if Lower if (C = 1) then PC PC + k + 1 None 1/2

BRMI k Branch if Minus if (N = 1) then PC PC + k + 1 None 1/2

BRPL k Branch if Plus if (N = 0) then PC PC + k + 1 None 1/2

BRGE k Branch if Greater or Equal, Signed if (N V= 0) then PC PC + k + 1 None 1/2

BRLT k Branch if Less Than Zero, Signed if (N V= 1) then PC PC + k + 1 None 1/2

BRHS k Branch if Half Carry Flag Set if (H = 1) then PC PC + k + 1 None 1/2

BRHC k Branch if Half Carry Flag Cleared if (H = 0) then PC PC + k + 1 None 1/2

BRTS k Branch if T Flag Set if (T = 1) then PC PC + k + 1 None 1/2

BRTC k Branch if T Flag Cleared if (T = 0) then PC PC + k + 1 None 1/2

BRVS k Branch if Overflow Flag is Set if (V = 1) then PC PC + k + 1 None 1/2

BRVC k Branch if Overflow Flag is Cleared if (V = 0) then PC PC + k + 1 None 1/2

BRIE k Branch if Interrupt Enabled if ( I = 1) then PC PC + k + 1 None 1/2

BRID k Branch if Interrupt Disabled if ( I = 0) then PC PC + k + 1 None 1/2

2018 Microchip Technology Inc. Data Sheet Complete DS40002061A-page 625

ATmega48A/PA/88A/PA/168A/PA/328/P

Mnemonics Operands Description Operation Flags #Clocks

BIT AND BIT-TEST INSTRUCTIONS

SBI P,b Set Bit in I/O Register I/O(P,b) 1 None 2

CBI P,b Clear Bit in I/O Register I/O(P,b) 0 None 2

LSL Rd Logical Shift Left Rd(n+1) Rd(n), Rd(0) 0 Z,C,N,V 1

LSR Rd Logical Shift Right Rd(n) Rd(n+1), Rd(7) 0 Z,C,N,V 1

ROL Rd Rotate Left Through Carry Rd(0)C,Rd(n+1) Rd(n),CRd(7) Z,C,N,V 1

ROR Rd Rotate Right Through Carry Rd(7)C,Rd(n) Rd(n+1),CRd(0) Z,C,N,V 1

ASR Rd Arithmetic Shift Right Rd(n) Rd(n+1), n=0...6 Z,C,N,V 1

SWAP Rd Swap Nibbles Rd(3...0)Rd(7...4),Rd(7...4)Rd(3...0) None 1

BSET s Flag Set SREG(s) 1 SREG(s) 1

BCLR s Flag Clear SREG(s) 0 SREG(s) 1

BST Rr, b Bit Store from Register to T T Rr(b) T 1

BLD Rd, b Bit load from T to Register Rd(b) T None 1

SEC Set Carry C1 C 1

CLC Clear Carry C0 C 1

SEN Set Negative Flag N1 N 1

CLN Clear Negative Flag N0 N 1

SEZ Set Zero Flag Z1 Z 1

CLZ Clear Zero Flag Z0 Z 1

SEI Global Interrupt Enable I1 I 1

CLI Global Interrupt Disable I 0 I 1

SES Set Signed Test Flag S1 S 1

CLS Clear Signed Test Flag S0 S 1

SEV Set Twos Complement Overflow. V1 V 1

CLV Clear Twos Complement Overflow V0 V 1

SET Set T in SREG T1 T 1

CLT Clear T in SREG T0 T 1

SEH Set Half Carry Flag in SREG H1 H 1

CLH Clear Half Carry Flag in SREG H0 H 1

DATA TRANSFER INSTRUCTIONS

MOV Rd, Rr Move Between Registers Rd Rr None 1

MOVW Rd, Rr Copy Register Word Rd+1:Rd Rr+1:Rr None 1

LDI Rd, K Load Immediate Rd K None 1

LD Rd, X Load Indirect Rd (X) None 2

LD Rd, X+ Load Indirect and Post-Inc. Rd (X), X X + 1 None 2

LD Rd, - X Load Indirect and Pre-Dec. X X - 1, Rd (X) None 2

LD Rd, Y Load Indirect Rd (Y) None 2

LD Rd, Y+ Load Indirect and Post-Inc. Rd (Y), Y Y + 1 None 2

LD Rd, - Y Load Indirect and Pre-Dec. Y Y - 1, Rd (Y) None 2

LDD Rd,Y+q Load Indirect with Displacement Rd (Y + q) None 2

LD Rd, Z Load Indirect Rd (Z) None 2

LD Rd, Z+ Load Indirect and Post-Inc. Rd (Z), Z Z+1 None 2

LD Rd, -Z Load Indirect and Pre-Dec. Z Z - 1, Rd (Z) None 2

LDD Rd, Z+q Load Indirect with Displacement Rd (Z + q) None 2

LDS Rd, k Load Direct from SRAM Rd (k) None 2

ST X, Rr Store Indirect (X) Rr None 2

ST X+, Rr Store Indirect and Post-Inc. (X) Rr, X X + 1 None 2

ST - X, Rr Store Indirect and Pre-Dec. X X - 1, (X) Rr None 2

ST Y, Rr Store Indirect (Y) Rr None 2

ST Y+, Rr Store Indirect and Post-Inc. (Y) Rr, Y Y + 1 None 2

ST - Y, Rr Store Indirect and Pre-Dec. Y Y - 1, (Y) Rr None 2

STD Y+q,Rr Store Indirect with Displacement (Y + q) Rr None 2

ST Z, Rr Store Indirect (Z) Rr None 2

ST Z+, Rr Store Indirect and Post-Inc. (Z) Rr, Z Z + 1 None 2

ST -Z, Rr Store Indirect and Pre-Dec. Z Z - 1, (Z) Rr None 2

STD Z+q,Rr Store Indirect with Displacement (Z + q) Rr None 2

STS k, Rr Store Direct to SRAM (k) Rr None 2

LPM Load Program Memory R0 (Z) None 3

LPM Rd, Z Load Program Memory Rd (Z) None 3

LPM Rd, Z+ Load Program Memory and Post-Inc Rd (Z), Z Z+1 None 3

SPM Store Program Memory (Z) R1:R0 None -

IN Rd, P In Port Rd P None 1

OUT P, Rr Out Port P Rr None 1

PUSH Rr Push Register on Stack STACK Rr None 2

POP Rd Pop Register from Stack Rd STACK None 2

MCU CONTROL INSTRUCTIONS

NOP No Operation None 1

SLEEP Sleep (see specific descr. for Sleep function) None 1

2018 Microchip Technology Inc. Data Sheet Complete DS40002061A-page 626

ATmega48A/PA/88A/PA/168A/PA/328/P

Mnemonics Operands Description Operation Flags #Clocks

WDR Watchdog Reset (see specific descr. for WDR/timer) None 1

BREAK Break For On-chip Debug Only None N/A

Note: 1. These instructions are only available in ATmega168PA and ATmega328P.

2018 Microchip Technology Inc. Data Sheet Complete DS40002061A-page 627

You might also like

- Experiment No.: 3: PC With Atmel StudioDocument11 pagesExperiment No.: 3: PC With Atmel StudioDhrumil ManiyarNo ratings yet

- Manual Cumins OnanDocument170 pagesManual Cumins OnanFelipe Uzabal100% (1)

- SVP-43763-DWG-ELE-RSAB-008 - GA Capacitor Bank B - R02Document12 pagesSVP-43763-DWG-ELE-RSAB-008 - GA Capacitor Bank B - R02septa ibnuNo ratings yet

- Instruction Set Summary: Mnemonics Operands Description Operation Flags #ClocksDocument3 pagesInstruction Set Summary: Mnemonics Operands Description Operation Flags #ClocksWalter Tintaya QuispeNo ratings yet

- ATmega328P - Instruction Set SummaryDocument4 pagesATmega328P - Instruction Set SummaryE&GNo ratings yet

- Atmega32 Instruction Set SummaryDocument3 pagesAtmega32 Instruction Set SummaryNumo BamiNo ratings yet

- AVR Instructions Set SummaryDocument5 pagesAVR Instructions Set SummaryChicowolfNo ratings yet

- AtmelDocument4 pagesAtmelBaba YagaNo ratings yet

- Instruction Set Summary for ATmega328/P MicrocontrollerDocument4 pagesInstruction Set Summary for ATmega328/P MicrocontrollerLeonardo AlvesNo ratings yet

- Ebook - Atmel Avr AssemblerDocument20 pagesEbook - Atmel Avr AssemblerTim OnnixNo ratings yet

- Atmel 0856 Avr Instruction Set ManualDocument9 pagesAtmel 0856 Avr Instruction Set ManualGabriel Alejandro Francisco Gallardo TineoNo ratings yet

- Cortex M4 Instruction Set OverviewDocument2 pagesCortex M4 Instruction Set OverviewQuique MoralesNo ratings yet

- Commands in AVR-assembler LanguageDocument1 pageCommands in AVR-assembler LanguageFrutzNo ratings yet

- Hoja Examen AVRDocument3 pagesHoja Examen AVRIceyNo ratings yet

- Chapter 4 Arithmetic and Logic ARMDocument31 pagesChapter 4 Arithmetic and Logic ARMzakariaNo ratings yet

- Kumpulan Instruksi Atmega 8535Document2 pagesKumpulan Instruksi Atmega 8535sword of excaliburNo ratings yet

- Instr Set PDFDocument150 pagesInstr Set PDFvannybowoooNo ratings yet

- Reference SheetDocument3 pagesReference Sheetandro baletiNo ratings yet

- Ddi0439b Errata 01Document5 pagesDdi0439b Errata 01Ahmed TriguiNo ratings yet

- AVR Instruction Set SummaryDocument4 pagesAVR Instruction Set SummarySinan PravadaliogluNo ratings yet

- Basic Laws - Delta-Wye and Source TransformationDocument24 pagesBasic Laws - Delta-Wye and Source TransformationSTACEYLEEN CYENTHIA LADIUN BK22110177No ratings yet

- COMPARE Signed and Unsigned Comparison InstructionsDocument3 pagesCOMPARE Signed and Unsigned Comparison InstructionsEmre CakmakyurduNo ratings yet

- ATmega16 ATmega32Document9 pagesATmega16 ATmega32binitdubeyNo ratings yet

- AVR Instructions 1Document133 pagesAVR Instructions 1Mlondo Khanyisani EmmanuelNo ratings yet

- ThumbRefV2 BetaDocument1 pageThumbRefV2 BetagregNo ratings yet

- ATtiny13, ATtiny2313, Instruction SetDocument19 pagesATtiny13, ATtiny2313, Instruction SetMihai PaunNo ratings yet

- ARM® and Thumb®-2 Instruction Set Quick Reference CardDocument6 pagesARM® and Thumb®-2 Instruction Set Quick Reference CardpavankrishnatNo ratings yet

- Memory Access Instructions: CME331 Microprocessor Khan Wahid Cheat Sheet (Oct 17, 2014) Page 1 of 2Document2 pagesMemory Access Instructions: CME331 Microprocessor Khan Wahid Cheat Sheet (Oct 17, 2014) Page 1 of 2Emre CakmakyurduNo ratings yet

- Memory Access Instructions: CME331 Microprocessor Khan Wahid Cheat Sheet (Oct 17, 2014) Page 1 of 2Document2 pagesMemory Access Instructions: CME331 Microprocessor Khan Wahid Cheat Sheet (Oct 17, 2014) Page 1 of 2Emre CakmakyurduNo ratings yet

- History and Working Principles of Tunnel DiodesDocument15 pagesHistory and Working Principles of Tunnel DiodesMahy MagdyNo ratings yet

- Instruction SetDocument1 pageInstruction Setmakerlog200No ratings yet

- R L C V I R L C R L C I - T: G 2 S T D 2 SDocument1 pageR L C V I R L C R L C I - T: G 2 S T D 2 SBrijendra SinghNo ratings yet

- Introduction To Arm AssemblyDocument42 pagesIntroduction To Arm AssemblySureshNo ratings yet

- Chapter 6 BJT ACDocument23 pagesChapter 6 BJT ACAsad Ur RehmanNo ratings yet

- Government Engineering College Experiment on AVR Data Transfer and Branch InstructionsDocument10 pagesGovernment Engineering College Experiment on AVR Data Transfer and Branch InstructionsDhrumil ManiyarNo ratings yet

- Skup Instrukcija ATxmegaDocument4 pagesSkup Instrukcija ATxmegaskvlukaNo ratings yet

- Digital To Analog Converter: Nov. 1, 2005 Fabian Goericke, Keunhan Park, Geoffrey WilliamsDocument39 pagesDigital To Analog Converter: Nov. 1, 2005 Fabian Goericke, Keunhan Park, Geoffrey WilliamsPunit MishraNo ratings yet

- 2 Introduction To Assembly v21Document42 pages2 Introduction To Assembly v21vokhacnam2k1No ratings yet

- 1AVR Juego de Instrucciones ResumidoDocument2 pages1AVR Juego de Instrucciones ResumidoLuis Alfonso Martinez FdezNo ratings yet

- Dac & AdcDocument108 pagesDac & AdcG RAJESHNo ratings yet

- 정리(기말 포함)_230530_154109Document16 pages정리(기말 포함)_230530_154109강기동No ratings yet

- Visio AVR v2Document3 pagesVisio AVR v2mcraeNo ratings yet

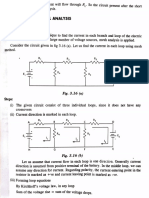

- Mesh and Nodal AnalysisDocument13 pagesMesh and Nodal AnalysisayushiNo ratings yet

- Bipolar Junction Transistor (BJT) : Dr. Ahmad Saudi SamosirDocument16 pagesBipolar Junction Transistor (BJT) : Dr. Ahmad Saudi Samosirmuhammad irfan fadhilaNo ratings yet

- Armv4t Instruction SetDocument2 pagesArmv4t Instruction SetMikiyas TewodroesNo ratings yet

- 3.2 Arm Addressing Mode and Instruction SetDocument32 pages3.2 Arm Addressing Mode and Instruction Set727721eumt082No ratings yet

- Modbus Protocol Mappings P3F30 v30.110: Name AccessDocument45 pagesModbus Protocol Mappings P3F30 v30.110: Name AccessPhan ChinhNo ratings yet

- Amplifier Circuits Analysis - GDLCDocument15 pagesAmplifier Circuits Analysis - GDLCMohammed AL-MaaitahNo ratings yet

- Amplifier Circuits Analysis - GDLCDocument15 pagesAmplifier Circuits Analysis - GDLCMohammed AL-MaaitahNo ratings yet

- Unit 4 Voltage Regulators Using OpampDocument15 pagesUnit 4 Voltage Regulators Using Opamp34 M.V.SakethNo ratings yet

- Star &delta ConnectionDocument4 pagesStar &delta ConnectionRali sp college DumkaNo ratings yet

- Unit-5 Signal Conditioning and Data Acquisition: Akshaya College of Engineering and TechnologyDocument45 pagesUnit-5 Signal Conditioning and Data Acquisition: Akshaya College of Engineering and TechnologyLakshmikanthBalasubramanianNo ratings yet

- ATtiny24/44/84 Instruction Set SummaryDocument2 pagesATtiny24/44/84 Instruction Set SummaryRajsekhar NagNo ratings yet

- 1c55c34f167e0c6b67ff50902d7b7a12107de736Assign%201%20QuesDocument3 pages1c55c34f167e0c6b67ff50902d7b7a12107de736Assign%201%20Quesaayushkumarsinghec22a1561No ratings yet

- Electric Potential and CapacitorsDocument4 pagesElectric Potential and CapacitorsAmir YonanNo ratings yet

- ARM Instruction Set Summary: Data Processing, Loads/Stores, Control TransferDocument2 pagesARM Instruction Set Summary: Data Processing, Loads/Stores, Control TransferADRISTANo ratings yet

- ARM-Inst SummaryDocument2 pagesARM-Inst Summarymkaccc4No ratings yet

- Electronlecture 2Document26 pagesElectronlecture 2Mohammed ShifulNo ratings yet

- 6 AdvancedAssemblyDocument26 pages6 AdvancedAssemblyKillers YTNo ratings yet

- Chapter 10 Compound CircuitsDocument38 pagesChapter 10 Compound Circuitsshubhankar palNo ratings yet

- Washing Machine ManualDocument66 pagesWashing Machine ManualBOSCHCLASSIXX1200No ratings yet

- Cbse Class 12 Physics Notes PDFDocument150 pagesCbse Class 12 Physics Notes PDFKochuzNo ratings yet

- Mechanical SchemeDocument202 pagesMechanical Schemeintresting videoNo ratings yet

- MPPT and Buck ConvertersDocument4 pagesMPPT and Buck ConvertersJuthik BVNo ratings yet

- Adverbial ClausesDocument16 pagesAdverbial ClausesSisma Pratama Arum PutriNo ratings yet

- Metallic BondingDocument6 pagesMetallic Bonding胡佳玲No ratings yet

- A Seminar On A Seminar On: HPLC Detectors HPLC DetectorsDocument36 pagesA Seminar On A Seminar On: HPLC Detectors HPLC DetectorsVivek SagarNo ratings yet

- Quad-Band Panel Dual Polarization Half-Power Beam Width Adjust. Electr. DowntiltDocument2 pagesQuad-Band Panel Dual Polarization Half-Power Beam Width Adjust. Electr. DowntiltAnnBliss50% (2)

- Proyect: E003835 - Gavião Branco Client:: Latam - HoustonDocument34 pagesProyect: E003835 - Gavião Branco Client:: Latam - HoustonJose ChuyNo ratings yet

- User Manual: HAT270A ATS (Automatic Transfer Switch) ControllerDocument13 pagesUser Manual: HAT270A ATS (Automatic Transfer Switch) ControllerVinhNo ratings yet

- Fundamentals of Microcontrollers (MCU's) : Hands-On WorkshopDocument23 pagesFundamentals of Microcontrollers (MCU's) : Hands-On WorkshopVIJAYPUTRANo ratings yet

- Energizer L91Document2 pagesEnergizer L91cgmannerheimNo ratings yet

- Solar AbstractDocument2 pagesSolar AbstractjohnjoshrNo ratings yet

- MD-D02 Installation Manual v02 - 200514 - EnglishDocument4 pagesMD-D02 Installation Manual v02 - 200514 - EnglishfgbcnmtNo ratings yet

- EquiposlaboratrioDocument120 pagesEquiposlaboratrioMarwin PilayNo ratings yet

- Guided MissileDocument40 pagesGuided Missileprakhar9045733882100% (2)

- Electromagnetic Induction (196)Document74 pagesElectromagnetic Induction (196)caiogabrielNo ratings yet

- Diagrama Camry 2006Document400 pagesDiagrama Camry 2006miky VelaNo ratings yet

- HP Printer Products ListDocument29 pagesHP Printer Products Listyatin0% (1)

- Simple Circuits and Kirchoffs LawsDocument24 pagesSimple Circuits and Kirchoffs LawsJoseMiguelDomingo100% (1)

- EEC Equivalent CircuitsDocument185 pagesEEC Equivalent CircuitsMert YılmazNo ratings yet

- Freidora DeanDocument54 pagesFreidora Deanjose marcanoNo ratings yet

- Amkor Panczak Copper Wirebondingan OSATViewDocument22 pagesAmkor Panczak Copper Wirebondingan OSATViewbalapmuruganNo ratings yet

- L1710S (L1710sm-Al - R, Au - R, Ad - R, Ag - R) CL-61Document18 pagesL1710S (L1710sm-Al - R, Au - R, Ad - R, Ag - R) CL-61Deki PericNo ratings yet

- B 12 A 6Document8 pagesB 12 A 6ElectromateNo ratings yet

- Improvement of Conventional MPPT Techniques P&O and INC by Integration of Fuzzy LogicDocument6 pagesImprovement of Conventional MPPT Techniques P&O and INC by Integration of Fuzzy LogicMECHNANENo ratings yet

- Industrial RS-232/485 Opto-Isolated Hub/Splitter/Repeater (Part Number: HUB-485-4)Document4 pagesIndustrial RS-232/485 Opto-Isolated Hub/Splitter/Repeater (Part Number: HUB-485-4)Nisar AhmedNo ratings yet

- Atmel AVR Instruction Set - Wikipedia, The Free EncyclopediaDocument4 pagesAtmel AVR Instruction Set - Wikipedia, The Free EncyclopediaNaga PrasadNo ratings yet