Professional Documents

Culture Documents

HAT2198R: Silicon N Channel Power MOS FET Power Switching

Uploaded by

Slava VanatOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

HAT2198R: Silicon N Channel Power MOS FET Power Switching

Uploaded by

Slava VanatCopyright:

Available Formats

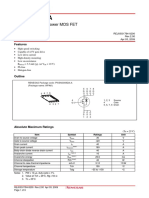

HAT2198R

Silicon N Channel Power MOS FET

Power Switching

REJ03G0062-0200

Rev.2.00

Oct.18.2004

Features

• High speed switching

• Capable of 4.5 V gate drive

• Low drive current

• High density mounting

• Low on-resistance

RDS(on) = 7.2 mΩ typ. (at VGS = 10 V)

Outline

SOP-8

5 6 7 8

D D D D

65

7

4 8 1, 2, 3 Source

G 4 Gate

3

4 5, 6, 7, 8 Drain

1 2

S S S

1 2 3

Absolute Maximum Ratings

(Ta = 25°C)

Item Symbol Ratings Unit

Drain to source voltage VDSS 30 V

Gate to source voltage VGSS ±20 V

Drain current ID 14 A

Drain peak current ID(pulse)Note1 112 A

Body-drain diode reverse drain current IDR 14 A

Note 2

Avalanche current IAP 14 A

Avalanche energy EAR Note 2 19.6 mJ

Channel dissipation Pch Note3 2.5 W

Channel to ambient thermal impedance θch-a Note3 50 °C/W

Channel temperature Tch 150 °C

Storage temperature Tstg –55 to +150 °C

Notes: 1. PW ≤ 10 µs, duty cycle ≤ 1%

2. Value at Tch = 25°C, Rg ≥ 50 Ω

3. When using the glass epoxy board (FR4 40 x 40 x 1.6 mm), PW ≤ 10s

Rev.2.00, Oct.18.2004, page 1 of 7

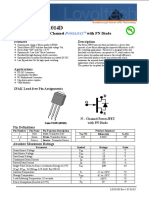

HAT2198R

Electrical Characteristics

(Ta = 25°C)

Item Symbol Min Typ Max Unit Test Conditions

Drain to source breakdown voltage V(BR)DSS 30 — — V ID = 10 mA, VGS = 0

Gate to source leak current IGSS — — ± 0.1 µA VGS = ±20 V, VDS = 0

Zero gate voltage drain current IDSS — — 1 µA VDS = 30 V, VGS = 0

Gate to source cutoff voltage VGS(off) 1.0 — 2.5 V VDS = 10 V, I D = 1 mA

Static drain to source on state RDS(on) — 7.2 9.0 mΩ ID = 7 A, VGS = 10 V Note4

resistance RDS(on) — 9.6 14.0 mΩ ID = 7 A, VGS = 4.5 V Note4

Forward transfer admittance |yfs| 18 30 — S ID = 7 A, VDS = 10 V Note4

Input capacitance Ciss — 1650 — pF VDS = 10 V

Output capacitance Coss — 390 — pF VGS = 0

Reverse transfer capacitance Crss — 135 — pF f = 1 MHz

Gate Resistance Rg — 0.55 — Ω

Total gate charge Qg — 11 — nC VDD = 10 V

Gate to source charge Qgs — 4.7 — nC VGS = 4.5 V

Gate to drain charge Qgd — 2.5 — nC ID = 14 A

Turn-on delay time td(on) — 8.5 — ns VGS = 10 V, ID = 7 A

Rise time tr — 5 — ns VDD ≅ 10 V

Turn-off delay time td(off) — 38 — ns RL = 1.42 Ω

Rg = 4.7 Ω

Fall time tf — 3.8 — ns

Body–drain diode forward voltage VDF — 0.80 1.04 V IF = 14 A, VGS = 0 Note4

Body–drain diode reverse recovery trr — 28 — ns IF = 14 A, VGS = 0

time diF/ dt = 100 A/ µs

Notes: 4. Pulse test

Rev.2.00, Oct.18.2004, page 2 of 7

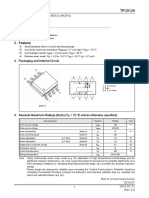

HAT2198R

Main Characteristics

Power vs. Temperature Derating Maximum Safe Operation Area

4.0 500

Test Condition : 10

When using the glass epoxy board µs

Pch (W)

100

ID (A)

(FR4 40 x 40 x 1.6 mm), PW < 10 s 10

3.0 0µ

1m s

DC PW s

10 Op =1

era 0m

Drain Current

Channel Dissipation

tio s

n(

2.0 PW

1 < 1Note

Operation in 0s 5

)

this area is

1.0 limited by RDS(on)

0.1

Ta = 25°C

1 shot Pulse

0.01

0 50 100 150 200 0.1 0.3 1 3 10 30 100

Ambient Temperature Ta (°C) Drain to Source Voltage VDS (V)

Note 5 :

When using the glass epoxy board

(FR4 40x40x1.6 mm)

Typical Output Characteristics Typical Transfer Characteristics

20 20

10 V Pulse Test VDS = 10 V

3V 2.8 V Pulse Test

16 16

ID (A)

ID (A)

12 12

Drain Current

2.6 V

Drain Current

Tc = 75°C

8 8

VGS = 2.4 V 25°C

4 4

–25°C

0 2 4 6 8 10 0 1 2 3 4 5

Drain to Source Voltage VDS (V) Gate to Source Voltage VGS (V)

Drain to Source Saturation Voltage vs. Static Drain to Source on State Resistance

Gate to Source Voltage vs. Drain Current

VDS(on) (mV)

300 100

Drain to Source On State Resistance

Pulse Test Pulse Test

VDS(on) (mΩ)

50

240

V GS = 4.5 V

20

180

Drain to Source Voltage

ID = 20 A

10

10 V

120

5

10 A

60

5A 2

1

0 4 8 12 16 20 1 10 100 1000

Gate to Source Voltage VGS (V) Drain Current ID (A)

Rev.2.00, Oct.18.2004, page 3 of 7

HAT2198R

Static Drain to Source on State Resistance Forward Transfer Admittance vs.

vs. Temperature Drain Current

20 1000

Static Drain to Source on State Resistance

RDS(on) (mΩ)

Forward Transfer Admittance |yfs| (S)

Pulse Test

20 A

16 Tc = –25°C

I = 5 A, 10 A

D 100

12 V

GS = 4.5 V

10

8 25°C

5 A, 10 A, 20 A

1 75°C

10 V

4

VDS = 10 V

Pulse Test

0

-25 0 25 50 75 100 125 150 0.1 0.3 1 3 10 30 100

Case Temperature Tc (°C) Drain Current ID (A)

Body–Drain Diode Reverse Typical Capacitance vs.

Recovery Time Drain to Source Voltage

100 10000

Reverse Recovery Time trr (ns)

3000

Ciss

Capacitance C (pF)

50

1000

Coss

300

Crss

20 100

di/dt = 100 A/µs 30 VGS = 0

VGS = 0, Ta = 25°C f = 1 MHz

10 10

0.1 1 10 100 0 5 10 15 20 25 30

Reverse Drain Current IDR (A)

Drain to Source Voltage VDS (V)

Dynamic Input Characteristics Switching Characteristics

50 20 1000

VDS (V)

ID = 14 A VGS = 10 V, VDS = 10 V

V GS (V)

Rg = 4.7 Ω, duty < 1 %

40 VGS 16

Switching Time t (ns)

VDD = 25 V

100

Drain to Source Voltage

10 V

Gate to Source Voltage

30 5V 12 t d(off)

VDS

tr

20 8 t d(on)

10

VDD = 25 V

10 10 V 4

5V tf

0 1

0 8 16 24 32 40 0.1 1 10 100

Gate Charge Qg (nc) Drain Current ID (A)

Rev.2.00, Oct.18.2004, page 4 of 7

HAT2198R

Reverse Drain Current vs. Maximum Avalanche Energy vs.

Source to Drain Voltage Channel Temperature Derating

20

Repetitive Avalanche Energy EAR (mJ)

20

IAP = 11 A

(A) 10 V VDD = 15 V

16 16

Reverse Drain Current IDR

duty < 0.1 %

5V Rg > 50 Ω

12 VGS = 0,-5 V 12

8 8

4 4

Pulse Test

0

0 0.4 0.8 1.2 1.6 2.0 25 50 75 100 125 150

Source to Drain Voltage VSD (V) Channel Temperature Tch (°C)

Normalized Transient Thermal Impedance vs. Pulse Width

10

Normalized Transient Thermal Impedance

γs (t)

D=1

1

0.5

0.2

0.1

0.1

0.05

θch - f(t) = γs (t) x θch - f

0.02 θch - f = 83.3°C/W, Ta = 25°C

0.01

0.01 When using the glass epoxy board

lse (FR4 40 x 40 x 1.6 mm)

t pu

ho PW

0.001 1s PDM D=

T

PW

T

0.0001

10 µ 100 µ 1m 10 m 100 m 1 10 100 1000 10000

Pulse Width PW (s)

Rev.2.00, Oct.18.2004, page 5 of 7

HAT2198R

Avalanche Test Circuit Avalanche Waveform

1 VDSS

EAR = L • IAP2 •

L 2 VDSS - V DD

V DS

Monitor

I AP V (BR)DSS

Monitor

I AP

Rg D. U. T VDD V DS

ID

Vin 50Ω

15 V

VDD

0

Switching Time Test Circuit Switching Time Waveform

Vin Monitor Vout 90%

Monitor

D.U.T.

Rg RL Vin 10%

Vout 10% 10%

Vin V DS

10 V = 10 V

90% 90%

td(on) tr td(off) tf

Rev.2.00, Oct.18.2004, page 6 of 7

HAT2198R

Package Dimensions

As of January, 2003

Unit: mm

4.90

5.3 Max

8 5

3.95

1 4

*0.22 ± 0.03

0.20 ± 0.03

1.75 Max

+ 0.10

6.10 – 0.30

0.75 Max

1.08

0˚ – 8˚

+ 0.11

0.14 – 0.04

+ 0.67

1.27 0.60 – 0.20

*0.42 ± 0.08

0.40 ± 0.06

0.15

0.25 M

Package Code FP-8DA

JEDEC Conforms

*Dimension including the plating thickness JEITA —

Base material dimension Mass (reference value) 0.085 g

Ordering Information

Part Name Quantity Shipping Container

HAT2198R-EL-E 2500 pcs Taping

Note: For some grades, production may be terminated. Please contact the Renesas sales office to check the state of

production before ordering the product.

Rev.2.00, Oct.18.2004, page 7 of 7

Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

Keep safety first in your circuit designs!

1. Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble

may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits,

(ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

Notes regarding these materials

1. These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's

application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party.

2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data,

diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of

publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is

therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product

information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors.

Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corp. by various means, including the Renesas Technology Corp. Semiconductor

home page (http://www.renesas.com).

4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to

evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes

no responsibility for any damage, liability or other loss resulting from the information contained herein.

5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life

is potentially at stake. Please contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor when considering the use of a

product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater

use.

6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials.

7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and

cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

RENESAS SALES OFFICES http://www.renesas.com

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

Renesas Technology America, Inc.

450 Holger Way, San Jose, CA 95134-1368, U.S.A

Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K.

Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology Hong Kong Ltd.

7th Floor, North Tower, World Finance Centre, Harbour City, 1 Canton Road, Tsimshatsui, Kowloon, Hong Kong

Tel: <852> 2265-6688, Fax: <852> 2730-6071

Renesas Technology Taiwan Co., Ltd.

10th Floor, No.99, Fushing North Road, Taipei, Taiwan

Tel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999

Renesas Technology (Shanghai) Co., Ltd.

Unit2607 Ruijing Building, No.205 Maoming Road (S), Shanghai 200020, China

Tel: <86> (21) 6472-1001, Fax: <86> (21) 6415-2952

Renesas Technology Singapore Pte. Ltd.

1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632

Tel: <65> 6213-0200, Fax: <65> 6278-8001

© 2004. Renesas Technology Corp., All rights reserved. Printed in Japan.

Colophon .2.0

You might also like

- Hat2198r 4Document8 pagesHat2198r 4srikrishNo ratings yet

- RJK0393DPA: Silicon N Channel Power MOS FET Power SwitchingDocument7 pagesRJK0393DPA: Silicon N Channel Power MOS FET Power Switchingbrunex000No ratings yet

- Rjk03e3dns MosfetDocument7 pagesRjk03e3dns MosfetkarkeraNo ratings yet

- RJK03S3DPADocument7 pagesRJK03S3DPAvineeth MNo ratings yet

- RJK0332DPB 01Document7 pagesRJK0332DPB 01Alberto CruzNo ratings yet

- RJK0393DPA RenesasTechnologyDocument7 pagesRJK0393DPA RenesasTechnologyDirson Volmir WilligNo ratings yet

- RJK0632JPD RenesasDocument7 pagesRJK0632JPD RenesasKwun Hok ChongNo ratings yet

- RJK0355DPA: Silicon N Channel Power MOS FET Power SwitchingDocument7 pagesRJK0355DPA: Silicon N Channel Power MOS FET Power SwitchingalexNo ratings yet

- HAT2114R, HAT2114RJ: Silicon N Channel Power MOS FET High Speed Power SwitchingDocument11 pagesHAT2114R, HAT2114RJ: Silicon N Channel Power MOS FET High Speed Power SwitchingTahar BenacherineNo ratings yet

- HAT2050T: Silicon N Channel Power MOS FET High Speed Power SwitchingDocument9 pagesHAT2050T: Silicon N Channel Power MOS FET High Speed Power SwitchingDinh Thuong CaoNo ratings yet

- RJK6014DPP: Silicon N Channel MOS FET High Speed Power SwitchingDocument4 pagesRJK6014DPP: Silicon N Channel MOS FET High Speed Power Switchingnnaans2013No ratings yet

- HAT1020 - Mosf Canal N SMDDocument11 pagesHAT1020 - Mosf Canal N SMDSergio MuriloNo ratings yet

- HAT2033R HitachiSemiconductorDocument10 pagesHAT2033R HitachiSemiconductorAmir MirnejadNo ratings yet

- 2SK2926 (L), 2SK2926 (S) : Silicon N Channel MOS FET High Speed Power SwitchingDocument9 pages2SK2926 (L), 2SK2926 (S) : Silicon N Channel MOS FET High Speed Power SwitchingNgoc AnNo ratings yet

- SOT-23-6L Plastic-Encapsulate MOSFETS: CJL8205ADocument5 pagesSOT-23-6L Plastic-Encapsulate MOSFETS: CJL8205AdexterNo ratings yet

- RJK0631JPD RenesasDocument7 pagesRJK0631JPD RenesasAbraham GutierrezNo ratings yet

- 2SK2978 RenesasDocument7 pages2SK2978 RenesasJuan NunesNo ratings yet

- Irf8736Pbf: ApplicationsDocument9 pagesIrf8736Pbf: ApplicationsAnilVarmaNo ratings yet

- Chopper Regulator Applications: Maximum RatingsDocument6 pagesChopper Regulator Applications: Maximum RatingsDinh NguyenNo ratings yet

- Infineon IRF8736 DataSheet v01 - 01 ENDocument10 pagesInfineon IRF8736 DataSheet v01 - 01 ENElbertt GonzalezNo ratings yet

- Silicon N Channel MOS FET High Speed Power Switching: FeaturesDocument8 pagesSilicon N Channel MOS FET High Speed Power Switching: FeaturesVictorJimmy Ibañez AlanocaNo ratings yet

- Silicon N Channel MOS FET: ApplicationDocument7 pagesSilicon N Channel MOS FET: ApplicationJesusRiveroNo ratings yet

- Silicon N Channel MOS FET: ApplicationDocument9 pagesSilicon N Channel MOS FET: ApplicationHeri AltisNo ratings yet

- TPC8065-H TPC8065-H TPC8065-H TPC8065-HDocument9 pagesTPC8065-H TPC8065-H TPC8065-H TPC8065-HRamiro Q ChNo ratings yet

- Lu1014d 1Document5 pagesLu1014d 1ettorreitNo ratings yet

- Notebook PC Applications Portable Equipment Applications: Absolute Maximum RatingsDocument7 pagesNotebook PC Applications Portable Equipment Applications: Absolute Maximum RatingsNATHANEASTBOUNDNo ratings yet

- 2 SK 2417Document6 pages2 SK 2417Darush RjNo ratings yet

- 2 SK 2350Document6 pages2 SK 2350jesus cautivoNo ratings yet

- Irf 7403Document9 pagesIrf 7403Макс БелыйNo ratings yet

- IRF510A: Advanced Power MOSFETDocument7 pagesIRF510A: Advanced Power MOSFETOuzeren AbdelhakimNo ratings yet

- 4435sc Datasheet Mosfet Canal P PDFDocument8 pages4435sc Datasheet Mosfet Canal P PDFLuis Luis GarciaNo ratings yet

- Data Sheet: ApplicationDocument7 pagesData Sheet: ApplicationDani HpNo ratings yet

- Switching Regulator Applications: Maximum RatingsDocument6 pagesSwitching Regulator Applications: Maximum RatingsPramote RodbonNo ratings yet

- 17N40K-MT: Unisonic Technologies Co., LTDDocument5 pages17N40K-MT: Unisonic Technologies Co., LTDmanda fanoaNo ratings yet

- Irlz24n PDFDocument9 pagesIrlz24n PDFSantiago DiosdadoNo ratings yet

- KIA KIA KIA: 1.descriptionDocument5 pagesKIA KIA KIA: 1.descriptionhugos31No ratings yet

- N Mosfet: Shenzhen Tuofeng Semiconductor Technology Co., LTDDocument2 pagesN Mosfet: Shenzhen Tuofeng Semiconductor Technology Co., LTDJUANNo ratings yet

- NDC7002N Dual N-Channel Enhancement Mode Field Effect TransistorDocument10 pagesNDC7002N Dual N-Channel Enhancement Mode Field Effect TransistorforogNo ratings yet

- Irlml 5103 PBFDocument9 pagesIrlml 5103 PBFBoniface AsuvaNo ratings yet

- IRF7832Z: V R Max QGDocument10 pagesIRF7832Z: V R Max QGShamim DhaliNo ratings yet

- Dual Enhancement Mode Field Effect Transistor (N and P Channel)Document11 pagesDual Enhancement Mode Field Effect Transistor (N and P Channel)BubunGuchhaitNo ratings yet

- 16N50Document6 pages16N50Fábio Vitor MartinsNo ratings yet

- LD1010DDocument5 pagesLD1010DJelatang KalapiahNo ratings yet

- KF 4 N 20 LWDocument6 pagesKF 4 N 20 LWJosé Manuel Izea NavarroNo ratings yet

- Switching Regulator, DC/DC Converter and Motor Drive ApplicationsDocument6 pagesSwitching Regulator, DC/DC Converter and Motor Drive ApplicationsMaj HusNo ratings yet

- TPC8129 Datasheet en 20140121 PDFDocument9 pagesTPC8129 Datasheet en 20140121 PDFCHARIS ZEVGARASNo ratings yet

- Switching Regulator Applications: Maximum RatingsDocument6 pagesSwitching Regulator Applications: Maximum RatingsJose M PeresNo ratings yet

- Sot-23-6 Plastic-Encapsulate Mosfets: Shenzhen Cansheng Industry Development Co.,LtdDocument4 pagesSot-23-6 Plastic-Encapsulate Mosfets: Shenzhen Cansheng Industry Development Co.,LtdKamal Kishore SharmaNo ratings yet

- TK10A60D: Switching Regulator ApplicationsDocument7 pagesTK10A60D: Switching Regulator ApplicationsAlexNo ratings yet

- Chopper Regulator, DC DC Converter and Motor Drive ApplicationsDocument7 pagesChopper Regulator, DC DC Converter and Motor Drive ApplicationsPablo AllosiaNo ratings yet

- KIA KIA KIA: 1.descriptionDocument5 pagesKIA KIA KIA: 1.descriptionOscarVargasNo ratings yet

- 8205A RZCMicroelectronicsDocument6 pages8205A RZCMicroelectronicsabdouzaouiidrissiNo ratings yet

- Shenzhen Tuofeng Semiconductor Technology Co., LTD: 4800 N-Channel Reducded Q, Fast Switching MOSFETDocument4 pagesShenzhen Tuofeng Semiconductor Technology Co., LTD: 4800 N-Channel Reducded Q, Fast Switching MOSFETMario QuiroaNo ratings yet

- HL Haolin Elec 5N04 - C237240Document4 pagesHL Haolin Elec 5N04 - C237240German ValenciaNo ratings yet

- STD16NF06: N-Channel 60V - 0.060 - 16A - DPAK Stripfet™ Ii Power MosfetDocument11 pagesSTD16NF06: N-Channel 60V - 0.060 - 16A - DPAK Stripfet™ Ii Power MosfetJose AlbertoNo ratings yet

- Infineon IRLML2502 DataSheet v01 - 01 ENDocument10 pagesInfineon IRLML2502 DataSheet v01 - 01 ENabbaseftekhariNo ratings yet

- La Conquista Divina Aw TozerDocument4 pagesLa Conquista Divina Aw TozerEmmanuel ZambranoNo ratings yet

- DatasheetDocument9 pagesDatasheetmaumaugarridoNo ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- Kozinets Gretzel 2020 Commentary Artificial Intelligence The Marketer S DilemmaDocument4 pagesKozinets Gretzel 2020 Commentary Artificial Intelligence The Marketer S DilemmalionelfamNo ratings yet

- 21 InfotainmentDocument10 pages21 InfotainmentIqtidar ANo ratings yet

- Cybercrime Tactics and Techniques: Q3 2018: Provided byDocument27 pagesCybercrime Tactics and Techniques: Q3 2018: Provided byAndres Felipe CameroNo ratings yet

- MockDocument19 pagesMockSourabh JakharNo ratings yet

- Interactive Paper and Cross-Media PublishingDocument13 pagesInteractive Paper and Cross-Media PublishingBeat SignerNo ratings yet

- RAN Signaling Analysis Guide (RAN10.0 - 02)Document245 pagesRAN Signaling Analysis Guide (RAN10.0 - 02)Juan Camilo GalvisNo ratings yet

- Service Agreement Between Awfis Space Solutions Private Limited ("Awfis") AND GHV Advanced Care Private Limited ("Company")Document25 pagesService Agreement Between Awfis Space Solutions Private Limited ("Awfis") AND GHV Advanced Care Private Limited ("Company")Abhinav KumarNo ratings yet

- Homology Modeling: Ref: Structural Bioinformatics, P.E Bourne Molecular Modeling, FolkersDocument16 pagesHomology Modeling: Ref: Structural Bioinformatics, P.E Bourne Molecular Modeling, FolkersPallavi VermaNo ratings yet

- 3AH4 Breaker Cn (油品 P26)Document29 pages3AH4 Breaker Cn (油品 P26)kokonut1128No ratings yet

- OptiX OSN 1800 Brochure PDFDocument4 pagesOptiX OSN 1800 Brochure PDFThi KháchNo ratings yet

- IT111 Mod3CDocument48 pagesIT111 Mod3CAlthea Lei Delos ReyesNo ratings yet

- JHLCT rm10 WBHF en 02i DatasheetDocument2 pagesJHLCT rm10 WBHF en 02i DatasheetBao Quoc MaiNo ratings yet

- 30 B 5 C 7Document16 pages30 B 5 C 7Irfan shagooNo ratings yet

- Diagnostic Grammar Test-CopiarDocument6 pagesDiagnostic Grammar Test-CopiarJuliana PachonNo ratings yet

- Computer BasicsDocument94 pagesComputer Basicssanthosh hkNo ratings yet

- Comparison of Digital Fiber DAS and Analog Fiber DASDocument13 pagesComparison of Digital Fiber DAS and Analog Fiber DASRam BhagatNo ratings yet

- Meeting and Interview MinutesDocument5 pagesMeeting and Interview MinutesRadoslav RobertNo ratings yet

- AIF BizTalk Adapter Configuration For Data Exchange Part IIDocument46 pagesAIF BizTalk Adapter Configuration For Data Exchange Part IIUmbBNo ratings yet

- Testbook2 AOPDocument231 pagesTestbook2 AOPJahed AhmedNo ratings yet

- As400 Subfile Programming Part II Basic CodingDocument13 pagesAs400 Subfile Programming Part II Basic Codingmaka123No ratings yet

- Bim Modeler & Site EngineerDocument2 pagesBim Modeler & Site EngineerMOHAMMADNo ratings yet

- Osama Quantum ComputingDocument49 pagesOsama Quantum ComputingErvin HodzicNo ratings yet

- Third-Party Tools As Destinations For OHDDocument27 pagesThird-Party Tools As Destinations For OHDNeha JhaNo ratings yet

- Google Ads Certification - Study GuideDocument6 pagesGoogle Ads Certification - Study GuideHadassa KalungaNo ratings yet

- DivideDocument19 pagesDivideБектурганова БектургановаNo ratings yet

- Sat 2004 Maths QuestionsDocument3 pagesSat 2004 Maths QuestionsSai Sumanth PNo ratings yet

- Add Disk and Create A PartitionDocument2 pagesAdd Disk and Create A PartitionaitlhajNo ratings yet

- Pythagorean Theorem WorksheetDocument4 pagesPythagorean Theorem WorksheetKhin Myat MawNo ratings yet

- Ecological Modelling and Energy DSSDocument325 pagesEcological Modelling and Energy DSSNàpoles RaymundoNo ratings yet

- My CAPE Computer Science Internal AssessmentDocument24 pagesMy CAPE Computer Science Internal Assessmentrod-vaughnNo ratings yet