Professional Documents

Culture Documents

Analysis and Design of Self-Oscillating Flyback Converter: Brian T. Irving and Milan M. Jovanović

Analysis and Design of Self-Oscillating Flyback Converter: Brian T. Irving and Milan M. Jovanović

Uploaded by

Javier Avalos GallosOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Analysis and Design of Self-Oscillating Flyback Converter: Brian T. Irving and Milan M. Jovanović

Analysis and Design of Self-Oscillating Flyback Converter: Brian T. Irving and Milan M. Jovanović

Uploaded by

Javier Avalos GallosCopyright:

Available Formats

Analysis and Design of Self-Oscillating Flyback Converter

Brian T. Irving and Milan M. Jovanović

Delta Products Corporation

Power Electronics Laboratory

P.O. Box 12173, 5101 Davis Drive

Research Triangle Park, N.C. 27709, U.S.A.

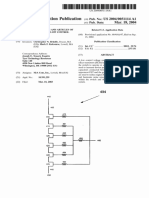

Abstract –The self-oscillating flyback converter is a popular circuit for applications which require a tight output regulation, such as

cost-sensitive applications due to its simplicity and low component count. It applications with a wide range of input voltage and load

is widely employed in mobile phone chargers and as the stand-by power

source in off-line power supplies for data-processing equipment. However, current, an error amplifier is often implemented.

the optimization of this circuit is almost exclusively performed by a cut- The circuit diagram of an isolated self-oscillating flyback

and-try approach since its operation is generally not well understood. This converter with output voltage control is shown in Fig. 1.

paper presents a detailed steady-state analysis of the self-oscillating flyback Transformer T1 consists of 2 secondary windings: output

converter along with its small-signal model. Design guidelines of the

control circuit and loop compensation are presented and verified on an off- winding NS1 and positive-feedback winding NS2. Main output

line, stand-by, 5-V/ 2-A power supply. VO1 is isolated, and tightly regulated by error amplifier E/A,

whereas auxiliary output VO2 is not isolated, and is loosely

I. INTRODUCTION regulated by main output VO1 through transformer T1. Output

voltage VO1 is sensed through a resistor divider consisting of

The self-oscillating flyback converter, often referred to as resistors Rd1 and Rd2, and compared at the input of a

the ringing choke converter (RCC), is a robust, low- transconductance type amplifier (TL431) to a stable voltage

component-count circuit that has been widely used in low- reference located within the TL431 device. Components

power off-line applications. Since the control of the circuit CEA1, CEA2, and REA1 are used as compensation to stabilize the

can be implemented with very few discrete components voltage control loop. The difference between the sensed

without loss of performance, the overall cost of the circuit is output voltage and the voltage reference is amplified by

generally lower than the conventional PWM flyback TL431 and reflected to the primary side through optocoupler

converter that employs a commercially available integrated IC1 as error current ie, which in turn develops error voltage Ve

control . across (the sum of) resistors RS and RF. Error voltage Ve is

Generally, the operation of the circuit is not well summed with a voltage proportional to switch current iS1 and

understood. This is primarily due to the fact that existing compared at the PWM modulator, which is implemented with

literature deals with the circuit in a very superficial manner bipolar junction transistor (BJT) Q1, to a fixed voltage

[1]-[2]. Therefore, the design of this converter usually threshold, which, in this case, is cut-off voltage Vγ of

follows a cut- and-try approach, which is a time consuming transistor Q1. Zero-current detect components CZCD and RZCD,

process and which usually doesn’t lead to an optimized along with winding NS2, sense, with some delay, the

design. continuous/discontinuous conduction mode (CCM/DCM)

The purpose of this paper is to present a complete design- boundary of transformer T1, and delivers charge to main

oriented steady-state analysis and small-signal model of the switch S1 to initiate switch turn-on. Finally, circuit start-up is

self-oscillating flyback converter that can be used in the T1 D1 LF

optimization of this circuit. In addition, a step-by-step design i01

NP NS1 i 1

procedure of the control circuit is presented and verified on CO1 CF RL1 Rd1

an off-line, 5-V/2-A, stand-by power supply. VO1

Rd2

RST

VIN

II. ANALYSIS OF OPERATION

S1 NS2

The self-oscillating flyback converter operates at the VDS

V2

CO2 RL2

VO2

boundary of continuous/discontinuous conduction mode i2 i02

VG i S1 D2 IK

(CCM/DCM) and utilizes peak current mode control. ZD1

Therefore, the circuit operates with a variable switching RS R ZCD

IC1

frequency. The implementation of the control is done V ZCD C ZCD RF

Vd

discretely, which is simple and cost effective since the pulse- RA

Q1 RB

width modulator (PWM) and switch driver are implemented PWM VQbe

ie CEA2

with a single transistor, a positive-feedback winding, and a MOD CEA1 REA1

resistor divider network. In applications which do not require VKA

TL431

tight regulation, a simple feedback control consisting of a E/A

single zener diode may be implemented. However, in

Fig. 1 Circuit diagram of self-oscillating flyback converter

0-7803-7405-3/02/$17.00 (C) 2002 IEEE

initiated through resistor RST, which delivers charge to input transistor Q1 will be in the off state only if it’s base-emitter

capacitance CISS of main switch S1 from input voltage VIN. voltage VQbe is below it’s cut-off voltage Vγ. Since, from

A. Steady-State Operation Fig. 2(a), VQbe = i e R F + iS1R S ≈ i e R F because iS1R S << i e R F ,

In order to simplify the explanation of the converter shown transistor Q1 is off during t0 < t < t1 if i e R F < Vγ . The stage in

in Fig. 1 during steady-state operation, several Fig. 2(a) ends at t = t1 when voltage VGS has decreased to the

approximations have been made. The first approximation is voltage level which is approximately one diode voltage drop

to neglect the leakage inductance of transformer T1. This below voltage VQbe of transistor Q1 so that its base-collector

eliminates the need to consider the action of a voltage clamp pn junction becomes forward biased.

across primary winding NP which is implemented to protect After base-collector diode Dbc starts conducting at t = t1,

main switch S1 from voltage ringings. The second current ie is divided between resistor RF and the base of Q1.

approximation is to model error current ie as a constant- Because collector-emitter voltage VQce is negative, transistor

current source, i.e., to replace compensated error amplifier Q1 operates in the inverse-constant-current region and current

TL431, opto-coupler IC1, capacitor CF, and resistors Rd1, Rd2, iQce flows from the emitter to collector, as shown in Fig. 2 (b).

RA, and RB with constant-current source ie. The final During this stage, capacitor CZCD continues to discharge by

approximation is to neglect the capacitance CGD between the the sum of currents iQce and iQbc. As a result, voltage VQbe

gate and drain terminals of main switch S1 and to model the increases exponentially as illustrated in waveform (f) of

terminal capacitances between the gate and source CGS and Fig. 3. At the same time, currents i1 and i2 continue to

between drain and source CDS as input capacitance CISS and decrease. This stage ends at t = t2 when rising voltage VO2

output capacitance COSS respectively. In addition to these reaches the winding voltage V2 and rectifier D2 turns off.

approximations, it is assumed that CO1>>CO2, and RL1<<RL2. Meanwhile, capacitor CZCD continues to discharge through

The assumption CO1>>CO2 implies that the ripple voltage of winding NS2, as shown in Fig. 2(c). During this stage, current

output VO2 is greater than the ripple voltage of main output i1 continues to decrease. This stage ends at t = t3 when current

VO1. Another assumption is that time constant RSTCISS is i1 reaches zero, i.e., when magnetizing energy of the

much greater than switching period TS, i.e., RSTCISS>>TS. transformer is completely discharged.

With this assumption, it is possible to ignore start-up resistor Since at t = t3, drain-source voltage VDS of switch S1 is

RST during steady-state operation. Finally, it is assumed that higher than input voltage VIN, capacitor COSS starts to

rectifiers D1 and D2 are ideal i.e., have zero forward voltage resonantly discharge through magnetizing inductance LM, as

drop while conducting. can be seen in waveform (b) of Fig. 3. As a result, primary

To facilitate the explanation of the converter operation, voltage VP decreases, causing a proportional decrease in

Fig. 2 shows eleven topological stages of the circuit in Fig. 1 secondary voltage V2. As the secondary voltage decreases,

during a switching cycle, including the reference directions of the voltage across resistor RZCD also decreases which

currents and voltages, whereas Fig. 3 shows key waveforms decreases current iZCD. This topological stage ends at t = t4

of the power and control stage. when current iZCD reaches zero.

Prior to t = t0, current iQce and voltage VCZCD is positive, After t = t4, current iZCD starts flowing in the opposite

and switch S1 is turning off because charge is drawn from direction so that capacitors CZCD and CISS start to charge, as

input capacitance CISS of main switch S1 by transistor Q1. As shown in Fig. 2(e). Since the increase of voltage VGS leads to

a result, drain-source voltage VDS increases towards the increase of collector-emitter voltage VQce, diode Dbc turns

VIN + NVO. When, at t = t0, voltage VDS reaches VIN + NVO, off, causing the turn-off of transistor Q1. At the same time,

rectifiers D1 and D2 start conducting. During this stage, which capacitor COSS continues to resonantly discharge, which

is shown in Fig. 2(a), magnetizing current iM is further decreases secondary winding voltage V2. As a result,

instantaneously commutated from switch S1 to output the voltage across resistor RZCD increases which causes a

rectifiers D1 and D2 since it is assumed that leakage further increase of current iZCD. This topological stage ends at

inductance Llkg of the transformer is zero. In the presence of t = t5 when the voltage across the windings of the transformer

winding resistances (not shown in Fig. 2), the selection of become equal to zero. After t = t5, capacitor COSS continues to

output capacitors CO1>>CO2 causes voltage VO1 to be discharge and the winding voltages change polarity, as shown

approximately constant while voltage VO2 increases, which in Fig. 2(f). Because in this topological stage voltage

results in a faster decrease of current i2 with respect to current VO2 + V2, which drives current iZCD, continues to increase,

i1, as shown in waveforms (d) and (e) of Fig. 3. Because current iZCD also continues to increase. This increased current

during this topological stage rectifier D2 is conducting, iZCD causes an increase of voltage VGS, which in turn

voltage VRZCD across resistor RZCD is equal to produces a further discharge of capacitor COSS and

−(VGS + VS + VCZCD ) ≈ −(VGS + VCZCD ) since VS << VGS + VCZCD . This consequently a further increase in the sum of voltages VO2

voltage induces current iZCD through resistor RZCD which and V2. This positive feedback continues until voltage VGS

discharges capacitors CISS and CZCD. At the same time, reaches voltage VTH at t = t6 and switch S1 is turned on by

transistor Q1 is off and current ie flows through the loop entering it’s constant-current region.

consisting of resistors RF, RS, and RL2. It should be noted that After t = t6, gate-source voltage VGS continues to increase

0-7803-7405-3/02/$17.00 (C) 2002 IEEE

T1

D1 i1 CO1 R L1 D1 CO1 RL1 D1 CO1 RL1

N S1 V1 V01 NS1 NS1

RCO1 RCO1

NP NS2 NP NS2 NP NS2

CO2 R L2 CO2 RL2 CO2 RL2

LM iM VP V2 V02 LM LM

D2 i2 RCO2 D2 RCO2

VIN V IN V IN

iS1

VRZCD RZCD RZCD D2 RZCD

S1 CZCD

VZCD S1 D S1 D

VCZCD G CZCD G CZCD

V DS

iQce COSS COSS

iRf CISS C ISS

VGS S S

RF RF

VQbc RF ie c c Dbc

Q1 RS RS

VS RS

iQb

VQbe e Q1 b ie e Q1 b ie

(a) (b) t 0 t1 (c) t 1 t2

D1 CO1 RL1 D1 C RL1 D1 C RL1

O1 O1

NS1 NS1 NS1

RCO1 RCO1 RCO1

NP NS2 NP NS2 NP NS2

LM CO2 RL2 LM CO2 RL2 LM CO2 RL2

RCO2 RCO2 RCO2

V IN V IN V IN

S1 D RZCD S1 D RZCD S1 D RZCD

G CZCD G CZCD G CZCD

COSS COSS COSS

C ISS CISS C ISS

S S S

RF RF RF

c Dbc c Dbc c

RS RS RS

e Q1 b ie e Q1 b ie e Q1 b ie

(d) t 2 t3 (e) t 3 t4 (f) t 4 t5

D1 C RL1 D1 C RL1 D1 C RL1

NS1 O1 NS1 O1 NS1 O1

RCO1 R CO1 RCO1

NP NS2 NP NS2 NP NS2

CO2 RL2 CO2 RL2 CO2 RL2

LM LM LM

RCO2 R CO2 RCO2

V IN V IN V IN

S1 D RZCD RZCD RZCD

D D

G CZCD S1 G CZCD S1

G CZCD

COSS

C ISS CISS C ISS

S S S

RF RF RF

c c c

RS RS RS

e Q1 b ie e Q1 b ie e Q1 b ie

(g) t 5 t6 (h) t 6 t7 (i) t 7 t8

D1 CO1 RL1 D1 C RL1 D1 CO1 RL1

NS1 NS1 O1 NS1

RCO1 RCO1 RCO1

NP NS2 NP NS2 NP NS2

CO2 RL2 CO2 RL2 CO2 RL2

LM LM LM

RCO2 RCO2 RCO2

V IN V IN V IN

RZCD RZCD RZCD

D D D

S1

G CZCD S1

G CZCD S1

G CZCD

C ISS CISS C ISS

S S S

RF RF RF

c c c

b b b

RS Q1 RS Q1 RS Q1

e ie e ie e ie

(j) t 8 t9 (k) t 9 t 10 (l) t 10 t 11

Fig. 2 (a) Simplified circuit diagram of self-oscillating flyback converter which contains voltage and current designators. (b) – (l) Topological stages of

self-oscillating flyback converter.

as current iZCD continues to flow through capacitor CISS, as turned on. After switch S1 is fully turned on at t = t7, drain-

shown in Fig. 2(g). This stage ends at t = t7 when gate-source source current iS1 starts increasing linearly with slope

voltage VGS reaches the level where switch S1 begins diS1 dt = VIN L M . As a result, voltage drop VS = iS1RS across

operating in the ohmic region, i.e., when switch S1 is fully sensing resistor RS also increases with the same slope. This

0-7803-7405-3/02/$17.00 (C) 2002 IEEE

t1 t3 t5 t7 t 9 t11

t0 t2 t4 t6 t8 t10

amplifier compensation requires knowledge of the small-

(a)

VGS

VTH

signal transfer functions in the control loop. Since the self-

t oscillating flyback converter operates with a variable

VDS ,

VIN +NVO1 switching frequency, the small-signal block diagram model

VIN+NVO1 VIN (b) differs from that of the conventional, constant-frequency type

VDS PWM converter, as discussed in [3].

t To facilitate the design optimization of the control loop, the

i

S1 (c) self-oscillating flyback circuit in Fig. 1 has been simplified to

t

include only circuit elements which plays a role in the

i

1 (d) feedback control, as shown in Fig. 4. Zero-current-detect

i

t components RZCD and CZCD, which are related to the

2 (e) switching transitions, and zener diode ZD1, which clamps the

Vγ

t potential of the gate terminal of switch S1, are neglected.

VQbe (f)

Also, since small-signal error current îe is not a function of

t

output voltage VO2, but rather is a function of small-signal

iRF (g)

error amplifier current îEA , auxiliary winding NS2, capacitor

t

(h) CO2, resistor RL2, and rectifier D2 can be neglected. Small-

iQce

t signal error current îe can, therefore, be represented as a

VCZCD (i)

dependent current source, as shown in Fig. 4. Finally, start-up

resistor RST is neglected.

t

Based on this equivalent circuit, the small signal block

Fig. 3 Power stage and control stage key waveforms diagram is derived, as shown in Fig. 5. The block diagram

increases the potential of the source terminal of switch S1, consists of control-to-output voltage transfer function

which also increases the potentials of the gate terminal of S1 G VeVo (s) = V̂O V̂e , output voltage sensing gain K d = V̂1 V̂O , error

and the base terminal of Q1, as shown in waveforms (a) and amplifier transfer function G EA (s) = V̂EA V̂1 , transconductance

(f) of Fig. 3. When, at t = t8, base-emitter voltage VQbe

gain G1 = îEA V̂B , opto-coupler gain G 2 = îe îEA , and

reaches it’s cut-off voltage Vγ, transistor Q1 starts conducting,

as shown in Fig. 2(i). It should be noted that to prevent the transresistance gain G 3 = V̂e îe . The transfer function

gate voltage of switch S1 of exceeding the maximum rated expressions are summarized in Table 1. The block diagram is

voltage, a voltage clamp (such as a zener diode) should be further simplified by incorporating transfer function blocks

connected between the gate terminal of S1 and ground. Once GVeVo(s), G1, G2, and G3 into block G VEA VO (s) = V̂O V̂EA to

the gate voltage is clamped, current is diverted from input

form a single loop system, where

capacitance CISS to the voltage clamp until the gate voltage

V̂O G 1G 2 G 3 G VeVo (s) TINNER

falls below the clamp voltage level. G VEA VO (s) = = = , (1)

V̂EA 1 + G 1G 2 G 3 G VeVo (s) 1 + TINNER

Since after t = t8 voltage VQbe continues to increase because

voltage VS = iS1RS increases, base current iQbe of Q1 increases

causing the increase of current iQce. This topological stage N : 1 D1 LF R LF

ends at t = t9 when current iQce becomes equal to current iZCD Kd

CO1 CF IO

and gate-source capacitance starts discharging, as shown in LM ^

Rd1

Fig. 2(j). As voltage VGS decreases, switch S1 is turning off. RCO1 RCF

VO

Rd2

At t = t10, voltage VGS decreases to threshold voltage VTH of

switch S1 so that S1 is turned off. After switch S1 is turned off S1 Gvevo (s) G1

at t = t10, output capacitance COSS of switch S1 begins to VIN

charge so that voltage VDS begins to increase. This ^

VB RB

topological stage shown in Fig. 2(k) ends when voltage RS G3

^

iEA

VDS + VS ≈ VDS reaches VIN + NVO . At the same time, secondary RF CEA2

GEA(s)

rectifiers D1 and D2 start conducting and transistor Q1 turns Q1

CEA1

REA1

off, which completes a switching cycle. ^

ie ^

^

V =^

EA VKA

VQbe TL431

A. Small-Signal Model ^

i e = β iEA ^

^

Ve = (RS + RF )^i e

To achieve tight output voltage regulation and good

G2

dynamic performance while ensuring system stability,

compensation components CEA1, CEA2, and REA1 need to be Fig. 4 Simplified circuit diagram of self-oscillating flyback converter for

determined. However, the design optimization of the error small-signal modeling and analysis

0-7803-7405-3/02/$17.00 (C) 2002 IEEE

GV EAVO

(s) for the flyback converter operating at the boundary of

continuous conduction mode and discontinuous conduction

^

GVEVO (s)

VO mode (CCM/DCM), and is out of the scope of this paper.

However, the selection of zero-current-detect components

^ RZCD and CZCD, as well as the components related to the

Ve Kd

feedback loop, is generally not well understood, and is

TINNER

^

V1

therefore discussed below in detail.

+

G3 G2 G1 Σ _ GEA(s) A. Steady-State Considerations

^i ^i ^ ^

e EA VB VEA

To achieve good output voltage regulation during steady-

Fig. 5 Small-signal block diagram of self-oscillating flyback converter state operation, ramp voltage iS1RS summed with dc voltage

and where TINNER = G VeVo (s)G1G 2G 3 . ie(RF+RS) must fit within the “regulation window” throughout

the line and load range, as illustrated in Fig. 6. The upper

As can be seen from Eq. (1), transfer function G VEA VO (s)

limit of the regulation window is the cut-off voltage Vγ of

has a low frequency gain which is less than 1. Also, poles of transistor Q1, which is inherent to the transistor selected,

transfer function G VEA VO (s) , which are within the bandwidth whereas the lower limit of the regulation window is defined

of inner loop TINNER, are shifted to higher frequencies with by the full load current. To achieve output voltage regulation,

respect to power stage transfer function GVeVo(s), whereas the resistors RB, RS, and RF must be carefully selected to limit the

location of power stage transfer function zeroes are error current within this regulation window.

unaffected by the existence of the inner loop. Assuming that Maximum error current iemax occurs at minimum load, as

only the first pole, i.e., sp1, of power stage transfer function shown in Fig. 6. At minimum load, less energy is needed to

GVeVo(s), is within the bandwidth of inner loop TINNER (i.e., maintain the output voltage which is why the on time of

that second stage LC filter resonant frequency ωO > ωINNER, switch S1 is very short. Conversely, minimum error current

where TINNER(@ ωINNER) = 0 dB), transfer function G VEA VO (s) occurs at full load because a longer on time is needed to store

can be written in pole-zero form as the required energy. It should be noted that unlike the

G 1G 2 G 3 M dc (s s z1 + 1)(s s z2 + 1) standard PWM, whose on time is determined at the moment

G VEA VO (s) = ⋅

( )(

1 + G 1G 2 G 3 M dc s s *p1 + 1 s 2 ω2O + s QωO + 1 ) , (2) the ramp voltage reaches the control voltage, the on time of

this control circuit is determined once sufficient charge is

where M dc , s z1, s z 2 , s*p1, ωO , and Q are summarized in Table 1. removed from input capacitance CISS by transistor Q1, which

is turned on the moment base voltage VQbe reaches its

By defining transfer function G VEA VO (s) , the system is

intrinsic cut-off voltage Vγ.

reduced to a single loop system with loop gain The design constraints for the selection of the control

T1 = K d G EA (s)G VEA VO (s) . (3) circuit components for steady state operation are based on the

operating range of the circuit as well as on component

II. DESIGN GUIDELINES ratings. Specifically, cathode-anode voltage VKA and cathode

The design of the power stage of the self-oscillating current IK of error amplifier TL431 are limited to

flyback converter follows the well established design rules VREF<VKA<36 V and 1 mA<IK<100 mA. Voltage VKA can be

expressed as

TABLE 1

SMALL-SIGNAL TRANSFER FUNCTIONS

(s s z1 + 1)(s s z2 + 1) VIN 1

G VeVo (s) M dc

(s s p1 )(

+ 1 s 2 ω2O + s QωO + 1 ) Mdc −

2R S I O

sz1

CO1R Co1

1 Kr 1 IO N

− ωO −

VIN (1 + N VO VIN )

sz2 sp1 Kr

C F R CF C O1 + C F L F (1 C O1 + 1 C F )

C F + C O1 1 R d2

Q LF Kd

C FCO1 R Co1 + R CF + R lf + K r (R Co1R CF − L F (C O1 + C F )) R d1 + R d 2

G1 1 RB G2 β G3 R F + RS *

s p1 (1+G1G2G3Mdc)sp1

A s s zcomp1 + 1 1 1 C EA1 + 1 C EA 2

GEA(s) szcomp1 spcomp2

s s s pcomp 2 + 1 R EA1C EA1 R EA1

R d1 + R d 2

R d1R d 2 (C EA1 + C EA 2 )

A

0-7803-7405-3/02/$17.00 (C) 2002 IEEE

I1 TABLE 2

STEP-BY-STEP DESIGN PROCEDURE

Imax Step 1 Choose I max based on TL431 current limits

I1min 1 K

t Step 2 Determine i emax from Eq. 9

VQbe REGULATION

WINDOW Step 3 Determine RS from Eq. 6

Vγ

i emax RF i eminRF Step 4 Determine resistor RF from Eq. 7

t Step 5 Determine resistor RB from Eq. 5

S1 ON OFF

t Step 6 Check I min

K from Eq. 8 to ensure within TL431 limits

Fig. 6 Key control circuit waveforms of self-oscillating flyback converter Step 7 max

Check VKA using Eq. 4 at i K = i min

K

at minimum and maximum load current

VKA = VO − Vd − I K R B . (4) The role of capacitor CZCD is to block dc current during start-

Since at minimum load, current IK is maximum, as seen from up, allowing charge to be delivered from the input voltage

Fig. 5, where IK = ie/β, and, therefore, voltage VKA is at a through start-up resistor RST until switch S1 turns on for the

minimum. Resistor RB can be expressed as first time. Otherwise, capacitor CZCD merely delays the full

VO − Vd − VKA

min turn-on of switch S1 by increasing the length of time spent by

RB < max

. (5) switch S1 in the constant-current region, which is undesirable

IK

from a power conversion efficiency point of view. Therefore,

The selection of sense resistor RS is limited by its maximum it is recommended that capacitor CZCD be set ten times greater

power dissipation, which, if set to 0.1% of circuit’s maximum than input capacitance CISS. Since capacitors CZCD and CISS

input power PINmax , is form a voltage divider at the gate of switch S1, steps should

RS =

0.001 ⋅ PIN

max

. (6) be taken to clamp the gate voltage with zener diode ZD1 to

i pk D max 3

2

avoid exceeding the terminal voltage rating. The role of

S1

resistor RZCD is to limit power PZD1 dissipated by zener diode

The selection of resistor RF is limited at minimum load by ZD1,

maximum error current i emax , sense resistor RS, and cut-off R ZCD =

max

VIN (NS2 N P ) − VZD1 V . (11)

ZD1

voltage Vγ, PZD1

i emax (R F + R S ) ≤ Vγ , (7) Generally, voltage VO2 should be chosen high enough to

where resistor RF should be selected much greater than drive switch S1 into its ohmic region (e.g., VO2 = 12-V to 15-

resistor RS, i.e., RF >> RS. At full load, the selection of V is often sufficient).

resistors RF and RS are further limited by minimum error The value of start-up resistor RST is limited by its power

dissipation, since a high voltage (approximately equal to

current i emin and maximum switch current iSpk1 ,

input voltage VIN) is across it at all times. As a good rule of

i emin (R F + R S ) + iSpk1 (max) R S > Vγ , (8) thumb, its power dissipation should be less than 1% of the

where i pk (max)

S1 =V D max

IN

max

L f .min

M S

converters maximum output power.

Finally, error current ie is related to cathode current IK

through dc current transfer ratio β of optocoupler IC1, B. Compensation Calculations

ie = βIK . (9) Compensation components CEA1, CEA2, and REA1 of error

The design procedure for the selection of the control circuit amplifier TL431 are determined so that the control loop

components RF, RS, and RB for steady state operation can be achieves the desired regulation accuracy and dynamic

broken down to five design steps, summarized in Table 2. It response of the output voltage while maintaining an

should be noted that resistor RB, whose value also affects the acceptable phase margin (typically >45o) in the entire line

voltage loop dc gain, should be chosen as low as possible and load range. Generally, a good regulation accuracy and

while adhering to step 5 in order to maximize the loop gain. fast transient response requires that closed loop T1 has a high

Generally, a 20-Ω resistor serves as a good first iteration for dc gain and high bandwidth. Typically, a dc gain of 20 to 60

output voltage VO1 less than 35-V. Later, when system dB is sufficient for good regulation accuracy, whereas a

stability is considered, the value of resistor RB will be re- crossover frequency (fC) of less than one-fourth of the

evaluated. minimum switching frequency is usually designed for.

The design of components RA, CZCD, and RZCD can be The optimum compensation of the voltage control loop

determined independently from steps 1-7 of Table 2. For consists of an error amplifier with 2 poles and 1 zero. Error

example, the role of resistor RA is to reduce power loss PIC1 amplifier transfer function GEA(s), given in Table 1, can be

of the phototransistor within optocoupler IC1, where PIC1 is realized with capacitors CEA1 and CEA2 and resistor REA1. For

a desired crossover frequency fC of loop T1, the selection of

PIC1 = VCE i emax = (VO 2 − i emax R A − VQbe )i emax < device power rating (10)

compensation zero fzcomp1 should equal pole frequency f p*1 ,

0-7803-7405-3/02/$17.00 (C) 2002 IEEE

and the selection of compensation pole fpcomp2 should be III. SUMMARY

greater than 4fC, i.e., fzcomp1= f p*1 and fpcomp2 > 4fC. Using this

criteria, compensation components CEA1, CEA2, and REA1 are A detailed design-oriented steady-state analysis and a

then expressed as complete small-signal model of the self-oscillating flyback

C EA1 = 0.73 2πf C R d1 , (12) converter were presented. It was found that the steady-state

operation of the converter can be described by eleven

R EA1 = 1 C EA1s *p1 , (13) topological stages. Based on this analysis and the small-

signal model, a step-by-step design procedure for a feedback

C EA 2 = C EA1 10 .

(14)

control of the circuit was defined. This design procedure was

The small-signal block diagram model was verified by verified on a 5-V/2-A, off-line experimental circuit. The

comparing it to measurements made on a 5-V, 2-A self- measured and calculated loop gain of the experimental

oscillating flyback converter operating from a 400-V nominal converter are in a very good agreement.

dc voltage under full load conditions, as shown in Fig. 7. As

can be seen, both the measured and calculated Bode plots REFERENCES

show an excellent agreement up to one-tenth of the minimum

switching frequency, i.e., up to 4 kHz, where the minimum [1] K. Billings, “Switchmode power supply handbook”, New York, N.Y.:

switching frequency is equal to 40 kHz. Beyond one-tenth of McGraw-Hill, Inc., 1989.

the switching frequency, the compared phase plots are shown [2] L. Hayes and J. Spangler, “Pair of controller ics provide critical

to diverge, possibly due to a right-half-plane RHP zero which conduction switching power supply with voltage and current limiting”,

is not described by either the small-signal model presented in Power Conversion and Intelligent Motion (PCIM) Magazine, pp. 42-50,

Table 1, or by the small-signal model presented in [3]. Nov. 2000.

[3] J. Lempinen and T. Suntio, “Small-signal modeling for design of robust

Breaking the Loop at T1

variable-frequency flyback battery chargers for portable device

30 applications”, IEEE Applied Power Electronics Conf. (APEC) Proc., pp.

548-554, March 2001.

20

10

0

Gain [dB]

10

20

30

40

50

3 4 5

10 100 1 .10 1 .10 1 .10

frequency [Hz]

Calculated Gain

Measured Gain

Breaking the Loop at T1

200

150

100

phase [deg]

50

50

100

3 4 5

10 100 1 .10 1 .10 1 .10

frequency [Hz]

Calculated Phase

Measured Phase

Fig. 7 Calculated and measured Bode plots of loop gain T1 of off-line, 5-

V/ 2-A self-oscillating flyback converter

0-7803-7405-3/02/$17.00 (C) 2002 IEEE

You might also like

- Lab Report On ECE 210 Lab1Document6 pagesLab Report On ECE 210 Lab1Joanne Lai100% (1)

- Getting Over Overeating For TeensDocument186 pagesGetting Over Overeating For TeensNaren Dran100% (4)

- The Door of Everything by Ruby NelsonDocument35 pagesThe Door of Everything by Ruby NelsonNaren Dran100% (1)

- RelayDocument6 pagesRelayElaNo ratings yet

- SenseDocument2 pagesSenseSpidey Reddy100% (1)

- Manifestation Test PDFDocument10 pagesManifestation Test PDFNaren DranNo ratings yet

- HCNR200 Application NoteDocument10 pagesHCNR200 Application NoteLogan JohnsonNo ratings yet

- Study and Design, Simulation of PWM Based Buck Converter For Low Power ApplicationDocument17 pagesStudy and Design, Simulation of PWM Based Buck Converter For Low Power ApplicationIOSRjournalNo ratings yet

- Altivar 312 - ATV312H075N4Document4 pagesAltivar 312 - ATV312H075N4Jose Norton Doria100% (1)

- Power Rectifier ASIC ControllerDocument5 pagesPower Rectifier ASIC ControllerQuang TaNo ratings yet

- E300 Electronic OverloadDocument36 pagesE300 Electronic OverloadIsraelNo ratings yet

- TP 1800 DC-DC Converter For Hybrid Electric Vehicle and EV ArrowTimesDocument7 pagesTP 1800 DC-DC Converter For Hybrid Electric Vehicle and EV ArrowTimespapipapii100% (1)

- Basic ElectronicsDocument1 pageBasic Electronicsvishwanath81100% (1)

- Lab 4 Half Wave and Full WaveDocument8 pagesLab 4 Half Wave and Full WaveRashid Rind Rashid Rind100% (1)

- TESYS T ConfigDocument284 pagesTESYS T ConfigDiego Carlos GarciaNo ratings yet

- Voltage Source InverterDocument77 pagesVoltage Source InverterSaied Aly SalamahNo ratings yet

- Unit-03 - Part-2 FiltersDocument57 pagesUnit-03 - Part-2 Filtersr55088299No ratings yet

- Solid State RelayDocument4 pagesSolid State RelaymysisterandmeNo ratings yet

- Wiring Diagram For NPN and PNP 3 Wire Sensors With The D2-16ND3-2Document1 pageWiring Diagram For NPN and PNP 3 Wire Sensors With The D2-16ND3-2cool_rdNo ratings yet

- On Unified Power Quality Conditioner (Upqc) : A Technical SeminarDocument25 pagesOn Unified Power Quality Conditioner (Upqc) : A Technical SeminarnaveenNo ratings yet

- Communication Training ReportDocument33 pagesCommunication Training ReportkakagoNo ratings yet

- 5 Current Mode Control ModelingDocument12 pages5 Current Mode Control ModelingzmrbillNo ratings yet

- 16X2 LCD Basics:: LCD Pin Description: Pin No Symbol I/O DescriptionDocument33 pages16X2 LCD Basics:: LCD Pin Description: Pin No Symbol I/O DescriptionvaralakshmikrNo ratings yet

- Generating 50Hz PWM Using PIC16F877ADocument2 pagesGenerating 50Hz PWM Using PIC16F877AZarko DacevicNo ratings yet

- First Course of Programmable Logic Controllers PLCS: Abdelbary Center For Computer Training and Technical StudiesDocument116 pagesFirst Course of Programmable Logic Controllers PLCS: Abdelbary Center For Computer Training and Technical Studieswapij51282100% (1)

- Life Cycle Testing of Electrical Loads by Down Counter: AbstractDocument4 pagesLife Cycle Testing of Electrical Loads by Down Counter: AbstractTRIAD TECHNO SERVICESNo ratings yet

- Design and Micro Controller Implementation of A Three Phase SCR Power ConverterDocument8 pagesDesign and Micro Controller Implementation of A Three Phase SCR Power ConverterIsmael Ochoa JimenezNo ratings yet

- Experiment No.02 To Observe The Characteristics of A Half Wave RectifierDocument4 pagesExperiment No.02 To Observe The Characteristics of A Half Wave RectifierWaqas MughalNo ratings yet

- Wiring Diagram For NPN and PNP 4 Wire Sensors With The D2-16ND3-2Document1 pageWiring Diagram For NPN and PNP 4 Wire Sensors With The D2-16ND3-2Undibal Alejandro RivasNo ratings yet

- JFET and MOSFETDocument20 pagesJFET and MOSFETmbkfet100% (1)

- Presentation On UPFC ControllerDocument18 pagesPresentation On UPFC ControllerTesfahun GirmaNo ratings yet

- LC5296 LC5296-H 5006RN LC5248E User Manual PDFDocument36 pagesLC5296 LC5296-H 5006RN LC5248E User Manual PDFPankaj MauryaNo ratings yet

- Transistor Tutorial About Bipolar and FET TransistorsDocument4 pagesTransistor Tutorial About Bipolar and FET TransistorslosmilzoNo ratings yet

- A Novel ZVS-ZCS Bi-Directional Flyback DC-DCDocument6 pagesA Novel ZVS-ZCS Bi-Directional Flyback DC-DCArceu CamposNo ratings yet

- Design of Single Phase H-Bridge Multilevel Inverter Using Microcontroller Atmel 89c51Document52 pagesDesign of Single Phase H-Bridge Multilevel Inverter Using Microcontroller Atmel 89c51Sabir VeNo ratings yet

- Industrial Electric RelayDocument26 pagesIndustrial Electric Relaysyed muazzam shah putraNo ratings yet

- SectionalizersDocument30 pagesSectionalizersNoel DegonesNo ratings yet

- CUK Converter Using LM2611 PDFDocument65 pagesCUK Converter Using LM2611 PDFrijilpoothadiNo ratings yet

- Banasthali University: (Programmable Logiccontroller)Document21 pagesBanasthali University: (Programmable Logiccontroller)goblockuNo ratings yet

- Eec 225Document15 pagesEec 225Ezekiel Iyamu100% (1)

- Exp 8 Buck ConverterDocument7 pagesExp 8 Buck Converterusmpowerlab50% (2)

- Power Electronics Lab ManualDocument68 pagesPower Electronics Lab ManualJonathan727No ratings yet

- 1992 - Performance Characterization of A High-Power Dual Active Bridge DC-To-DC Converter - KheraluwalaDocument8 pages1992 - Performance Characterization of A High-Power Dual Active Bridge DC-To-DC Converter - Kheraluwalahafizabu123No ratings yet

- Quiz MasterDocument25 pagesQuiz MasterTeja DharmaNo ratings yet

- Motor Control PanelDocument2 pagesMotor Control PanelKhairel RiezzalNo ratings yet

- Operation of DC/DC Converter For Hybrid Electric Vehicle: Atul Kumar and Prerna GaurDocument6 pagesOperation of DC/DC Converter For Hybrid Electric Vehicle: Atul Kumar and Prerna GaurAhana MalhotraNo ratings yet

- B501 Series User Manual: Sensorless Current Vector Frequency InverterDocument136 pagesB501 Series User Manual: Sensorless Current Vector Frequency InverterkalepohNo ratings yet

- Combine TRDocument8 pagesCombine TRAchmad ZulkifliNo ratings yet

- Chapter 15old PDFDocument53 pagesChapter 15old PDFAbderrahmane WardiNo ratings yet

- Welding Harmonics PDFDocument8 pagesWelding Harmonics PDFYouwan LeeNo ratings yet

- Silicon Chip Online - Build A Water Level IndicatorDocument7 pagesSilicon Chip Online - Build A Water Level Indicatoredeva36No ratings yet

- Application of Power Diode in Power ElectronicsDocument18 pagesApplication of Power Diode in Power ElectronicsSahale Shera Lutse 18BEE0376No ratings yet

- Rectifier - 1 Half-Wave Rectification - 2 Full-Wave Rectification - Peak Loss - The Full-Wave Bridge - RectifierDocument9 pagesRectifier - 1 Half-Wave Rectification - 2 Full-Wave Rectification - Peak Loss - The Full-Wave Bridge - Rectifierysn_usmaniNo ratings yet

- Up 2210 R PDFDocument18 pagesUp 2210 R PDFkggganiNo ratings yet

- AQ3485Y ManualDocument15 pagesAQ3485Y ManualVu SonNo ratings yet

- Eee-Vi-Power System Analysis and Stability (10ee61) - Notes PDFDocument119 pagesEee-Vi-Power System Analysis and Stability (10ee61) - Notes PDFLatisha CarterNo ratings yet

- Electrical Overstress (EOS): Devices, Circuits and SystemsFrom EverandElectrical Overstress (EOS): Devices, Circuits and SystemsNo ratings yet

- Power Transformer Online Monitoring Using Electromagnetic WavesFrom EverandPower Transformer Online Monitoring Using Electromagnetic WavesNo ratings yet

- 100318interview Robert Thurman PDFDocument15 pages100318interview Robert Thurman PDFNaren DranNo ratings yet

- Early Ideas About Motion Predictions of Aristotle's TheoryDocument6 pagesEarly Ideas About Motion Predictions of Aristotle's TheoryNaren DranNo ratings yet

- Banks CMD HO & Tag LineDocument1 pageBanks CMD HO & Tag LineNaren DranNo ratings yet

- RulesBook PDFDocument70 pagesRulesBook PDFNaren DranNo ratings yet

- Intuitiveeating 0811 PDFDocument13 pagesIntuitiveeating 0811 PDFNaren Dran100% (1)

- He Art of Virtue: Benjamin Franklin (1706-90) - He Was A Writer, A Newspaper Editor, A Printer and ADocument4 pagesHe Art of Virtue: Benjamin Franklin (1706-90) - He Was A Writer, A Newspaper Editor, A Printer and ANaren DranNo ratings yet

- Mock 05Document127 pagesMock 05Naren DranNo ratings yet

- © Pinch Me Living 2012Document52 pages© Pinch Me Living 2012Naren DranNo ratings yet

- Call 38001 38909Document1 pageCall 38001 38909Naren DranNo ratings yet

- Early Ideas About Motion Predictions of Aristotle's TheoryDocument6 pagesEarly Ideas About Motion Predictions of Aristotle's TheoryNaren DranNo ratings yet

- Solutions For 50 Aptitude Questions On Profit and Loss QuestionsDocument16 pagesSolutions For 50 Aptitude Questions On Profit and Loss QuestionsNaren Dran100% (1)

- FFRC Advertisement Post 10 01 2018 PDFDocument1 pageFFRC Advertisement Post 10 01 2018 PDFNaren DranNo ratings yet

- Celibacy and Religious TraditionsDocument2 pagesCelibacy and Religious TraditionsNaren DranNo ratings yet

- Bonding With God: Swami Dayananda SaraswatiDocument9 pagesBonding With God: Swami Dayananda SaraswatiNaren DranNo ratings yet

- Surrender in Shadanga - Yoga PDFDocument3 pagesSurrender in Shadanga - Yoga PDFNaren DranNo ratings yet

- A Complaint Free World PDFDocument6 pagesA Complaint Free World PDFNaren DranNo ratings yet

- ELEN 303 Mobile Phone DetectorDocument8 pagesELEN 303 Mobile Phone DetectorMylavarapu SriprithamNo ratings yet

- HGTG7N60A4D, HGTP7N60A4D, HGT1S7N60A4DS: 600V, SMPS Series N-Channel IGBT With Anti-Parallel Hyperfast Diode FeaturesDocument9 pagesHGTG7N60A4D, HGTP7N60A4D, HGT1S7N60A4DS: 600V, SMPS Series N-Channel IGBT With Anti-Parallel Hyperfast Diode FeaturesJarden VegaNo ratings yet

- Electronica DesingDocument48 pagesElectronica DesingEmer nelsonNo ratings yet

- Project..... Thesis of Brake Failure Indicator SystemDocument52 pagesProject..... Thesis of Brake Failure Indicator SystemGurukeerthana Nagasamy88% (8)

- VTH Instability of MOSFETs With Advanced Gate Dielectrics (PHD Thesis)Document150 pagesVTH Instability of MOSFETs With Advanced Gate Dielectrics (PHD Thesis)shenchen100% (2)

- Amit INDICONDocument6 pagesAmit INDICONSonam RewariNo ratings yet

- A High Speed, Low Voltage To High Voltage Level Shifter in Standard 1.2V 0.13 M CmosDocument4 pagesA High Speed, Low Voltage To High Voltage Level Shifter in Standard 1.2V 0.13 M CmosaramshishmanyanNo ratings yet

- Temperature Monitor and Control Using Lm35Document2 pagesTemperature Monitor and Control Using Lm35Harsha0% (1)

- IDC 3321703 All Co 75 MCQDocument18 pagesIDC 3321703 All Co 75 MCQjigarNo ratings yet

- SAR-66 Amd2Document92 pagesSAR-66 Amd2Tan Lian KiatNo ratings yet

- CT208 (Anglais)Document30 pagesCT208 (Anglais)fgfNo ratings yet

- AnalogEl 1 BTJDocument33 pagesAnalogEl 1 BTJAlbert GenceNo ratings yet

- M. Tech. Mircroelectronics and VLSI DesignDocument27 pagesM. Tech. Mircroelectronics and VLSI DesignSvraghava SripathiNo ratings yet

- Elect SylDocument87 pagesElect SylDeepak KumarNo ratings yet

- Semiconductor TransistorDocument526 pagesSemiconductor TransistorAkhmad Reza FathanNo ratings yet

- CH 8Document38 pagesCH 8mugammad wasimNo ratings yet

- Syllabus Computer Science (3rd-8th) SemDocument57 pagesSyllabus Computer Science (3rd-8th) SemAsim Arunava Sahoo100% (2)

- Esab Arc4000i Tig4000i Mig4000iDocument78 pagesEsab Arc4000i Tig4000i Mig4000iliviucatalinNo ratings yet

- Effect of Globalisation On World WarslDocument18 pagesEffect of Globalisation On World WarslShrayan BarmanNo ratings yet

- Transistors Notes 4Document13 pagesTransistors Notes 4Anil Sai100% (1)

- SUper Perc EleXDocument18 pagesSUper Perc EleXCharles Adrian CNo ratings yet

- Application Note: @hitachiDocument9 pagesApplication Note: @hitachi김광호No ratings yet

- D ME Parts II-&-IIIDocument79 pagesD ME Parts II-&-IIIprasenjitsayantanNo ratings yet

- Modul Prak Elka 1Document12 pagesModul Prak Elka 1izhasepdianti123No ratings yet

- Electronics Mod 4 Quarter 2Document2 pagesElectronics Mod 4 Quarter 2Aldritz Peralta alagarmoNo ratings yet

- Electronics Circuits Analysis and Design: Prepared By: Engr. Maurine C. Panergo AY 2020-2021Document149 pagesElectronics Circuits Analysis and Design: Prepared By: Engr. Maurine C. Panergo AY 2020-2021MARINELA CademiaNo ratings yet

- Nmos Pmos Char PDFDocument4 pagesNmos Pmos Char PDFSpidey ReddyNo ratings yet

- Pic Programmer by Myke PredkoDocument10 pagesPic Programmer by Myke PredkoAnonymous HNCgfojJC0% (1)

- Led LCD TV: Service ManualDocument37 pagesLed LCD TV: Service ManualOvi DiuNo ratings yet

- European Type Designation Code SystemDocument16 pagesEuropean Type Designation Code Systemsarantapodarusa4009No ratings yet