Professional Documents

Culture Documents

Features: EL5202, EL5203

Uploaded by

Евгений ИвановOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Features: EL5202, EL5203

Uploaded by

Евгений ИвановCopyright:

Available Formats

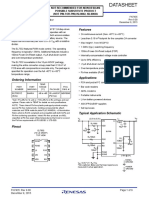

DATASHEET

EL5202, EL5203 FN7331

400MHz Slew Enhanced VFAs Rev 9.00

January 17, 2014

The EL5202 and EL5203 are dual, high-speed VFAs based on a

CFA architecture. This gives the typical high slew rate benefits

Features

of a CFA family along with the stability and ease of use • Operates off 3V, 5V, or ±5V supplies

associated with the VFA type architecture. With slew rates of • Power-down to 13µA (EL5202)

3500V/µs, these devices enable the use of voltage feedback

• -3dB bandwidth = 400MHz

amplifiers in a space where the only alternative has been

current feedback amplifiers. This family also includes single, • ±0.1dB bandwidth = 35MHz

dual, and triple versions with 750MHz bandwidths; please see • Low supply current = 5mA per amplifier

the EL5104 through EL5304 data sheet for details.

• Slew rate = 3500V/µs

Both devices operate on single 5V or ±5V supplies from

• Low offset voltage = 5mV max

minimum supply current. The EL5202 also features an output

enable function, which can be used to put the output in to a • Output current = 150mA

high-impedance mode. This allows the outputs of multiple • AVOL = 2000

amplifiers to be tied together for use in multiplexing

• Differential gain/phase = 0.01%/0.01°

applications.

• Pb-free (RoHS compliant)

Typical applications for these families include cable driving,

filtering, A/D and D/A buffering, multiplexing and summing

within video, communications, and instrumentation designs.

Applications

• Video amplifiers

• PCMCIA applications

• A/D drivers

• Line drivers

• Portable computers

• High speed communications

• RGB applications

• Broadcast equipment

• Active filtering

FN7331 Rev 9.00 Page 1 of 14

January 17, 2014

EL5202, EL5203

Ordering Information

PART NUMBER TEMP RANGE PACKAGE PKG

(Note 3) PART MARKING (°C) (Pb-free) DWG. #

EL5202IYZ (Note 2) BAAAD -40 to +85 10 Ld MSOP (3.0mm) M10.118A

EL5202IYZ-T7 (Notes 1, 2) BAAAD -40 to +85 10 Ld MSOP (3.0mm) M10.118A

EL5202IYZ-T13 (Notes 1, 2) BAAAD -40 to +85 10 Ld MSOP (3.0mm) M10.118A

EL5203ISZ (Note 2) 5203ISZ -40 to +85 8 Ld SOIC (150 mil) M8.15E

EL5203ISZ-T7 (Notes 1, 2) 5203ISZ -40 to +85 8 Ld SOIC (150 mil) M8.15E

EL5203ISZ-T13 (Notes 1, 2) 5203ISZ -40 to +85 8 Ld SOIC (150 mil) M8.15E

EL5203IYZ (Note 2) BAAAE -40 to +85 8 Ld MSOP (3.0mm) M8.118A

EL5203IYZ-T7 (Notes 1, 2) BAAAE -40 to +85 8 Ld MSOP (3.0mm) M8.118A

EL5203IYZ-T13 (Notes 1, 2) BAAAE -40 to +85 8 Ld MSOP (3.0mm) M8.118A

NOTES:

1. Please refer to TB347 for details on reel specifications.

2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte

tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil

Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

3. For Moisture Sensitivity Level (MSL), please see product information page for EL5202, EL5203 . For more information on MSL, please see tech brief

TB363.

Pin Configurations

EL5202 EL5203

(10 LD MSOP) (8 LD SOIC, MSOP)

TOP VIEW TOP VIEW

OUT 1 10 VS+ OUTA 1 8 VS+

IN- 2 9 OUT INA- 2 - 7 OUTB

-

+

+

IN+ 3 8 IN- INA+ 3 6 INB-

-

-

+

VS- 4 7 IN+ VS- 4 + 5 INB+

CE 5 6 CE

FN7331 Rev 9.00 Page 2 of 14

January 17, 2014

EL5202, EL5203

Absolute Maximum Ratings (TA = +25°C) Thermal Information

Supply Voltage between VS+ and VS-. . . . . . . . . . . . . . . . . . . . . . . . . . 13.2V Thermal Resistance (Typical) JA (°C/W) JC (°C/W)

Maximum Supply Slew Rate between VS+ and VS- . . . . . . . . . . . . . . 1V/µs 10 Ld MSOP Package (Notes 4, 5) . . . . . . . 160 75

Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±VS 8 Ld SOIC Package (Notes 4, 5) . . . . . . . . . 125 75

Differential Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±4V 8 Ld MSOP Package (Notes 4, 5) . . . . . . . . 170 80

Maximum Continuous Output Current . . . . . . . . . . . . . . . . . . . . . . . . . 80mA Storage Temperature Range. . . . . . . . . . . . . . . . . . . . . . . -65°C to +150°C

Maximum Current into IN+, IN-, CE . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±5mA Ambient Operating Temperature Range . . . . . . . . . . . . . . -40°C to +85°C

Operating Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . +150°C

Pb-Free Reflow Profile . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . see link below

http://www.intersil.com/pbfree/Pb-FreeReflow.asp

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product

reliability and result in failures not covered by warranty.

NOTES:

4. JA is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

5. For JC, the “case temp” location is taken at the package top center.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise

noted, all tests are at the specified temperature and are pulsed tests, therefore: TJ = TC = TA

DC Electrical SpecificationsMVS+ = +5V, VS- = -5V, TA = +25°C, RL = 500, VCE = 0V, Unless Otherwise Specified.

MIN MAX

PARAMETER DESCRIPTION CONDITIONS (Note 9) TYP (Note 9) UNIT

VOS Offset Voltage 1 5 mV

TCVOS Offset Voltage Temperature Coefficient Measured from TMIN to TMAX 10 µV/°C

IB Input Bias Current VIN = 0V -12 2 12 µA

IOS Input Offset Current VIN = 0V -8 1 8 µA

TCIOS Input Bias Current Temperature Coefficient Measured from TMIN to TMAX 50 nA/°C

PSRR Power Supply Rejection Ratio VS = ±4.75V to ±5.25V -70 -80 dB

CMRR Common Mode Rejection Ratio VCM = -3V to 3.0V -60 -80 dB

CMIR Common Mode Input Range Guaranteed by CMRR test -3 ±3.3 3 V

RIN Input Resistance Common mode 200 400 k

CIN Input Capacitance SO package 1 pF

IS,ON Supply Current - Enabled, Per Amplifier 4.6 5.2 5.8 mA

IS,OFF Supply Current - Shut-down, VS+ +1 +9 +25 µA

Per Amplifier

VS- -25 -13 -1 µA

AVOL Open Loop Gain VOUT = ±2.5V, RL = 1k to GND 58 66 dB

VOUT = ±2.5V, RL = 150 to GND 60 dB

VOUT Output Voltage Swing RL = 1k to GND ±3.5 ±3.9 V

RL = 150 to GND ±3.4 ±3.7 V

IOUT Output Current AV = 1, RL = 10 to 0V ±80 ±150 mA

VCE-ON CE Pin Voltage for Power-up (VS+) -5 (VS+) -3 V

VCE-OFF CE Pin Voltage for Shut-down (VS+) -1 VS+ V

ICE-ON CE Pin Current - Enabled CE = 0V -1 0 +1 µA

ICE-OFF CE Pin Current - Disabled CE = +5V 1 14 25 µA

FN7331 Rev 9.00 Page 3 of 14

January 17, 2014

EL5202, EL5203

Closed Loop AC Electrical Specifications VS+ = +5V, VS- = -5V, TA = +25°C, VCE = 0V, AV = +1, RF = 0, RL = 150 to GND,

Unless Otherwise Specified. (Note 6)

MIN MAX

PARAMETER DESCRIPTION CONDITIONS (Note 9) TYP (Note 9) UNIT

BW -3dB Bandwidth (VOUT = 400mVP-P) AV = 1, RF = 0 400 MHz

SR Slew Rate AV = +2, RL = 100, VOUT = -3V to +3V 1100 2200 5000 V/µs

RL = 500, VOUT = -3V to +3V 4000 V/µs

tR,tF Rise Time, Fall Time ±0.1V step 2.8 ns

OS Overshoot ±0.1V step 10 %

tS 0.1% Settling Time VS = ±5V, RL = 500, AV = 1, VOUT = ±3V 20 ns

dG Differential Gain (Note 7) AV = 2, RF = 1k 0.01 %

dP Differential Phase (Note 7) AV = 2, RF = 1k 0.01 °

eN Input Noise Voltage f = 10kHz 12 nV/Hz

iN Input Noise Current f = 10kHz 11 pA/Hz

tDIS Disable Time (Note 8) 50 ns

tEN Enable Time (Note 8) 25 ns

NOTES:

6. All AC tests are performed on a “warmed up” part, except slew rate, which is pulse tested.

7. Standard NTSC signal = 286mVP-P, f = 3.58MHz, as VIN is swept from 0.6V to 1.314V.RL is DC coupled.

8. Disable/Enable time is defined as the time from when the logic signal is applied to the CE pin to when the supply current has reached half its final

value.

9. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

FN7331 Rev 9.00 Page 4 of 14

January 17, 2014

EL5202, EL5203

Typical Performance Curves

5 240

VS = ±5V VS = ±5V

4 AV = +1 180 AV = +1

RF = 0 RF = 0

NORMALIZED GAIN (dB)

3

RL = 500 120 RL = 500

2 CL = +3.3pF CL = +3.3pF

60

PHASE (°)

1

0 0

-1 -60

-2

-120

-3

-180

-4 -3dB BW @ 438MHz

-5 -240

0.1M 1M 10M 100M 1G 0.1M 1M 10M 100M 1G

FREQUENCY (Hz) FREQUENCY (Hz)

FIGURE 1. GAIN vs FREQUENCY (-3dB BANDWIDTH) FIGURE 2. PHASE vs FREQUENCY

0.5 70

VS = ±5V

VS = ±5V

0.4 RL = 500

AV = +1 GAIN = 40dB or 100

NORMALIZED GAIN (dB)

0.3 RF = 0 60 FREQUENCY = 1.64 MHz

RL = 500 GAIN BW PRODUCT =

0.2 0.1dB BW @ 35MHz

CL = +3.3pF 1.64 x 100 = 164MHz

GAIN (dB)

0.1 50

0

-0.1 40

-0.2

-0.3 30

-0.4

-0.5 20

1M 10M 100M 0.1M 1M 10M 100M

FREQUENCY (Hz) FREQUENCY (Hz)

FIGURE 3. 0.1dB BANDWIDTH FIGURE 4. GAIN BANDWIDTH PRODUCT

300 5

GAIN-BANDWIDTH PRODUCT (MHz)

RL = 500 VS = ±5V

4 RL = 500

CL = +3.3pF AV = +2

NORMALIZED GAIN (dB)

250 3

RF = RG = 400

2

AV = +1

200 1 RF = 0

0

150 -1

-2

100 -3 AV = +5

RF = 1.6k, RG = 400

-4

50 -5

2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5 6.0 0.1M 1M 10M 100M 1G

SUPPLY VOLTAGES (±V) FREQUENCY (Hz)

FIGURE 5. GAIN BANDWIDTH PRODUCT vs SUPPLY VOLTAGES FIGURE 6. GAIN vs FREQUENCY FOR VARIOUS +AV

FN7331 Rev 9.00 Page 5 of 14

January 17, 2014

EL5202, EL5203

Typical Performance Curves (Continued)

5 5

AV = +1 VS = ±5V

4 4

RF = 0 AV = +1

NORMALIZED GAIN (dB)

NORMALIZED GAIN (dB)

3 RL = 500 3 RF = 0

RL = 1k

CL = +3.3pF CL = +3.3pF RL = 500

2 2

1 1

0 0

-1 VS = ±6 -1

-2 VS = ±5V -2 RL = 150

VS = ±4V

-3 -3 RL = 75

VS = ±3V

-4 -4

VS = ±2.5V RL = 50

-5 -5

0.1M 1M 10M 100M 1G 0.1M 1M 10M 100M 1G

FREQUENCY (Hz) FREQUENCY (Hz)

FIGURE 7. GAIN vs FREQUENCY FOR VARIOUS ±VS FIGURE 8. GAIN vs FREQUENCY FOR VARIOUS

RLOAD (AV = +1)

5 5

VS = ±5V VS = ±5V

4 4

AV = +2 AV = +5

NORMALIZED GAIN (dB)

3 RF = 402

NORMALIZED GAIN (dB)

3 RF = 402

CL = +3.9pF RL = 500 CL = +3.9pF

2 2 RL = 500

1 RL = 1k

1

0 RL = 1k

0

-1 -1

-2 RL = 50

-2 RL = 50

-3 RL = 70

-3

RL = 75

-4 RL = 150 -4

RL = 150

-5 -5

0.1M 1M 10M 100M 1G 0.1M 1M 10M 100M

FREQUENCY (Hz) FREQUENCY (Hz)

FIGURE 9. GAIN vs FREQUENCY FOR VARIOUS FIGURE 10. GAIN vs FREQUENCY FOR VARIOUS

RLOAD (AV = +2) RLOAD (AV = +5)

5 5

VS = ±5V VS = ±5V CL = 47pF

4 CL = 27pF 4 CL = 33pF

AV = +1 CL = 15pF AV = +2

RF = 0 RF = 400

NORMALIZED GAIN (dB)

NORMALIZED GAIN (dB)

3 3 CL = 18pF

RL = 500 RL = 500

2 2

CL = 8.2pF

1 1

0 0

-1 -1

-2 CL = 3.3pF -2 CL = 8.2pF

-3 -3

CL = 0pF CL = 0pF

-4 -4

-5 -5

0.1M 1M 10M 100M 1G 0.1M 1M 10M 100M 1G

FREQUENCY (Hz) FREQUENCY (Hz)

FIGURE 11. GAIN vs FREQUENCY FOR VARIOUS FIGURE 12. GAIN vs FREQUENCY FOR VARIOUS

CLOAD (AV = +1) CLOAD (AV = +2)

FN7331 Rev 9.00 Page 6 of 14

January 17, 2014

EL5202, EL5203

Typical Performance Curves (Continued)

5 5

VS = ±5V CL = 220pF VS = ±5V RF = 150

4 AV = +5 CL = 150pF 4 AV = +1 RF = 100

RF = 400 RL = 500

NORMALIZED GAIN (dB)

NORMALIZED GAIN (dB)

CL = 100pF 3

RL = 500 CL = +3pF

2 2

1 1

0 0

-1 -1

RF = 50

-2 CL = 56pF -2 RF = 25

-3 -3 RF = 0

-4 CL = 0pF -4

-5 -5

0.1M 1M 10M 100M 0.1M 1M 10M 100M 1G

FREQUENCY (Hz) FREQUENCY (Hz)

FIGURE 13. GAIN vs FREQUENCY FOR VARIOUS FIGURE 14. GAIN vs FREQUENCY FOR VARIOUS RF (AV = +1)

CLOAD (AV = +5)

5 5

VS = ±5V VS = ±5V

4 AV = +2 RF = 1.0k 4 AV = +5

RL = 500 RL = 500

NORMALIZED GAIN (dB)

3 3

NORMALIZED GAIN (dB)

RF = 680 RF = 4k

CL = +8pF CL = +12pF

2 2 RF = 2k

1 1

0 0

-1 -1 RF = 100

RF = 402

-2 -2 RF = 1k

-3 RF = 274 -3

RF = 402

-4 -4

RF = 100

-5 -5

0.1M 1M 10M 100M 1G 0.1M 1M 10M 100M

FREQUENCY (MHz) FREQUENCY (Hz)

FIGURE 15. GAIN vs FREQUENCY FOR VARIOUS RF (AV = +2) FIGURE 16. GAIN vs FREQUENCY FOR VARIOUS RF (AV = +5)

5 5

VS = ±5V CIN = 4.7pF

4 CIN = 3.3pF 4

VS = ±5V CIN = 8.2pF CIN = 10pF

AV = +2 AV = +5

NORMALIZED GAIN (dB)

3 RF = RG = 402 CIN = 2.2pF RG = 402

NORMALIZED GAIN (dB)

3 CIN = 6.8pF

RL = 500 RF = 1600

2 2

CL= +8pF CL = +12pF

1 1

0 0

-1 -1

-2 -2 CIN = 0pF

CIN = 1pF

-3 -3 CIN = 4.7pF

CIN = 0pF

-4 -4

-5 -5

0.1M 1M 10M 100M 1G 0.1M 1M 10M 100M

FREQUENCY (Hz) FREQUENCY (Hz)

FIGURE 17. GAIN vs FREQUENCY FOR VARIOUS CIN(-) FIGURE 18. GAIN vs FREQUENCY FOR VARIOUS CIN(-)

(AV = +2) (AV = +5)

FN7331 Rev 9.00 Page 7 of 14

January 17, 2014

EL5202, EL5203

Typical Performance Curves (Continued)

80 -45

100 AV = +2

70 0 VS = ±5V

OUTPUT IMPEDANCE (Ω)

60 PHASE 45

10

50 90

GAIN (dB)

PHASE (°)

40 135

30 180 1

20 225

GAIN

10 270 0.1

0 315

-10 360

VS = ±5V 0.01

-20 405

10 100 1k 10k 100k 1M 10M 100M 1G 10k 100k 1M 10M 100M

FREQUENCY (Hz) FREQUENCY (Hz)

FIGURE 19. OPEN LOOP GAIN AND PHASE vs FREQUENCY FIGURE 20. OUTPUT IMPEDANCE vs FREQUENCY

-10 10

AV = +5 AV = +1

-20 VS = ±5V 0 VS = ±5V

-30 -10

-40 -20

CMRR (dB)

-50 PSRR (dB) -30

-60 -40

-70 -50

-80 -60

-70 +PSRR

-90

-100 -80

-PSRR

-110 -90

1k 10k 100k 1M 10M 100M 500M 1k 10k 100k 1M 10M 100M 500M

FREQUENCY (Hz) FREQUENCY (Hz)

FIGURE 21. CMRR vs FREQUENCY FIGURE 22. PSRR vs FREQUENCY

MAX OUTPUT VOLTAGE SWING (VP-P)

10 30

9 25 VS = ±5V

RLOAD = 1k A = +1

20 RV = 0

8 F

15 RL = 500

GROUP DELAY (ns)

7

10

6 5

5 0

4 -5

VS = ±5V -10

3

AV = +2 -15

2 RF = RG = 402 RLOAD = 150 -20

1 CL = 8pF -25

0 -30

0.1M 1M 10M 100M 1G 0.1M 1M 10M 100M 1G

FREQUENCY (Hz) FREQUENCY (Hz)

FIGURE 23. MAX OUTPUT VOLTAGE SWING vs FREQUENCY FIGURE 24. GROUP DELAY vs FREQUENCY

FN7331 Rev 9.00 Page 8 of 14

January 17, 2014

EL5202, EL5203

Typical Performance Curves (Continued)

-10 10

VS = ±5V 0 VS = ±5V NOTE:

-20 OUTPUT TO INPUT

AV = +1 This was done on the

-10 AV = +1

-30 RF = 0 RF = 0 EL5203 (Dual Op-Amps)

-20 R = 500

CHIP DISABLED L

ISOLATION (dB)

-40 -30 BIN TO AOUT

GAIN (dB)

-40

-50 -50 AIN TO BOUT

-60 INPUT TO OUTPUT -60

-70

-70

-80

-80 -90

-100

-90

-110

-100 -120

0.1M 1M 10M 100M 1G 0.1M 1M 10M 100M 1G

FREQUENCY (Hz) FREQUENCY (Hz)

FIGURE 25. INPUT AND OUTPUT ISOLATION FIGURE 26. CHANNEL-TO-CHANNEL ISOLATION

-30 -20

VS = ±5V VS = ±5V

HARMONIC DISTORTION (dBc)

-40 AV = +1 -30 AV = +5

RF = 0 RG = 402 FIN = 10MHz

RL = 500 -40 RF = 1600

-50

CL = 3.3pF RL = 500

-50 CL = 12pF

-60 VOUT = 2VP-P T.H.D THD (dBc)

-60

-70

2nd HD -70

-80

-80

-90 FIN = 1MHz

3rd HD -90

-100 -100

0.1M 1M 10M 100M 0 1 2 3 4 5 6 7 8

FUNDAMENTAL FREQUENCY (Hz) OUTPUT VOLTAGES (VP-P)

FIGURE 27. HARMONIC DISTORTION vs FREQUENCY FIGURE 28. TOTAL HARMONIC DISTORTION vs OUTPUT VOLTAGES

6 6

VS = ±5V VS = ±5V

5 ENABLE SIGNAL AV = +1 5 AV = +1

RF = 0 RF = 0

4 4 R = 500

RL = 500 L

VOUT = 2VP-P 3 VOUT = 2VP-P

AMPLITUDE (V)

AMPLITUDE (V)

3 DISABLE SIGNAL

OUTPUT SIGNAL 2

2

OUTPUT SIGNAL

1 1

0 0

-1 -1

-2 -2

-3 -3

-600 -400 -200 0 200 400 600 800 1000 1200 1400 1600 -600 -400 -200 0 200 400 600 800 1000 1200 1400 1600

TIME (ns) TIME (ns)

FIGURE 29. TURN-ON TIME FIGURE 30. TURN-OFF TIME

FN7331 Rev 9.00 Page 9 of 14

January 17, 2014

EL5202, EL5203

Typical Performance Curves (Continued)

0.5

1000 VS = ±5V VS = ±5V RL = 500

0.4 AV = +1 CL = 3.3pF

NOISE VOLTAGE (nV/Hz)

RF = 0 VOUT = 400mV

0.3

AMPLITUDE (V)

100 0.2

0.1 tFALL = 0.9ns

0.0 tRISE = 0.923ns

10

-0.1

-0.2

1 -0.3

10 100 1k 10k 100k -20 0 20 40 60 80 100 120 140 160

FREQUENCY (Hz) TIME (ns)

FIGURE 31. EQUIVALENT NOISE VOLTAGE vs FREQUENCY FIGURE 32. SMALL SIGNAL STEP RESPONSE RISE AND FALL TIME

5 6.0

VS = ±5V RL = 500 AV = +1

4 AV = +5 CL = 5pF 5.8 RF = 0

RG = 25 VOUT = 4.0V RL = 500

SUPPLY CURRENT (mA)

5.6

3 CL = 3.3pF

5.4

AMPLITUDE (V)

2 5.2

1 tFALL = 1.167ns 5.0

0 4.8

tRISE = 1.243ns

4.6

-1

4.4 Please note that the curve showed

-2 positive Current. The negative current

4.2

was almost the same.

-3 4.0

-20 0 20 40 60 80 100 120 140 160 2.5 3.0 3.5 4.0 4.5 5.0 5.5 6.0

TIME (ns) SUPPLY VOLTAGE (V)

FIGURE 33. LARGE SIGNAL STEP RESPONSE RISE AND FALL TIME FIGURE 34. SUPPLY CURRENT vs SUPPLY VOLTAGE

10 50

VS = ±5V IM = (1) - (-77) = 78dB VS = ±5V

0 AV = +5 IP3 = 1+ (78/2) = 40dBm 45 AV = +5

-10 RF = 1600 40 RF = 1600

RL = 100 f2 = 1dBm RL = 100

AMPLITUDE (dBm)

-20 @ 1.05MHz

CL = 12pF 35 CL = 12pF

-30

IP3 (dBm)

30

-40 f1 = 1dBm

@ 0.95MHz 25

-50 2f2-f1 = -77.0dBm

2f1-f2 = -76.8dBm @ 1.15MHz 20

-60 @ 0.85MHz

-70 15

-80 10

-90 5

-100 0

0.8M 0.9M 1.0M 1.1M 1.2M 1M 10M 100M

FREQUENCY (Hz) FREQUENCY (Hz)

FIGURE 35. THIRD ORDER IMD INTERCEPT (IP3) FIGURE 36. THIRD ORDER IMD INTERCEPT vs FREQUENCY

FN7331 Rev 9.00 Page 10 of 14

January 17, 2014

EL5202, EL5203

© Copyright Intersil Americas LLC 2002-2014. All Rights Reserved.

All trademarks and registered trademarks are the property of their respective owners.

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted

in the quality certifications found at www.intersil.com/en/support/qualandreliability.html

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such

modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are

current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its

subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

FN7331 Rev 9.00 Page 11 of 14

January 17, 2014

EL5202, EL5203

Package Outline Drawing

M10.118A (JEDEC MO-187-BA)

10 LEAD MINI SMALL OUTLINE PLASTIC PACKAGE (MSOP)

Rev 0, 9/09

A

3.0 ± 0.1

0.25 CAB DETAIL "X"

10

1.10 Max

SIDE VIEW 2 0.18 ± 0.05

4.9 ± 0.15

3.0 ± 0.1

PIN# 1 ID B

1 2

0.95 BSC

0.5 BSC

TOP VIEW

Gauge

Plane

H 0.86 ± 0.09 0.25

SEATING PLANE 3°±3°

0.55 ± 0.15

0.10 ± 0.05

0.23 +0.07/ -0.08 0.10 C

0.08 C A B DETAIL "X"

SIDE VIEW 1

5.80

4.40

NOTES:

3.00

1. Dimensions are in millimeters.

2. Dimensioning and tolerancing conform to AMSE Y14.5m-1994.

0.50 3. Plastic or metal protrusions of 0.15mm max per side are not

included.

4. Plastic interlead protrusions of 0.25mm max per side are not

0.30 included.

1.40 5. Dimensions “D” and “E1” are measured at Datum Plane “H”.

TYPICAL RECOMMENDED LAND PATTERN 6. This replaces existing drawing # MDP0043 MSOP10L.

FN7331 Rev 9.00 Page 12 of 14

January 17, 2014

EL5202, EL5203

Package Outline Drawing

M8.118A

8 LEAD MINI SMALL OUTLINE PLASTIC PACKAGE (MSOP)

Rev 0, 9/09

A

3.0±0.1

8 0.25 CAB

4.9±0.15 DETAIL "X"

3.0±0.1

1.10 Max

PIN# 1 ID B

0.18 ± 0.05

SIDE VIEW 2

1 2

0.65 BSC

TOP VIEW

0.95 BSC

0.86±0.09

H GAUGE

PLANE

C 0.25

SEATING PLANE

0.33 +0.07/ -0.08 3°±3°

0.10 ± 0.05 0.10 C 0.55 ± 0.15

0.08 C A B

DETAIL "X"

SIDE VIEW 1

5.80 NOTES:

4.40

3.00 1. Dimensions are in millimeters.

2. Dimensioning and tolerancing conform to JEDEC MO-187-AA

and AMSE Y14.5m-1994.

3. Plastic or metal protrusions of 0.15mm max per side are not

0.65 included.

0.40 4. Plastic interlead protrusions of 0.25mm max per side are not

included.

1.40

5. Dimensions “D” and “E1” are measured at Datum Plane “H”.

TYPICAL RECOMMENDED LAND PATTERN

6. This replaces existing drawing # MDP0043 MSOP 8L.

FN7331 Rev 9.00 Page 13 of 14

January 17, 2014

EL5202, EL5203

Package Outline Drawing

M8.15E

8 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE

Rev 0, 08/09

4

4.90 ± 0.10 A

DETAIL "A" 0.22 ± 0.03

6.0 ± 0.20

3.90 ± 0.10

PIN NO.1

ID MARK

(0.35) x 45°

4° ± 4°

0.43 ± 0.076

1.27

0.25 M C A B

SIDE VIEW “B”

TOP VIEW

1.75 MAX

1.45 ± 0.1

0.25

GAUGE PLANE

C

0.175 ± 0.075 SEATING PLANE

0.10 C

SIDE VIEW “A

0.63 ±0.23

DETAIL "A"

(1.27) (0.60)

NOTES:

(1.50)

1. Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

2. Dimensioning and tolerancing conform to AMSE Y14.5m-1994.

(5.40) 3. Unless otherwise specified, tolerance : Decimal ± 0.05

4. Dimension does not include interlead flash or protrusions.

Interlead flash or protrusions shall not exceed 0.25mm per side.

5. The pin #1 identifier may be either a mold or mark feature.

6. Reference to JEDEC MS-012.

TYPICAL RECOMMENDED LAND PATTERN

FN7331 Rev 9.00 Page 14 of 14

January 17, 2014

You might also like

- EL5166, EL5167: FeaturesDocument16 pagesEL5166, EL5167: FeaturesЕвгений ИвановNo ratings yet

- Features: 12Mhz Rail-To-Rail Input-Output BufferDocument13 pagesFeatures: 12Mhz Rail-To-Rail Input-Output BufferЕвгений ИвановNo ratings yet

- REN El5172 DST 20220721Document15 pagesREN El5172 DST 20220721jpamericoNo ratings yet

- Features: High Supply Voltage 220Mhz Unity-Gain Stable Operational AmplifierDocument13 pagesFeatures: High Supply Voltage 220Mhz Unity-Gain Stable Operational AmplifiersdasfaNo ratings yet

- DG408, DG409: Single 8-Channel/Differential 4-Channel, CMOS Analog Multiplexers FeaturesDocument17 pagesDG408, DG409: Single 8-Channel/Differential 4-Channel, CMOS Analog Multiplexers FeaturesmikigabriNo ratings yet

- Features: Dual, Low Power CMOS Operational AmplifiersDocument9 pagesFeatures: Dual, Low Power CMOS Operational AmplifiersDibya DeyNo ratings yet

- Features: 600Khz/1.2Mhz PWM Step-Up RegulatorDocument12 pagesFeatures: 600Khz/1.2Mhz PWM Step-Up RegulatorЕвгений ИвановNo ratings yet

- Features: EL8170, EL8173Document14 pagesFeatures: EL8170, EL8173Евгений ИвановNo ratings yet

- El8100 01Document14 pagesEl8100 01Евгений ИвановNo ratings yet

- El 7104Document7 pagesEl 7104Oscar FernandezNo ratings yet

- Features: Ultra-Low Noise, Low Power, Wideband AmplifierDocument16 pagesFeatures: Ultra-Low Noise, Low Power, Wideband AmplifierЕвгений ИвановNo ratings yet

- OPA365Document33 pagesOPA365tinig64603No ratings yet

- Features: EL5160, EL5161, EL5260, EL5261, EL5360Document17 pagesFeatures: EL5160, EL5161, EL5260, EL5261, EL5360Евгений ИвановNo ratings yet

- DatasheetDocument12 pagesDatasheetAsad AhmedNo ratings yet

- EL8200, EL8201, EL8401: FeaturesDocument16 pagesEL8200, EL8201, EL8401: FeaturesЕвгений ИвановNo ratings yet

- 100V/2A Peak, Low Cost, High Frequency Half Bridge Driver FeaturesDocument13 pages100V/2A Peak, Low Cost, High Frequency Half Bridge Driver FeaturescarcavaNo ratings yet

- Linhkien QuangDocument20 pagesLinhkien QuangHiếuNo ratings yet

- HFBR 2506afzDocument7 pagesHFBR 2506afzMikel IglesiasNo ratings yet

- Features: High-Speed USB 2.0 (480Mbps) DPST Switch With Overvoltage Protection (OVP) and Dedicated Charger Port DetectionDocument17 pagesFeatures: High-Speed USB 2.0 (480Mbps) DPST Switch With Overvoltage Protection (OVP) and Dedicated Charger Port DetectionAlejha GNo ratings yet

- DS90LV031A 3-V LVDS Quad CMOS Differential Line Driver: 1 Features 3 DescriptionDocument26 pagesDS90LV031A 3-V LVDS Quad CMOS Differential Line Driver: 1 Features 3 Descriptionliai linNo ratings yet

- HF/VHF Power MOS Transistor: Important NoticeDocument19 pagesHF/VHF Power MOS Transistor: Important Noticegabriel souza silva soares coimbraNo ratings yet

- Opax340 Single-Supply, Rail-To-Rail Operational Amplifiers Microamplifier™ SeriesDocument43 pagesOpax340 Single-Supply, Rail-To-Rail Operational Amplifiers Microamplifier™ SerieslordgtyNo ratings yet

- Opax340 Single-Supply, Rail-To-Rail Operational Amplifiers Microamplifier™ SeriesDocument44 pagesOpax340 Single-Supply, Rail-To-Rail Operational Amplifiers Microamplifier™ Seriesjason bourneNo ratings yet

- Opa810 140-Mhz, Rail-To-Rail Input and Output, Fet-Input Operational AmplifierDocument50 pagesOpa810 140-Mhz, Rail-To-Rail Input and Output, Fet-Input Operational AmplifierPablo AllosiaNo ratings yet

- 6N135-136, HCNW135-136, HCPL-2502-0500-0501Document16 pages6N135-136, HCNW135-136, HCPL-2502-0500-0501robert_lascuNo ratings yet

- EL7532 fn7435Document8 pagesEL7532 fn7435csclzNo ratings yet

- Ref 5030Document38 pagesRef 5030dinhngock6No ratings yet

- lmv342 NDocument39 pageslmv342 NJuan CecconiNo ratings yet

- Broadband Fiber Optic CouplersDocument2 pagesBroadband Fiber Optic CouplersAndriiNo ratings yet

- Tps 65135Document28 pagesTps 65135Arthit SomrangNo ratings yet

- Adaptadores LC DatatronixDocument2 pagesAdaptadores LC DatatronixChristianNo ratings yet

- Features: 0.5Mhz, Low Supply Voltage, Low Input Current Bimos Operational AmplifierDocument5 pagesFeatures: 0.5Mhz, Low Supply Voltage, Low Input Current Bimos Operational AmplifierAlexandre Correa100% (1)

- VBMB - 002-1Document56 pagesVBMB - 002-1Seethalakshmi VNo ratings yet

- Opax350 High-Speed, Single-Supply, Rail-To-Rail Operational Amplifiers Microamplifier SeriesDocument43 pagesOpax350 High-Speed, Single-Supply, Rail-To-Rail Operational Amplifiers Microamplifier SeriesLuis J. Gonzalez LugoNo ratings yet

- OPAx350 AMPOPDocument42 pagesOPAx350 AMPOPBernardo AraújoNo ratings yet

- PROFIBUS DP Gateway Converts EncodersDocument4 pagesPROFIBUS DP Gateway Converts Encodersalpha1ahNo ratings yet

- Moxa Transio A52 A53 Series Datasheet v1.0 PDFDocument3 pagesMoxa Transio A52 A53 Series Datasheet v1.0 PDFleqaa abdNo ratings yet

- AP63200/AP63201/AP63203/AP63205: 3.8V To 32V Input, 2A Low Iq Synchronous Buck With Enhanced Emi ReductionDocument19 pagesAP63200/AP63201/AP63203/AP63205: 3.8V To 32V Input, 2A Low Iq Synchronous Buck With Enhanced Emi ReductionJonathan Da SilvaNo ratings yet

- RTL8019ASDocument12 pagesRTL8019ASgovemi7604No ratings yet

- 4.5-V To 65-V Input, Compact Bias Supply With Power Stage Reference Design For Igbt/Sic Gate DriversDocument44 pages4.5-V To 65-V Input, Compact Bias Supply With Power Stage Reference Design For Igbt/Sic Gate DriversDebasish MishraNo ratings yet

- MC33290Document12 pagesMC33290Harris RaoNo ratings yet

- Features: 110Mhz, High Slew Rate, High Output Current BufferDocument12 pagesFeatures: 110Mhz, High Slew Rate, High Output Current BufferPepe ChorizoNo ratings yet

- P542 CortecDocument6 pagesP542 CortecZeckrey JikurunNo ratings yet

- DVP-K870P K880P SMDocument87 pagesDVP-K870P K880P SMReginNo ratings yet

- Industrial Fiber Optic Components and Accessories: Selection GuideDocument8 pagesIndustrial Fiber Optic Components and Accessories: Selection Guideershivkumar2002No ratings yet

- Ca 3260Document4 pagesCa 3260Carlos TibussiNo ratings yet

- DMN3350LDW DiodesDocument7 pagesDMN3350LDW DiodesJuan NunesNo ratings yet

- Opa365 Q11Document22 pagesOpa365 Q11Victor HernandezNo ratings yet

- ISL6612, ISL6613: Advanced Synchronous Rectified Buck MOSFET Drivers With Protection FeaturesDocument12 pagesISL6612, ISL6613: Advanced Synchronous Rectified Buck MOSFET Drivers With Protection FeaturesAnonymous oyUAtpKNo ratings yet

- CA3450Document8 pagesCA3450MUHAMMAD SISWANTORONo ratings yet

- Icl7650s Cba-1zDocument13 pagesIcl7650s Cba-1zmarcodlcruz94No ratings yet

- OPA357 - RRIO AmpOpDocument28 pagesOPA357 - RRIO AmpOpClara FortesNo ratings yet

- A5191HRTNGEVBDocument21 pagesA5191HRTNGEVBAvaq SemiconductorNo ratings yet

- Opsis LD500Document16 pagesOpsis LD500IMTB MumbaiNo ratings yet

- DatasheetDocument21 pagesDatasheetKunal SononeNo ratings yet

- LSF010x 1/2/8 Channel Auto-Bidirectional Multi-Voltage Level Translator For Open-Drain and Push-Pull ApplicationsDocument40 pagesLSF010x 1/2/8 Channel Auto-Bidirectional Multi-Voltage Level Translator For Open-Drain and Push-Pull ApplicationsSankar SaroNo ratings yet

- LM4041 Precision Micropower Shunt Voltage Reference: 1 Features 3 DescriptionDocument34 pagesLM4041 Precision Micropower Shunt Voltage Reference: 1 Features 3 Descriptionalgnben1746No ratings yet

- OPA2810 Dual-Channel, 27-V, Rail-to-Rail Input/Output FET-Input Operational AmplifierDocument51 pagesOPA2810 Dual-Channel, 27-V, Rail-to-Rail Input/Output FET-Input Operational AmplifierYashodhan JaltareNo ratings yet

- HF/VHF Power MOS Transistor: Important NoticeDocument20 pagesHF/VHF Power MOS Transistor: Important Noticejolupeco44No ratings yet

- 1N5817Document3 pages1N5817Gallego OrtizNo ratings yet

- Backhoe 220 To 600 SeriesDocument3 pagesBackhoe 220 To 600 SeriesЕвгений ИвановNo ratings yet

- 216 Spare Part ListDocument21 pages216 Spare Part ListЕвгений ИвановNo ratings yet

- General Operation Instructions: Hydraulic High Pressure Water PumpsDocument14 pagesGeneral Operation Instructions: Hydraulic High Pressure Water PumpsEdwin MorenoNo ratings yet

- Schottky Barrier Diode: Dual Series Schottky Barrier Diode For Mixer and Detector 5V, 30ma, 0.69pF, CPDocument6 pagesSchottky Barrier Diode: Dual Series Schottky Barrier Diode For Mixer and Detector 5V, 30ma, 0.69pF, CPЕвгений ИвановNo ratings yet

- Horizontal Genlock, 8FSC: FeaturesDocument15 pagesHorizontal Genlock, 8FSC: FeaturesЕвгений ИвановNo ratings yet

- 1EDN7550 and 1EDN8550: Feature ListDocument21 pages1EDN7550 and 1EDN8550: Feature ListЕвгений ИвановNo ratings yet

- Mccsemi: 1N746 A Thru 1N759 ADocument3 pagesMccsemi: 1N746 A Thru 1N759 AЕвгений ИвановNo ratings yet

- 1N4728A - 1N4758A: Zener DiodesDocument4 pages1N4728A - 1N4758A: Zener DiodesЕвгений ИвановNo ratings yet

- EQCO30R5.D 3G/HD-SDI Video Cable EqualizerDocument24 pagesEQCO30R5.D 3G/HD-SDI Video Cable EqualizerЕвгений ИвановNo ratings yet

- 1°C Triple Temperature Sensor With Hotter of Two Zones: Product FeaturesDocument26 pages1°C Triple Temperature Sensor With Hotter of Two Zones: Product FeaturesЕвгений ИвановNo ratings yet

- Features: 600Khz/1.2Mhz PWM Step-Up RegulatorDocument12 pagesFeatures: 600Khz/1.2Mhz PWM Step-Up RegulatorЕвгений ИвановNo ratings yet

- 1°C Triple Smbus Sensor With Resistance Error Correction: Product FeaturesDocument3 pages1°C Triple Smbus Sensor With Resistance Error Correction: Product FeaturesЕвгений ИвановNo ratings yet

- Features: High Speed, Monolithic Pin DriverDocument9 pagesFeatures: High Speed, Monolithic Pin DriverЕвгений ИвановNo ratings yet

- Ev12aq600 PDSDocument57 pagesEv12aq600 PDSЕвгений ИвановNo ratings yet

- E523-81 Elmos DsDocument68 pagesE523-81 Elmos DsЕвгений ИвановNo ratings yet

- Multiple RPM-Based PWM Fan Controller For Five Fans: Product FeaturesDocument56 pagesMultiple RPM-Based PWM Fan Controller For Five Fans: Product FeaturesЕвгений ИвановNo ratings yet

- Features: Monolithic 2A Step-Down RegulatorDocument9 pagesFeatures: Monolithic 2A Step-Down RegulatorЕвгений ИвановNo ratings yet

- 40 Volt, 10 Amp Peak, High-Frequency, Integrated Laser Driver DescriptionDocument9 pages40 Volt, 10 Amp Peak, High-Frequency, Integrated Laser Driver DescriptionЕвгений ИвановNo ratings yet

- EMC6W201Document5 pagesEMC6W201Евгений ИвановNo ratings yet

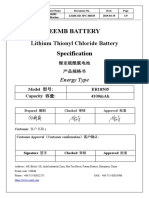

- Eemb Battery Specification: Lithium Thionyl Chloride BatteryDocument9 pagesEemb Battery Specification: Lithium Thionyl Chloride BatteryЕвгений ИвановNo ratings yet

- EPC2050 - Enhancement-Mode Power Transistor Preliminary Specification SheetDocument8 pagesEPC2050 - Enhancement-Mode Power Transistor Preliminary Specification SheetЕвгений ИвановNo ratings yet

- Features: Monolithic 4A DC/DC Step-Down RegulatorDocument14 pagesFeatures: Monolithic 4A DC/DC Step-Down RegulatorЕвгений ИвановNo ratings yet

- EMC2106Document106 pagesEMC2106Евгений ИвановNo ratings yet

- Features: Monolithic 350ma Step-Down RegulatorDocument10 pagesFeatures: Monolithic 350ma Step-Down RegulatorЕвгений ИвановNo ratings yet

- EPC2059 - Enhancement Mode Power Transistor: V, 170 V R, 9 mΩ I, 24 ADocument6 pagesEPC2059 - Enhancement Mode Power Transistor: V, 170 V R, 9 mΩ I, 24 AЕвгений ИвановNo ratings yet

- Features: Monolithic 600ma Step-Down Regulator With Low Quiescent CurrentDocument11 pagesFeatures: Monolithic 600ma Step-Down Regulator With Low Quiescent CurrentЕвгений ИвановNo ratings yet

- EQCO31R20Document34 pagesEQCO31R20Евгений ИвановNo ratings yet

- Monolithic Amplifier: Dc-4 GHZDocument21 pagesMonolithic Amplifier: Dc-4 GHZЕвгений ИвановNo ratings yet

- EMC6D102Document86 pagesEMC6D102Евгений ИвановNo ratings yet

- Henry FordDocument18 pagesHenry Fordsonabeta07No ratings yet

- Unit-II Inheritance and PointersDocument140 pagesUnit-II Inheritance and PointersAbhishekNo ratings yet

- Geotextile Its Application To Civil Engineering ODocument7 pagesGeotextile Its Application To Civil Engineering OezequilNo ratings yet

- Internship Report On: "Training and Development of Bengal Group of Industries."Document47 pagesInternship Report On: "Training and Development of Bengal Group of Industries."Lucy NguyenNo ratings yet

- AfghanistanLML OnlinDocument117 pagesAfghanistanLML Onlinعارف حسینNo ratings yet

- Feasibility ReportDocument10 pagesFeasibility ReportAdityaNo ratings yet

- Study of The Pre-Processing Impact in A Facial Recognition SystemDocument11 pagesStudy of The Pre-Processing Impact in A Facial Recognition Systemalmudena aguileraNo ratings yet

- Microprocessor 8086 Memory and ArchitectureDocument13 pagesMicroprocessor 8086 Memory and ArchitecturehrrameshhrNo ratings yet

- Menomonee Falls Express News 091413Document32 pagesMenomonee Falls Express News 091413Hometown Publications - Express NewsNo ratings yet

- S3 Unseen PracticeDocument7 pagesS3 Unseen PracticeTanush GoelNo ratings yet

- HOUSEKEEPING SESSION PLANDocument2 pagesHOUSEKEEPING SESSION PLANScarlette Beauty Enriquez100% (1)

- 2003 June Calc Paper 6 (H)Document20 pages2003 June Calc Paper 6 (H)abbasfazilNo ratings yet

- Lab Manual 2 PrintDocument17 pagesLab Manual 2 Printmonikandakumar ramachandranNo ratings yet

- TM 9-1651 Data Transmission System m3, January 1942Document78 pagesTM 9-1651 Data Transmission System m3, January 1942Advocate100% (1)

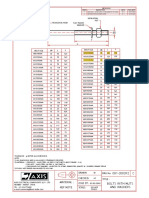

- Material: Ref Note: Rev # Description Appv. Rev DateDocument1 pageMaterial: Ref Note: Rev # Description Appv. Rev DateNimish TaterhNo ratings yet

- Caed102: Financial MarketsDocument2 pagesCaed102: Financial MarketsXytusNo ratings yet

- Handling Precautions: Butterfly Valves (Common To All Models)Document9 pagesHandling Precautions: Butterfly Valves (Common To All Models)xaaabbb_550464353No ratings yet

- Athus Souza - ResumeDocument2 pagesAthus Souza - ResumeArielBen-ShalomBarbosaNo ratings yet

- MCQ (Trigo)Document10 pagesMCQ (Trigo)RaghavNo ratings yet

- Sample Administrative Disicplinary CasesDocument13 pagesSample Administrative Disicplinary CasesWen DyNo ratings yet

- Uti MF v. Ito 345 Itr 71 - (2012) 019taxmann - Com00250 (Bom)Document8 pagesUti MF v. Ito 345 Itr 71 - (2012) 019taxmann - Com00250 (Bom)bharath289No ratings yet

- Bloodborne Pathogens Program: Western Oklahoma State College Employee Training HandbookDocument35 pagesBloodborne Pathogens Program: Western Oklahoma State College Employee Training HandbookKashaNo ratings yet

- United Nations Manual on Reimbursement for Peacekeeping EquipmentDocument250 pagesUnited Nations Manual on Reimbursement for Peacekeeping EquipmentChefe GaragemNo ratings yet

- Affidavit Defends Wife's InnocenceDocument6 pagesAffidavit Defends Wife's InnocenceGreggy LawNo ratings yet

- Rate of Grease Penetration of Flexible Barrier Materials (Rapid Method)Document3 pagesRate of Grease Penetration of Flexible Barrier Materials (Rapid Method)DanZel Dan100% (1)

- Column:C2 900X900: Basic Design ParametersDocument2 pagesColumn:C2 900X900: Basic Design ParametersAnonymous tBhJoH5wgMNo ratings yet

- 1081 Camid Vs Op DigestDocument2 pages1081 Camid Vs Op DigestLennart Reyes67% (3)

- Juno Gi BrochureDocument2 pagesJuno Gi BrochureJerry VagilidadNo ratings yet

- Baja2018 Unisa Team3 Design ReportDocument23 pagesBaja2018 Unisa Team3 Design ReportDaniel MabengoNo ratings yet

- 12.CEH Module 3 Assignment 3.1Document7 pages12.CEH Module 3 Assignment 3.1piyuhNo ratings yet