Professional Documents

Culture Documents

Features: Monolithic 600ma Step-Down Regulator With Low Quiescent Current

Uploaded by

Евгений ИвановOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Features: Monolithic 600ma Step-Down Regulator With Low Quiescent Current

Uploaded by

Евгений ИвановCopyright:

Available Formats

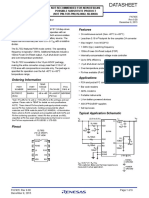

D FOR NEW DESIGN

S DATASHEET

NOT RECOMMENDE

UTE PRODUCT

POSSIBLE SUBSTIT

ISL9106

(NOT PIN-FOR-PIN)

EL7530 FN7434

Monolithic 600mA Step-Down Regulator with Low Quiescent Current Rev 6.00

July 12, 2006

The EL7530 is a synchronous, integrated FET 600mA step- Features

down regulator with internal compensation. It operates with an

input voltage range from 2.5V to 5.5V, which accommodates • Less than 0.18in2 footprint for the complete 600mA

converter

supplies of 3.3V, 5V, or a Li-Ion battery source. The output can

be externally set from 0.8V to VIN with a resistive divider. • Components on one side of PCB

The EL7530 features automatic PFM/PWM mode control, or • Max height 1.1mm MSOP10

PWM mode only. The PWM frequency is typically 1.4MHz • Power-Good (PG) output

and can be synchronized up to 12MHz. The typical no load

quiescent current is only 120µA. Additional features include • Internally-compensated voltage mode controller

a Power-Good output, <1µA shut-down current, short-circuit • Up to 95% efficiency

protection, and over-temperature protection.

• <1µA shut-down current

The EL7530 is available in the 10 Ld MSOP package,

• 120µA quiescent current

making the entire converter occupy less than 0.18n2 of PCB

area with components on one side only. The 10 Ld MSOP • Overcurrent and over-temperature protection

package is specified for operation over the full -40°C to • External synchronizable up to 12MHz

+85°C temperature range.

• Pb-free plus anneal available (RoHS compliant)

Ordering Information

PART TAPE & PKG. Applications

PART NUMBER MARKING REEL PACKAGE DWG. #

• PDA and pocket PC computers

EL7530IY BYAAA - 10 Ld MSOP MDP0043

• Bar code readers

EL7530IY-T7 BYAAA 7” 10 Ld MSOP MDP0043

EL7530IY-T13 BYAAA 13” 10 Ld MSOP MDP0043 • Cellular phones

EL7530IYZ BAADA - 10 Ld MSOP MDP0043 • Portable test equipment

(Note) (Pb-free)

• Li-Ion battery powered devices

EL7530IYZ-T7 BAADA 7” 10 Ld MSOP MDP0043

(Note) (Pb-free) • Small form factor (SFP) modules

EL7530IYZ-T13 BAADA 13” 10 Ld MSOP MDP0043

(Note) (Pb-free) Typical Application Diagram

NOTE: Intersil Pb-free plus anneal products employ special Pb-free EL7530

material sets; molding compounds/die attach materials and 100% TOP VIEW

matte tin plate termination finish, which are RoHS compliant and VO

VS (2.5V to 5.5V) L1

compatible with both SnPb and Pb-free soldering operations. Intersil

VIN LX

Pb-free products are MSL classified at Pb-free peak reflow 1.8µH

R3 100

temperatures that meet or exceed the Pb-free requirements of VDD

C1

IPC/JEDEC J STD-020. 10µF

C2 C3

10µF 0.1µF EL7530

Pinout

EL7530 (10 LD MSOP) R5 100k

R1*

TOP VIEW PG

124k C4

EN FB

1 SGND FB 10 470pF

R4 100k SYNC R2*

100k

2 PGND VO 9 R6

100k

PGND

3 LX PG 8 SGND VO

(1.8V @ 600mA)

4 VIN EN 7

5 VDD SYNC 6 * VO = 0.8V * (1 + R1 / R2)

FN7434 Rev 6.00 Page 1 of 11

July 12, 2006

EL7530

Absolute Maximum Ratings (TA = 25°C) Thermal Information

VIN, VDD, PG to SGND . . . . . . . . . . . . . . . . . . . . . . . -0.3V to +6.5V Thermal Resistance (Typical) JA (°C/W)

LX to PGND . . . . . . . . . . . . . . . . . . . . . . . . . . -0.3V to (VIN + +0.3V) MSOP Package (Note 1) . . . . . . . . . . . . . . . . . . . . . 115

SYNC, EN, VO, FB to SGND . . . . . . . . . . . . . -0.3V to (VIN + +0.3V) Operating Ambient Temperature . . . . . . . . . . . . . . . .-40°C to +85°C

PGND to SGND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.3V to +0.3V Storage Temperature . . . . . . . . . . . . . . . . . . . . . . . .-65°C to +150°C

Peak Output Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 800mA Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +125°C

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typ values are for information purposes only. Unless otherwise noted, all tests are

at the specified temperature and are pulsed tests, therefore: TJ = TC = TA

NOTE:

1. JA is measured in free air with the component mounted on a high effective thermal conductivity test board with “direct attach” features. See

Tech Brief TB379.

Electrical Specifications VDD = VIN = VEN = 3.3V, C1 = C2 = 10µF, L = 1.8µH, VO = 1.8V (as shown in Typical Application Diagram),

unless otherwise specified.

PARAMETER DESCRIPTION CONDITIONS MIN TYP MAX UNIT

DC CHARACTERISTICS

VFB Feedback Input Voltage PWM Mode 790 800 810 mV

IFB Feedback Input Current 100 nA

VIN, VDD Input Voltage 2.5 5.5 V

VIN,OFF Minimum Voltage for Shutdown VIN falling 2 2.2 V

VIN,ON Maximum Voltage for Startup VIN rising 2.2 2.4 V

IS Input Supply Quiescent Current

Active - PFM Mode VSYNC = 0V 120 145 µA

Active - PWM Mode VSYNC = 3.3V 6.5 7.5 mA

IDD Supply Current PWM, VIN = VDD = 5V 400 500 µA

EN = 0, VIN = VDD = 5V 0.1 1 µA

RDS(ON)-PMOS PMOS FET Resistance VDD = 5V, wafer test only 70 100 m

RDS(ON)-NMOS NMOS FET Resistance VDD = 5V, wafer test only 45 75 m

ILMAX Current Limit 1.2 A

TOT,OFF Over-temperature Threshold T rising 145 °C

TOT,ON Over-temperature Hysteresis T falling 130 °C

IEN, ISYNC EN, SYNC Current VEN, VRSI = 0V and 3.3V -1 1 µA

VEN1, VSYNC1 EN, SYNC Rising Threshold VDD = 3.3V 2.4 V

VEN2, VSYNC2 EN, SYNC Falling Threshold VDD = 3.3V 0.8 V

VPG Minimum VFB for PG, WRT Targeted VFB rising 95 %

VFB Value

VFB falling 86 %

VOLPG PG Voltage Drop ISINK = 3.3mA 35 70 mV

AC CHARACTERISTICS

FPWM PWM Switching Frequency 1.25 1.4 1.6 MHz

tSYNC Minimum SYNC Pulse Width Guaranteed by design 25 ns

tSS Soft-start Time 650 µs

FN7434 Rev 6.00 Page 2 of 11

July 12, 2006

EL7530

Pin Descriptions

PIN NUMBER PIN NAME PIN FUNCTION

1 SGND Negative supply for the controller stage

2 PGND Negative supply for the power stage

3 LX Inductor drive pin; high current digital output with average voltage equal to the regulator output voltage

4 VIN Positive supply for the power stage

5 VDD Power supply for the controller stage

6 SYNC SYNC input pin; when connected to HI, regulator runs at forced PWM mode; when connected to Low, auto

PFM/PWM mode; when connected to external sync signal, at external PWM frequency up to 12MHz

7 EN Enable

8 PG Power-Good open drain output

9 VO Output voltage sense

10 FB Voltage feedback input; connected to an external resistor divider between VO and SGND for variable

output

Block Diagram

100 VDD

VO INDUCTOR SHORT

0.1µF

+

10pF VIN

-

C4 124K

CURRENT

470pF FB 5M SENSE

-

+ PWM

COMPEN- +

SATION -

PWM P-DRIVER

100K COMPARATOR

RAMP LX 1.8µH

SYNC PFM

GENERA- CONTROL 1.8V

SYNC CLOCK ON-TIME LOGIC

TOR 0 TO 600mA

CONTROL

EN

EN

SOFT- +

START -

10µF 10µF

PWM N-DRIVER

COMPARATOR

UNDER-

VOLTAGE PGND

5V +

–

BANDGAP

LOCKOUT

REFERENCE +

100K

TEMPERA- -

TURE SYNCHRONOUS PG

SENSE PG

RECTIFIER

SGND

POWER

GOOD

FN7434 Rev 6.00 Page 3 of 11

July 12, 2006

EL7530

Performance Curves and Waveforms

All waveforms are taken at VIN = 3.3V, VO = 1.8V, IO = 600mA with component values shown on page 1 at room ambient temperature, unless

otherwise noted.

100 100

VO=3.3V

95

90 VO=3.3V

90 VO=2.5V

80

85 VO=2.5V

EFFICIENCY (%)

70

EFFICIENCY (%)

80 VO=1.8V

75 VO=1.8V 60

VO=1.0V VO=1.5V

70 VO=1.5V 50

65 VO=1.2V

40

60 VO=0.8V VO=1.0V

30

55 VO=1.2V

20 VO=0.8V

50

45 VIN=5V 10

VIN=5V

40 0

1 10 100 600

1 10 100 600

IO (mA) IO (mA)

FIGURE 1. EFFICIENCY vs IO (PFM/PWM MODE) FIGURE 2. EFFICIENCY vs IO (PWM MODE)

100 100

VO=2.5V 90 VO=2.5V

95

VO=1.8V VO=1.8V

90 80

85 VO=1.5V

EFFICIENCY (%)

70

EFFICIENCY (%)

80 VO=1.2V

VO=1.5V 60

75 VO=1.2V

50 VO=1.0V

70 VO=1.0V

65 40

VO=0.8V

60 30

55 20

VO=0.8V

50

10 VIN=3.3V

45 VIN=3.3V 0

40

1 10 100 600

1 10 100 600

IO (mA) IO (mA)

FIGURE 3. EFFICIENCY vs IO (PFM/FWM MODE) FIGURE 4. EFFICIENCY vs IO (PWM MODE)

1.44 0.1%

VIN=5V IO=600mA VIN=3.3V IO=600mA

1.42 VIN=5V IO=0A

0.0%

VO CHANGES

1.4 -0.1%

FS (MHz)

VIN=3.3V IO=0A

VIN=3.3V

1.38 -0.2%

VIN=5V

1.36 -0.3%

1.34 -0.4%

1.32 -0.5%

-50 0 50 100 150 0 0.2 0.4 0.6 0.8 1

TA (°C) IO (A)

FIGURE 5. FS vs JUNCTION TEMPERATURE (PWM MODE) FIGURE 6. LOAD REGULATIONS (PWM MODE)

FN7434 Rev 6.00 Page 4 of 11

July 12, 2006

EL7530

Performance Curves and Waveforms (Continued)

All waveforms are taken at VIN = 3.3V, VO = 1.8V, IO = 600mA with component values shown on page 1 at room ambient temperature, unless

otherwise noted.

0.1% 12

0.0% VIN=5V IO=0A

10

VIN=3.3V IO=0A

-0.1%

8

VO CHANGES

-0.2%

IS (mA)

-0.3% VIN=3.3V IO=600mA

6

-0.4%

4

-0.5%

2

-0.6% VIN=5V IO=600mA

-0.7% 0

-50 0 50 100 150 2.5 3 3.5 4 4.5 5

TJ (°C) VS (V)

FIGURE 7. PWM MODE LOAD/LINE REGULATIONS vs FIGURE 8. NO LOAD QUIESCENT CURRENT (PWM MODE)

JUNCTION TEMPERATURE

140

VO=3.3V

130 VO=1.8V

120

110

100

IS (µA)

VO=1.5V

90 VO=1.2V VO=1.0V

VO=0.8V

80

70

60

50

2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5 6.0

VS (V)

FIGURE 9. NO LOAD QUIESCENT CURRENT (PFM MODE)

1 2

VIN

(2V/DIV)

EN

IIN

(0.25A/DIV)

IIN

VO (0.25A/DIV)

(2V/DIV)

PG VO

(2V/DIV)

PG

200µs/DIV 500µs/DIV

FIGURE 10. START-UP AT IO = 600mA FIGURE 11. ENABLE AND SHUT-DOWN

FN7434 Rev 6.00 Page 5 of 11

July 12, 2006

EL7530

Performance Curves and Waveforms (Continued)

All waveforms are taken at VIN = 3.3V, VO = 1.8V, IO = 600mA with component values shown on page 1 at room ambient temperature, unless

otherwise noted.

LX LX

(2V/DIV) (2V/DIV)

IL

IL (0.5A/DIV)

(0.5A/DIV)

VO

VO (10mV/DIV)

(50mV/DIV)

2µs/DIV 0.5µs/DIV

FIGURE 12. PFM STEADY-STATE OPERATION WAVEFORM FIGURE 13. PWM STEADY-STATE OPERATION (IO = 600mA)

(IO = 100mA)

SYNC SYNC

(2V/DIV) (2V/DIV)

LX LX

(2V/DIV) (2V/DIV)

IL

(0.5A/DIV) IL

(0.5A/DIV)

0.2µs/DIV 20ns/DIV

FIGURE 14. EXTERNAL SYNCHRONIZATION TO 2MHz FIGURE 15. EXTERNAL SYNCHRONIZATION TO 12MHz

IO

IO (200mA/DIV)

(200mA/DIV)

VO

VO (100mV/DIV)

(100mV/DIV)

100µs/DIV 50µs/DIV

FIGURE 16. LOAD TRANSIENT RESPONSE (22mA TO 600mA) FIGURE 17. PWM LOAD TRANSIENT RESPONSE (30mA TO

600mA)

FN7434 Rev 6.00 Page 6 of 11

July 12, 2006

EL7530

Performance Curves and Waveforms (Continued)

All waveforms are taken at VIN = 3.3V, VO = 1.8V, IO = 600mA with component values shown on page 1 at room ambient temperature, unless

otherwise noted.

100

1.4MHz

80

EFFICIENCY (%)

5MHz 12MHz

60

IO

(200mA/DIV)

40

VO 20

(50mV/DIV)

0

0 200 400 600 800 1K 1.2K

50µs/DIV IO (mA)

FIGURE 18. PWM LOAD TRANSIENT RESPONSE (100mA TO FIGURE 19. EFFICIENCY vs IO (PWM MODE)

500mA)

1 0.5

12MHz

0.6 0.3

VO CHANGES (%)

VO CHANGES (%)

1.4MHz 12MHz

0.2 0.1

5MHz 1.4MHz

0 -0.1

-0.2 -0.3 5MHz

-0.6 -0.5

0 200 400 600 800 1K 1.2K 0 200 400 600 800 1K 1.2K

IO (mA) VIN (V)

FIGURE 20. LOAD REGULATION (PWM MODE) FIGURE 21. LINE REGULATION @ 500mA (PWM MODE)

IO=150mA IO=50mA

SYNC SYNC

(2V/DIV) (2V/DIV)

LX LX

(2V/DIV) (2V/DIV)

2µs/DIV 2µs/DIV

FIGURE 22. PFM-PWM TRANSITION TIME FIGURE 23. PFM-PWM TRANSITION TIME

FN7434 Rev 6.00 Page 7 of 11

July 12, 2006

EL7530

Performance Curves and Waveforms (Continued)

All waveforms are taken at VIN = 3.3V, VO = 1.8V, IO = 600mA with component values shown on page 1 at room ambient temperature, unless

otherwise noted.

VO CHANGES (%)

1

-1

PFM PWM

-2

-3

0 200 400 600 800 1000 1200

IOUT (mA)

FIGURE 24. PFM-PWM LOAD REGULATION

JEDEC JESD51-3 LOW EFFECTIVE THERMAL JEDEC JESD51-7 HIGH EFFECTIVE THERMAL

CONDUCTIVITY TEST BOARD CONDUCTIVITY TEST BOARD

0.6 1

0.9 870mW

486mW

0.5

POWER DISSIPATION (W)

POWER DISSIPATION (W)

0.8

M

0.7 SO

0.4 M JA P8

SO = /1

P8 0.6 11 0

JA 5°

= 20 /1 C/

0.3 6° 0 0.5 W

C/

W 0.4

0.2

0.3

0.2

0.1

0.1

0 0

0 25 50 75 85 100 125 0 25 50 75 85 100 125

AMBIENT TEMPERATURE (°C) AMBIENT TEMPERATURE (°C)

FIGURE 25. PACKAGE POWER DISSIPATION vs AMBIENT FIGURE 26. PACKAGE POWER DISSIPATION vs AMBIENT

TEMPERATURE TEMPERATURE

FN7434 Rev 6.00 Page 8 of 11

July 12, 2006

EL7530

Applications Information In this mode, the P channel MOSFET and N channel

MOSFET always operate complementary. When the

Product Description PMOSFET is on and the NMOSFET off, the inductor current

The EL7530 is a synchronous, integrated FET 600mA step- increases linearly. The input energy is transferred to the

down regulator which operates from an input of 2.5V to 5.5V. output and also stored in the inductor. When the P channel

The output voltage is user-adjustable with a pair of external MOSFET is off and the N channel MOSFET on, the inductor

resistors. current decreases linearly, and energy is transferred from

the inductor to the output. Hence, the average current

When the load is very light, the regulator automatically

through the inductor is the output current. Since the inductor

operates in the PFM mode, thus achieving high efficiency at

and the output capacitor act as a low pass filter, the duty

light load (>70% for 1mA load). When the load increases,

cycle ratio is approximately equal to VO divided by VIN.

the regulator automatically switches over to a voltage-mode

PWM operating at nominal 1.4MHz switching frequency. The The output LC filter has a second order effect. To maintain

efficiency is up to 95%. the stability of the converter, the overall controller must be

compensated. This is done with the fixed internally

It can also operate in a fixed PWM mode or be synchronized

compensated error amplifier and the PWM compensator.

to an external clock up to 12MHz for improved EMI

Because the compensations are fixed, the values of input

performance.

and output capacitors are 10µF to 22µF ceramic and

PFM Operation inductor is 1.5µH to 2.2µH.

The heart of the EL7530 regulator is the automatic Forced PWM Mode/SYNC Input

PFM/PWM controller. Pulling the SYNC pin HI (>2.5V) forces the converter into

If the SYNC pin is connected to ground, the regulator PWM mode in the next switching cycle regardless of output

operates automatically in either the PFM or PWM mode, current. The duration of the transition varies depending on the

depending on load. When the SYNC pin is connected to VIN, output current. Figures 22 and 23 (under two different loading

the regulator operates in the fixed PWM mode. When the pin conditions) show the device goes from PFM to PWM mode.

is connected to an external clock ranging from 1.6MHz to Note: In Forced PWM mode, the IC will continue to start-up

12MHz, the regulator is in the fixed PWM mode and in PFM mode to support pre-biased load applications.

synchronized to the external clock frequency.

Start-Up and Shut-Down

In the automatic PFM/PWM operation, when the load is light, When the EN pin is tied to VIN, and VIN reaches

the regulator operates in the PFM mode to achieve high approximately 2.4V, the regulator begins to switch. The

efficiency. The top P channel MOSFET is turned on first. The inductor current limit is gradually increased to ensure proper

inductor current increases linearly to a preset value before it soft-start operation.

is turned off. Then the bottom N channel MOSFET turns on,

and the inductor current linearly decreases to zero current. When the EN pin is connected to a logic low, the EL7530 is

The N channel MOSFET is then turned off, and an anti- in the shut-down mode. All the control circuitry and both

ringing MOSFET is turned on to clamp the VLX pin to VO. MOSFETs are off, and VOUT falls to zero. In this mode, the

The inductor current looks like triangular pulses. The total input current is less than 1µA.

frequency of the pulses is mainly a function of output current. When the EN reaches logic HI, the regulator repeats the

The higher the load, the higher the frequency of the pulses start-up procedure, including the soft-start function.

until the inductor current becomes continuous. At this point,

the controller automatically changes to PWM operation. Current Limit and Short-Circuit Protection

The current limit is set at about 1.2A for the PMOS. When a

When the controller transitions to PWM mode, there can be short-circuit occurs in the load, the preset current limit

a perturbation to the output voltage. This perturbation is due restricts the amount of current available to the output, which

to the inherent behavior of switching converters when causes the output voltage to drop below the preset voltage.

transitioning between two control loops. To reduce this In the meantime, the excessive current heats up the

effect, it is recommended to use the phase-lead capacitor regulator until it reaches the thermal shut-down point.

(C4) shown in the Typical Application Diagram on page 1.

This capacitor allows the PWM loop to respond more quickly Thermal Shut-Down

to this type of perturbation. To properly size C4, refer to the Once the junction reaches about 145°C, the regulator shuts

Component Selection section. down. Both the P channel and the N channel MOSFETs turn

off. The output voltage will drop to zero. With the output

PWM Operation

MOSFETs turned off, the regulator will soon cool down.

The regulator operates the same way in the forced PWM or Once the junction temperature drops to about 130°C, the

synchronized PWM mode. In this mode, the inductor current regulator will restart again in the same manner as EN pin

is always continuous and does not stay at zero. connects to logic HI.

FN7434 Rev 6.00 Page 9 of 11

July 12, 2006

EL7530

Thermal Performance by generating a zero and a pole in the transfer function. As a

The EL7530 is available in a fused-lead MSOP10. general rule of thumb, C4 should be sized to start the phase-

Compared with regular MSOP10 package, the fused- lead lead at a frequency of ~2.5kHz. The zero will always appear

package provides lower thermal resistance. The JA is at lower frequency than the pole and follow the equation

100°C/W on a 4-layer board and 125°C/W on 2-layer board. below:

Maximizing the copper area around the pins will further 1

f Z = ----------------------

improve the thermal performance. 2R 2 C 4

Power Good Output

Over a normal range of R2 (~10-100k), C4 will range from

The PG (pin 8) output is used to indicate when the output ~470-4700pF. The pole frequency cannot be set once the

voltage is properly regulating at the desired set point. It is an zero frequency is chosen as it is dictated by the ratio of R1

open-drain output that should be tied to VIN or VCC through and R2, which is solely determined by the desired output set

a 100k resistor. If no faults are detected, EN is high, and point. The equation below shows the pole frequency

the output voltage is within ~5% of regulation, the PG pin will relationship:

be allowed to go high. Otherwise, the open-drain NMOS will

pull PG low. 1

f P = ---------------------------------------

2 R 1 R 2 C 4

Output Voltage Selection

Users can set the output voltage of the variable version with Layout Considerations

a resister divider, which can be chosen based on the The layout is very important for the converter to function

following formula: properly. The following PC layout guidelines should be

R 2 followed:

V O = 0.8 1 + -------

R 1 1. Separate the Power Ground ( ) and Signal Ground

( i); connect them only at one point right at the pins

Component Selection 2. Place the input capacitor as close to VIN and PGND pins

Because of the fixed internal compensation, the component as possible

choice is relatively narrow. For a regulator with fixed output 3. Make the following PC traces as small as possible:

voltage, only two capacitors and one inductor are required. from LX pin to L

We recommend 10µF to 22µF multi-layer ceramic capacitors from CO to PGND

with X5R or X7R rating for both the input and output 4. If used, connect the trace from the FB pin to R1 and R2

capacitors, and 1.5µH to 2.2µH for the inductor. as close as possible

The RMS current present at the input capacitor is decided by 5. Maximize the copper area around the PGND pin

the following formula: 6. Place several via holes under the chip to additional

ground plane to improve heat dissipation

V O V IN – V O

I INRMS = ----------------------------------------------- I O The demo board is a good example of layout based on this

V IN

outline. Please refer to the EL7530 Application Brief.

This is about half of the output current IO for all the VO. This

input capacitor must be able to handle this current.

The inductor peak-to-peak ripple current is given as:

V IN – V O V O

I IL = --------------------------------------------

L V IN f S

L is the inductance

fS the switching frequency (nominally 1.4MHz)

The inductor must be able to handle IO for the RMS load

current, and to assure that the inductor is reliable, it must

handle the 2A surge current that can occur during a current

limit condition.

In addition to decoupling capacitors and inductor value, it is

important to properly size the phase-lead capacitor C4

(Refer to the Typical Application Diagram). The phase-lead

capacitor creates additional phase margin in the control loop

FN7434 Rev 6.00 Page 10 of 11

July 12, 2006

EL7530

Mini SO Package Family (MSOP)

0.25 M C A B A

MDP0043

MINI SO PACKAGE FAMILY

D

(N/2)+1

N SYMBOL MSOP8 MSOP10 TOLERANCE NOTES

A 1.10 1.10 Max. -

A1 0.10 0.10 ±0.05 -

A2 0.86 0.86 ±0.09 -

E E1 PIN #1 b 0.33 0.23 +0.07/-0.08 -

I.D.

c 0.18 0.18 ±0.05 -

D 3.00 3.00 ±0.10 1, 3

E 4.90 4.90 ±0.15 -

1

B (N/2) E1 3.00 3.00 ±0.10 2, 3

e 0.65 0.50 Basic -

L 0.55 0.55 ±0.15 -

e H

C L1 0.95 0.95 Basic -

SEATING N 8 10 Reference -

PLANE

Rev. C 6/99

0.10 C b 0.08 M C A B NOTES:

N LEADS

1. Plastic or metal protrusions of 0.15mm maximum per side are not

included.

2. Plastic interlead protrusions of 0.25mm maximum per side are

L1 not included.

3. Dimensions “D” and “E1” are measured at Datum Plane “H”.

A 4. Dimensioning and tolerancing per ASME Y14.5M-1994.

c

SEE DETAIL "X"

A2

GAUGE

PLANE

0.25

A1 L

3° ±3°

DETAIL X

© Copyright Intersil Americas LLC 2004-2006. All Rights Reserved.

All trademarks and registered trademarks are the property of their respective owners.

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted

in the quality certifications found at www.intersil.com/en/support/qualandreliability.html

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such

modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are

current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its

subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

FN7434 Rev 6.00 Page 11 of 11

July 12, 2006

You might also like

- Features: Monolithic 1A Step-Down Regulator With Low Quiescent CurrentDocument12 pagesFeatures: Monolithic 1A Step-Down Regulator With Low Quiescent CurrentVaibhavNo ratings yet

- EL7532 fn7435Document8 pagesEL7532 fn7435csclzNo ratings yet

- Features: 600Khz/1.2Mhz PWM Step-Up RegulatorDocument12 pagesFeatures: 600Khz/1.2Mhz PWM Step-Up RegulatorЕвгений ИвановNo ratings yet

- Datasheet AP7175Document14 pagesDatasheet AP7175Edwin SorianoNo ratings yet

- Off-Line Quasi-Resonant Switching Regulators: STR-Y6763, STR-Y6765, and STR-Y6766Document13 pagesOff-Line Quasi-Resonant Switching Regulators: STR-Y6763, STR-Y6765, and STR-Y6766Renato Luther escalanteNo ratings yet

- Features: Lt1375/Lt1376 1.5A, 500Khz Step-Down Switching RegulatorsDocument29 pagesFeatures: Lt1375/Lt1376 1.5A, 500Khz Step-Down Switching RegulatorsSergio MuriloNo ratings yet

- Features: Ultra-Low Noise, Low Power, Wideband AmplifierDocument16 pagesFeatures: Ultra-Low Noise, Low Power, Wideband AmplifierЕвгений ИвановNo ratings yet

- AL6562ADocument16 pagesAL6562ASibi DhayalanNo ratings yet

- Features: 0.5Mhz, Low Supply Voltage, Low Input Current Bimos Operational AmplifierDocument5 pagesFeatures: 0.5Mhz, Low Supply Voltage, Low Input Current Bimos Operational AmplifierAlexandre Correa100% (1)

- DatasheetDocument14 pagesDatasheetsamaya egNo ratings yet

- RT8015 2A 2MHz Synchronous Step-Down RegulatorDocument15 pagesRT8015 2A 2MHz Synchronous Step-Down RegulatorPedrolaura BethencourtNo ratings yet

- RT8059Document10 pagesRT8059Bijan AmiriNo ratings yet

- BOSCH CJ135 Product Information 101201Document2 pagesBOSCH CJ135 Product Information 101201Wang Zheng Feng100% (1)

- Features: Monolithic 4A DC/DC Step-Down RegulatorDocument14 pagesFeatures: Monolithic 4A DC/DC Step-Down RegulatorЕвгений ИвановNo ratings yet

- Features: High Performance Pin DriverDocument11 pagesFeatures: High Performance Pin DriverЕвгений ИвановNo ratings yet

- uPI Semiconductor Up1735 Synchronous-Rectified Buck Converter DatasheetDocument13 pagesuPI Semiconductor Up1735 Synchronous-Rectified Buck Converter DatasheetSultan SinghNo ratings yet

- REN Isl8014a DST 20030828Document16 pagesREN Isl8014a DST 20030828cer cerNo ratings yet

- Isl6545 A PDFDocument17 pagesIsl6545 A PDFdragoblaztrNo ratings yet

- DatasheetDocument10 pagesDatasheetmartin andres rodriguez rengifoNo ratings yet

- Icl 7667Document11 pagesIcl 7667De JeanNo ratings yet

- LM273yh3 DatasheetDocument22 pagesLM273yh3 DatasheetsongdashengNo ratings yet

- El8100 01Document14 pagesEl8100 01Евгений ИвановNo ratings yet

- 3A, 23V, 340Khz Synchronous Step-Down Converter: General Description FeaturesDocument12 pages3A, 23V, 340Khz Synchronous Step-Down Converter: General Description FeaturesJuan Carlos SrafanNo ratings yet

- 3A Ultra Low Dropout Linear Regulator: General Description FeaturesDocument11 pages3A Ultra Low Dropout Linear Regulator: General Description FeaturesdejanNo ratings yet

- Power Factor Corrector: Minidip SO8 Ordering Numbers: L6561 (Minidip) L6561D (SO8)Document11 pagesPower Factor Corrector: Minidip SO8 Ordering Numbers: L6561 (Minidip) L6561D (SO8)Karim CocasNo ratings yet

- Features: Differential Receiver/EqualizerDocument10 pagesFeatures: Differential Receiver/EqualizerShashank MittalNo ratings yet

- Tps 65135Document28 pagesTps 65135Arthit SomrangNo ratings yet

- DG401, DG403, DG405: Vishay SiliconixDocument15 pagesDG401, DG403, DG405: Vishay SiliconixytnateNo ratings yet

- AT1526 GlobalMixed ModetechnologyDocument2 pagesAT1526 GlobalMixed ModetechnologyFafa MangstabNo ratings yet

- rt8009 201Document14 pagesrt8009 201Алексей ГомоновNo ratings yet

- Tiny Package, High Performance, Constant Current Switching Regulator For White LEDDocument15 pagesTiny Package, High Performance, Constant Current Switching Regulator For White LEDFahed AlmaktariNo ratings yet

- L6561Document11 pagesL6561Gilson3DNo ratings yet

- REN Isl6549 DST 20051027Document18 pagesREN Isl6549 DST 20051027Jesus RodriguezNo ratings yet

- lc5222d Ds enDocument11 pageslc5222d Ds enRick HunterNo ratings yet

- RT8290: 3A, 23V, 340kHz Synchronous Step-Down ConverterDocument12 pagesRT8290: 3A, 23V, 340kHz Synchronous Step-Down ConverterMarcius RodriguesNo ratings yet

- 1Mhz, 2.0A, High-Efficiency Synchronous-Rectified Buck ConverterDocument16 pages1Mhz, 2.0A, High-Efficiency Synchronous-Rectified Buck ConverterFuNn FFNo ratings yet

- LD7550B-PWM 6pinDocument14 pagesLD7550B-PWM 6pinSanjeev GuptaNo ratings yet

- Icl7667 1528911Document12 pagesIcl7667 1528911Trung Nguyên VõNo ratings yet

- Ds8204a 05Document19 pagesDs8204a 05marcelo Chiu LeonNo ratings yet

- Features: 12Mhz Rail-To-Rail Input-Output BufferDocument13 pagesFeatures: 12Mhz Rail-To-Rail Input-Output BufferЕвгений ИвановNo ratings yet

- El 7104Document7 pagesEl 7104Oscar FernandezNo ratings yet

- REN Isl6522 DST 20010525-1998129Document17 pagesREN Isl6522 DST 20010525-1998129atillaacar34No ratings yet

- RT8204-DS8204-06 Single Synchronous Buck With LDO ControllerDocument19 pagesRT8204-DS8204-06 Single Synchronous Buck With LDO ControllerMaks ProstNo ratings yet

- 3A Ultra Low Dropout Linear Regulator With Enable: GND FB V EN PG V V 8 7 6 5 1 2 3 4 VDocument14 pages3A Ultra Low Dropout Linear Regulator With Enable: GND FB V EN PG V V 8 7 6 5 1 2 3 4 VNuriyanto 3No ratings yet

- MP172Document20 pagesMP172leo.alpha94No ratings yet

- Ap64350 2Document26 pagesAp64350 2Nishanth MNo ratings yet

- Tda7265 (30W+30W)Document18 pagesTda7265 (30W+30W)ShiguMiku TheyNo ratings yet

- Obd 1 Ecus Component List: Chipping Components All EcusDocument1 pageObd 1 Ecus Component List: Chipping Components All EcusGaragem do FerreiraNo ratings yet

- REN Hip2101 DST 20010410Document15 pagesREN Hip2101 DST 20010410Yenidir TeknoNo ratings yet

- Features: Single 12V Input Supply Dual Regulator - Synchronous Rectified Buck PWM and Linear Power ControllerDocument18 pagesFeatures: Single 12V Input Supply Dual Regulator - Synchronous Rectified Buck PWM and Linear Power ControllerJesus RodriguezNo ratings yet

- Data Sheet: Stereo Cassette Head Preamplifier and EqualizerDocument16 pagesData Sheet: Stereo Cassette Head Preamplifier and EqualizerahmedNo ratings yet

- 3A, 1Mhz, Synchronous Step-Down Converter: General Description FeaturesDocument12 pages3A, 1Mhz, Synchronous Step-Down Converter: General Description FeatureskiryanoffNo ratings yet

- 1571fDocument16 pages1571fSanele LangaNo ratings yet

- Green-Mode PWM Controller GuideDocument16 pagesGreen-Mode PWM Controller Guidegulhshan khanNo ratings yet

- 1605Document8 pages1605Yuda AditamaNo ratings yet

- Features: High Speed, Monolithic Pin DriverDocument9 pagesFeatures: High Speed, Monolithic Pin DriverЕвгений ИвановNo ratings yet

- 1.5A Switch Step Down Switching Regulator: 1 General FeaturesDocument11 pages1.5A Switch Step Down Switching Regulator: 1 General FeaturesRene gNo ratings yet

- 3A, 18V, 340Khz Synchronous Step-Down Converter: General Description FeaturesDocument14 pages3A, 18V, 340Khz Synchronous Step-Down Converter: General Description FeaturesAgung KaryaNo ratings yet

- uPI Confidential: 3A Ultra Low Dropout Linear RegulatorDocument13 pagesuPI Confidential: 3A Ultra Low Dropout Linear RegulatorLEONNo ratings yet

- Backhoe 220 To 600 SeriesDocument3 pagesBackhoe 220 To 600 SeriesЕвгений ИвановNo ratings yet

- 216 Spare Part ListDocument21 pages216 Spare Part ListЕвгений ИвановNo ratings yet

- Mccsemi: 1N746 A Thru 1N759 ADocument3 pagesMccsemi: 1N746 A Thru 1N759 AЕвгений ИвановNo ratings yet

- General Operation Instructions: Hydraulic High Pressure Water PumpsDocument14 pagesGeneral Operation Instructions: Hydraulic High Pressure Water PumpsEdwin MorenoNo ratings yet

- Schottky Barrier Diode: Dual Series Schottky Barrier Diode For Mixer and Detector 5V, 30ma, 0.69pF, CPDocument6 pagesSchottky Barrier Diode: Dual Series Schottky Barrier Diode For Mixer and Detector 5V, 30ma, 0.69pF, CPЕвгений ИвановNo ratings yet

- 1EDN7550 and 1EDN8550: Feature ListDocument21 pages1EDN7550 and 1EDN8550: Feature ListЕвгений ИвановNo ratings yet

- 1°C Triple Smbus Sensor With Resistance Error Correction: Product FeaturesDocument3 pages1°C Triple Smbus Sensor With Resistance Error Correction: Product FeaturesЕвгений ИвановNo ratings yet

- 1°C Triple Temperature Sensor With Hotter of Two Zones: Product FeaturesDocument26 pages1°C Triple Temperature Sensor With Hotter of Two Zones: Product FeaturesЕвгений ИвановNo ratings yet

- 1N4728A - 1N4758A: Zener DiodesDocument4 pages1N4728A - 1N4758A: Zener DiodesЕвгений ИвановNo ratings yet

- Multiple RPM-Based PWM Fan Controller For Five Fans: Product FeaturesDocument56 pagesMultiple RPM-Based PWM Fan Controller For Five Fans: Product FeaturesЕвгений ИвановNo ratings yet

- Horizontal Genlock, 8FSC: FeaturesDocument15 pagesHorizontal Genlock, 8FSC: FeaturesЕвгений ИвановNo ratings yet

- 1N5817Document3 pages1N5817Gallego OrtizNo ratings yet

- Eemb Battery Specification: Lithium Thionyl Chloride BatteryDocument9 pagesEemb Battery Specification: Lithium Thionyl Chloride BatteryЕвгений ИвановNo ratings yet

- E523-81 Elmos DsDocument68 pagesE523-81 Elmos DsЕвгений ИвановNo ratings yet

- Ev12aq600 PDSDocument57 pagesEv12aq600 PDSЕвгений ИвановNo ratings yet

- Features: High Speed, Monolithic Pin DriverDocument9 pagesFeatures: High Speed, Monolithic Pin DriverЕвгений ИвановNo ratings yet

- EMC2106Document106 pagesEMC2106Евгений ИвановNo ratings yet

- EPC2050 - Enhancement-Mode Power Transistor Preliminary Specification SheetDocument8 pagesEPC2050 - Enhancement-Mode Power Transistor Preliminary Specification SheetЕвгений ИвановNo ratings yet

- EMC6W201Document5 pagesEMC6W201Евгений ИвановNo ratings yet

- EQCO30R5.D 3G/HD-SDI Video Cable EqualizerDocument24 pagesEQCO30R5.D 3G/HD-SDI Video Cable EqualizerЕвгений ИвановNo ratings yet

- Features: Monolithic 2A Step-Down RegulatorDocument9 pagesFeatures: Monolithic 2A Step-Down RegulatorЕвгений ИвановNo ratings yet

- 40 Volt, 10 Amp Peak, High-Frequency, Integrated Laser Driver DescriptionDocument9 pages40 Volt, 10 Amp Peak, High-Frequency, Integrated Laser Driver DescriptionЕвгений ИвановNo ratings yet

- EMC6D102Document86 pagesEMC6D102Евгений ИвановNo ratings yet

- Features: Monolithic 350ma Step-Down RegulatorDocument10 pagesFeatures: Monolithic 350ma Step-Down RegulatorЕвгений ИвановNo ratings yet

- Features: Monolithic 4A DC/DC Step-Down RegulatorDocument14 pagesFeatures: Monolithic 4A DC/DC Step-Down RegulatorЕвгений ИвановNo ratings yet

- Monolithic Amplifier: Dc-4 GHZDocument21 pagesMonolithic Amplifier: Dc-4 GHZЕвгений ИвановNo ratings yet

- EPC2059 - Enhancement Mode Power Transistor: V, 170 V R, 9 mΩ I, 24 ADocument6 pagesEPC2059 - Enhancement Mode Power Transistor: V, 170 V R, 9 mΩ I, 24 AЕвгений ИвановNo ratings yet

- EQCO31R20Document34 pagesEQCO31R20Евгений ИвановNo ratings yet

- Kelas Xii - May I Help You - Chapter 1Document2 pagesKelas Xii - May I Help You - Chapter 1Syifa Fauziah50% (2)

- Field Work Report on Social Services at Mukono DistrictDocument36 pagesField Work Report on Social Services at Mukono Districtronny rymes tusubira100% (2)

- Ch. 32 - Optical ImagesDocument19 pagesCh. 32 - Optical ImagesAbdallah IslaihNo ratings yet

- Riva, Anna - Secrets of Magical Seals A Modern Grimoire of Amulets, Charms, Symbols and TalismansDocument35 pagesRiva, Anna - Secrets of Magical Seals A Modern Grimoire of Amulets, Charms, Symbols and Talismansbondogoof83% (12)

- Answers YEAR 9 EXAM TERM 2Document13 pagesAnswers YEAR 9 EXAM TERM 2Mustafa Al Qady50% (2)

- Chapter No # 03 Product Innovation CharterDocument11 pagesChapter No # 03 Product Innovation CharterabzuarNo ratings yet

- MET 2017 Child and AdolDocument193 pagesMET 2017 Child and AdolFerlyn Serio AguilarNo ratings yet

- Measuring Solar Radiation the Right WayDocument14 pagesMeasuring Solar Radiation the Right WayObada Ar-ruzziNo ratings yet

- Coriolis Mass Flow MeterDocument2 pagesCoriolis Mass Flow MeterSreejesh SundaresanNo ratings yet

- Statim 5000Document2 pagesStatim 5000Alexandra JanicNo ratings yet

- Neuropsychoanalysis: An Interdisciplinary Journal For Psychoanalysis and The NeurosciencesDocument18 pagesNeuropsychoanalysis: An Interdisciplinary Journal For Psychoanalysis and The NeurosciencesPierreNo ratings yet

- 02 WholeDocument155 pages02 WholeTayeb CheliremNo ratings yet

- The Impact of New Normal To The Gadget Store OwnersDocument28 pagesThe Impact of New Normal To The Gadget Store OwnersKatricia Elaine VillanuevaNo ratings yet

- Seismic Force CANADA Code - CNBC2005-V421Document7 pagesSeismic Force CANADA Code - CNBC2005-V421Niko NištićNo ratings yet

- Eltorai, Ibrahim M A Spotlight On The History of Ancient EgyptianDocument215 pagesEltorai, Ibrahim M A Spotlight On The History of Ancient EgyptianJonas PsontomfanceNo ratings yet

- SPECIFICATIONS For Constant Temperature and Humidity ChamberDocument5 pagesSPECIFICATIONS For Constant Temperature and Humidity Chamber彭以和No ratings yet

- MSCCH 504Document309 pagesMSCCH 504Harshal YadavNo ratings yet

- The Six-Flow Reactor Technology A Review PDFDocument17 pagesThe Six-Flow Reactor Technology A Review PDFTysir SarhanNo ratings yet

- Planning and Optimal Control Policy Gradient MethodsDocument34 pagesPlanning and Optimal Control Policy Gradient MethodscosmicduckNo ratings yet

- Throwing Garbage in The SeaDocument3 pagesThrowing Garbage in The SeaZaramagne CaliboNo ratings yet

- Magnetic Particle Test Record Truck Crane Articulating Boom (Gb-La03)Document2 pagesMagnetic Particle Test Record Truck Crane Articulating Boom (Gb-La03)Hario PramuditoNo ratings yet

- ECE PhD Requirements GuideDocument29 pagesECE PhD Requirements GuideFrancisco HurtadoNo ratings yet

- Clinical Teaching on Geriatric AssessmentDocument9 pagesClinical Teaching on Geriatric AssessmentANITTA SNo ratings yet

- Subculture The Meaning of StyleDocument3 pagesSubculture The Meaning of StyleMandic SutomoreNo ratings yet

- Rising Strong: How The Ability To Reset Transforms The Way We Live, Love, Parent, and Lead - Brené BrownDocument5 pagesRising Strong: How The Ability To Reset Transforms The Way We Live, Love, Parent, and Lead - Brené Browndarupasi40% (5)

- BPSC Exam Pattern DetailsDocument21 pagesBPSC Exam Pattern DetailsBPSC BPSCNo ratings yet

- Galileo (Satellite Navigation)Document21 pagesGalileo (Satellite Navigation)irayoNo ratings yet

- Course-Outline-For-Stud2020 (1) - English 9 THIRD QUARTERDocument3 pagesCourse-Outline-For-Stud2020 (1) - English 9 THIRD QUARTERTyrone Dave BalitaNo ratings yet

- Mock Teaching Lesson PlanDocument2 pagesMock Teaching Lesson Planapi-354968419No ratings yet