Professional Documents

Culture Documents

Multi-Phase PWM Controller For CPU Core Power Supply: Features General Description

Uploaded by

Freddy ArmstrongOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Multi-Phase PWM Controller For CPU Core Power Supply: Features General Description

Uploaded by

Freddy ArmstrongCopyright:

Available Formats

www.DataSheet4U.

com

Preliminary RT9248A

Multi-Phase PWM Controller for CPU Core Power Supply

General Description Features

The RT9248A is a cost-effective multi-phase buck DC/DC z Multi-Phase Power Conversion with Automatic

controller integrated with all control functions for GHz CPU Phase Selection

VRM. The RT9248A controls 2 or 3 buck switching stages z VRM9 & VRD10 DAC Output with Active Droop

operating in interleaved phase set automatically. The multi- Compensation for Fast Load Transient

phase architecture provides high output current while z Smooth VCORE Transition at VID Jump

maintaining low power dissipation on power devices and z Multi-Level VID125 Input for VRM9 & VRD10

low stress on input and output capacitors. The high Selection

equivalent operating frequency also reduces the component z Power Stage Thermal Balance by RDS(ON) Current

dimension and the output voltage ripple in load transient. Sense

RT9248A controls both voltage and current loops to achieve z Hiccup Mode Over-Current Protection

good regulation, response & power stage thermal balance. z Programmable Switching Frequency (50kHz to

Precise current loop using RDS(ON) as sense component 400kHz per Phase), Under-Voltage Lockout and

builds precise load line for strict VRM DC & transient Soft-Start

specification and also ensures thermal balance of different z High Ripple Frequency Times Channel Number

power stages. The settings of current sense, droop tuning, z RoHS Compliant and 100% Lead (Pb)-Free

VCORE initial offset and over current protection are

independent to compensation circuit of voltage loop. The Applications

feature greatly facilitates the flexibility of CPU power supply z Intel® Processors Voltage Regulator: VRM9 and VRD10

design and tuning. z Low Output Voltage, High Current DC-DC Converters

The DAC output of RT9248A supports VRM9 & VRD10 by z Voltage Regulator Modules

VID125 multi-level input, precise initial value & smooth

VCORE transient at VID jump. The IC monitors the VCORE Pin Configurations

voltage for PGOOD and over-voltage protection. Soft-start,

over-current protection and programmable under-voltage (TOP VIEW)

lockout are also provided to assure the safety of micro- VID4 28 VCC

VID3 2 27 PWM1

processor and power system.

VID2 3 26 PWM2

VID1 4 25 PWM3

Ordering Information VID0 5 24 NC

RT9248A VID125 6 23 ISP1

SGND 7 22 ISP2

Package Type FB 8 21 ISP3

C : TSSOP-28 COMP 9 20 ISN

PGOOD 10 19 GND

Operating Temperature Range DVD 11 18 ADJ

P : Pb Free with Commercial Standard

SS 12 17 VDIF

G : Green (Halogen Free with Commer- 16 VSEN

RT 13

cial Standard) VOSS 15 IMAX

14

Note : TSSOP-28

RichTek Pb-free and Green products are :

`RoHS compliant and compatible with the current require-

ments of IPC/JEDEC J-STD-020.

`Suitable for use in SnPb or Pb-free soldering processes.

`100% matte tin (Sn) plating.

DS9248A-06 March 2006 www.richtek.com

1

2

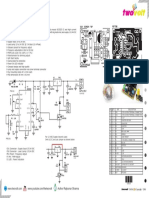

+12V

+12V C6

1uF

C7

www.richtek.com

R12 C8

10 4.7uF 2200uF

D1 RT9603 Q1

1N4148 1 8

RT9248A

BST DRVH L1

1uH

7 IPD09N03LA

+5V SW

4

VCC Q2 R13

C5 2 5 1

1uF VIN DRVL

C4

1uF PGND IPD06N03LA C9

0.01uF

RT9248A 6

1 28

VID4 > VID4 VCC

2 27

Typical Application Circuit

VID3 > VID3 PWM1 +12V

3 26 +12V C11 VCORE

VID2 > VID2 PWM2 1uF

4 25 C12

VID1 > VID1 PWM3 C20 to C24

R14 C13 2200uF x 5

5 24 4.7uF 2200uF

VID0 > VID0 NC 10 D2

RT9603 Q3

1N4148 1 8

6 23 R7 3k BST DRVH

VID125 > VID125 ISP1 L2

1uH

7 22 R8 3k 7 IPD09N03LA

SGND ISP2 SW

4

8 21 R9 3k VCC Q4 R15 C25 to C28

FB ISP3 5 4.7 2200uF x 4

R1 C1 C10 2

15k 22nF 1uF VIN DRVL

9 20 R10 1k

COMP ISN IPD06N03LA C14

PGND 0.01uF

10 19

Preliminary

GND 6

PG_VCORE < PGOOD

C2 33pF

11 18

DVD ADJ

R2 C3

2.4k +12V 12 17

0.1uF VDIF

SS

R3 16 +12V

9k 13 VSEN +12V C16

RT 1uF

14 15

VOSS IMAX C17

R4 R5 R16 C18

12k R6 4.7uF 2200uF

1k 100k R11 10 D3

12k RT9603 Q5

1N4148 1 8

BST DRVH L3

1uH

7 IPD09N03LA

SW

4

VCC Q6 R17

2 5 4.7

C15

1uF VIN DRVL

PGND IPD06N03LA C19

0.01uF

6

DS9248A-06 March 2006

Preliminary RT9248A

Functional Pin Description

VID4 (Pin 1), VID3 (Pin 2), VID2 (Pin 3), VID1 (Pin 4), VOSS (Pin 14)

VID0 (Pin 5) & VID125 (Pin 6) VCORE initial value offset. Connect this pin to GND with a

DAC voltage identification inputs. Tie VID125 to GND for resistor to set the offset value.

VRM9 or to VCC for VRD10. These pins are internally

pulled to 3.3V if left open. IMAX (Pin 15)

Over-Current protection set.

SGND (Pin 7)

Connect this pin to the return pin of VCORE . VSEN (Pin 16)

Power good and over-voltage monitor input. Connect this

FB (Pin 8) to the sense pin of VCORE.

Inverting input of the internal error amplifier.

VDIF (Pin 17)

COMP (Pin 9) This pin is being tied to VSEN pin internally.

Output of the error amplifier and input of the PWM

comparator. ADJ (Pin 18)

Current sense output for active droop adjust. Connect a

PGOOD (Pin 10) resistor from this pin to GND to set the load droop.

Power good open-drain output.

GND (Pin 19)

DVD (Pin 11) IC ground.

Programmable power UVLO detection or converter enable

input. ISN (Pin 20)

RDS(ON) current sense input from anyone of channel sense

SS (Pin 12) components' GND node.

Connect this SS pin to GND with a capacitor to set the

soft-start time interval. ISP1 (Pin 23), ISP2 (Pin 22), ISP3 (Pin 21)

RDS(ON) current sense inputs for individual converter

RT (Pin 13) channels. Tie this pin to the component's sense node.

Switching frequency setting. Connect this pin to GND with

a resistor to set the frequency. NC (Pin 24)

No internal connection.

Frequency vs. RRT

450

PWM1 (Pin 27), PWM2 (Pin 26), PWM3 (Pin 25)

400

PWM outputs for each driven channel. Connect these pins

350

to the PWM input of the MOSFET driver. For systems

300

which use 2 channels, connect PWM3 high.

f OSC(kHz)

250

200 VCC (Pin 28)

150 IC power supply. Connect this pin to a 5V supply.

100

50

0

0 10 20 30 40 50 60 70

RRT (k Ω)

DS9248A-06 March 2006 www.richtek.com

3

4

www.richtek.com

RT9248A

IMAX PGOOD VCC DVD RT

+ INH PWM Logic

VID0 Oscillator PWM1

OCP - & Driver

VID1 Power On Reset & + +

VID2 Setting

VID3 DAC Sawtooth PWMCP

Function Block Diagram

VID4

VID125 INH + INH PWM Logic

PWM2

- & Driver

+ +

SGND PWMCP

OVP Trip + INH

Point

+ PWM Logic

PWM3

- - & Driver

+ +

PWMCP

PG Trip +

DAC + Droop

Point

-

Offset Currrent

Source/Sink

+ +

+ - Current -

- Correction ISP1

VOSS

Preliminary

+ +

ERROR ISN

AMP

- -

GAP AMP ISP2

+ +

+

SS -

-

Control -

ISP3

SUM/M

VSEN VDIF FB COMP SS ADJ GND

DS9248A-06 March 2006

Preliminary RT9248A

Table 1. Output Voltage Program

Pin Name Nominal Output Voltage DACOUT

VID4 VID3 VID2 VID1 VID0 VID125 = H VID125 = L

1 1 1 1 1 No CPU No CPU

0 1 0 0 1 0.850V 1.625V

0 1 0 0 0 0.875V 1.650V

0 0 1 1 1 0.900V 1.675V

0 0 1 1 0 0.925V 1.700V

0 0 1 0 1 0.950V 1.725V

0 0 1 0 0 0.975V 1.750V

0 0 0 1 1 1.000V 1.775V

0 0 0 1 0 1.025V 1.800V

0 0 0 0 1 1.050V 1.825V

0 0 0 0 0 1.075V 1.850V

1 1 1 1 0 1.100V 1.100V

1 1 1 0 1 1.125V 1.125V

1 1 1 0 0 1.150V 1.150V

1 1 0 1 1 1.175V 1.175V

1 1 0 1 0 1.200V 1.200V

1 1 0 0 1 1.225V 1.225V

1 1 0 0 0 1.250V 1.250V

1 0 1 1 1 1.275V 1.275V

1 0 1 1 0 1.300V 1.300V

1 0 1 0 1 1.325V 1.325V

1 0 1 0 0 1.350V 1.350V

1 0 0 1 1 1.375V 1.375V

1 0 0 1 0 1.400V 1.400V

1 0 0 0 1 1.425V 1.425V

1 0 0 0 0 1.450V 1.450V

0 1 1 1 1 1.475V 1.475V

0 1 1 1 0 1.500V 1.500V

0 1 1 0 1 1.525V 1.525V

0 1 1 0 0 1.550V 1.550V

0 1 0 1 1 1.575V 1.575V

0 1 0 1 0 1.600V 1.600V

Note: (1) 0: Connected to GND

(2) 1: Open

(3) For VID125, H: VCC, L: GND

DS9248A-06 March 2006 www.richtek.com

5

RT9248A Preliminary

Absolute Maximum Ratings (Note 1)

z Supply Voltage, VCC ------------------------------------------------------------------------------------------- 7V

z Input, Output or I/O Voltage ---------------------------------------------------------------------------------- GND-0.3V to VCC+0.3V

z Package Thermal Resistance

TSSOP-28, θJA -------------------------------------------------------------------------------------------------- 45°C/W

z Junction Temperature ------------------------------------------------------------------------------------------ 150°C

z Lead Temperature (Soldering, 10 sec.) -------------------------------------------------------------------- 260°C

z Storage Temperature Range --------------------------------------------------------------------------------- −65°C to 150°C

z ESD Susceptibility (Note 2)

HBM (Human Body Mode) ----------------------------------------------------------------------------------- 2kV

MM (Machine Mode) ------------------------------------------------------------------------------------------- 200V

Recommended Operating Conditions (Note 3)

z Supply Voltage, VCC ------------------------------------------------------------------------------------------- 5V ± 10%

z Ambient Temperature Range --------------------------------------------------------------------------------- 0°C to 70°C

z Junction Temperature Range --------------------------------------------------------------------------------- 0°C to 125°C

Electrical Characteristics

(VCC = 5V, TA = 25°C, unless otherwise specified)

Parameter Symbol Test Conditions Min Typ Max Units

VCC Supply Current

Nominal Supply Current ICC PWM 1,2,3 Open -- 12 -- mA

Power-On Reset

POR Threshold VCCRTH VCC Rising 4.0 4.2 4.5 V

Hysteresis VCCHYS 0.2 0.5 -- V

Trip (Low to High) VDVDTP Enable 0.9 1.0 1.1 V

VDVD Threshold

Hysteresis VDVDHYS -- 70 -- mV

Oscillator

Free Running Frequency fOSC RRT = 12kΩ 170 200 230 kHz

Frequency Adjustable Range fOSC_ADJ 50 -- 400 kHz

Ramp Amplitude ΔVOSC RRT = 12kΩ -- 1.9 -- V

Ramp Valley VRV -- 1.0 -- V

Maximum On-Time of Each Channel 62 66 75 %

RT Pin Voltage VRT RRT = 12kΩ 0.94 1.0 1.06 V

Reference and DAC

VRD10, VDAC ≥ 1V −1 -- +1 %

DACOUT Voltage Accuracy ΔVDAC_10

VRD10, VDAC < 1V −10 -- +10 mV

DACOUT Voltage Accuracy ΔVDAC_9 VRM9 −1 -- +1 %

To be continued

www.richtek.com DS9248A-06 March 2006

6

Preliminary RT9248A

Parameter Symbol Test Conditions Min Typ Max Units

DAC (VID0-VID4) Input Low VILDAC -- -- 0.4 V

DAC (VID0-VID4) Input High VIHDAC 0.8 -- -- V

VID125 Input for VRM9 VVID125_9 -- -- 0.4 V

VID125 Input for VRD10 VVID125_10 0.8 -- -- V

DAC (VID0-VID125) Bias Current IBIAS_DAC 35 50 65 μA

VOSS Pin Voltage VVOSS RVOSS = 100kΩ 0.95 1.0 1.15 V

Error Amplifier

DC Gain -- 85 -- dB

Gain-Bandwidth Product GBW -- 10 -- MHz

Slew Rate SR COMP = 10pF -- 3 -- V/μs

Current Sense GM Amplifier

ISP 1,2,3 Full Scale Source Current IISPFSS 60 -- -- μA

ISP 1,2,3 Current for OCP IISPOCP 90 -- -- μA

Protection

IMAX Voltage VIMAX RIMAX = 10k 0.94 1.0 1.06 V

SS Current ISS VSS = 1V -- 13 -- μA

Over-Voltage Trip (VSEN/DACOUT) ΔOVT -- 140 -- %

Power Good

Lower Threshold (VSEN/DACOUT) VPG− VSEN Rising -- 92 -- %

Output Low Voltage VPGL IPG = 4mA -- -- 0.2 V

Note 1. Stresses listed as the above “Absolute Maximum Ratings” may cause permanent damage to the device. These are for

stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the

operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended

periods may remain possibility to affect device reliability.

Note 2. Devices are ESD sensitive. Handling precaution recommended.

Note 3. The device is not guaranteed to function outside its operating conditions.

DS9248A-06 March 2006 www.richtek.com

7

RT9248A Preliminary

Application Information

RT9248A is a multi-phase DC/DC controller that precisely Fault Detection

regulates CPU core voltage and balances the current of The chip detects VCORE for over voltage and power good

different power channels. The converter consisting of detection. The “hiccup mode” operation of over-current

RT9248A and its companion MOSFET driver provides high protection is adopted to reduce the short circuit current.

quality CPU power and all protection functions to meet The inrush current at the start up is suppressed by the

the requirement of modern VRM. soft start circuit through clamping the pulse width and output

voltage.

Voltage Control

RT9248A senses the CPU V CORE by an precise Phase Setting and Converter Start Up

instrumental amplifier to minimize the voltage drop on PCB RT9248A interfaces with companion MOSFET drivers (like

trace at heavy load. VSEN & SGND are the differential RT9600, RT9602 or RT9603 series) for correct converter

inputs. VDIF is the output node of the differential voltage & initialization. The tri-state PWM output (high, low and high

the input for PGOOD & OVP sense. The internal high impedance) pins sense the interface voltage at IC POR

accuracy VID DAC allows selection of either VRM9 or period (both VCC and DVD trip). The channel is enabled if

VRD10 compliance via VID125 pin setting. Control loop the pin voltage is 1.2V less than VCC. Please tie the PWM

consists of error amplifier, multi-phase pulse width output to VCC and the current sense pins to GND or left

modulator, driver and power components. Like conventional floating if the channel is unused. For 2-Channel application,

voltage mode PWM controller, the output voltage is locked connect PWM3 high.

at the VREF of error amplifier and the error signal is used as

the control signal VC of pulse width modulator. The PWM Current Sensing Setting

signals of different channels are generated by comparison RT9248A senses the current of low side MOSFET in each

of EA output and split-phase sawtooth wave. Power stage synchronous rectifier when it is conducting for channel

transforms VIN to output by PWM signal on-time ratio. current balance and droop tuning. The differential sensing

GM amplifier converts the voltage on the sense component

Current Balance (can be a sense resistor or the RDS(ON) of the low side

RT9248A senses the current of low side MOSFET in each MOSFET) to current signal into internal circuit (see

synchronous rectifier when it is conducting for channel Figure 1). Be careful to choose GND sense input, ISN, of

current balance and droop tuning. The differential sensing the GM amplifier for effective channel current balance.

GM amplifier converts the voltage on the sense component

(can be a sense resistor or the RDS(ON) of the low side

IX 1

MOSFET) to current signal into internal balance circuit.

C u rre n t

The current balance circuit sums and averages the current <

B a la n c e IX

S a m p le

IB P

IS P 1

R SP1

D ro o p T u n e 2 IX -

< & GM

signals then produces the balancing signals injected to <

IX H o ld + RS IL

IB N

O v e r-C u rre n t

pulse width modulator. If the current of some power channel D e te c tio n

is greater than average, the balancing signal reduces the IX 2

output pulse width to keep the balance. C u rre n t

B a la n c e IX

< IB P R SP2

S a m p le - IS P 2

D ro o p T u n e 2 IX

< & GM

Load Droop <

IX H o ld

+

IB N IS N

RSN RS IL

O v e r-C u rre n t

D e te c tio n

The sensed power channel current signals regulate the G N D R e tu rn

reference of DAC to form a output voltage droop proportional IX 3

to the load current. The droop or so-called “active voltage C u rre n t

B a la n c e IX

< IB P R SP3

positioning” can reduce the output voltage ripple at load <

D ro o p T u n e 2 IX S a m p le

& GM

- IS P 3

IX + RS IL

H o ld

transient and the LC filter size. <

O v e r-C u rre n t

IB N

D e te c tio n

Figure 1. Current Sense Circuit

www.richtek.com DS9248A-06 March 2006

8

Preliminary RT9248A

I L × RS

The sensing circuit gets IX = by local feedback. Protection and SS Function

RSP

RSP = 3 x RSN (at 3 phase operation) to cancel the voltage For OVP, the RT9248A detects the VCORE by VDIF pin

drop caused by GM amplifier input bias current. IX is voltage of the differential amplifier output. Eliminate the

sampled and held just before low side MOSFET turns off delay due to compensation network (compared to sensing

(See Figure 2). Therefore, FB voltage) for fast and accurate detection. The trip point

of OVP is 140% of normal output level. The PWM outputs

I L (S/H) × R S V O T OFF

I X (S/H) = , I L (S/H) = I L (AVG) − × , are pulled low to turn on the low side MOSFET and turn off

R SP L 2 the high side MOSFET of the synchronous rectifier at OVP.

⎡ V IN − V O ⎤

T OFF = ⎢ ⎥ × 5uS for fosc = 200kHz

The OVP latch can only be reset by VCC or DVD restart

⎣ V IN ⎦ power on reset sequence. The PGOOD detection trip point

⎡ ⎡ V IN − V O ⎤ ⎤ of VCORE is 92% lower than the normal level. The PGOOD

⎢ VO − ⎢ ⎥ × 5uS ⎥

I X (S/H) = ⎢I L(AVG) − ⎣ V IN ⎦ ⎥×

RS open drain output pulls low when VCORE is lower than the

⎢ 2L ⎥ R SP

trip point. For VID jumping issue, only power fail conditions

⎢ ⎥

⎣ ⎦ (VCC & DVD are lower than trip point or OVP) reset the

Falling Slope = Vo/L

IL output low.

IL(AVG) Soft-start circuit generates a ramp voltage by charging

IL(S/H) external capacitor with 13μA current after IC POR acts.

Inductor Current

The PWM pulse width and VCORE are clamped by the rising

ramp to reduce the inrush current and protect the power

devices.

PWM Signal & High Side MOSFET Gate Signal

Over-current protection trip point is set by the resistor RIMAX

connected to IMAX pin. OCP is triggered if one channel

⎛ 0 .6 V ⎞

S/H current signal IX > ⎜ ⎟ × 1 .4 . Controller forces

Low Side MOSFET Gate Signal ⎝ R IMAX ⎠

PWM output latched at high impedance to turn off both

Figure 2. Inductor Current and PWM Signal high and low side MOSFETs in the power stage and initial

the hiccup mode protection. The SS pin voltage is pulled

DAC Offset Voltage & Droop Tuning

low with a 13μA current after it is less than 90% VCC. The

The DAC offset voltage is set by compensation network

converter restarts after SS pin voltage < 0.2V. Three times

⎛ 1V ⎞ R f 1

& VOSS pin external resistors by ⎜ R VOSS ⎟ × 4 . of OCP disable the converter and only release the latch by

⎝ ⎠

POR acts (see Figure 4).

The S/H current signals from power channels are injected

to ADJ pin to create droop voltage. VADJ = RADJ× 2 IX ∑ S.S

Count ==11 COUNT

COUNT Count ==22 COUNT

Count ==33

The DAC output voltage decreases by VADJ to form the

VCORE load droop (see Figure 3). VCORE

VDAC

0V

Overload

+

VADJ 2IX1 Applied

COMP

EA

+ - ∑ 2IX2

- 2IX3

Current ILOAD

Source >

1 IVOSS 0A

1V 4

IVOSS =

>

RVOSS

VOSS + FB ADJ T0,T1 T2 T3,T4

TIME

RVOSS RF1 RADJ

-

Figure 4.

>

VCORE

Figure 3. DAC Offset Voltage & Droop Tune Circuit

DS9248A-06 March 2006 www.richtek.com

9

RT9248A Preliminary

3-Phase Converter and Components Function Grouping

12V

VCC BST

DRVH

SW

RT9603

IN DRVL

PGND

SGND

VSEN

VDIF

PWM1

VID 12V

ISP1

PGOOD

VCC BST

DRVH

RT9248A

Compensation SW VCORE

& Offset COMP RT9603

FB PWM2 IN DRVL

PGND

ADJ

Droop Setting ISP2

ISN

12V DVD 12V

Driver Power

UVLO VOSS

ISP3

SS

VCC BST

DAC Offset

PWM3 DRVH

Voltage Setting

IMAX SW

GND

RT9603

OCP Setting IN DRVL

PGND

Current Sense

Components

Design Procedure Suggestion

Voltage Loop Setting VRM Load Line Setting

a. Output filter pole and zero (Inductor, output capacitor a. Droop amplitude (ADJ pin resistor).

value & ESR). b. No load offset (additional resistor in compensation

b. Error amplifier compensation & sawtooth wave amp- network).

litude (compensation network). c. DAC offset voltage setting (VOSS pin & compen-

c. Kelvin sense for VCORE. sation network resistor).

Current Loop Setting Power Sequence & SS

a. GM amplifier S/H current (current sense component DVD pin external resistor and SS pin capacitor.

RDS(ON), ISPx & ISN pin external resistor value,

PCB Layout

keep ISPx current < 60μA at full load condition for

a. Kelvin sense for current sense GM amplifier input.

better load line linearity).

b. Refer to layout guide for other item.

b. Over-current protection trip point (IMAX pin resistor,

keep ISPx current < 90μA at OCP condition for

precision issue).

www.richtek.com DS9248A-06 March 2006

10

Preliminary RT9248A

Design Example Asymptotic Bode Plot of PWM Loop Gain

100

Given:

80

Apply for three phase converter

VIN = 12V 60

Uncompensated EA Gain

VCORE = 1.5V 40

Gain (dB)

ILOAD (max) = 60A 20

VDROOP = 120mV at full load 0

Compensated EA Gain

OCP trip point set at 30A for each channel (S/H) -20 PWM Loop Gain

RDS(ON) = 6mΩ of low side MOSFET at 27°C -40 Modulator Gain

L = 2μH

-60

COUT = 9,000μF with 2mΩ ESR. 10

10 100

100 1K

1000 10K

10000 100K

100000 1M

1000000 10M

10000000

Frequency (Hz)

1. Compensation Setting Figure 6.

a. Modulator Gain, Pole and Zero:

2. Droop & DAC Offset Setting

From the following formula: For each channel the load current is 60A / 3 = 20A

V IN 12V

Modulator Gain = = = 4.2 (12.46dB) and the ripple current, ΔIL, is given as:

V RAMP 1.9V × 3

2 1.5V ⎛ 1.5V ⎞

where VRAMP : ramp amplitude of sawtooth wave 5us x x ⎜1 − ⎟ = 3.28A

1 2uH ⎝ 12V ⎠

LC Filter Pole = 2π x LC = 1.2kHz and ΔIL

The load current, IL, at S/H is 20 A − = 18.36 A .

2

Using the following formula to select the appropriate

1

ESR Zero = = 8.8kHz IX (MAX) for the S/H of GM amplifier:

2π x ESR x COUT

R DS(ON) × 18.36A

b. EA Compensation Network: I X (MAX) =

R SP

Select R1 = 2.4kΩ, R2 = 24kΩ, C1 = 6.6nF, The suggested IX is in the order of 40 to 50μA, select

C2 = 33pF and use the type 2 compensation RSP = 2.4kΩ then IX (MAX) will be 45.9μA.

scheme shown in Figure 5. VDROOP = 120mV = 45.9μA × 2 × 3 (phase no.) ×

R2 C1 R3 C3 RADJ, therefore RADJ will be 435Ω.

The RDS(ON) of MOSFET varies with temperature

C2 R1 rise. When the low side MOSFET working at 70°C

> VDIF

COMP and 5000ppm/°C temperature coefficient of RDS(ON),

FB

- the RDS(ON) at 70°C is given as:

+

R3,C3 are used in type 6mΩ × {1+ (70°C − 27°C) × 5000ppm/°C} = 7.3mΩ.

3 compensation scheme RADJ at 70°C is given as:

DACOUT (left NC in type 2)

RADJ_27°C × (RDS(ON)_27°C / RDS(ON)_70°C) = 358Ω

Figure 5.

3. Over-Current Protection Setting

From the following formulas: OCP trip point set at 30A for each channel,

1 1

FZ = , FP = RDS(ON) × 30A 0.6V

2π x R 2 x C 1 ⎛ C1 × C 2 ⎞ IX = = 1.4 × , RIMAX = 11.2kΩ

2π x R 2 x ⎜ ⎟ RSP RIMAX

Middle Band Gain =

R2 ⎝ C1 + C 2 ⎠

R1 Take the temperature rise into account, the RIMAX at

By calculation, the FZ = 1kHz, FP = 200kHz and 70°C will be:

Middle Band Gain is 10 (i.e 20dB). RIMAX_27°C × (RDS(ON)_27°C / RDS(ON)_70°C) = 9.2kΩ

The asymptotic bode plot of EA compensation and

4. Soft-Start Capacitor Selection

PWM loop gain is shown as Figure 6. CSS = 0.1μF is the suitable value for most application.

DS9248A-06 March 2006 www.richtek.com

11

RT9248A Preliminary

Layout Guide

Place the high-power switching components first, and separate them from sensitive nodes.

1. Most critical path: the current sense circuit is the most sensitive part of the converter. The current sense

resistors tied to ISP1,2,3 and ISN should be located not more than 0.5 inch from the IC and away from the

noise switching nodes. The PCB trace of sense nodes should be parallel and as short as possible. Kelvin

connection of the sense component (additional sense resistor or MOSFET RDS(ON)) ensures the accurate

stable current sensing.

Keep well Kelvin sense to ensure the stable operation!

2. Switching ripple current path:

a. Input capacitor to high side MOSFET.

b. Low side MOSFET to output capacitor.

c. The return path of input and output capacitor.

d. Separate the power and signal GND.

e. The switching nodes (the connection node of high/low side MOSFET and inductor) is the most noisy points.

Keep them away from sensitive small-signal node.

f. Reduce parasitic R, L by minimum length, enough copper thickness and avoiding of via.

3. MOSFET driver should be closed to MOSFET.

4. The compensation, bypass and other function setting components should be near the IC and away from the noisy

power path.

L1

SW1

VIN VOUT

RIN

COUT

CIN RL

V

L2

SW2

Figure 7. Power Stage Ripple Current Path

www.richtek.com DS9248A-06 March 2006

12

Preliminary RT9248A

Next to IC

+12V

CBP +12V or +5V

PWM VCC +5VIN

CBP

CBOOT IMAX

VCC BST VOSS Next to IC

IN DRVH COMP

LO1

VCORE CC

SW

RT9603 CIN COUT RT9248A RC

DRVL Kelvin Locate next

Sense RSP FB

PGND to FB Pin

ISPx

RFB

ISN

RSN

Locate near MOSFETs VSEN

ADJ

GND

For Thermal Couple

Figure 8. Layout Consideration

DS9248A-06 March 2006 www.richtek.com

13

RT9248A Preliminary

Outline Dimension

E E1

A A2

A1

b

Dimensions In Millimeters Dimensions In Inches

Symbol

Min Max Min Max

A 0.850 1.200 0.033 0.047

A1 0.050 0.152 0.002 0.006

A2 0.800 1.050 0.031 0.041

b 0.178 0.305 0.007 0.012

D 9.601 9.804 0.378 0.386

e 0.650 0.026

E 6.300 6.500 0.248 0.256

E1 4.293 4.496 0.169 0.177

L 0.450 0.762 0.018 0.030

28-Lead TSSOP Plastic Package

Richtek Technology Corporation Richtek Technology Corporation

Headquarter Taipei Office (Marketing)

5F, No. 20, Taiyuen Street, Chupei City 8F, No. 137, Lane 235, Paochiao Road, Hsintien City

Hsinchu, Taiwan, R.O.C. Taipei County, Taiwan, R.O.C.

Tel: (8863)5526789 Fax: (8863)5526611 Tel: (8862)89191466 Fax: (8862)89191465

Email: marketing@richtek.com

www.richtek.com DS9248A-06 March 2006

14

You might also like

- Multi-Phase PWM Controller For CPU Core Power Supply: General Description FeaturesDocument22 pagesMulti-Phase PWM Controller For CPU Core Power Supply: General Description FeaturesJose SamaNo ratings yet

- 5V/12V Synchronous Buck PWM DC-DC and Linear Power ControllerDocument18 pages5V/12V Synchronous Buck PWM DC-DC and Linear Power Controllerraed hasaniaNo ratings yet

- Datasheet Ic CE DEDocument15 pagesDatasheet Ic CE DEBersama UkhuwahNo ratings yet

- RT8204-DS8204-06 Single Synchronous Buck With LDO ControllerDocument19 pagesRT8204-DS8204-06 Single Synchronous Buck With LDO ControllerMaks ProstNo ratings yet

- 3-Phase Brushless Fan Motor DriverDocument30 pages3-Phase Brushless Fan Motor DriverAravind Prasad Sounder RajNo ratings yet

- Ds8204a 05Document19 pagesDs8204a 05marcelo Chiu LeonNo ratings yet

- Single Synchronous Buck Controller: RT8202L/MDocument19 pagesSingle Synchronous Buck Controller: RT8202L/MDenis DenisovNo ratings yet

- Single Synchronous Buck Controller: RT8202/A/BDocument18 pagesSingle Synchronous Buck Controller: RT8202/A/BMax ReparNo ratings yet

- 3-Phase Brushless Fan Motor DriverDocument30 pages3-Phase Brushless Fan Motor DriverAravind Prasad Sounder RajNo ratings yet

- 3-Phase Brushless Fan Motor DriverDocument30 pages3-Phase Brushless Fan Motor DriverAravind Prasad Sounder RajNo ratings yet

- Half Bridge Driver Based On: C2 1uF/25V CN1 C5 10uF/25V D1 MBRS140T3G C3 220uF/63VDocument2 pagesHalf Bridge Driver Based On: C2 1uF/25V CN1 C5 10uF/25V D1 MBRS140T3G C3 220uF/63VratnaNo ratings yet

- MAX218Document8 pagesMAX218Edson HenriqueNo ratings yet

- PIC PWM ControllerDocument10 pagesPIC PWM Controllerkeitabando100% (2)

- Halogen Dimmer PDFDocument1 pageHalogen Dimmer PDFVictorFaucheretNo ratings yet

- High Current Helogen Lamp Dimmer 1Document1 pageHigh Current Helogen Lamp Dimmer 1Nguyen Phuoc HoNo ratings yet

- PLCC-28: FeaturesDocument25 pagesPLCC-28: FeaturesTitoNo ratings yet

- DatasheetDocument10 pagesDatasheetmartin andres rodriguez rengifoNo ratings yet

- 5V/12V Synchronous Buck PWM DC-DC Controller: Features General DescriptionDocument17 pages5V/12V Synchronous Buck PWM DC-DC Controller: Features General DescriptionLuis Dark-passengerNo ratings yet

- High Efficiency Single Synchronous Buck PWM Controller: RT8240A/B/CDocument17 pagesHigh Efficiency Single Synchronous Buck PWM Controller: RT8240A/B/Ckamil_yilmaz_6No ratings yet

- EOBD/OBDII to RS232 gatewayDocument22 pagesEOBD/OBDII to RS232 gatewaylaurentiu_gd100% (1)

- Cost-Effective, 2A Peak Sink/Source Bus Termination RegulatorDocument14 pagesCost-Effective, 2A Peak Sink/Source Bus Termination Regulatoronc3h 112No ratings yet

- ACPL-C87AT/ACPL-C87BT: Data SheetDocument16 pagesACPL-C87AT/ACPL-C87BT: Data SheetMattias RahmNo ratings yet

- DatasheetDocument12 pagesDatasheetWAN MOZESNo ratings yet

- DC Motor Speed Controller 1 PDFDocument1 pageDC Motor Speed Controller 1 PDFRyn YahuFNo ratings yet

- DC Motor Speed Controller 1Document1 pageDC Motor Speed Controller 1Antonio BentoNo ratings yet

- DC Motor Speed Controller 1 PDFDocument1 pageDC Motor Speed Controller 1 PDFyukie heningNo ratings yet

- EasyArc Zx7-200 Igbt Inverter WelderDocument1 pageEasyArc Zx7-200 Igbt Inverter WelderSandeep Kumar67% (12)

- DC-MOTOR-SPEED-CONTROLLER-1 Using 3525 Circuit of Oscillator PDFDocument1 pageDC-MOTOR-SPEED-CONTROLLER-1 Using 3525 Circuit of Oscillator PDFChAmirShokatGujjar100% (2)

- 4A, 21V, 500Khz Synchronous Step-Down Converter: General DescriptionDocument17 pages4A, 21V, 500Khz Synchronous Step-Down Converter: General DescriptionJose MartinezNo ratings yet

- 3A, 18V, 700Khz Acot Synchronous Step-Down Converter: Features General DescriptionDocument14 pages3A, 18V, 700Khz Acot Synchronous Step-Down Converter: Features General DescriptionVasil StoyanovNo ratings yet

- 2A, 23V, 340Khz Synchronous Step-Down Converter: General Description FeaturesDocument14 pages2A, 23V, 340Khz Synchronous Step-Down Converter: General Description FeaturesGioVoTamNo ratings yet

- DC To DC Converter rt8272Document14 pagesDC To DC Converter rt8272hadNo ratings yet

- Dual Channel Synchronous-Rectified Buck MOSFET Driver: General Description FeaturesDocument11 pagesDual Channel Synchronous-Rectified Buck MOSFET Driver: General Description FeaturesLopos PoloNo ratings yet

- Synchronous Rectified Buck MOSFET Drivers: RT9611C/DDocument13 pagesSynchronous Rectified Buck MOSFET Drivers: RT9611C/Dcyberpunk.tech.brNo ratings yet

- Tesla Coil Driver Using SG3525 1 PDFDocument1 pageTesla Coil Driver Using SG3525 1 PDFNguyen Phuoc HoNo ratings yet

- RT9025 25GSP RichtekDocument12 pagesRT9025 25GSP RichtekBengkel Kompu7erNo ratings yet

- MT7830A MaxicTechnologyDocument8 pagesMT7830A MaxicTechnologyKamran AzamNo ratings yet

- 1Mhz, All-Ceramic, 3A PWM Buck DC/DC Converter: Global Mixed-Mode Technology IncDocument1 page1Mhz, All-Ceramic, 3A PWM Buck DC/DC Converter: Global Mixed-Mode Technology IncLeonardo FusserNo ratings yet

- FAN7314 LCD Backlight Inverter Drive IC: Features DescriptionDocument3 pagesFAN7314 LCD Backlight Inverter Drive IC: Features DescriptionJúnior Da Silva SantanaNo ratings yet

- RT8202AGQWDocument20 pagesRT8202AGQWandi FalikNo ratings yet

- Synchronous-Rectified Buck MOSFET Drivers: Features General DescriptionDocument5 pagesSynchronous-Rectified Buck MOSFET Drivers: Features General DescriptionTeles SilvaNo ratings yet

- Is Now Part ofDocument11 pagesIs Now Part offefoheavymetalNo ratings yet

- Single-Phase PWM Controller for CPU / GPU Core Power SupplyDocument24 pagesSingle-Phase PWM Controller for CPU / GPU Core Power SupplyakashNo ratings yet

- BookDocument8 pagesBookThakuri Man SinghNo ratings yet

- Intersil-ISL97649AIRZ-T-datasheetDocument21 pagesIntersil-ISL97649AIRZ-T-datasheetKeys SyekNo ratings yet

- Daikin PSL Controller GK247A - J-088Document2 pagesDaikin PSL Controller GK247A - J-088sunhuynhNo ratings yet

- 3A, 23V, 340Khz Synchronous Step-Down Converter: General Description FeaturesDocument12 pages3A, 23V, 340Khz Synchronous Step-Down Converter: General Description FeaturesAbdul MuhidNo ratings yet

- TrasDocument11 pagesTrasAmauri RogérioNo ratings yet

- 28V/10A Synchronous Buck Regulator with 0.8V OutputDocument15 pages28V/10A Synchronous Buck Regulator with 0.8V OutputРоман ІкалюкNo ratings yet

- Unisonic Technologies Co., LTD: Multiple Rs-232 Drivers and ReceiversDocument10 pagesUnisonic Technologies Co., LTD: Multiple Rs-232 Drivers and ReceiversRamon Alexander PradaNo ratings yet

- 3A, 18V, 340Khz Synchronous Step-Down Converter: General Description FeaturesDocument14 pages3A, 18V, 340Khz Synchronous Step-Down Converter: General Description FeaturesAgung KaryaNo ratings yet

- AT1526 GlobalMixed ModetechnologyDocument2 pagesAT1526 GlobalMixed ModetechnologyFafa MangstabNo ratings yet

- Richtek Tech R7731AGE C250411Document14 pagesRichtek Tech R7731AGE C250411Игорь ПочепаNo ratings yet

- High Voltage 8-CH LED Driver: Features General DescriptionDocument13 pagesHigh Voltage 8-CH LED Driver: Features General DescriptionSetiawan Abdul RochimNo ratings yet

- Single Synchronous Buck Controller: RT8209A/B/CDocument18 pagesSingle Synchronous Buck Controller: RT8209A/B/CscobaNo ratings yet

- 3A, 23V, 340Khz Synchronous Step-Down Converter: General Description FeaturesDocument12 pages3A, 23V, 340Khz Synchronous Step-Down Converter: General Description FeaturesJuan Carlos SrafanNo ratings yet

- Unisonic Technologies Co., LTD: Multiple Rs-232 Drivers and ReceiversDocument10 pagesUnisonic Technologies Co., LTD: Multiple Rs-232 Drivers and Receiversll_luiguiNo ratings yet

- RT9018ADocument12 pagesRT9018Abusamawan wayanNo ratings yet

- Xiaomi Redmi 2 Schematic MobilegsmDocument59 pagesXiaomi Redmi 2 Schematic MobilegsmJefreeM67% (9)

- (LED Monitor ) : Owner'S ManualDocument38 pages(LED Monitor ) : Owner'S ManualFreddy ArmstrongNo ratings yet

- A400CG EE Trouble ShootingDocument40 pagesA400CG EE Trouble ShootingFreddy ArmstrongNo ratings yet

- Datasheet: Multi-Mode Multi-Key Multi-Function SeriesDocument13 pagesDatasheet: Multi-Mode Multi-Key Multi-Function SeriesFreddy ArmstrongNo ratings yet

- W83301R Winbond ACPI-STR ControllerDocument16 pagesW83301R Winbond ACPI-STR ControllerFreddy ArmstrongNo ratings yet

- Radeon7500 SpecsDocument2 pagesRadeon7500 SpecsFreddy ArmstrongNo ratings yet

- Multi-Phase PWM Controller For CPU Core Power Supply: Features General DescriptionDocument14 pagesMulti-Phase PWM Controller For CPU Core Power Supply: Features General DescriptionFreddy ArmstrongNo ratings yet

- Via P4M266 (VT8751)Document68 pagesVia P4M266 (VT8751)Freddy ArmstrongNo ratings yet

- MSI MS-7222 Chipset and Block DiagramDocument30 pagesMSI MS-7222 Chipset and Block DiagramFreddy ArmstrongNo ratings yet

- DSL-2730E T1 Manual v1.00 (DI)Document96 pagesDSL-2730E T1 Manual v1.00 (DI)Freddy ArmstrongNo ratings yet

- Prerequisites: Simatic It 6.6Document31 pagesPrerequisites: Simatic It 6.6nitramNo ratings yet

- Integrated Circuits For Audio Power AmplifiersDocument6 pagesIntegrated Circuits For Audio Power Amplifiershectormv22No ratings yet

- B6 LXI2 DS T811067en BDocument3 pagesB6 LXI2 DS T811067en BProyectos KdoNo ratings yet

- Ower Lectronics (: Soft Switching (L40 - L41)Document7 pagesOwer Lectronics (: Soft Switching (L40 - L41)Mayank KashyapNo ratings yet

- CompoundDocument4 pagesCompounduscrNo ratings yet

- Hawkboard Quick Start GuideDocument34 pagesHawkboard Quick Start GuideneduninnamonnaNo ratings yet

- Monthly ReportDocument3 pagesMonthly ReportRaphoto Mokete100% (1)

- Abd MotorolaDocument441 pagesAbd MotorolaAmr Mohamed Abd El-baryNo ratings yet

- Compiler Design - Software Design ProjectDocument54 pagesCompiler Design - Software Design Projectal3mary0% (1)

- Comando Gns 3Document145 pagesComando Gns 3NeycerAnchundiaNo ratings yet

- Micro Focus Enterprise 2.3.1 Quick Start GuideDocument41 pagesMicro Focus Enterprise 2.3.1 Quick Start GuidepoojagirotraNo ratings yet

- Hadoop Configuration and Single Node SetupDocument61 pagesHadoop Configuration and Single Node SetupParthNo ratings yet

- MAVLink Survey: A Comprehensive OverviewDocument23 pagesMAVLink Survey: A Comprehensive OverviewthendyNo ratings yet

- Gayle McDowell CareerCup Sample ResumeDocument2 pagesGayle McDowell CareerCup Sample ResumeKaran KakwaniNo ratings yet

- Types of Blocks in TerraformDocument6 pagesTypes of Blocks in Terraformkunta.srujan5No ratings yet

- 0542 (MDM) HubJavaUserExits en H2LDocument18 pages0542 (MDM) HubJavaUserExits en H2LarjuncchaudharyNo ratings yet

- User Guide Indu SoftDocument0 pagesUser Guide Indu SoftJoseNo ratings yet

- NGEA - M02 - NGEA Hardware - TXTDocument20 pagesNGEA - M02 - NGEA Hardware - TXTGuido Emanuel SteinbachNo ratings yet

- 12201619001-Niladree Pal-41 (DIP)Document12 pages12201619001-Niladree Pal-41 (DIP)NILADREE PAULNo ratings yet

- Installing SolidWorks 2016 On Your PC Jan 2017 (Stand Alone)Document6 pagesInstalling SolidWorks 2016 On Your PC Jan 2017 (Stand Alone)Jignesh ChauhanNo ratings yet

- Ground Faulty Monitor RelayDocument1 pageGround Faulty Monitor RelayAsad NaeemNo ratings yet

- P.P.10.1 Node Analysis of Phasor CircuitsDocument10 pagesP.P.10.1 Node Analysis of Phasor CircuitsNguyễn Bá HoàngNo ratings yet

- Linear Control Systems Lab 08 Block Diagram ReductionDocument13 pagesLinear Control Systems Lab 08 Block Diagram ReductionUmer EhsanNo ratings yet

- XNC-NC1000-NC500 - Office Network ConnectionsDocument48 pagesXNC-NC1000-NC500 - Office Network ConnectionsANDREI HENDRICNo ratings yet

- User Manual: SINGLE/DUAL 16/24/32/48 CHANNEL Versatile Multiplexer Module (MODEL No. 40-630/632)Document34 pagesUser Manual: SINGLE/DUAL 16/24/32/48 CHANNEL Versatile Multiplexer Module (MODEL No. 40-630/632)Kecseg Fonce AndreiNo ratings yet

- 220 1002 Exam ObjectivesDocument19 pages220 1002 Exam Objectivesapi-272637257100% (1)

- Vertiv Smart-Solutions-Intelligent-Integrated-Infrastructure-For-The-Data-CenterDocument12 pagesVertiv Smart-Solutions-Intelligent-Integrated-Infrastructure-For-The-Data-Centeryogesh chandrayanNo ratings yet

- Pi Toolbox V3.1 Manual 29P-071406Document491 pagesPi Toolbox V3.1 Manual 29P-071406ddNo ratings yet

- Zenitel P 6223Document3 pagesZenitel P 6223ANDREASBOULNo ratings yet

- Preprocessor Directives in C# - Key Concepts and UsageDocument6 pagesPreprocessor Directives in C# - Key Concepts and UsageNiranjanNo ratings yet