Professional Documents

Culture Documents

Features: CMOS Programmable Peripheral Interface

Uploaded by

bedoui marwenOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Features: CMOS Programmable Peripheral Interface

Uploaded by

bedoui marwenCopyright:

Available Formats

DATASHEET

82C55A FN2969

CMOS Programmable Peripheral Interface Rev 11.01

Jan 20, 2020

The 82C55A is a high performance CMOS version of the Features

industry standard 8255A and is manufactured using a

self-aligned silicon gate CMOS process (Scaled SAJI IV). It • Pb-Free Plus Anneal Available (RoHS Compliant)

(See Ordering Info)

is a general purpose programmable I/O device which may

be used with many different microprocessors. There are 24 • Pin Compatible with NMOS 8255A

I/O pins which may be individually programmed in 2 groups

• 24 Programmable I/O Pins

of 12 and used in 3 major modes of operation. The high

performance and industry standard configuration of the • Fully TTL Compatible

82C55A make it compatible with the 80C86, 80C88 and • High Speed, No “Wait State” Operation with 5MHz and

other microprocessors. 8MHz 80C86 and 80C88

Static CMOS circuit design insures low operating power. TTL • Direct Bit Set/Reset Capability

compatibility over the full military temperature range and bus

• Enhanced Control Word Read Capability

hold circuitry eliminate the need for pull-up resistors. The

Intersil advanced SAJI process results in performance equal • L7 Process

to or greater than existing functionally equivalent products at • 2.5mA Drive Capability on All I/O Ports

a fraction of the power.

• Low Standby Power (ICCSB) . . . . . . . . . . . . . . . . . . .10µA

Ordering Information

PART NUMBERS

PART PART TEMP.

5MHz MARKING 8MHz MARKING RANGE (°C) PACKAGE PKG. DWG. #

CP82C55A-5Z (Note) CP82C55A-5Z CP82C55AZ (Note) CP82C55AZ 0 to +70 40 Ld PDIP (Pb-free) E40.6

IP82C55AZ (Note) IP82C55AZ -40 to +85 40 Ld PDIP (Pb-free)

CS82C55A-5Z* (Note) CS82C55A-5Z CS82C55AZ* (Note) CS82C55AZ 0 to +70 44 Ld PLCC (Pb-free)

N44.65

IS82C55A-5Z* (Note) IS82C55A-5Z IS82C55AZ* (Note) IS82C55AZ -40 to +85 44 Ld PLCC (Pb-free)

CQ82C55AZ (Note) CQ82C55AZ 0 to +70 44 Ld MQFP (Pb-free) Q44.10x10

IQ82C55AZ* (Note) IQ82C55AZ -40 to +85 44 Ld MQFP (Pb-free)

ID82C55A ID82C55A -40 to +85 40 Ld CERDIP F40.6

MD82C55A/B MD82C55A/B -55 to +125

8406602QA 8406602QA SMD#

8406602XA 8406602XA SMD# 44 Ld CLCC J44.A

*Add “96” suffix to part number for tape and reel packaging.

NOTE: Intersil Pb-free products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination

finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-

free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

FN2969 Rev 11.01 Page 1 of 31

Jan 20, 2020

82C55A

Pinouts

82C55A (PDIP, CERDIP) 82C55A (CLCC)

TOP VIEW TOP VIEW

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7

WR

PA3 1 40 PA4

RD

CS

PA2 2 39 PA5 6 5 4 3 2 1 44 43 42 41 40

PA1 3 38 PA6

GND 7 39 NC

PA0 4 37 PA7

NC 8 38 RESET

RD 5 36 WR

A1 9 37 D0

CS 6 35 RESET

A0 10 36 D1

GND 7 34 D0

PC7 11 35 D2

A1 8 33 D1

PC6 12 34 D3

A0 9 32 D2

PC5 13 33 D4

PC7 10 31 D3

PC4 14 32 D5

PC6 11 30 D4

PC0 15 31 D6

PC5 12 29 D5

PC1 16 30 D7

PC4 13 28 D6

PC2 17 29 NC

PC0 14 27 D7

PC1 15 26 VCC 18 19 20 21 22 23 24 25 26 27 28

PC2 PB7

PB3

PC3

PB0

PB1

PB2

PB4

PB5

PB6

PB7

16 25

NC

VCC

PC3 17 24 PB6

PB0 18 23 PB5

PB1 19 22 PB4

PB2 20 21 PB3

82C55A (PLCC) 82C55A (MQFP)

TOP VIEW TOP VIEW

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7

WR

WR

RD

RD

NC

NC

6 5 4 3 2 1 44 43 42 41 40

CS 7 39 RESET

GND 8 38 D0 44 43 42 41 40 39 38 37 36 35 34

CS 1 33 RESET

A1 9 37 D1

A0 10 36 D2 GND 2 32 D0

PC7 11 35 D3 A1 3 31 D1

NC 12 34 NC

A0 4 30 D2

PC6 13 33 D4

PC5 14 D5 PC7 5 29 D3

32

PC4 15 31 D6 PC6 6 28 D4

PC0 16 30 D7

PC5 7 27 D5

PC1 17 29 VCC

PC4 8 26 D6

18 1920 21 22 23 24 25 26 27 28

PC0 9 25 D7

PC2

PC3

PB0

PB1

PB2

PB3

PB4

PB5

PB6

PB7

10 24

NC

PC1 VCC

PC2 11 23 PB7

12 13 14 15 16 17 18 19 20 21 22

PC3

PB0

PB1

PB2

PB3

PB4

PB5

PB6

NC

NC

NC

FN2969 Rev 11.01 Page 2 of 31

Jan 20, 2020

82C55A

Pin Description

SYMBOL TYPE DESCRIPTION

VCC VCC: The +5V power supply pin. A 0.1F capacitor between VCC and GND is recommended for decoupling.

GND GROUND

D0-D7 I/O DATA BUS: The Data Bus lines are bidirectional three-state pins connected to the system data bus.

RESET I RESET: A high on this input clears the control register and all ports (A, B, C) are set to the input mode with the “Bus

Hold” circuitry turned on.

CS I CHIP SELECT: Chip select is an active low input used to enable the 82C55A onto the Data Bus for CPU

communications.

RD I READ: Read is an active low input control signal used by the CPU to read status information or data via the data bus.

WR I WRITE: Write is an active low input control signal used by the CPU to load control words and data into the 82C55A.

A0-A1 I ADDRESS: These input signals, in conjunction with the RD and WR inputs, control the selection of one of the three

ports or the control word register. A0 and A1 are normally connected to the least significant bits of the Address Bus

A0, A1.

PA0-PA7 I/O PORT A: 8-bit input and output port. Both bus hold high and bus hold low circuitry are present on this port.

PB0-PB7 I/O PORT B: 8-bit input and output port. Bus hold high circuitry is present on this port.

PC0-PC7 I/O PORT C: 8-bit input and output port. Bus hold circuitry is present on this port.

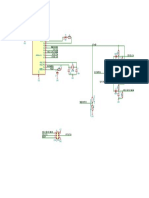

Functional Diagram

+5V GROUP A I/O

POWER PA7-PA0

SUPPLIES PORT A

GND GROUP A (8)

CONTROL

GROUP A

PORT C I/O

BIDIRECTIONAL PC7-PC4

UPPER

DATA BUS (4)

DATA BUS

D7-D0 BUFFER

8-BIT GROUP B

PORT C I/O

INTERNAL

PC3-PC0

DATA BUS LOWER

(4)

RD

READ

WR WRITE GROUP B

CONTROL CONTROL GROUP B I/O

A1

LOGIC PORT B PB7-PB0

A0 (8)

RESET

CS

FN2969 Rev 11.01 Page 3 of 31

Jan 20, 2020

82C55A

Functional Description I/O

PA7-

Data Bus Buffer POWER +5V GROUP A PA0

SUPPLIES GND GROUP A PORT A

This three-state bidirectional 8-bit buffer is used to interface the CONTROL (8)

82C55A to the system data bus. Data is transmitted or I/O

PC7-

received by the buffer upon execution of input or output GROUP A PC4

BIDIRECTIONAL PORT C

instructions by the CPU. Control words and status information DATA BUS UPPER

(4)

are also transferred through the data bus buffer. DATA

I/O

PC3-

D7-D0 BUS GROUP B PC0

Read/Write and Control Logic BUFFER 8-BIT PORT C

INTERNAL LOWER

The function of this block is to manage all of the internal and DATA BUS (4)

external transfers of both Data and Control or Status words. It RD I/O

WR READ PB7-

accepts inputs from the CPU Address and Control busses and WRITE

GROUP B PB0

A1 CONTROL GROUP B

in turn, issues commands to both of the Control Groups. CONTROL PORT B

A0 LOGIC (8)

RESET

(CS) Chip Select. A “low” on this input pin enables the

communication between the 82C55A and the CPU.

(RD) Read. A “low” on this input pin enables 82C55A to send CS

the data or status information to the CPU on the data bus. In FIGURE 1. 82C55A BLOCK DIAGRAM. DATA BUS BUFFER,

essence, it allows the CPU to “read from” the 82C55A. READ/WRITE, GROUP A & B CONTROL LOGIC

FUNCTIONS

(WR) Write. A “low” on this input pin enables the CPU to write

data or control words into the 82C55A. Group A and Group B Controls

The functional configuration of each port is programmed by the

(A0 and A1) Port Select 0 and Port Select 1. These input

systems software. In essence, the CPU “outputs” a control

signals, in conjunction with the RD and WR inputs, control the

word to the 82C55A. The control word contains information

selection of one of the three ports or the control word register.

such as “mode”, “bit set”, “bit reset”, etc., that initializes the

They are normally connected to the least significant bits of the

functional configuration of the 82C55A.

address bus (A0 and A1).

Each of the Control blocks (Group A and Group B) accepts

82C55A BASIC OPERATION

“commands” from the Read/Write Control logic, receives

INPUT OPERATION “control words” from the internal data bus and issues the

A1 A0 RD WR CS (READ)

proper commands to its associated ports.

0 0 0 1 0 Port A Data Bus

Control Group A - Port A and Port C upper (C7 - C4)

0 1 0 1 0 Port B Data Bus

Control Group B - Port B and Port C lower (C3 - C0)

1 0 0 1 0 Port C Data Bus

The control word register can be both written and read as

1 1 0 1 0 Control Word Data Bus

shown in the “Basic Operation” table. Figure 4 shows the

OUTPUT OPERATION control word format for both Read and Write operations. When

(WRITE)

the control word is read, bit D7 will always be a logic “1”, as this

0 0 1 0 0 Data Bus Port A implies control word mode information.

0 1 1 0 0 Data Bus Port B Ports A, B, and C

1 0 1 0 0 Data Bus Port C The 82C55A contains three 8-bit ports (A, B, and C). All can be

1 1 1 0 0 Data Bus Control configured to a wide variety of functional characteristics by the

system software but each has its own special features or

DISABLE FUNCTION

“personality” to further enhance the power and flexibility of the

X X X X 1 Data Bus Three-State 82C55A.

X X 1 1 0 Data Bus Three-State Port A One 8-bit data output latch/buffer and one 8-bit data

input latch. Both “pull-up” and “pull-down” bus-hold devices are

(RESET) Reset. A “high” on this input initializes the control present on Port A. See Figure 2A.

register to 9Bh and all ports (A, B, C) are set to the input mode.

Port B One 8-bit data input/output latch/buffer and one 8-bit

“Bus hold” devices internal to the 82C55A will hold the I/O port

data input buffer. See Figure 2B.

inputs to a logic “1” state with a maximum hold current of

400A. Port C One 8-bit data output latch/buffer and one 8-bit data

input buffer (no latch for input). This port can be divided into

FN2969 Rev 11.01 Page 4 of 31

Jan 20, 2020

82C55A

two 4-bit ports under the mode control. Each 4-bit port contains

ADDRESS BUS

a 4-bit latch and it can be used for the control signal output and

status signal inputs in conjunction with ports A and B. See CONTROL BUS

Figure 2B.

DATA BUS

INPUT MODE

MASTER

RESET

OR MODE RD, WR D7-D0 A0-A1

CHANGE CS

82C55A

INTERNAL EXTERNAL

DATA IN PORT A PIN MODE 0 C

B A

INTERNAL

DATA OUT

(LATCHED) 8 I/O 4 I/O 4 I/O 8 I/O

OUTPUT MODE

PB7-PB0 PC3-PC0 PC7-PC4 PA7-PA0

FIGURE 2A. PORT A BUS-HOLD CONFIGURATION

MODE 1 C

B A

VCC

RESET

OR MODE 8 I/O 8 I/O

CHANGE P

PB7-PB0 CONTROL CONTROL PA7-PA0

OR I/O OR I/O

MODE 2 C

B A

INTERNAL EXTERNAL

DATA IN PORT B, C BI-

8 I/O DIRECTIONAL

PIN

INTERNAL

DATA OUT PB7-PB0 PA7-PA0

(LATCHED) CONTROL

OUTPUT MODE

FIGURE 3. BASIC MODE DEFINITIONS AND BUS INTERFACE

FIGURE 2B. PORT B AND C BUS-HOLD CONFIGURATION

FIGURE 2. BUS-HOLD CONFIGURATION

CONTROL WORD

Operational Description D7 D6 D5 D4 D3 D2 D1 D0

GROUP B

Mode Selection

There are three basic modes of operation than can be selected PORT C (LOWER)

1 = INPUT

by the system software: 0 = OUTPUT

Mode 0 - Basic Input/Output PORT B

1 = INPUT

Mode 1 - Strobed Input/Output 0 = OUTPUT

Mode 2 - Bidirectional Bus MODE SELECTION

0 = MODE 0

When the reset input goes “high”, all ports will be set to the 1 = MODE 1

input mode with all 24 port lines held at a logic “one” level by

internal bus hold devices. After the reset is removed, the GROUP A

82C55A can remain in the input mode with no additional PORT C (UPPER)

initialization required. This eliminates the need to pull-up or 1 = INPUT

0 = OUTPUT

pull-down resistors in all-CMOS designs. The control word

PORT A

register will contain 9Bh. During the execution of the system 1 = INPUT

program, any of the other modes may be selected using a 0 = OUTPUT

single output instruction. This allows a single 82C55A to MODE SELECTION

00 = MODE 0

service a variety of peripheral devices with a simple software 01 = MODE 1

1X = MODE 2

maintenance routine. Any port programmed as an output port

is initialized to all zeros when the control word is written.

MODE SET FLAG

1 = ACTIVE

FIGURE 4. MODE DEFINITION FORMAT

FN2969 Rev 11.01 Page 5 of 31

Jan 20, 2020

82C55A

The modes for Port A and Port B can be separately defined, INTE Flip-Flop Definition

while Port C is divided into two portions as required by the Port (BIT-SET)-INTE is SET - Interrupt Enable

A and Port B definitions. All of the output registers, including

the status flip-flops, will be reset whenever the mode is (BIT-RESET)-INTE is Reset - Interrupt Disable

changed. Modes may be combined so that their functional NOTE: All Mask flip-flops are automatically reset during mode

definition can be “tailored” to almost any I/O structure. For selection and device Reset.

instance: Group B can be programmed in Mode 0 to monitor

simple switch closings or display computational results, Group Operating Modes

A could be programmed in Mode 1 to monitor a keyboard or Mode 0 (Basic Input/Output). This functional configuration

tape reader on an interrupt-driven basis. provides simple input and output operations for each of the

three ports. No handshaking is required, data is simply written

The mode definitions and possible mode combinations may

to or read from a specific port.

seem confusing at first, but after a cursory review of the

complete device operation a simple, logical I/O approach will Mode 0 Basic Functional Definitions:

surface. The design of the 82C55A has taken into account

• Two 8-bit ports and two 4-bit ports

things such as efficient PC board layout, control signal

definition vs. PC layout and complete functional flexibility to • Any Port can be input or output

support almost any peripheral device with no external logic.

• Outputs are latched

Such design represents the maximum use of the available

pins. • Inputs are not latched

Single Bit Set/Reset Feature (Figure 5) • 16 different Input/Output configurations possible

Any of the eight bits of Port C can be Set or Reset using a

single Output instruction. This feature reduces software MODE 0 PORT DEFINITION

requirements in control-based applications. A B GROUP A GROUP B

When Port C is being used as status/control for Port A or B, PORT C PORT C

these bits can be set or reset by using the Bit Set/Reset D4 D3 D1 D0 PORT A (Upper) # PORT B (Lower)

operation just as if they were output ports. 0 0 0 0 Output Output 0 Output Output

0 0 0 1 Output Output 1 Output Input

CONTROL WORD

0 0 1 0 Output Output 2 Input Output

D7 D6 D5 D4 D3 D2 D1 D0

BIT SET/RESET 0 0 1 1 Output Output 3 Input Input

X X X 1 = SET

0 = RESET 0 1 0 0 Output Input 4 Output Output

DON’T

CARE 0 1 0 1 Output Input 5 Output Input

BIT SELECT

0 1 2 3 4 5 6 7 0 1 1 0 Output Input 6 Input Output

0 1 0 1 0 1 0 1 B0 0 1 1 1 Output Input 7 Input Input

0 0 1 1 0 0 1 1 B1

0 0 0 0 1 1 1 1 B2 1 0 0 0 Input Output 8 Output Output

1 0 0 1 Input Output 9 Output Input

BIT SET/RESET FLAG

1 0 1 0 Input Output 10 Input Output

0 = ACTIVE

1 0 1 1 Input Output 11 Input Input

FIGURE 5. BIT SET/RESET FORMAT

1 1 0 0 Input Input 12 Output Output

1 1 0 1 Input Input 13 Output Input

Interrupt Control Functions

When the 82C55A is programmed to operate in mode 1 or 1 1 1 0 Input Input 14 Input Output

mode 2, control signals are provided that can be used as 1 1 1 1 Input Input 15 Input Input

interrupt request inputs to the CPU. The interrupt request

signals, generated from port C, can be inhibited or enabled by

setting or resetting the associated INTE flip-flop, using the bit

set/reset function of port C.

This function allows the programmer to enable or disable a

CPU interrupt by a specific I/O device without affecting any

other device in the interrupt structure.

FN2969 Rev 11.01 Page 6 of 31

Jan 20, 2020

82C55A

Mode 0 (Basic Input)

tRR

RD

tIR tHR

INPUT

tAR tRA

CS, A1, A0

D7-D0

tRD tDF

Mode 0 (Basic Output)

tWW

WR

tWD

tDW

D7-D0

tAW tWA

CS, A1, A0

OUTPUT

tWB

Mode 0 Configurations

CONTROL WORD #0 CONTROL WORD #2

D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5 D4 D3 D2 D1 D0

1 0 0 0 0 0 0 0 1 0 0 0 0 0 1 0

8 8

A PA7 - PA0 A PA7 - PA0

82C55A 82C55A

4 4

PC7 - PC4 PC7 - PC4

D7 - D0 C D7 - D0 C

4 4

PC3 - PC0 PC3 - PC0

8 8

B PB7 - PB0 B PB7 - PB0

CONTROL WORD #1 CONTROL WORD #3

D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5 D4 D3 D2 D1 D0

1 0 0 0 0 0 0 1 1 0 0 0 0 0 1 1

8 8

A PA7 - PA0 A PA7 - PA0

82C55A 82C55A

4 4

PC7 - PC4 PC7 - PC4

D7 - D0 C D7 - D0 C

4 4

PC3 - PC0 PC3 - PC0

8 8

B PB7 - PB0 B PB7 - PB0

FN2969 Rev 11.01 Page 7 of 31

Jan 20, 2020

82C55A

Mode 0 Configurations (Continued)

CONTROL WORD #4 CONTROL WORD #8

D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5 D4 D3 D2 D1 D0

1 0 0 0 1 0 0 0 1 0 0 1 0 0 0 0

8 8

A PA7 - PA0 A PA7 - PA0

82C55A 82C55A

4 4

PC7 - PC4 PC7 - PC4

D7 - D0 C D7 - D0 C

4 4

PC3 - PC0 PC3 - PC0

8 8

B PB7 - PB0 B PB7 - PB0

CONTROL WORD #5 CONTROL WORD #9

D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5 D4 D3 D2 D1 D0

1 0 0 0 1 0 0 1 1 0 0 1 0 0 0 1

8 8

A PA7 - PA0 A PA7 - PA0

82C55A 82C55A

4 4

PC7 - PC4 PC7 - PC4

D7 - D0 C D7 - D0 C

4 4

PC3 - PC0 PC3 - PC0

8 8

B PB7 - PB0 B PB7 - PB0

CONTROL WORD #6 CONTROL WORD #10

D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5 D4 D3 D2 D1 D0

1 0 0 0 1 0 1 0 1 0 0 1 0 0 1 0

8 8

A PA7 - PA0 A PA7 - PA0

82C55A 82C55A

4 4

PC7 - PC4 PC7 - PC4

D7 - D0 C D7 - D0 C

4 4

PC3 - PC0 PC3 - PC0

8 8

B PB7 - PB0 B PB7 - PB0

CONTROL WORD #7 CONTROL WORD #11

D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5 D4 D3 D2 D1 D0

1 0 0 0 1 0 1 1 1 0 0 1 0 0 1 1

8 8

A PA7 - PA0 A PA7 - PA0

82C55A 82C55A

4 4

PC7 - PC4 PC7 - PC4

D7 - D0 C D7 - D0 C

4 4

PC3 - PC0 PC3 - PC0

8 8

B PB7 - PB0 B PB7 - PB0

FN2969 Rev 11.01 Page 8 of 31

Jan 20, 2020

82C55A

Mode 0 Configurations (Continued)

CONTROL WORD #12 CONTROL WORD #14

D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5 D4 D3 D2 D1 D0

1 0 0 1 1 0 0 0 1 0 0 1 1 0 1 0

8 8

A PA7 - PA0 A PA7 - PA0

82C55A 82C55A

4 4

PC7 - PC4 PC7 - PC4

D7 - D0 C D7 - D0 C

4 4

PC3 - PC0 PC3 - PC0

8 8

B PB7 - PB0 B PB7 - PB0

CONTROL WORD #13 CONTROL WORD #15

D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5 D4 D3 D2 D1 D0

1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 1

8 8

A PA7 - PA0 A PA7 - PA0

82C55A 82C55A

4 4

PC7 - PC4 PC7 - PC4

D7 - D0 C D7 - D0 C

4 4

PC3 - PC0 PC3 - PC0

8 8

B PB7 - PB0 B PB7 - PB0

Operating Modes

MODE 1 (PORT A)

Mode 1 - (Strobed Input/Output). This functional configuration

provides a means for transferring I/O data to or from a PA7-PA0 8

CONTROL WORD

specified port in conjunction with strobes or “hand shaking” D7 D6 D5 D4 D3 D2 D1 D0 INTE STBA

PC4

signals. In mode 1, port A and port B use the lines on port C to A

1 0 1 1 1/0

generate or accept these “hand shaking” signals. PC6, PC7

PC5 IBFA

1 = INPUT

Mode 1 Basic Function Definitions: 0 = OUTPUT

PC3 INTRA

• Two Groups (Group A and Group B)

RD 2

• Each group contains one 8-bit port and one 4-bit control/data PC6, PC7 I/O

port

• The 8-bit data port can be either input or output. Both inputs

MODE 1 (PORT B)

and outputs are latched.

PB7-PB0 8

• The 4-bit port is used for control and status of the 8-bit port. CONTROL WORD

D7 D6 D5 D4 D3 D2 D1 D0 INTE PC2

Input Control Signal Definition 1 1 1

B STBB

(Figures 6 and 7) PC1 IBFB

STB (Strobe Input)

A “low” on this input loads data into the input latch. PC0 INTRB

RD

IBF (Input Buffer Full F/F)

A “high” on this output indicates that the data has been loaded

into the input latch: in essence, an acknowledgment. IBF is set FIGURE 6. MODE 1 INPUT

by STB input being low and is reset by the rising edge of the

RD input.

FN2969 Rev 11.01 Page 9 of 31

Jan 20, 2020

82C55A

tST

STB

tSIB

IBF

tSIT tRIB

INTR

tRIT

RD

tPH

INPUT FROM

PERIPHERAL

tPS

FIGURE 7. MODE 1 (STROBED INPUT)

INTR (Interrupt Request) INTE A

A “high” on this output can be used to interrupt the CPU when Controlled by Bit Set/Reset of PC6.

an input device is requesting service. INTR is set by the

INTE B

condition: STB is a “one”, IBF is a “one” and INTE is a “one”. It

is reset by the falling edge of RD. This procedure allows an Controlled by Bit Set/Reset of PC2.

input device to request service from the CPU by simply NOTE:

strobing its data into the port. 1. To strobe data into the peripheral device, the user must operate the

strobe line in a hand shaking mode. The user needs to send OBF

INTE A to the peripheral device, generates an ACK from the peripheral

Controlled by bit set/reset of PC4. device and then latch data into the peripheral device on the rising

edge of OBF.

INTE B

Controlled by bit set/reset of PC2. MODE 1 (PORT A)

Output Control Signal Definition PA7-PA0 8

CONTROL WORD

(Figure 8 and 9) D7 D6 D5 D4 D3 D2 D1 D0

PC7 OBFA

OBF - (Output Buffer Full F/F). The OBF output will go “low” 1 0 1 1 1/0

INTE PC6 ACKA

to indicate that the CPU has written data out to the specified PC4, PC5 A

port. This does not mean valid data is sent out of the port at 1 = INPUT

0 = OUTPUT

this time since OBF can go true before data is available. Data INTRA

PC3

is guaranteed valid at the rising edge of OBF, (See Note 1).

WR 2

The OBF F/F will be set by the rising edge of the WR input and PC4, PC5

reset by ACK input being low.

ACK - (Acknowledge Input). A “low” on this input informs the

82C55A that the data from Port A or Port B is ready to be MODE 1 (PORT B)

accepted. In essence, a response from the peripheral device PB7-PB0 8

CONTROL WORD

indicating that it is ready to accept data, (See Note 1).

D7 D6 D5 D4 D3 D2 D1 D0

PC1 OBFB

INTR - (Interrupt Request). A “high” on this output can be used 1 1 0

to interrupt the CPU when an output device has accepted data INTE PC2 ACKB

B

transmitted by the CPU. INTR is set when ACK is a “one”, OBF

is a “one” and INTE is a “one”. It is reset by the falling edge of

WR. PC0 INTRB

WR

FIGURE 8. MODE 1 OUTPUT

FN2969 Rev 11.01 Page 10 of 31

Jan 20, 2020

82C55A

tWOB

WR

tAOB

OBF

INTR tWIT

ACK

tAK tAIT

OUTPUT

tWB

FIGURE 9. MODE 1 (STROBED OUTPUT)

PA7-PA0 8 PA7-PA0 8

RD PC4 STBA WR PC7 OBFA

CONTROL WORD CONTROL WORD

PC5 IIBFA PC6 ACKA

D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5 D4 D3 D2 D1 D0

1 0 1 1 1/0 1 0 PC3 INTRA 1 0 1 0 1/0 1 1 PC3 INTRA

2 2

PC6, PC7 PC6, PC7 I/O PC4, PC5 PC4, PC5 I/O

1 = INPUT 1 = INPUT

0 = OUTPUT PB7, PB0 8 0 = OUTPUT PB7, PB0 8

WR PC1 OBFB RD PC2 STBB

PC2 ACKB PC1 IBFB

PC0 INTRB PC0 INTRB

PORT A - (STROBED INPUT) PORT A - (STROBED OUTPUT)

PORT B - (STROBED OUTPUT) PORT B - (STROBED INPUT)

Combinations of Mode 1: Port A and Port B can be individually defined as input or output in Mode 1 to support a wide variety of strobed I/O applications.

FIGURE 10. COMBINATIONS OF MODE 1

Operating Modes Output Operations

OBF - (Output Buffer Full). The OBF output will go “low” to

Mode 2 (Strobed Bidirectional Bus I/O)

indicate that the CPU has written data out to port A.

This functional configuration provides a means for

communicating with a peripheral device or structure on a single ACK - (Acknowledge). A “low” on this input enables the three-

8-bit bus for both transmitting and receiving data (bidirectional state output buffer of port A to send out the data. Otherwise, the

bus I/O). “Hand shaking” signals are provided to maintain proper output buffer will be in the high impedance state.

bus flow discipline similar to Mode 1. Interrupt generation and INTE 1 - (The INTE flip-flop associated with OBF). Controlled

enable/disable functions are also available. by bit set/reset of PC4.

Mode 2 Basic Functional Definitions:

Input Operations

• Used in Group A only STB - (Strobe Input). A “low” on this input loads data into the

• One 8-bit, bidirectional bus Port (Port A) and a 5-bit control input latch.

Port (Port C)

IBF - (Input Buffer Full F/F). A “high” on this output indicates

• Both inputs and outputs are latched

that data has been loaded into the input latch.

• The 5-bit control port (Port C) is used for control and status

for the 8-bit, bidirectional bus port (Port A) INTE 2 - (The INTE flip-flop associated with IBF). Controlled by

bit set/reset of PC4.

Bidirectional Bus I/O Control Signal Definition

(Figures 11, 12, 13, 14)

INTR - (Interrupt Request). A high on this output can be used

to interrupt the CPU for both input or output operations.

FN2969 Rev 11.01 Page 11 of 31

Jan 20, 2020

82C55A

CONTROL WORD

D7 D6 D5 D4 D3 D2 D1 D0

PC3 INTRA

1 1 1/0 1/0 1/0

PA7-PA0 8

PC7 OBFA

INTE PC6

PC2-PC0 1 ACKA

1 = INPUT

0 = OUTPUT

INTE

PORT B 2 PC4 STBA

1 = INPUT

0 = OUTPUT PC5 IBFA

WR

GROUP B MODE

0 = MODE 0

1 = MODE 1 3

PC2-PC0 I/O

RD

FIGURE 11. MODE CONTROL WORD FIGURE 12. MODE 2

DATA FROM

CPU TO 82C55A

WR

tAOB

OBF

tWOB

INTR

tAK

ACK

tST

STB

tSIB

IBF

tAD

tKD

tPS

PERIPHERAL

BUS

tPH tRIB

RD DATA FROM DATA FROM

PERIPHERAL TO 82C55A 82C55A TO PERIPHERAL

DATA FROM

82C55A TO CPU

NOTE: Any sequence where WR occurs before ACK and STB occurs before RD is permissible. (INTR = IBF MASK STB RD + OBF MASK

ACK WR)

FIGURE 13. MODE 2 (BIDIRECTIONAL)

FN2969 Rev 11.01 Page 12 of 31

Jan 20, 2020

82C55A

MODE 2 AND MODE 0 (INPUT) MODE 2 AND MODE 0 (OUTPUT)

PC3 INTRA PC3 INTRA

PA7-PA0 8 PA7-PA0 8

PC7 OBFA PC7 OBFA

CONTROL WORD CONTROL WORD

D7 D6 D5 D4 D3 D2 D1 D0 PC6 ACKA D7 D6 D5 D4 D3 D2 D1 D0 PC6 ACKA

1 1 0 1 1/0 1 1 0 0 1/0

PC4 STBA PC4 STBA

PC2-PC0 PC5 IBFA PC2-PC0 PC5 IBFA

1 = INPUT 1 = INPUT

0 = OUTPUT 3 0 = OUTPUT 3

PC2-PC0 I/O PC2-PC0 I/O

RD RD

PB7-PB0 8 PB7, PB0 8

WR WR

MODE 2 AND MODE 1 (OUTPUT) MODE 2 AND MODE 1 (INPUT)

PC3 INTRA PC3 INTRA

PA7-PA0 8 PA7-PA0 8

PC7 OBFA PC7 OBFA

CONTROL WORD ACKA CONTROL WORD ACKA

PC6 PC6

D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5 D4 D3 D2 D1 D0

PC4 STBA PC4 STBA

1 1 1 0 1 1 1 1

PC5 IBFA PC5 IBFA

PB7-PB0 8 PB7-PB0 8

PC1 OBFB PC2 STBB

RD RD

PC2 ACKB PC1 IBFB

PC0 INTRB PC0 INTRB

WR WR

FIGURE 14. MODE 2 COMBINATIONS

FN2969 Rev 11.01 Page 13 of 31

Jan 20, 2020

82C55A

MODE DEFINITION SUMMARY

MODE 0 MODE 1 MODE 2

IN OUT IN OUT GROUP A ONLY

PA0 In Out In Out

PA1 In Out In Out

PA2 In Out In Out

PA3 In Out In Out

PA4 In Out In Out

PA5 In Out In Out

PA6 In Out In Out

PA7 In Out In Out

PB0 In Out In Out

PB1 In Out In Out

PB2 In Out In Out

Mode 0

PB3 In Out In Out or Mode 1

PB4 In Out In Out Only

PB5 In Out In Out

PB6 In Out In Out

PB7 In Out In Out

PC0 In Out INTRB INTRB I/O

PC1 In Out IBFB OBFB I/O

PC2 In Out STBB ACKB I/O

PC3 In Out INTRA INTRA INTRA

PC4 In Out STBA I/O STBA

PC5 In Out IBFA I/O IBFA

PC6 In Out I/O ACKA ACKA

PC7 In Out I/O OBFA OBFA

Special Mode Combination Considerations INPUT CONFIGURATION

There are several combinations of modes possible. For any D7 D6 D5 D4 D3 D2 D1 D0

combination, some or all of Port C lines are used for control or

I/O I/O IBFA INTEA INTRA INTEB IBFB INTRB

status. The remaining bits are either inputs or outputs as

defined by a “Set Mode” command. GROUP A GROUP B

During a read of Port C, the state of all the Port C lines, except OUTPUT CONFIGURATION

the ACK and STB lines, will be placed on the data bus. In place D7 D6 D5 D4 D3 D2 D1 D0

of the ACK and STB line states, flag status will appear on the

data bus in the PC2, PC4, and PC6 bit positions as illustrated OBFA INTEA I/O I/O INTRA INTEB OBFB INTRB

by Figure 17.

GROUP A GROUP B

Through a “Write Port C” command, only the Port C pins FIGURE 15. MODE 1 STATUS WORD FORMAT

programmed as outputs in a Mode 0 group can be written. No

other pins can be affected by a “Write Port C” command, nor D7 D6 D5 D4 D3 D2 D1 D0

can the interrupt enable flags be accessed. To write to any Port

OBFA INTE1 IBFA INTE2 INTRA X X X

C output programmed as an output in Mode 1 group or to

change an interrupt enable flag, the “Set/Reset Port C Bit” GROUP A GROUP B

command must be used. (Defined by Mode 0 or Mode 1 Selection)

With a “Set/Reset Port C Bit” command, any Port C line FIGURE 16. MODE 2 STATUS WORD FORMAT

programmed as an output (including IBF and OBF) can be

written, or an interrupt enable flag can be either set or reset. Current Drive Capability

Port C lines programmed as inputs, including ACK and STB Any output on Port A, B or C can sink or source 2.5mA. This

lines, associated with Port C are not affected by a “Set/Reset feature allows the 82C55A to directly drive Darlington type

Port C Bit” command. Writing to the corresponding Port C bit drivers and high-voltage displays that require such sink or

positions of the ACK and STB lines with the “Set Reset Port C source current.

Bit” command will affect the Group A and Group B interrupt

enable flags, as illustrated in Figure 17. Reading Port C Status (Figures 15 and 16)

In Mode 0, Port C transfers data to or from the peripheral

device. When the 82C55A is programmed to function in Modes

FN2969 Rev 11.01 Page 14 of 31

Jan 20, 2020

82C55A

1 or 2, Port C generates or accepts “hand shaking” signals with Applications of the 82C55A

the peripheral device. Reading the contents of Port C allows

The 82C55A is a very powerful tool for interfacing peripheral

the programmer to test or verify the “status” of each peripheral

equipment to the microcomputer system. It represents the

device and change the program flow accordingly.

optimum use of available pins and is flexible enough to

There is not a special instruction to read the status information interface almost any I/O device without the need for additional

from Port C. A normal read operation of Port C is executed to external logic.

perform this function.

Each peripheral device in a microcomputer system usually has

a “service routine” associated with it. The routine manages the

INTERRUPT ALTERNATE PORT C software interface between the device and the CPU. The

ENABLE FLAG POSITION PIN SIGNAL (MODE) functional definition of the 82C55A is programmed by the I/O

INTE B PC2 ACKB (Output Mode 1) service routine and becomes an extension of the system

or STBB (Input Mode 1) software. By examining the I/O devices interface

INTE A2 PC4 STBA (Input Mode 1 or Mode characteristics for both data transfer and timing, and matching

2) this information to the examples and tables in the detailed

INTE A1 PC6 ACKA (Output Mode 1 or

operational description, a control word can easily be developed

Mode 2) to initialize the 82C55A to exactly “fit” the application. Figures

18 through 24 present a few examples of typical applications of

FIGURE 17. INTERRUPT ENABLE FLAGS IN MODES 1 AND 2

the 82C55A.

INTERRUPT

REQUEST

PC3 PA0

PA1

HIGH SPEED

PA2 PRINTER

PA3

PA4

PA5

MODE 1

PA6

(OUTPUT)

PA7 HAMMER

RELAYS

PC7 DATA READY

PC6 ACK

PC5 PAPER FEED

PC4 FORWARD/REV.

82C55A

PB0

PB1

PB2

PB3

PB4

MODE 1 PB5 PAPER FEED

(OUTPUT) PB6 FORWARD/REV.

PB7 RIBBON

CARRIAGE SEN.

PC1 DATA READY

PC2 ACK

PC0

INTERRUPT CONTROL LOGIC

REQUEST AND DRIVERS

FIGURE 18. PRINTER INTERFACE

FN2969 Rev 11.01 Page 15 of 31

Jan 20, 2020

82C55A

INTERRUPT

REQUEST

PC3 PA0 R0

PA1 R1

PA2 R2

FULLY

PA3 R3 DECODED INTERRUPT

PA4 R4 KEYBOARD REQUEST

PA5 R5

MODE 1 PC3 PA0 R0

(INPUT) PA6 SHIFT

PA1 R1

PA7 CONTROL

PA2 R2

FULLY

PA3 R3 DECODED

PC4 STROBE

PA4 R4 KEYBOARD

PC5 ACK

PA5 R5

MODE 1 PA6

(INPUT) SHIFT

82C55A PA7 CONTROL

PB0 B0

PC4 STROBE

PB1 B1

82C55A PC5 ACK

PB2 B2 BURROUGHS PC6 BUST LT

PB3 B3 SELF-SCAN

DISPLAY PC7 TEST LT

PB4 B4

MODE 1 PB5 B5

PB0 TERMINAL

(OUTPUT) PB6 BACKSPACE ADDRESS

PB1

PB7 CLEAR PB2

PB3

PC1 DATA READY MODE 0

(INPUT) PB4

PC2 ACK PB5

PC6 BLANKING PB6

PC7 CANCEL WORD PB7

INTERRUPT

REQUEST

FIGURE 19. KEYBOARD AND DISPLAY INTERFACE FIGURE 20. KEYBOARD AND TERMINAL ADDRESS

INTERFACE

INTERRUPT

REQUEST

PA0 LSB PC3

PA0 R0

PA1 PA1 R1

PA2 PA2 R2 CRT CONTROLLER

PA3 PA3 R3 ² CHARACTER GEN.

PA4 12-BIT PA4 R4 ² REFRESH BUFFER

D/A

MODE 0 PA5 CONVERTER

PA5 R5 ² CURSOR CONTROL

(OUTPUT) PA6 MODE 1 PA6

(DAC) ANALOG (OUTPUT) SHIFT

PA7 OUTPUT PA7 CONTROL

PC4

PC5 PC7 DATA READY

PC6 PC6 ACK

PC7 MSB PC5 BLANKED

82C55A PC4 BLACK/WHITE

PC0 STB DATA 82C55A

PC1

BIT PC2 ROW STB

SET/RESET PC2 SAMPLE EN PC1 COLUMN STB

PC3 STB PC0 CURSOR H/V STB

PB0 LSB PB0

PB1 8-BIT MODE 0 PB1

ANALOG

PB2 A/D INPUT (OUTPUT) PB2

CONVERTER

MODE 0 PB3 (ADC) PB3 CURSOR/ROW/COLUMN

(INPUT) PB4 PB4 ADDRESS

H&V

PB5 PB5

PB6 PB6

PB7 MSB PB7

FIGURE 21. DIGITAL TO ANALOG, ANALOG TO DIGITAL FIGURE 22. BASIC CRT CONTROLLER INTERFACE

FN2969 Rev 11.01 Page 16 of 31

Jan 20, 2020

82C55A

INTERRUPT INTERRUPT

REQUEST REQUEST

PC3 PA0 D0 PC3 PA0 R0

PA1 D1 PA1 R1

PA2 D2 PA2 R2

PA3 FLOPPY DISK PA3 B LEVEL

D3 CONTROLLER R3 PAPER

PA4 D4 AND DRIVE PA4 R4 TAPE

PA5 D5 PA5 R5 READER

MODE 1

MODE 2 PA6 D6 (INPUT) PA6 R6

PA7 D7 PA7 R7

PC4 DATA STB PC4 STB

PC5 ACK (IN) PC5 ACK

PC7 DATA READY PC6 STOP/GO

PC6 ACK (OUT)

82C55A 82C55A MACHINE TOOL

PC2 TRACK “0” SENSOR PC0 START/STOP

PC1 SYNC READY MODE 0 PC1 LIMIT SENSOR (H/V)

PC0 (INPUT) PC2

INDEX OUT OF FLUID

PB0 ENGAGE HEAD PB0 CHANGE TOOL

PB1 FORWARD/REV. PB1 LEFT/RIGHT

PB2 READ ENABLE PB2 UP/DOWN

MODE 0 PB3 WRITE ENABLE MODE 0 PB3 HOR. STEP STROBE

(OUTPUT) PB4 DISC SELECT (OUTPUT) PB4 VERT. STEP STROBE

PB5 ENABLE CRC PB5 SLEW/STEP

PB6 TEST PB6 FLUID ENABLE

PB7 BUSY LT PB7 EMERGENCY STOP

FIGURE 23. BASIC FLOPPY DISC INTERFACE FIGURE 24. MACHINE TOOL CONTROLLER INTERFACE

FN2969 Rev 11.01 Page 17 of 31

Jan 20, 2020

82C55A

Absolute Maximum Ratings TA = +25°C Thermal Information

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +8.0V Thermal Resistance (Typical, Note 1) JA (°C/W) JC(°C/W)

Input, Output or I/O Voltage . . . . . . . . . . . . . GND-0.5V to VCC+0.5V CERDIP Package. . . . . . . . . . . . . . . . . 50 10

ESD Classification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Class 1 CLCC Package . . . . . . . . . . . . . . . . . . 65 14

PDIP Package . . . . . . . . . . . . . . . . . . . 50 N/A

Operating Conditions PLCC Package. . . . . . . . . . . . . . . . . . . 55 N/A

MQFP Package . . . . . . . . . . . . . . . . . . 62 N/A

Voltage Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +4.5V to 5.5V

Maximum Storage Temperature Range. . . . . . . . . .-65°C to +150°C

Operating Temperature Range

CX82C55A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0°C to 70°C Maximum Junction Temperature

CDIP Packages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +175°C

IX82C55A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-40°C to 85°C

PDIP Packages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +150°C

MX82C55A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-55°C to 125°C

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . +300°C

(PLCC and MQFP Lead Tips Only)

Die Characteristics

Gate Count. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1000 Gates

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. JA is measured with the component mounted on an evaluation PC board in free air.

Electrical Specifications VCC = 5.0V ±10%; TA = Operating Temperature Range

SYMBOL PARAMETER TEST CONDITIONS MIN MAX UNITS

VIH Logical One Input Voltage 2.0 - V

2.2

VIL Logical Zero Input Voltage - 0.8 V

VOH Logical One Output Voltage IOH = -2.5mA, 3.0 - V

IOH = -100A VCC -0.4

VOL Logical Zero Output Voltage IOL +2.5mA - 0.4 V

II Input Leakage Current VIN = VCC or GND, RD, CS, A1, A0, RESET, WR -1.0 +1.0 A

IO I/O Pin Leakage Current VO = VCC or GND, D0 - D7 -10 +10 A

IBHH Bus Hold High Current VO = 3.0V. Ports A, B, C

TA = -55°C -50 -450 A

TA = +128°C -50 -400 A

IBHL Bus Hold Low Current VO = 1.0V. Port A ONLY

TA = -55°C 50 450 A

TA = +128°C 50 400 A

IDAR Darlington Drive Current Ports A, B, C. Test Condition 3 -2.5 Note 2, 4 mA

ICCSB Standby Power Supply Current VCC = 5.5V, VIN = VCC or GND. Output Open - 10 A

ICCOP Operating Power Supply Current TA = +25°C, VCC = 5.0V, Typical (See Note 3) - 1 mA/MHz

NOTES:

2. No internal current limiting exists on Port Outputs. A resistor must be added externally to limit the current.

3. ICCOP = 1mA/MHz of Peripheral Read/Write cycle time. (Example: 1.0s I/O Read/Write cycle time = 1mA).

4. Tested as VOH at -2.5mA.

Capacitance TA = +25°C

SYMBOL PARAMETER TYPICAL UNITS TEST CONDITIONS

CIN Input Capacitance 10 pF FREQ = 1MHz, All Measurements are referenced to

device GND

CI/O I/O Capacitance 20 pF

FN2969 Rev 11.01 Page 18 of 31

Jan 20, 2020

82C55A

AC Electrical Specifications VCC = +5V 10%, GND = 0V; TA = Operating Temperature Range

82C55A-5 82C55A

TEST

SYMBOL PARAMETER MIN MAX MIN MAX UNITS CONDITIONS

READ TIMING

(1) tAR Address Stable Before RD 0 - 0 - ns

(2) tRA Address Stable After RD 0 - 0 - ns

(3) tRR RD Pulse Width 250 - 150 - ns

(4) tRD Data Valid From RD - 200 - 120 ns 1

(5) tDF Data Float After RD 10 75 10 75 ns 2

(6) tRV Time Between RDs and/or WRs 300 - 300 - ns

WRITE TIMING

(7) tAW Address Stable Before WR 0 - 0 - ns

(8) tWA Address Stable After WR 20 - 20 - ns

(9) tWW WR Pulse Width 100 - 100 - ns

(10) tDW Data Valid to WR High 100 - 100 - ns

(11) tWD Data Valid After WR High 30 - 30 - ns

OTHER TIMING

(12) tWB WR = 1 to Output - 350 - 350 ns 1

(13) tIR Peripheral Data Before RD 0 - 0 - ns

(14) tHR Peripheral Data After RD 0 - 0 - ns

(15) tAK ACK Pulse Width 200 - 200 - ns

(16) tST STB Pulse Width 100 - 100 - ns

(17) tPS Peripheral Data Before STB High 20 - 20 - ns

(18) tPH Peripheral Data After STB High 50 - 50 - ns

(19) tAD ACK = 0 to Output - 175 - 175 ns 1

(20) tKD ACK = 1 to Output Float 20 250 20 250 ns 2

(21) tWOB WR = 1 to OBF = 0 - 150 - 150 ns 1

(22) tAOB ACK = 0 to OBF = 1 - 150 - 150 ns 1

(23) tSIB STB = 0 to IBF = 1 - 150 - 150 ns 1

(24) tRIB RD = 1 to IBF = 0 - 150 - 150 ns 1

(25) tRIT RD = 0 to INTR = 0 - 200 - 200 ns 1

(26) tSIT STB = 1 to INTR = 1 - 150 - 150 ns 1

(27) tAIT ACK = 1 to INTR = 1 - 150 - 150 ns 1

(28) tWIT WR = 0 to INTR = 0 - 200 - 200 ns 1

(29) tRES Reset Pulse Width 500 - 500 - ns 1, (Note)

NOTE: Period of initial Reset pulse after power-on must be at least 50sec. Subsequent Reset pulses may be 500ns minimum.

FN2969 Rev 11.01 Page 19 of 31

Jan 20, 2020

82C55A

Timing Waveforms

tRR (3)

RD

tIR (13) tHR (14)

INPUT

tAR (1) tRA (2)

CS, A1, A0

D7-D0

tRD (4) tDF (5)

FIGURE 25. MODE 0 (BASIC INPUT)

tWW (9)

WR

tWD (11)

tDW

(10)

D7-D0

tAW (7) tWA (8)

CS, A1, A0

OUTPUT

tWS (12)

FIGURE 26. MODE 0 (BASIC OUTPUT)

tST (16)

STB

tSIB

IBF (23)

tSIT

(26) tRIB (24)

INTR tRIT

(25)

RD tPH

(18)

INPUT FROM

PERIPHERAL

tPS (17)

FIGURE 27. MODE 1 (STROBED INPUT)

FN2969 Rev 11.01 Page 20 of 31

Jan 20, 2020

82C55A

Timing Waveforms (Continued)

tWOB (21)

WR

tAOB (22)

OBF

INTR tWIT

(28)

ACK

tAK (15) tAIT (27)

OUTPUT

tWB (12)

FIGURE 28. MODE 1 (STROBED OUTPUT)

DATA FROM

CPU TO 82C55A

WR

(NOTE)

tAOB

(22)

OBF

tWOB

(21)

INTR

tAK

(15)

ACK

tST

(16)

STB

(NOTE)

tSIB

IBF (23)

tAD (19)

tKD

tPS (17) (20)

PERIPHERAL

BUS

tPH (18) tRIB (24)

RD

DATA FROM DATA FROM

PERIPHERAL TO 82C55A 82C55A TO PERIPHERAL

DATA FROM

82C55A TO CPU

FIGURE 29. MODE 2 (BIDIRECTIONAL)

NOTE: Any sequence where WR occurs before ACK and STB occurs before RD is permissible. (INTR = IBF MASK STB RD OBF MASK

ACK WR)

FN2969 Rev 11.01 Page 21 of 31

Jan 20, 2020

82C55A

Timing Waveforms (Continued)

A0-A1,

CS A0-A1,

CS

tAW (7) tWA (8)

tAR (1) tRA (2)

DATA

BUS tRR (3)

RD

tDW (10) tWD (11)

(4) tRD tDF (5)

WR

DATA VALID

BUS

tWW (9) HIGH IMPEDANCE

FIGURE 30. WRITE TIMING FIGURE 31. READ TIMING

AC Test Circuit AC Testing Input, Output Waveforms

V1 INPUT OUTPUT

VIH + 0.4V VOH

R1 1.5V 1.5V

OUTPUT FROM TEST VIL - 0.4V VOL

DEVICE UNDER POINT

TEST AC Testing: All AC Parameters tested as per test circuits. Input RISE

R2 C1

(SEE NOTE) and FALL times are driven at 1ns/V.

TEST CONDITION DEFINITION TABLE

TEST CONDITION V1 R1 R2 C1

1 1.7V 523 Open 150pF

NOTE: Includes STRAY and JIG Capacitance

2 VCC 2k 1.7k 50pF

3 1.5V 750 Open 50pF

FN2969 Rev 11.01 Page 22 of 31

Jan 20, 2020

82C55A

Burn-In Circuits

CERDIP CLCC

F11

F12

F13

F14

F6 1 40 F11

F3

F4

F9

F8

F7

F6

F2

F7 2 39 F12

F8 3 38 F13

F9 4 37 F14

F4 5 36 F2 6 5 4 3 2 1 44 43 42 41 40

F3 6 35 F5 GND 7 39

GND 7 34 F15 8 38 F5

F0 8 33 F11 F0 9 37 F15

F1 9 32 F12 F1 10 36 F11

F10 10 31 F13 F10 11 35 F12

11 30 F6 12 34 F13

F6 F14

F7 13 33 F14

F7 12 29 F15

F8 14 32 F15

F8 13 28 F11

F9 15 31 F11

F9 14 27 F12

VCC F10 16 30 F12

F10 15 26

F6 17 29

F6 16 25 F13 C1 18 19 20 21 22 23 24 25 26 27 28

F7 17 24 F14

F8 18 23 F15

F9 19 22 F11 C1

F10 20 21 F12

F7

F8

F9

F10

F12

F15

F14

F13

F11

VCC

NOTES: NOTES:

1. VCC = 5.5V 0.5V 1. C1 = 0.01F minimum

2. VIH = 4.5V 10% 2. All resistors are 47k 5%

3. VIL = -0.2V to 0.4V 3. f0 = 100kHz 10%

4. GND = 0V 4. f1 = f0 2; f2 = f1 2; . . . ; f15 = f14 2

FN2969 Rev 11.01 Page 23 of 31

Jan 20, 2020

82C55A

Die Characteristics GLASSIVATION:

Type: SiO2

METALLIZATION:

Thickness: 8kÅ 1kÅ

Type: Silicon - Aluminum

Thickness: 11kÅ 1kÅ

Metallization Mask Layout

82C55A

RD PA0 PA1 PA2 PA3 PA4 PA5 PA6 PA7 WR

CS RESET

D0

GND

D1

A1 D2

A0 D3

PC7 D4

PC6 D5

PC5 D6

PC4 D7

PC0

VCC

PC1

PC2 PC3 PB0 PB1 PB2 PB3 PB4 PB5 PB6 PB7

FN2969 Rev 11.01 Page 24 of 31

Jan 20, 2020

82C55A

Revision History

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to the web to make

sure that you have the latest revision.

DATE REVISION CHANGE

Jan 20, 2020 11.01 Updated ordering Information Table on page 1.

Removed About Intersil section.

Updated disclaimer.

Dec 8, 2015 11.00 - Ordering Information Table on page 1.

- Added Revision History.

- Added About Intersil Verbiage.

FN2969 Rev 11.01 Page 25 of 31

Jan 20, 2020

82C55A

Package Outline Drawings

N

E40.6 (JEDEC MS-011-AC ISSUE B)

E1 40 LEAD DUAL-IN-LINE PLASTIC PACKAGE (PDIP)

INDEX

AREA 1 2 3 N/2

INCHES MILLIMETERS

-B- SYMBOL MIN MAX MIN MAX NOTES

-A- A - 0.250 - 6.35 4

D E

BASE A1 0.015 - 0.39 - 4

PLANE A2

-C- A A2 0.125 0.195 3.18 4.95 -

SEATING

PLANE B 0.014 0.022 0.356 0.558 -

L C

L

B1 0.030 0.070 0.77 1.77 8

D1 A1 eA

D1

B1 e C 0.008 0.015 0.204 0.381 -

eC C

B D 1.980 2.095 50.3 53.2 5

eB

0.010 (0.25) M C A B S

D1 0.005 - 0.13 - 5

E 0.600 0.625 15.24 15.87 6

NOTES:

5. Controlling Dimensions: INCH. In case of conflict between English E1 0.485 0.580 12.32 14.73 5

and Metric dimensions, the inch dimensions control. e 0.100 BSC 2.54 BSC -

6. Dimensioning and tolerancing per ANSI Y14.5M-1982. eA 0.600 BSC 15.24 BSC 6

7. Symbols are defined in the “MO Series Symbol List” in Section 2.2

eB - 0.700 - 17.78 7

of Publication No. 95.

8. Dimensions A, A1 and L are measured with the package seated in L 0.115 0.200 2.93 5.08 4

JEDEC seating plane gauge GS-3. N 40 40 9

9. D, D1, and E1 dimensions do not include mold flash or protrusions. Rev. 0 12/93

Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

10. E and eA are measured with the leads constrained to be per-

pendicular to datum -C- .

11. eB and eC are measured at the lead tips with the leads uncon-

strained. eC must be zero or greater.

12. B1 maximum dimensions do not include dambar protrusions.

Dambar protrusions shall not exceed 0.010 inch (0.25mm).

13. N is the maximum number of terminal positions.

14. Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3,

E42.6 will have a B1 dimension of 0.030 - 0.045 inch (0.76 - 1.14mm).

FN2969 Rev 11.01 Page 26 of 31

Jan 20, 2020

82C55A

c1 LEAD FINISH F40.6 MIL-STD-1835 GDIP1-T40 (D-5, CONFIGURATION A)

-A- -D- 40 LEAD CERAMIC DUAL-IN-LINE FRIT SEAL PACKAGE

BASE INCHES MILLIMETERS

(c)

METAL

E SYMBOL MIN MAX MIN MAX NOTES

b1 A - 0.225 - 5.72 -

M M

-B- (b)

b 0.014 0.026 0.36 0.66 2

SECTION A-A

b1 0.014 0.023 0.36 0.58 3

bbb S C A-B S D S

b2 0.045 0.065 1.14 1.65 -

D

BASE b3 0.023 0.045 0.58 1.14 4

PLANE Q

-C- A c 0.008 0.018 0.20 0.46 2

SEATING

PLANE L c1 0.008 0.015 0.20 0.38 3

S1 D - 2.096 - 53.24 5

A A eA

b2 E 0.510 0.620 12.95 15.75 5

b e eA/2 c e 0.100 BSC 2.54 BSC -

ccc M C A-B S D S aaa M C A - B S D S eA 0.600 BSC 15.24 BSC -

eA/2 0.300 BSC 7.62 BSC -

NOTES:

1. Index area: A notch or a pin one identification mark shall be locat- L 0.125 0.200 3.18 5.08 -

ed adjacent to pin one and shall be located within the shaded Q 0.015 0.070 0.38 1.78 6

area shown. The manufacturer’s identification shall not be used

S1 0.005 - 0.13 - 7

as a pin one identification mark.

2. The maximum limits of lead dimensions b and c or M shall be 90o 105o 90o 105o -

measured at the centroid of the finished lead surfaces, when aaa - 0.015 - 0.38 -

solder dip or tin plate lead finish is applied.

bbb - 0.030 - 0.76 -

3. Dimensions b1 and c1 apply to lead base metal only. Dimension

M applies to lead plating and finish thickness. ccc - 0.010 - 0.25 -

4. Corner leads (1, N, N/2, and N/2+1) may be configured with a M - 0.0015 - 0.038 2, 3

partial lead paddle. For this configuration dimension b3 replaces N 40 40 8

dimension b2.

Rev. 0 4/94

5. This dimension allows for off-center lid, meniscus, and glass

overrun.

6. Dimension Q shall be measured from the seating plane to the

base plane.

7. Measure dimension S1 at all four corners.

8. N is the maximum number of terminal positions.

9. Dimensioning and tolerancing per ANSI Y14.5M - 1982.

10. Controlling dimension: INCH.

FN2969 Rev 11.01 Page 27 of 31

Jan 20, 2020

82C55A

0.010 S E H S

J44.A MIL-STD-1835 CQCC1-N44 (C-5)

44 PAD CERAMIC LEADLESS CHIP CARRIER PACKAGE

D

INCHES MILLIMETERS

D3

SYMBOL MIN MAX MIN MAX NOTES

j x 45o

A 0.064 0.120 1.63 3.05 6, 7

A1 0.054 0.088 1.37 2.24 -

B 0.033 0.039 0.84 0.99 4

B1 0.022 0.028 0.56 0.71 2, 4

E3 E B2 0.072 REF 1.83 REF -

B

B3 0.006 0.022 0.15 0.56 -

D 0.640 0.662 16.26 16.81 -

D1 0.500 BSC 12.70 BSC -

D2 0.250 BSC 6.35 BSC -

h x 45o D3 - 0.662 - 16.81 2

0.010 S E F S

E 0.640 0.662 16.26 16.81 -

A A1 E1 0.500 BSC 12.70 BSC -

E2 0.250 BSC 6.35 BSC -

PLANE 2

E3 - 0.662 - 16.81 2

PLANE 1 e 0.050 BSC 1.27 BSC -

-E-

e1 0.015 - 0.38 - 2

h 0.040 REF 1.02 REF 5

j 0.020 REF 0.51 REF 5

0.007 M E F S H S

L 0.045 0.055 1.14 1.40 -

B1 L1 0.045 0.055 1.14 1.40 -

e

L3 L2 0.075 0.095 1.90 2.41 -

L -H-

L3 0.003 0.015 0.08 0.38 -

ND 11 11 3

NE 11 11 3

N 44 44 3

-F-

Rev. 0 5/18/94

B3 NOTES:

E1

1. Metallized castellations shall be connected to plane 1 terminals

and extend toward plane 2 across at least two layers of ceramic

E2 L2 or completely across all of the ceramic layers to make electrical

B2 connection with the optional plane 2 terminals.

2. Unless otherwise specified, a minimum clearance of 0.015 inch

(0.38mm) shall be maintained between all metallized features

L1

(e.g., lid, castellations, terminals, thermal pads, etc.)

e1 D2 3. Symbol “N” is the maximum number of terminals. Symbols “ND”

and “NE” are the number of terminals along the sides of length

D1

“D” and “E”, respectively.

4. The required plane 1 terminals and optional plane 2 terminals (if

used) shall be electrically connected.

5. The corner shape (square, notch, radius, etc.) may vary at the

manufacturer’s option, from that shown on the drawing.

6. Chip carriers shall be constructed of a minimum of two ceramic

layers.

7. Dimension “A” controls the overall package thickness. The maxi-

mum “A” dimension is package height before being solder dipped.

8. Dimensioning and tolerancing per ANSI Y14.5M-1982.

9. Controlling dimension: INCH.

FN2969 Rev 11.01 Page 28 of 31

Jan 20, 2020

82C55A

0.042 (1.07)

0.042 (1.07)

0.048 (1.22)

0.056 (1.42) 0.004 (0.10) C N44.65 (JEDEC MS-018AC ISSUE A)

PIN (1) IDENTIFIER 44 LEAD PLASTIC LEADED CHIP CARRIER PACKAGE

0.050 (1.27) TP 0.025 (0.64)

R

C 0.045 (1.14) INCHES MILLIMETERS

L

SYMBOL MIN MAX MIN MAX NOTES

A 0.165 0.180 4.20 4.57 -

D2/E2 A1 0.090 0.120 2.29 3.04 -

C

L D 0.685 0.695 17.40 17.65 -

E1 E

D1 0.650 0.656 16.51 16.66 3

D2/E2 D2 0.291 0.319 7.40 8.10 4, 5

VIEW “A” E 0.685 0.695 17.40 17.65 -

E1 0.650 0.656 16.51 16.66 3

0.020 (0.51)

E2 0.291 0.319 7.40 8.10 4, 5

MIN

D1 A1 N 44 44 6

D A

SEATING Rev. 2 11/97

0.020 (0.51) MAX -C- PLANE

3 PLCS 0.026 (0.66)

0.032 (0.81) 0.013 (0.33)

0.021 (0.53)

0.025 (0.64)

0.045 (1.14) MIN

MIN

VIEW “A” TYP.

NOTES:

1. Controlling dimension: INCH. Converted millimeter dimensions are

not necessarily exact.

2. Dimensions and tolerancing per ANSI Y14.5M-1982.

3. Dimensions D1 and E1 do not include mold protrusions. Allowable

mold protrusion is 0.010 inch (0.25mm) per side. Dimensions D1

and E1 include mold mismatch and are measured at the extreme

material condition at the body parting line.

4. To be measured at seating plane -C- contact point.

5. Centerline to be determined where center leads exit plastic body.

6. “N” is the number of terminal positions.

FN2969 Rev 11.01 Page 29 of 31

Jan 20, 2020

82C55A

D

D1 Q44.10x10 (JEDEC MS-022AB ISSUE B)

-D- 44 LEAD METRIC PLASTIC QUAD FLATPACK PACKAGE

INCHES MILLIMETERS

SYMBOL MIN MAX MIN MAX NOTES

A - 0.096 - 2.45 -

A1 0.004 0.010 0.10 0.25 -

-A- -B- A2 0.077 0.083 1.95 2.10 -

E E1 b 0.012 0.018 0.30 0.45 6

b1 0.012 0.016 0.30 0.40 -

D 0.515 0.524 13.08 13.32 3

D1 0.389 0.399 9.88 10.12 4, 5

E 0.516 0.523 13.10 13.30 3

e E1 0.390 0.398 9.90 10.10 4, 5

L 0.029 0.040 0.73 1.03 -

PIN 1

N 44 44 7

SEATING e 0.032 BSC 0.80 BSC -

-H-

A PLANE

Rev. 2 4/99

NOTES:

0.076

0.003 1. Controlling dimension: MILLIMETER. Converted inch

12o-16o -C- dimensions are not necessarily exact.

0.40 0.20 2. All dimensions and tolerances per ANSI Y14.5M-1982.

0.016 MIN 0.008

M C A-B S D S

0o MIN 3. Dimensions D and E to be determined at seating plane -C- .

b

A2 A1 4. Dimensions D1 and E1 to be determined at datum plane

0o-7o b1 -H- .

5. Dimensions D1 and E1 do not include mold protrusion.

0.13/0.17 Allowable protrusion is 0.25mm (0.010 inch) per side.

0.005/0.007

12o-16o 6. Dimension b does not include dambar protrusion. Allowable

L

dambar protrusion shall be 0.08mm (0.003 inch) total.

BASE METAL

7. “N” is the number of terminal positions.

WITH PLATING

0.13/0.23

0.005/0.009

FN2969 Rev 11.01 Page 30 of 31

Jan 20, 2020

IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES (“RENESAS”) PROVIDES TECHNICAL

SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING

REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND

OTHER RESOURCES “AS IS” AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED,

INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A

PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible

for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3)

ensuring your application meets applicable standards, and any other safety, security, or other requirements. These

resources are subject to change without notice. Renesas grants you permission to use these resources only for

development of an application that uses Renesas products. Other reproduction or use of these resources is strictly

prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property.

Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims,

damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject

to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources

expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

Corporate Headquarters Contact Information

TOYOSU FORESIA, 3-2-24 Toyosu, For further information on a product, technology, the most

Koto-ku, Tokyo 135-0061, Japan up-to-date version of a document, or your nearest sales

www.renesas.com office, please visit:

www.renesas.com/contact/

Trademarks

Renesas and the Renesas logo are trademarks of Renesas

Electronics Corporation. All trademarks and registered

trademarks are the property of their respective owners.

© 2020 Renesas Electronics Corporation. All rights reserved.

You might also like

- Features: CMOS Programmable Peripheral InterfaceDocument30 pagesFeatures: CMOS Programmable Peripheral InterfaceFernandoDanielMelgarPinedaNo ratings yet

- Features Description: CMOS Programmable Peripheral InterfaceDocument22 pagesFeatures Description: CMOS Programmable Peripheral Interfacekhawar mukhtarNo ratings yet

- MAX7328-MAX7329 Port ExpanderDocument13 pagesMAX7328-MAX7329 Port Expanderalbert.sureda.spamNo ratings yet

- Features: Single-Chip SIGFOX RF TransmitterDocument23 pagesFeatures: Single-Chip SIGFOX RF TransmitterDiego ZuñigaNo ratings yet

- AVR and C Programming FinalDocument58 pagesAVR and C Programming Finalzbhp zNo ratings yet

- Microcomputer Components: 8-Bit CMOS Single-Chip MicrocontrollerDocument58 pagesMicrocomputer Components: 8-Bit CMOS Single-Chip MicrocontrollerBrahim MidouneNo ratings yet

- MAX7310 8bit I2C Port ExpanderDocument15 pagesMAX7310 8bit I2C Port Expanderalbert.sureda.spamNo ratings yet

- Atmel 9111 LIN Networking ATA6612C ATA6613C - Datasheet PDFDocument312 pagesAtmel 9111 LIN Networking ATA6612C ATA6613C - Datasheet PDFAnkadi Sikari ReddyNo ratings yet

- Apw7705 PDFDocument54 pagesApw7705 PDFLin CokeNo ratings yet

- 74HC164 74HCT164: 1. General DescriptionDocument16 pages74HC164 74HCT164: 1. General DescriptionteomondoNo ratings yet

- Pca9555 I2c To Gpio NXPDocument34 pagesPca9555 I2c To Gpio NXPWillam TurnerNo ratings yet

- HPS50 Maual VellemanDocument21 pagesHPS50 Maual VellemanAngel GonzalezNo ratings yet

- At91m55800 PDFDocument250 pagesAt91m55800 PDFLeland ChristensenNo ratings yet

- 8-Bit Single-Chip Microcomputer With Ad Converter D78c10agq Nec Datasheet PDFDocument66 pages8-Bit Single-Chip Microcomputer With Ad Converter D78c10agq Nec Datasheet PDFAnonymous qWeFIfN90No ratings yet

- DatasheetDocument22 pagesDatasheetAnderson gonçalvesNo ratings yet

- DG408, DG409: Single 8-Channel/Differential 4-Channel, CMOS Analog Multiplexers FeaturesDocument17 pagesDG408, DG409: Single 8-Channel/Differential 4-Channel, CMOS Analog Multiplexers FeaturesmikigabriNo ratings yet

- PCD7F150SDocument6 pagesPCD7F150SMichal SzyjaNo ratings yet

- 80V, 1.25A Peak Current H-Bridge FET Driver: FeaturesDocument14 pages80V, 1.25A Peak Current H-Bridge FET Driver: FeaturesPiotr WłaźlińskiNo ratings yet

- STM32F 100pin SCHDocument1 pageSTM32F 100pin SCHHungNo ratings yet

- Ds8295a 04Document14 pagesDs8295a 04Bsm GwapuNo ratings yet

- Data SheetDocument15 pagesData Sheetzakie wahyuNo ratings yet

- Description Features: PT4452 PLL-based OOK/ASK/FSK Transmitter ICDocument4 pagesDescription Features: PT4452 PLL-based OOK/ASK/FSK Transmitter ICSamerNo ratings yet

- Micom CXP83624 AV-2: R.G.B AMP. & CPT Drive TDA6107QDocument1 pageMicom CXP83624 AV-2: R.G.B AMP. & CPT Drive TDA6107QJose navarro martinNo ratings yet

- 6A, 23V Synchronous Step-Down Converter With 3.3V/5V LDO: RT6256B/CDocument20 pages6A, 23V Synchronous Step-Down Converter With 3.3V/5V LDO: RT6256B/CkiryanoffNo ratings yet

- Fan7382 103101Document17 pagesFan7382 103101Oleksandr ShandurskyiNo ratings yet

- PCA9544A: 1. General DescriptionDocument26 pagesPCA9544A: 1. General DescriptionUmar AnjumNo ratings yet

- HI-506, HI-507, HI-508, HI-509: Single 16 and 8/differential 8-Channel and 4-Channel CMOS Analog MultiplexersDocument25 pagesHI-506, HI-507, HI-508, HI-509: Single 16 and 8/differential 8-Channel and 4-Channel CMOS Analog MultiplexersIsmael GuzmanNo ratings yet

- PAL16R8 Family 20-Pin TTL Programmable Array LogicDocument33 pagesPAL16R8 Family 20-Pin TTL Programmable Array LogicsolomonicbdmNo ratings yet

- Sab80c535 16 NDocument56 pagesSab80c535 16 Nmoyali25176750No ratings yet

- Connections For Supported MMDVM BoardsDocument1 pageConnections For Supported MMDVM BoardsFABIANNo ratings yet

- REN - Hi 546 47 48 49 - DST - 19990429Document25 pagesREN - Hi 546 47 48 49 - DST - 19990429Davide MirraNo ratings yet

- K6X4016C3F Family Cmos Sram: Document TitleDocument10 pagesK6X4016C3F Family Cmos Sram: Document TitledarezenaNo ratings yet

- Parallel Interface 6821Document19 pagesParallel Interface 6821Fouad ElhajjiNo ratings yet

- M81C55 OkiDocument19 pagesM81C55 OkiEsteban MaryoryNo ratings yet

- I2c Moist SensorDocument1 pageI2c Moist SensormicNo ratings yet

- Microcontroller Lab Manual (10ESL47) BY RAGHUNATHDocument87 pagesMicrocontroller Lab Manual (10ESL47) BY RAGHUNATHRaghunath B HNo ratings yet

- Atmel Atmega165A/Pa/325A/Pa/3250A/Pa/645A/P/6450A/P: FeaturesDocument841 pagesAtmel Atmega165A/Pa/325A/Pa/3250A/Pa/645A/P/6450A/P: FeaturesjmsaakNo ratings yet

- A25L40P Series: 4 Mbit, Low Voltage, Serial Flash Memory Preliminary With 85Mhz Spi Bus InterfaceDocument38 pagesA25L40P Series: 4 Mbit, Low Voltage, Serial Flash Memory Preliminary With 85Mhz Spi Bus InterfaceiclogicNo ratings yet

- Synchronous-Rectified Buck MOSFET Drivers: Features General DescriptionDocument5 pagesSynchronous-Rectified Buck MOSFET Drivers: Features General DescriptionTeles SilvaNo ratings yet

- RTDocument12 pagesRTdopsocedriNo ratings yet

- Pa340u ADocument7 pagesPa340u AAriNetoNo ratings yet

- Interfacing ADC 0809 With 8051 TrainerDocument9 pagesInterfacing ADC 0809 With 8051 TrainerSoumyabrataPatraNo ratings yet

- HT46R46/C46/R47/C47/R48A/C48A/R49 Cost-Effective A/D Type 8-Bit MCUDocument77 pagesHT46R46/C46/R47/C47/R48A/C48A/R49 Cost-Effective A/D Type 8-Bit MCUOrlando García RodríguezNo ratings yet

- CAT28C16A 16 KB CMOS Parallel Eeprom: DescriptionDocument11 pagesCAT28C16A 16 KB CMOS Parallel Eeprom: DescriptionLaboratorio GTO Perú S.A.C.No ratings yet

- YaEwN89a PCA9536Document22 pagesYaEwN89a PCA9536vvvNo ratings yet

- Clock SchematicDocument1 pageClock SchematicRaja Babu100% (1)

- 6532 CommodoreDocument10 pages6532 Commodoredomagix470No ratings yet

- Multi-Phase PWM Controller For CPU Core Power Supply: Features General DescriptionDocument14 pagesMulti-Phase PWM Controller For CPU Core Power Supply: Features General DescriptionFreddy ArmstrongNo ratings yet

- Datasheet Pca9555pw 118 - C128392Document36 pagesDatasheet Pca9555pw 118 - C128392vromikoNo ratings yet

- ProductLine 2Document10 pagesProductLine 2Mike ThomsonNo ratings yet

- Datasheet Ic CE DEDocument15 pagesDatasheet Ic CE DEBersama UkhuwahNo ratings yet

- RT8296A RichtekDocument14 pagesRT8296A Richtektecnicown eletricaNo ratings yet

- 8-Bit Microcontroller With 8K Bytes Flash AT89S8252: FeaturesDocument31 pages8-Bit Microcontroller With 8K Bytes Flash AT89S8252: Featuresapi-3808344No ratings yet

- ATMEGA165P ATMELCorporationDocument364 pagesATMEGA165P ATMELCorporationbbraun chandranNo ratings yet

- Data Sheet: CAN Serial Linked I/O Device (SLIO) With Digital and Analog Port FunctionsDocument36 pagesData Sheet: CAN Serial Linked I/O Device (SLIO) With Digital and Analog Port FunctionsalexNo ratings yet

- Features: 0.5Mhz, Low Supply Voltage, Low Input Current Bimos Operational AmplifierDocument5 pagesFeatures: 0.5Mhz, Low Supply Voltage, Low Input Current Bimos Operational AmplifierAlexandre Correa100% (1)

- ATtiny 24Document240 pagesATtiny 24hissein ousmanNo ratings yet

- 03 JM EFIE ControllerDocument1 page03 JM EFIE Controllerskyman05100% (1)

- THGBMHG7C1LBAIL ToshibaDocument33 pagesTHGBMHG7C1LBAIL ToshibaCube7 GeronimoNo ratings yet

- Rhel-9 Rhce Exam Model PaperDocument18 pagesRhel-9 Rhce Exam Model Paperbedoui marwenNo ratings yet

- EX294 QuestionsDocument7 pagesEX294 Questionsbedoui marwenNo ratings yet

- Installing Ubuntu Server 22-04Document3 pagesInstalling Ubuntu Server 22-04bedoui marwenNo ratings yet

- Ma Network Automation For Everyone Ebook 511700 202309 enDocument18 pagesMa Network Automation For Everyone Ebook 511700 202309 enbedoui marwenNo ratings yet

- The Bet and Other Stories by Anton TchekhovDocument63 pagesThe Bet and Other Stories by Anton Tchekhovbedoui marwenNo ratings yet

- Santiago Bernabéu: Listening Section Reading SectionDocument1 pageSantiago Bernabéu: Listening Section Reading Sectionbedoui marwenNo ratings yet

- OussemaDocument2 pagesOussemabedoui marwenNo ratings yet

- 26 February 2022Document1 page26 February 2022bedoui marwenNo ratings yet

- Prepared by Destiny Corporation: Reading and Writing Data From Microsoft Excel/Word Using DDEDocument6 pagesPrepared by Destiny Corporation: Reading and Writing Data From Microsoft Excel/Word Using DDEniravNo ratings yet

- Oracle Hyperion PlanningDocument3 pagesOracle Hyperion PlanningAmit Sharma0% (1)

- Pocket Folder - Contents (PDF) - Added 4-3-20Document22 pagesPocket Folder - Contents (PDF) - Added 4-3-20Dereck SeckmanNo ratings yet

- Conformance Testing ProcessDocument37 pagesConformance Testing ProcessvietbkfetNo ratings yet

- Docu93977 Avamar 19 Management Console Command Line Interface (MCCLI) Programmer GuideDocument166 pagesDocu93977 Avamar 19 Management Console Command Line Interface (MCCLI) Programmer GuidelinuxirNo ratings yet

- Analysys Mason ALU 5780DSC Profile Oct 2012Document24 pagesAnalysys Mason ALU 5780DSC Profile Oct 2012lcardonagNo ratings yet

- Sellos PDFDocument8 pagesSellos PDFchuylemalo1990No ratings yet

- Lecture Notes OopsDocument147 pagesLecture Notes OopspriyanshumundyalNo ratings yet

- Unit 1: MPI (CST-282, ITT-282) SUBMISSION DATE: 14.02.2020Document9 pagesUnit 1: MPI (CST-282, ITT-282) SUBMISSION DATE: 14.02.2020Shruti SinghNo ratings yet

- Major Project ReportDocument38 pagesMajor Project ReportHritik JaiswalNo ratings yet

- Online Offline LearningDocument10 pagesOnline Offline LearninghelpilNo ratings yet

- UntitledDocument2 pagesUntitledHariharan VeerannanNo ratings yet

- C++ Robert LaforeDocument701 pagesC++ Robert LaforeUsman Waheed100% (3)

- SFP-1GE-FE-E-T: Optics OverviewDocument6 pagesSFP-1GE-FE-E-T: Optics OverviewAlexander Sison Jr.No ratings yet

- Lec51 Pat312 2001 Gap Model WhiteDocument6 pagesLec51 Pat312 2001 Gap Model WhiteHumayun NawazNo ratings yet

- Change LogDocument70 pagesChange LogTan Khai ChuanNo ratings yet

- Exception HandlingDocument6 pagesException Handlinghonaday945No ratings yet

- TSV3561 Lesson Plan For StudentDocument9 pagesTSV3561 Lesson Plan For StudentShenWeiNo ratings yet

- All Technologies Boolean Search Strings 1561560291Document43 pagesAll Technologies Boolean Search Strings 1561560291Praveen Rayapaty72% (25)

- Analytics - Magellan: An OverviewDocument25 pagesAnalytics - Magellan: An OverviewAditya Mohan GoelNo ratings yet

- Net102 Midterm Lab-Activity-1Document2 pagesNet102 Midterm Lab-Activity-1John Carlo Mesina GomezNo ratings yet

- DCAD OverviewDocument9 pagesDCAD OverviewSue KimNo ratings yet

- 2010-11 Hawell 7000seriesDVRmanual SVR 7504Document72 pages2010-11 Hawell 7000seriesDVRmanual SVR 7504BBFulNo ratings yet

- Ora-600 kdsgrp1Document10 pagesOra-600 kdsgrp1Yulin LiuNo ratings yet

- Seth J. Gillespie PH.D., MBA, PMP, PMI-ACP, CSM, ITIL, CISSPDocument11 pagesSeth J. Gillespie PH.D., MBA, PMP, PMI-ACP, CSM, ITIL, CISSPSeth J. Gillespie, PhDNo ratings yet

- Illustrated Microsoft Office 365 and Office 2016 Projects Loose Leaf Version 1st Edition Cram Solutions Manual DownloadDocument10 pagesIllustrated Microsoft Office 365 and Office 2016 Projects Loose Leaf Version 1st Edition Cram Solutions Manual DownloadJan Neeley100% (22)

- Online Music PortalDocument21 pagesOnline Music PortalSaurabh Singh100% (1)

- Interrupts and 8259 ChipDocument48 pagesInterrupts and 8259 ChipYaar RaiderNo ratings yet

- DAQLINKII Manual 9 2009Document100 pagesDAQLINKII Manual 9 2009Carlo RojasNo ratings yet

- Training For Civil 3DDocument3 pagesTraining For Civil 3Doseni momoduNo ratings yet