Professional Documents

Culture Documents

Atmel 0059

Atmel 0059

Uploaded by

kachalOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Atmel 0059

Atmel 0059

Uploaded by

kachalCopyright:

Available Formats

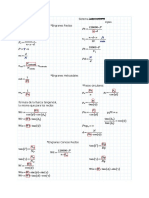

13.

2 Ports as General Digital I/O

The ports are bi-directional I/O ports with optional internal pull-ups. Figure 13-2 shows a functional description of one

I/O-port pin, here generically called Pxn.

Figure 13-2. General Digital I/O(1)

PUD

Q D

DDxn

Q

CLR

WDx

RESET

RDx

DATA BUS

Pxn Q D

0

PORTxn

Q

CLR

RESET WPx

SLEEP WRx

RRx

Synchronizer

RPx

D Q D Q

PINxn

L Q Q

CLKI/O

PUD: PULLUP DISABLE WDx: WRITE DDRx

SLEEP: SLEEP CONTROL RDx: READ DDRx

CLKI/O: I/O CLOCK WRx: WRITE PORTx

RRx: READ PORTx REGISTER

RPx: READ PORTx PIN

WPx: WRITE PINx REGISTER

Note: 1. WRx, WPx, WDx, RRx, RPx, and RDx are common to all pins within the same port. clkI/O, SLEEP, and PUD

are common to all ports.

13.2.1 Configuring the Pin

Each port pin consists of three register bits: DDxn, PORTxn, and PINxn. As shown in Section 13.4 “Register Description” on

page 72, the DDxn bits are accessed at the DDRx I/O address, the PORTxn bits at the PORTx I/O address, and the PINxn

bits at the PINx I/O address.

The DDxn bit in the DDRx register selects the direction of this pin. If DDxn is written logic one, Pxn is configured as an output

pin. If DDxn is written logic zero, Pxn is configured as an input pin.

If PORTxn is written logic one when the pin is configured as an input pin, the pull-up resistor is activated. To switch the

pull-up resistor off, PORTxn has to be written logic zero or the pin has to be configured as an output pin. The port pins are

tri-stated when reset condition becomes active, even if no clocks are running.

If PORTxn is written logic one when the pin is configured as an output pin, the port pin is driven high (one). If PORTxn is

written logic zero when the pin is configured as an output pin, the port pin is driven low (zero).

ATmega328P [DATASHEET] 59

7810D–AVR–01/15

You might also like

- Quick Reference Guide: Delcos 1000Document2 pagesQuick Reference Guide: Delcos 1000Vijačni kompresori- Prodaja i servis65% (20)

- LGR25 ManualDocument27 pagesLGR25 ManualSyed JahangirNo ratings yet

- Autodyn Parallel Processing GuideDocument52 pagesAutodyn Parallel Processing Guideทัช ชี่No ratings yet

- Atmega128: I/O PortsDocument24 pagesAtmega128: I/O PortsCorina SoareNo ratings yet

- RegistersDocument19 pagesRegistersjjrmllnNo ratings yet

- Latches, Flip-Flops, and RegistersDocument15 pagesLatches, Flip-Flops, and RegistersTIKTOK ChannelNo ratings yet

- Final F17 SolDocument8 pagesFinal F17 Solm.esadakrasNo ratings yet

- Note 4 Schematic PDFDocument20 pagesNote 4 Schematic PDFAlif AdnanNo ratings yet

- 华南X99 F8D主板说明书 12Document1 page华南X99 F8D主板说明书 12messiahsNo ratings yet

- DECSE - Chapter 3 1Document24 pagesDECSE - Chapter 3 1KrithiiNo ratings yet

- PIC16F87X: 3.0 I/O PortsDocument6 pagesPIC16F87X: 3.0 I/O PortsMenad SalahNo ratings yet

- 6 Bacnet Interface - Easylab: Analog Value ObjectsDocument1 page6 Bacnet Interface - Easylab: Analog Value ObjectsKoteswara RaoNo ratings yet

- 03 Intruction ExecDocument18 pages03 Intruction Execsanjanamooli77No ratings yet

- L-6. Tristates & LatchesDocument12 pagesL-6. Tristates & Latchesjery tomNo ratings yet

- Time Borring and Clock SkewDocument18 pagesTime Borring and Clock SkewNitin Suyan PanchalNo ratings yet

- 8051 ArchitectureDocument13 pages8051 ArchitectureKabilanNo ratings yet

- Co 1Document43 pagesCo 1Akula Lakshmi SreenivasuluNo ratings yet

- TI TI: PLC Modem PLC ModemDocument9 pagesTI TI: PLC Modem PLC ModemHyundianto AgNo ratings yet

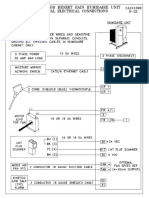

- WiringDocument1 pageWiringaravindh raNo ratings yet

- CH 3 AVR Peripherals - KeypadDocument16 pagesCH 3 AVR Peripherals - KeypadMischka BudhaiNo ratings yet

- Clocking: Bharadwaj Amrutur Ece Dept, Iisc Bangalore 12Document26 pagesClocking: Bharadwaj Amrutur Ece Dept, Iisc Bangalore 12Shankey GoelNo ratings yet

- D D D D: SN74ALS166 Parallel-Load 8-Bit Shift RegisterDocument16 pagesD D D D: SN74ALS166 Parallel-Load 8-Bit Shift Registerpraveenverma1990No ratings yet

- EE 508 Lect 21 Fall 2020Document40 pagesEE 508 Lect 21 Fall 2020Sai KiranNo ratings yet

- Ade Mod4Document24 pagesAde Mod4Sud UiNo ratings yet

- Sahara Storm Rev 13Document3 pagesSahara Storm Rev 13AristideNo ratings yet

- Causes of Water Influx Relationship Between:: - A Well and Oil Reservoir. - Oil Reservoir and The AquiferDocument26 pagesCauses of Water Influx Relationship Between:: - A Well and Oil Reservoir. - Oil Reservoir and The AquiferAnonymous qaI31HNo ratings yet

- Lecture 3 - Chapter 4 - REGISTER TRANSFER AND MICROOPERATIONSDocument31 pagesLecture 3 - Chapter 4 - REGISTER TRANSFER AND MICROOPERATIONSsaifsunnyNo ratings yet

- Datasheet - Live: HD74HC273Document8 pagesDatasheet - Live: HD74HC273OskarNo ratings yet

- Process PLCDocument35 pagesProcess PLCreezmanNo ratings yet

- Digital Systems - Mini AVR 5: Pere Pal' A - Alexis L OpezDocument15 pagesDigital Systems - Mini AVR 5: Pere Pal' A - Alexis L OpezPau Susin AlsinaNo ratings yet

- Radar StructureDocument1 pageRadar StructureKarl Martin AlduesoNo ratings yet

- Fyp 1 Scematic DemoDocument1 pageFyp 1 Scematic DemoNazreen KamaruddinNo ratings yet

- Module 6Document38 pagesModule 6Sidharth GuptaNo ratings yet

- Experiment No.: 5Document6 pagesExperiment No.: 5Dhrumil ManiyarNo ratings yet

- ADC Interface MKII1Document1 pageADC Interface MKII1bloodbathNo ratings yet

- IT66121FNDocument39 pagesIT66121FNCarlos ChuekeNo ratings yet

- Jameco Part Number 49357FSC: Distributed byDocument6 pagesJameco Part Number 49357FSC: Distributed byFaisal Zidni Miftahul IlmiNo ratings yet

- Control Valve CalcDocument7 pagesControl Valve Calcartneves100% (1)

- HV7355DB1 150V, 1.5A, Unipolar Ultrasound Pulser Demoboard: General DescriptionDocument9 pagesHV7355DB1 150V, 1.5A, Unipolar Ultrasound Pulser Demoboard: General DescriptionAhmed YasserNo ratings yet

- Basic Processing UnitDocument57 pagesBasic Processing UnitHerambh DubeyNo ratings yet

- 8-Input NAND Gate: Integrated CircuitsDocument8 pages8-Input NAND Gate: Integrated CircuitsJHON EDWARD LIZARAZO PARADANo ratings yet

- KW RPM MM FT Min T N N: Internacional InglesDocument2 pagesKW RPM MM FT Min T N N: Internacional InglesAdriana Elorza RamosNo ratings yet

- SN 74 HCT 573Document20 pagesSN 74 HCT 573bvNo ratings yet

- 2.9 Shell Momentum Balance and Velocity Profile in Laminar Flow 2.9A IntroductionDocument6 pages2.9 Shell Momentum Balance and Velocity Profile in Laminar Flow 2.9A IntroductionElijah GoreNo ratings yet

- sn74hc273 q1Document17 pagessn74hc273 q1uumar33355No ratings yet

- Objecttves: Upon Completion Chapte4 You ToDocument22 pagesObjecttves: Upon Completion Chapte4 You ToFaizan AliNo ratings yet

- Internal Architecture of A UART: TX Buffer (Register)Document1 pageInternal Architecture of A UART: TX Buffer (Register)Lavakumar KarneNo ratings yet

- Lecture 1 IntroDocument17 pagesLecture 1 Intro凌芷婕 LING ZHI JIE C44101175No ratings yet

- Dual J-K Flip Flop With Preset and Clear: Order CodesDocument11 pagesDual J-K Flip Flop With Preset and Clear: Order CodesAtzin SanchezNo ratings yet

- D D D D D D D: SN54HC574, SN74HC574 Octal Edge-Triggered D-Type Flip-Flops With 3-State OutputsDocument25 pagesD D D D D D D: SN54HC574, SN74HC574 Octal Edge-Triggered D-Type Flip-Flops With 3-State OutputsДрагиша Небитни ТрифуновићNo ratings yet

- Nptel Cad1 05Document20 pagesNptel Cad1 05Tahir KhAnNo ratings yet

- TCONDocument5 pagesTCONLotteDomineNo ratings yet

- Decode ManchesterDocument16 pagesDecode ManchesterNelson VazquezNo ratings yet

- Floor PlanDocument40 pagesFloor PlansiddhasenNo ratings yet

- HD74LS76A: Dual J-K Flip-Flops (With Preset and Clear)Document7 pagesHD74LS76A: Dual J-K Flip-Flops (With Preset and Clear)Thế giới điện tửNo ratings yet

- DOP-103WQ DOP-107WV DOP-110WS: Instruction SheetDocument8 pagesDOP-103WQ DOP-107WV DOP-110WS: Instruction SheetPatrícia Queiróz Suporte Técnico CristófoliNo ratings yet

- HCF4017B: Decade Counter With 10 Decoded OutputsDocument11 pagesHCF4017B: Decade Counter With 10 Decoded Outputs19thmnlfreemsNo ratings yet

- CD4538Document11 pagesCD4538Sridhar MohanNo ratings yet

- RC Circuits - The Physics HypertextbookDocument2 pagesRC Circuits - The Physics HypertextbookNo NameNo ratings yet

- EE 308 Apr. 19, 2002Document12 pagesEE 308 Apr. 19, 2002asprillaNo ratings yet

- Ipcc Uap - Update Alg RouteDocument12 pagesIpcc Uap - Update Alg Routewilly cNo ratings yet

- HP Library and Tape Tools Webgui and LTT Service User Guide: Product Version: 5.1Document115 pagesHP Library and Tape Tools Webgui and LTT Service User Guide: Product Version: 5.1jvaras1No ratings yet

- Automatic Storage ManagementDocument23 pagesAutomatic Storage ManagementPeter AsaneNo ratings yet

- T-SQL Coding StandardsDocument4 pagesT-SQL Coding Standardsmonday0rsundayNo ratings yet

- Reusable Code For OAFDocument6 pagesReusable Code For OAFpuramganeshNo ratings yet

- Bluetooth40 enDocument51 pagesBluetooth40 enqaz100% (1)

- SPPU University Paper May - Jun - 2023-1Document2 pagesSPPU University Paper May - Jun - 2023-1Dustin HenderNo ratings yet

- 7 Using C With Altera DE2 BoardDocument11 pages7 Using C With Altera DE2 BoardTiến Phương NguyễnNo ratings yet

- The Magic of LD - PRELOAD For Userland RootkitsDocument8 pagesThe Magic of LD - PRELOAD For Userland RootkitsRonaldNo ratings yet

- Tech Note 336 - Supporting USB Hardware Keys On FactorySuite A2 ProductsDocument4 pagesTech Note 336 - Supporting USB Hardware Keys On FactorySuite A2 ProductsTaleb EajalNo ratings yet

- Cross Platform Developer AssignmentDocument7 pagesCross Platform Developer AssignmentSuraj SinghNo ratings yet

- Silicon Labs Efm8ub20f64g B QFP48R - C2053313Document57 pagesSilicon Labs Efm8ub20f64g B QFP48R - C2053313TNo ratings yet

- Selesaikan Dan Buka Kembali Project Android Studio Minggu Lalu 2. Klik File - New - Activity - Empty ActivityDocument6 pagesSelesaikan Dan Buka Kembali Project Android Studio Minggu Lalu 2. Klik File - New - Activity - Empty ActivityRahmad Rifa'iNo ratings yet

- 9.1 Radwin Software For HWM Data LoggersDocument1 page9.1 Radwin Software For HWM Data LoggersMais OmarNo ratings yet

- Free Form RPG PDFDocument18 pagesFree Form RPG PDFAlina AlinuztzaNo ratings yet

- MESH Client Installation Guidance v1.2Document25 pagesMESH Client Installation Guidance v1.2rcabacasNo ratings yet

- Ricoh Product Code Cross ReferenceDocument22 pagesRicoh Product Code Cross ReferenceBrian DuBridge50% (2)

- Kubernetes Interview Questions and AnswersDocument8 pagesKubernetes Interview Questions and AnswerssrinivasNo ratings yet

- ECE 4140 SyllabusDocument2 pagesECE 4140 SyllabusroderickvicenteNo ratings yet

- UntitledDocument32 pagesUntitledRichard MuleyNo ratings yet

- Aws Certified Cloud Practitioner PDFDocument5 pagesAws Certified Cloud Practitioner PDFSiddharthNo ratings yet

- 3 (A)Document4 pages3 (A)kshyetrarklNo ratings yet

- (6sl3255-0aa00-4ca1) Basic Operator PanelDocument4 pages(6sl3255-0aa00-4ca1) Basic Operator PanelRyan TorresNo ratings yet

- Chapter-5 Threads and ConcurrancyDocument47 pagesChapter-5 Threads and ConcurrancyAsad KhanNo ratings yet

- 3-DatAdvantage Advanced Installation For NAS and Linux Platforms 8.6Document47 pages3-DatAdvantage Advanced Installation For NAS and Linux Platforms 8.6yaritzaNo ratings yet

- Modern Batch Scripting PDFDocument64 pagesModern Batch Scripting PDFEduin OrtegaNo ratings yet

- Machines Simulator Instruction GuideDocument27 pagesMachines Simulator Instruction Guideforfor3No ratings yet