Professional Documents

Culture Documents

Bi-Directional Isolated DC-DC Converter For Next-Generation Power Distribution - Comparison of Converters Using Si and Sic Devices

Uploaded by

Prasad SolasaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Bi-Directional Isolated DC-DC Converter For Next-Generation Power Distribution - Comparison of Converters Using Si and Sic Devices

Uploaded by

Prasad SolasaCopyright:

Available Formats

Paper

Bi-Directional Isolated DC-DC Converter for Next-Generation Power

Distribution - Comparison of Converters using Si and SiC Devices

J. Biela∗ Non-member

D. Aggeler∗ Non-member

S. Inoue∗∗ Member

H. Akagi∗∗ Member

J.W. Kolar∗ Member

In this paper two bi-directional DC-DC converters for a 1MW next-generation BTB system of a distribution

system, as it is applied in Japan, are presented and compared with respect to design, efficiency and power

density. One DC-DC converter applies commercially available Si-devices and the other one high voltage SiC

switch, which consists of a SiC JFET cascode (MOSFET+1 JFET) in series with five SiC JFETs.

In the comparison also the high frequency, high voltage transformer, which ensures galvanic isolation and

which is a core element of the DC-DC converter, is examined in detail by analytic calculations and FEM

simulations.

For validating the analytical considerations a 20kW SiC DC-DC converter has been designed in detail.

Measurement results for the switching and conduction losses have been acquired from the SiC and also for a

Si system for calculating the losses of the scaled 1MW system.

Keywords: Next-generation BTB system, High voltage HF DC-DC converter, SiC JFET cascode, High voltage HF

transformer

6.6kV Feeder 1

1. Introduction Distribution

Transformer

BTB

Generally, the power generation with renewable en- System

ergy sources is a discontinuous process and in most of 6.6kV Feeder 2

the cases depending on the environment. Feeding in the

produced energy into a distribution system influences Distributed

the overall energy flow. Therefore, it is a challenge to Power

Generators

control and keep the energy stabilised. Figure 1 shows

a Japanese 6.6kV power distribution system having two Fig. 1. A 6.6kV distribution system in Japan hav-

feeders from a transformer. ing two feeders.

Today, each distribution system in Japan has radial

feeders, forming no loop. If the distributed power gen-

erators are installed concentrated on one of the feeders 2 a circuit configuration is shown which is presented in

(feeder 2 in figure 1), regulating voltage on both feeders [1]. The line-frequency (50Hz or 60Hz) transformers in

within an acceptable range becomes difficult. figure 2 play an important role in stepping down/up the

Back-to-Back (BTB) systems, also known as loop con- voltage and in ensuring galvanic isolation between the

trollers, have been investigated to solve the problem of two feeders. Especially, galvanic isolation is desirable

power flow balancing. The dotted lines in figure 1 show to prevent a zero-sequence current circulating between

where the BTB system would be installed and in figure the two feeders. However, one 6.6kV, 1MW transformer

∗

weighs approximately 3,000kg to 4,000kg, and may be

Based on ”’Bi-Directional Isolated DC-DC Converter for too heavy to be mounted on an electric pole. Actu-

Next-Generation Power Distribution - Comparison of

Converters using Si and SiC Devices”’, by D. Aggeler, J. ally, the solution with the transformers results in a large

Biela, S. Inoue, H. Akagi, J. W. Kolar which appeared in volume and occupy a big part of the conversion sys-

the proceedings of the 2007 Power Conversion Conference tem. Furthermore, the costs are quite high due to ris-

- Nagoya, (c) 2007 IEEE. ing prices for raw materials. As a consequence, a new

∗

ETH Zurich, Power Electronic Systems Laboratory topology is under investigation substituting the two line-

Physikstrasse 3, 8092 Zurich, Switzerland

∗∗

Tokyo Institute of Technology, Department of Electrical frequency transformers. The present BTB system with

and Electronic Engineering two three-phase, line frequency transformers will be re-

Tokyo, Japan placed by the next-generation BTB system given in fig-

IEEJ Trans. 128-D, Vol.128, No.7, 2008 1

Bi-Directional Isolated DC-DC Converter with SiC Devices

Two- or Three-Level Converter First Converter Cell

50/60Hz 50/60Hz

Transformer Transformer 6.6kV Circuit 6.6kV

in

6.6kV 6.6kV

Feeder 1 Feeder 2 figures

4, 5

Fig. 2. The present BTB system for the 6.6kV Second Converter Cell

power distribution system.

ure 3. There it is shown, that a BTB system in the N -th Converter Cell

next-generation consists of a number of converter cells

which in each case consists of a rectifier/inverter stage

and a DC-DC converter. The galvanic isolation of the

proposed BTB system is guaranteed by a high frequency Fig. 3. A 6.6kV BTB system in the next

(HF) transformer. Due to the high operating frequency generation.

the volume and the weight of the passive components

is reduced very much compared to the line-frequency

converter cell depends on the number of cascade con-

transformers.

nections N . Hence, waveform levels, AC input voltages

For the design of the full bridge converter different

and DC-link voltages per converter cell are calculated,

device technologies can be used: on the one hand a real-

for a different number N of converter cells, and sum-

isation with Si IGBT devices [2] and on the other hand

marised in table 2.

with SiC JFET components provided by SiCED [3]. In

The analysed Si IGBT system consists of six converter

the following a galvanic isolated BTB system with SiC

cells in each phase (N =6), what results in a DC-link

will be designed, according the specification parameters

voltage of 1.02kV in each cell, allowing to use 1.7kV

given in table 1 and compared with the Si system of [2].

IGBTs available at a lower cost than higher voltage

In section 2 the operation principle of the next-

Si devices. The application of several converter cells

generation BTB system solution is summarised shortly.

and phase shifted unipolar sinusoidal PWM of the rec-

The following section 3 focuses on the DC-DC converter

tifier/inverter stage, where the triangular carrier signal

with SiC JFET cascodes. There, the converter specifica-

in one converter cell is phase shifted by π/N from each

tions, the dual active bridge (DAB) as well as the high

other, results in a multilevel waveform of the line-to-

voltage (HV) SiC switch are explained. In section 4

neutral voltage. Therefore, the equivalent switching fre-

experimental results of the SiC JFET cascode and the

quency is 2N fc , where fc is the carrier frequency. As

design of the HV-HF transformer based on analytic cal-

a result, the voltage waveform has (2N +1) levels with

culations and FEM simulations are presented. Further-

the switching frequency of 2N fc . Thus, the carrier fre-

more, a 3D-model of the proposed DC-DC converter is

quency of the PWM converters can be as low as 4kHz

shown. Section 5 summarises the performance of the Si

by six converter cells in each phase.

IGBT system presented in [2]. Thereafter, the possible

solutions for a next-generation BTB system – Si IGBT

and SiC JFET cascode – are compared for a 1MW sys- Table 2. Voltage and waveform levels depending

tem in section 6 and finally conclusions are drawn in on the number N of converter cells of a next-gen-

eration BTB system.

section 7.

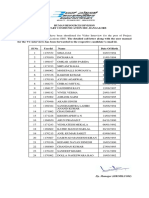

N Waveform AC Input DC Link

2. Next-Generation Medium Voltage BTB 1 3 Level 3,811V 6.10kV

System 2 5 Level 1,905V 3.48kV

3 7 Level 1,270V 2.03kV

The next-generation BTB system (figure 3) consists 4 9 Level 952V 1.52kV

of a rectifier/inverter stage and as the core circuit a 5 11 Level 752V 1.22kV

bi-directional, galvanic isolated DC-DC converter, as 6 13 Level 635V 1.02kV

shown in figure 4 (Si IGBT) or figure 5 (SiC JFET 7 15 Level 544V 870V

cascode), is applied. 8 17 Level 476V 762V

The cascaded converter cells form a single-phase part 9 19 Level 423V 677V

of the BTB system where each converter cell consists

of a DC-DC converter. The DC-link voltage in each Bridge 1

Csnub P

Bridge 2

DC

L/2 L/2

Table 1. Design requirements of the BTB system. VDC,1 VDC,2

vT 1 i1 vT 2

Input Voltage 6.6kV

Output Voltage 6.6kV

1:1

Rated Power 1MW

10kHz

Current THD 5%

Each Harmonic <3% Fig. 4. A bi-directional isolated DC-DC converter.

IEEJ Trans. 128-D, Vol.128, No.7, 2008 2

Bi-Directional Isolated DC-DC Converter with SiC Devices

fer from the active bridge on the input side via the gal-

T11 T12

1:1

T21 T22

vanic isolation (transformer) to the active bridge on the

VDC,1 iL L VDC,2

output side. There, the amount of transferred power is

6.1kV

C DC,1 v T1 v T2 CDC,2

6.1kV controlled by the phase shift angle φ [4],

50kHz

D

VDC,1 VDC,2 /n · φ · (π − φ)

T14 T13 T24 T23 P = · · · · · · · · · · · · · (1)

G S

2π 2 fS L

cf. Figure 7 and the leakage inductance L is used as energy storing

Fig. 5. SiC high voltage DC-DC converter. element. The variable n stands for the transformer turns

ratio and fS for the switching frequency.

The transferred power depends nonlinearly on the

The application of SiC JFET cascode devices for the phase shift angle φ between the voltages vT 1 and vT 2

DC-DC converter offer a HV blocking capability and and is limited by the switching frequency and the leak-

thus only one converter cell (N =1) is required. Ac- age inductance. The minimal phase shift angle and with

cordingly, a smaller number of power devices is utilised. this the minimal controllable power step is given by the

While in the Si IGBT based design (N =6) the number of clock frequency of the control board. Depending on the

power devices is 288, for the SiC JFET cascode system nonlinear relation of power and phase shift angle, the

48 semiconductor devices are used. Due to the lower biggest gradient is with a phase shift angle of zero de-

number of converter cells, in the SiC system a higher gree. There, the maximal power step will appear re-

carrier frequency is needed. spective the minimal controllable power at this point.

3. Operation Principle of the SiC HV-HF- With an increased phase shift angle, the power step will

Converter decrease and the controllable power will be smaller.

In [5] the active and reactive power are shown as a

The proposed HV and HF DAB converter with SiC function of the phase shift angle. A high phase shift

JFET cascode, replacing the conventional BTB system value will increase significantly the reactive part of the

with the two line-frequency transformers, is shown in power and only a little bit the active power. Conse-

figure 5. quently, the efficiency of the converter is reduced. A

The specification of the SiC DAB converter is given small phase shift angle the control signal constrain the

in table 3. The design requirements for the distribu- controllability of the power steps. Therefore, an opera-

tion system given at a line-to-line voltage VAC of 6.6kV tion in the phase shift interval of [ π4 , π3 ] is favourable and

(table 1), a DC-link voltage VDC of 6.1kV (with 13% chosen for the considered DAB.

safety margin, table 2) is resulting. One goal of the next- In order to verify the operation of the DAB topology

generation BTB system is reduction in terms of size, a simulation model was built for the specification given

especially of the passive components. A high switch- in table 3. There, only a simplified equivalent circuit of

ing frequency will result in smaller magnetic compo- the HV SiC switch was used. An exact model, which de-

nents/transformer but the HF losses increase consider- scribes static and dynamic behaviour of the HV switch

able. For that reason the switching frequency of 50kHz in more detail is under investigation. Figure 6 shows

is chosen to limit HF losses. Consideration of power con- the simulated transformer voltages vT 1 and vT 2 with the

trollability and a dynamical margin of continuous cur- inductor current iL , whereas the stray capacitance of the

rent flowing a rated power of 20kW is designed for the transformer is considered.

DAB. For transferring a bigger amount of power, devices 3.2 High voltage SiC switch As a result of the

must be connected in parallel to increase the continuous operation voltage, switches with a HV blocking capabil-

current capability. Furthermore, the transformer turns ity are required. Thus, SiC JFET cascode are chosen

ratio is fixed because of the equal voltage level on both because of the good material characteristics of SiC, as

side of the distribution system. the low on-state losses and high frequency operation.

3.1 Dual Active Bridge As modulation method Two different modules are applied: one contains four

the common phase shift operation is chosen for the SiC JFETs, two connected in series and two in parallel.

DAB. The low computation complexity of the phase shift For controlling the switch additionally a low-voltage Si

method, the simplicity of the circuit and the reduced MOSFET is connected to the lower JFETs (A, figure 7).

power losses due to zero voltage switching (ZVS) are the In the other module just two SiC JFETs are connected

main reasons for the wide application of this method. in series and two in parallel (B, figure 7).

Characteristic of the DAB principle is the power trans- The structure of the SiC JFET die is designed with

a internal pn-junction from source to drain [6], which

Table 3. Specification of DC-DC converter. is working as the freewheeling diode of the SiC JFET.

Thus, no external freewheeling diodes are required.

DC-link Voltage 6.1kV

Switching Frequency 50kHz The gates of the JFETs are connected to additional

Rated Power 20kW diodes for passive controlling the turn-on and turn-off

Transformer Turns Ratio 1:1 mechanism of each JFET. This diode is a low leakage

Peak Inductance Current 7A fast recovery epitaxial diode (FRED) and is included in

DC-link Voltage Ripple < 5% the SEMITOP package.

IEEJ Trans. 128-D, Vol.128, No.7, 2008 3

Bi-Directional Isolated DC-DC Converter with SiC Devices

8 8 drain-source voltage is now blocked by the first JFET,

VT1 which is blocking the excess voltage, until the belong-

4 iL 4 ing Diode between the gate of the upper and the lower

VT2

Voltage [kV]

Current [A]

JFET reaches its avalanche blocking voltage. At this

0 0 point the avalanche current is flowing and the gate of

the second JFET drops down below its source potential.

-4 -4 The gate-source voltage of the second JFET is negative

and therefore in blocking state. For the next stages this

-8 -8 process is iterative until the DC-link voltage is blocked.

0 10 20 30 40

Time [µs] 4. Design of DC-DC converter

Fig. 6. Simulated waveforms for the phase shift In the following the design of the SiC DC-DC con-

mode at V1 = V2 = 6.1kV and POut = 20kW (fs =

50kHz, φ = π/3). verter for an output power of 20kW is presented. For

calculating the switching and conduction losses measure-

ment results for the SiC JFET are presented. Moreover,

In order to achieve the required blocking voltage for the design of the high voltage transformer will be dis-

the DC-link input voltage, multiple modules must be cussed in detail and a 3D model of the converter is pre-

connected in series. Since the conventional JFET is a sented.

normally-on device a low-voltage Si MOSFET is con- 4.1 Experimental Results For an application

nected in series to the JFETs. In the series connec- in the distribution system with the specifications given

tion the normally-off MOSFET allows a normally-off in table 1 the HV switch consists of two modules B and

behaviour of the cascode and a control of the series one module A, resulting in a total blocking voltage of

switch by a standard gate drive circuit. Both mod- 9kV. There, a safety voltage margin is included for dy-

ules are mounted in a SEMITOP package (figure 7) namic voltage balancing. In the following these three

by Semikron International [7]. The ratings of the JFET series connected modules are denoted as one HV switch.

are a blocking voltage VCES of 1500V and a continuous For determining the switching and conducting losses

drain current ID of 8A. an experimental setup as shown in figure 8 was built.

The basic concept of the SiC JFET cascode switch is There, also a simplified schematic is given. On the high

described in [8]. There, also the static blocking charac- voltage side the gate of the HV switch is connected to

teristics and the dynamic switching behaviour are dis- the source so that it works as freewheeling diode. The

cussed. In the on-state of the SiC JFET cascode, a HV switch on the low voltage side is actively controlled

positive gate voltage is applied to the MOSFET. Then, by a gate driver.

the gate of the lower JFET in the A module is con- In a first step single pulses for testing the turn-off be-

nected to the source of the MOSFET and the JFET is haviour with an inductive load at different current am-

conducting. Also the other in series connected JFETs plitudes have been acquired. With the measured current

are conducting due to its already mentioned normally- and voltage waveforms the ZVS turn-off losses of the

on characteristics. For this case the JFETs work as a DAB converter can be calculated. In a next step double

resistor connected in series to the on-resistance of the pulse measurements will be performed in order to test

MOSFET. also the turn-on behaviour of the SiC JFET devices.

In the blocking state the MOSFET gate is shorted to The gate drive circuit is designed with a small trans-

the ground and the drain-source voltage of the MOS- former, which could withstand the 6.1kV DC-link volt-

FET increases until the pinch-off voltage of the first age, for the gate drive power supply. Furthermore, the

JFET is reached. Further increasing of the MOSFET’s gate drive signal is transferred via fiber optic to the gate

driver, where the standard MOSFET driver IXDI409SI

D

22mm +Vdc

Gate Drive

B

B

100mm L

Ceramic

Capacitors

B

Gate

46mm Signal

A

A

Film cf. Figure 7

Capacitors

G Fan 215mm

S 103mm

Fig. 7. SiC JFET cascode mounted in a SEMI- Fig. 8. Power loss measurement setup for the HV

TOP package. switch with the corresponding simplified schematic.

IEEJ Trans. 128-D, Vol.128, No.7, 2008 4

Bi-Directional Isolated DC-DC Converter with SiC Devices

from IXYS is used. The gate-source voltage to turn the as soon as the upper switch is turned-on. Due to this

HV switch on is +12V. For turning the MOSFET off a approximately capacitive turn-off behaviour (ZVS) the

negative gate-source voltage of -12V is used in order to turn-off and also the turn-on switching losses are negli-

reduced the influence of induced noise. gible.

In the test circuit (figure 8) the HV switch is on There, the interlocking delay time must be larger than

the bottom side of the PCB between the film capacitors the rise time of the drain-source voltage in order to guar-

mounted on a heat sink behind the fan. Additionally, to antee soft switching. In the considered case with a volt-

the film capacitances ceramic capacitors are placed on age of 5kV a interlocking time of at least 80ns results

the top side close to the switches in order to minimise (depending on the load current and the ZVS range).

the stray inductance and reduce voltage overshoot. For a constant load current this time will increase with

In figure 9 and figure 10 experimental results for the higher DC-link voltages, since the parasitic capacitances

switching behaviour with a DC-link voltage of 5kV and must be dis-/charged by the load current.

a gate resistance of Rof f = 10Ω for turning off and of In figure 12 the drain-source voltages for different

Ron = 0Ω for turning on are presented. The measure- load currents are shown at turn-off. There, the on time

ments are made with high voltage probes from LeCroy of the HV switch and the load was the same for all DC-

and trimmed, isolated current transformers. link voltages. Since the parasitic capacitances of the

The turn-on current waveform in figure 9 of the HV JFETs and the load must be dis/-charged by the load

switch shows a significant peak of capacitive current dur- current, the dv/dt increases with increasing load cur-

ing the falling edge of the voltage. This usually would rent. This results in a decreasing rise times of the HV

result in significant turn-on losses of the SiC JFET. In switch voltage for increasing load current. At a DC-

the DAB, however, the switch is operated under ZVS link voltage of 5kV the dv/dt is approximately 60kV/µs

conditions what leads to negligible turn-on losses, since for turn on and 70kV/µs for turn off (ILoad = 5A,

the parasitic capacitances are dis-/charged by the load Rof f = 10Ω/Ron = 0Ω).

current and the switches are turned on at zero voltage During the switching tests several voltage balancing

[9, 10]. diodes (FRED) of the integrated modules have been de-

In figure 10 the turn-off characteristic is shown. There, stroyed. This was caused due to excessive avalanche

the current first decreases rapidly to half of the origi- energies during the turn-off of the JFETs at rising volt-

nal drain current, stays constant and then falls down ages. Therefore, a discrete setup with a Si-MOSFET,

to zero. The total fall time of the current is approxi- SiC JFETs and Si-balancing diodes has been designed

mately 80ns. The drain-source voltage VDS rises within as shown in figure 13. Due to limitations of the current

70ns. This current shape reflects a capacitive turn-off voltage source, measurements could be just performed

behaviour (cf. figure 10). up to 5kV, but the switching behaviour will be investi-

The equivalent circuit during the ZVS turn-off is gated at higher voltages with a new power supply in a

shown in figure 11. During the period (A) the load cur- future paper.

rent flows through the low side HV switch. At turn-off, Besides the switching losses also the conduction losses

the current splits up into two capacitive currents (B). are required for calculating the overall system losses.

One is charging the lower capacitance which has a high Therefore, the on-resistance RDS,on of the HV switch

value at low drain-source voltage. With increasing volt- has been measured. The value is approximately 1.35Ω

age the capacitance is decreasing due to the spreading at 25◦ C, which results in 18.7W conduction losses in

space charge region. The second current is discharging forward direction per HV switch at 50kHz and a contin-

the capacitance of the upper switch, which is increasing uous load current of 4A. For higher temperatures this

with increasing voltage. Finally, the load current flows value must be multiplied by (Tj /298)1.6 , where Tj is the

through the freewheeling diode of the upper HV switch absolute junction temperature.

(C) and then in reverse direction through the n-channel In the reverse direction the current first flows through

6.0 6 6.0 6

Voltage Capacitive

Peak Current

Voltage [ kV ]

Voltage [ kV ]

4.0 4 4.0 4

Current [ A ]

Current [ A ]

2.0 2 2.0 2

Current Voltage Current

0 0 0 0

0 35 70 105 140 175 0 35 70 105 140 175

Time [ ns ] Time [ ns ]

Fig. 9. Turn-on characteristic of the SiC HV Fig. 10. Turn-off characteristic of the SiC HV

switch: drain-source voltage and drain-source cur- switch: drain-source voltage and drain-source

rent. current.

IEEJ Trans. 128-D, Vol.128, No.7, 2008 5

Bi-Directional Isolated DC-DC Converter with SiC Devices

+Vdc +Vdc +Vdc

SiC JFETs

cf. Figure 7 Fan

Current L L L MOSFET

Measurement Diode

Heat sink

cf. Figure 7

Fig. 13. High-voltage SiC switch built with dis-

crete components.

A B C

Fig. 11. Current flow during turn-off: A) HV For calculating the core losses Van den Bossche’s [11]

switch is in on-state. B) Charge/discharge of ca- loss model of ferrites cores, considering non-sinusoidal

pacitors. C) High side diode is conducting.

waveforms, is used and compared to the losses result-

ing with the conventional Steinmetz equation and with

also the modified Steinmetz equation [12]. The values

the antiparallel diodes of the MOSFET and of the

of the loss models do not differ significantly and for the

JFETs. The forward voltage of the intrinsic antipar-

considered design the worst case value is used.

allel JFET diodes is in the range of 4V at a current

Based on these equations different ferrite materials

of 4A. This would lead to relatively large conduction

have been examined. There, it turned out that the N87

losses during the freewheeling period. However, as soon

material from Epcos has the lowest core losses at the

as the MOSFET and the JFETs are turned on the cur-

specified switching frequency of 50kHz and a maximal

rent could also flow in reverse direction through the n-

flux density of 150mT. The core selection results in four

channel of the MOSFET/JFETs which has a resistance

UU93/152/30 cores, where the primary and secondary

in the range of 1.35Ω what results in much lower reverse

winding are wounded around the middle leg as shown in

conduction losses. These are 3.7W per HV switch for

the 3D-Model (figure 16) of the 20kW DC-DC converter

conducting MOSFET/JFETs and 0.39W for the short

system. For choosing the number of turns and also the

period where the freewheeling diodes are conducting.

flux density in the core different designs have been com-

4.2 High Voltage - High Frequency Trans-

pared. There, it turned out that with 120 turns on the

former In the next-generation BTB system the line-

primary and on the secondary winding the lowest over-

frequency transformer should be replaced by a HV trans-

all losses occur. In this operating point also the core

former operating at HF. Each DC-DC converter in the

and the HF losses in the windings are approximately

BTB system uses one transformer which also ensures the

balanced.

galvanic isolation between the input and output stage.

For guaranteeing a high isolation voltage the distance

The HV-HF transformer is one of the core elements in

between the windings and also between the winding and

DAB operation considering power transfer and efficiency

the core must be large enough and some high voltage

of the whole DC-DC converter. The phase shift opera-

isolating material must be used for the bobbin. Fur-

tion mode of the DAB defines the requirements of the

thermore, the winding should be covered by an isolating

transformer, which will be designed in the following for

material at the outer side between the winding and the

an output power of 20kW and a phase shift angle be-

core. The insulation of the wire itself must be capable

tween π4 and π3 . Due to the HF operation ferrite mate-

of withstanding at least voltage between the different

rial must be used for the core and the HF losses in the

layers of the winding. These requirements significantly

windings must be considered.

influence the winding arrangement of the transformer.

In figure 14 a possible arrangement, which fulfils the

6.0 above mentioned requirements, is shown.

There, each winding is distributed into three cham-

bers in order to reduce the layer voltage and the para-

Voltage [ kV ]

4.0

2.7 A 96mm

2.0 4.0 A 1mm 2mm 8mm

5.6 A P P S P S S

7.3 A

0 9.7 A

0 35 70 105 140 175

Time [ ns ]

35mm Core

Fig. 12. HV SiC switch turn-off behaviour for dif-

ferent load currents. Fig. 14. Arrangement of the transformer windings.

IEEJ Trans. 128-D, Vol.128, No.7, 2008 6

Bi-Directional Isolated DC-DC Converter with SiC Devices

Table 4. Characterization of the HV-HF transformer.

Insulation

Material N87

Turn Number 120

Turn Ratio 1:1

Transferred Power 20kW

Inter-

P P S P S S Core Losses (25◦ C) 35W

leaved

(100◦ C) 15W

winding

HF Losses (25◦ C) 24W

(100◦ C) 30W

Leakage Inductance 3.4mH

Main Inductance 215mH

Core Magnetising Current 283mA

Specified max. Flux Density 150mT

Fig. 15. Energy density in a cut plane through Effective Cross Section 3360mm2

the core determined by a 3D FEM simulation with Effective Volume 1188cm3

MaxwellT M of the specified transformer as shown

in figure 14.

For reducing the influence of skin- and proximity

effects litz wire with 315 strands/strand diameter of

sitic capacitance of the transformer [13]. This results in 0.071mm, a total external diameter of 2.01mm and

a relatively low layer voltage, what is important for the 1.27mm2 cross section is used.

high frequency operation with high dv/dt-values. The 4.3 Rectifier/Inverter Besides the DC-DC con-

fast edges of the voltage leads to a non uniform voltage verter also single phase PWM converters in the input

distribution between the single turns of one winding and (rectifier) and output (inverter) stage of the BTB sys-

to higher turn voltages at the ends of the winding dur- tem are required. There, also the HV SiC cascodes is ap-

ing high dv/dt. This is like charging a transmission line plied as switching device in order to reduce the switching

with a voltage pulse where a wave travels along the line losses and the number of series connected stages. The se-

until a uniform distribution is reached. This effect will lection of the switching frequency is a trade-off between

be examined in detail in a future paper. switching/HF-/capacitor losses and the size of the in-

Another advantage of the higher number of chambers put/output inductance. With the relatively low switch-

is an interleaving of the windings which could be used ing losses of the SiC cascode a switching frequency of

for reducing the HF losses in the windings or to control 50kHz is achievable what results in small passive com-

the leakage inductance of the transformer. In the con- ponents.

sidered case the two inner chambers are interleaved, i.e. The required capacitance for a voltage ripple

primary and secondary chamber are exchanged and a vDC,link,pp of less than 5% of the DC-link voltage

sequence: primary - primary - secondary - primary - sec- VDC,link can be calculated [14] by

ondary - secondary chamber results (cf. figure 14). The

two chambers in the middle of the winding window have P

CDC,min = , · · · · · · · · · (2)

less turns than the outer ones. Instead of 9 layers and 5 VDC,link · ω · vDC,link,pp

turns per layer, only 6 layers and 5 turns. With this ar-

rangement a leakage inductance of approximately 4mH – where P is the nominal power and ω is the line-

calculated by 3D FEM simulations with MAXWELLT M frequency. For dimensioning the input/output inductor

(cf. figure 15)– results. This inductance is required for a maximal admissible current ripple of 5% of the nom-

transferring the rated power of 20kW at the optimal inal current amplitude IN,i is assumed. Therefore, a

phase shift angle of π/3. Thus, no additional external minimal inductance L (cf. figure 5) of

inductor is needed and the power density of the system VDC,link

increases. L= · · · · · · · · · · · · · · · · · · · · · · · · · · · (3)

fS 8 · 5% IN,i

In conventional windings the layers are wound from

the left to the right and then back in the next layer (S- is required, where fS again is the switching frequency.

or U-winding). There, the maximum voltage between With the specifications for the 20kW system in table

two consecutive layers is twice the layer voltage – in 3 a capacitance value of 34.2µF and an input/output

the considered case maximal 500V . This relatively high inductance value of L = 41mH (cf. figure 3) results.

layer-to-layer voltage could be divided by two with a 4.4 3D-Model of DAB converter In order to

Z-winding, where each layer is wound in the same di- achieve a small volume of the system a compact layout of

rection, i.e. for example all layers are wound from left the DAB converter is required. Accordingly, an optimal

to right. In this case the wire must be returned to the placement of the components is essential. A 3D-model

beginning of the layer outside the chamber in order to of the DC-DC converter is shown in figure 16 with an ap-

avoid a crossing of all wires of the considered layer. In proximated power density of 1.9kW/dm3 and the power

order to guarantee a high isolating voltage also for the per kilogram is 1.39kW/kg.

returning wire also the middle leg of the core is sur- The DC-link capacitor is realised with electrolytic ca-

rounded by an insulation. In table 4 the transformer pacitor banks which consist of Epcos 450V/33µF capac-

design characteristics are summarised. itors. Between the two capacitor banks on the input and

IEEJ Trans. 128-D, Vol.128, No.7, 2008 7

Bi-Directional Isolated DC-DC Converter with SiC Devices

DC-Link SiC system have been evaluated based on measurement

Capacitors Removed

Heat Isolating Cover results. There, it could be seen that the SiC material

Sink Heat shows a better performance in comparison to the con-

Transformer

Sink

ventional Si material. In general, the achievable current

density, the operating temperature and the breakdown

120mm

voltage are higher and the switching and conduction

losses are lower. The drawback of the SiC material are

the limited current carrying capability (limited die size)

and the high price due to higher manufacturing costs for

240mm the SiC wafers/processing costs at the moment.

HV SiC 364mm

Switches Control Gate Drivers With the results for the 10kW/20kW system, a system

Board with the specifications given in table 1 for a BTB system

Fig. 16. 3D-model of the high voltage, high fre- of the distribution system in Japan at a rated power of

quency DC-DC converter featuring SiC JFET 1MW could be designed. Therefore, the Si IGBT sys-

cascode (removed isolating cover of transformer

tem [2] and the SiC JFET cascode system are scaled up

winding).

to this power level and are compared with respect to

power losses, the performance and the efficiency in the

output side of the DC-DC converter the full bridge with following. The differences between the two converter

four HV switches mounted on two heat sinks with fans systems are on the one hand the applied core materi-

is located. The gate drive circuits of the SiC JFET cas- als and on the other hand the semiconductor devices.

codes including auxiliary supply are mounted in between Due to the different semiconductor materials different

the upper and the lower heat sink. There, additionally switching frequencies and voltage levels result. In ta-

high voltage ceramic capacitors are placed close to the ble 6 the parameters of the scaled systems, referred to

modules for reducing the stray inductance. The control a transferred power of 1MW, are summarised.

circuit for the DC-DC converter and its supply could A significant advantage of the SiC JFET switch is the

be mounted below the transformer in a EMI protective high blocking voltage what results in only one converter

housing. cell per phase for a distribution system operating with

an AC line-to-line voltage of 6.6kV. In the Si system, ap-

5. Losses of Si System

plying commercial 1.7kV IGBTs, six in series connected

The comparative system with latest trench-gate Si IG- converter cells in each phase are required to adapt the

BTs, evaluated in [2], operates with a switching fre- voltage to the blocking capability of the Si DC-DC con-

quency of 20kHz, at a rated power of 10kW and with verter. The benefit of the larger amount of series con-

a DC-link voltage of 350V. An experimental setup was nected stages is, that the number of switching levels is

built and measurements results were presented. Based higher and therefore a smaller input/output inductance

on this the overall loss have been determined and a loss of the inverter/rectifier stage is required.

analysis was performed. To transfer a rated power of 1MW fifty 20kW SiC

The specified application is the same as for the SiC DC-DC converters, as presented in this paper, must be

system and is also based on the specification parame- connected in parallel and none of them in series. Due

ters of table 1. A summary of the determined power to the lower power rating of the Si DC-DC converters

component losses and magnetic losses of the Si System this number must be doubled for a 1MW Si system and

and also of the SiC system are given in table 5. because of the lower DC-link voltage (1.02kV) six Si

DC-DC converters are connected in series and also in

Table 5. Power losses based on measurements and parallel per phase. Resulting is a large number of power

simulations of the Si IGBT system and the SiC component devices in the Si system.

JFET system. (Inductor losses of the SiC-system The conduction losses of the Si IGBT system are dom-

are included in the transformer losses, since the in- inated by the current flowing through the switch at

ductance is realised by the leakage inductance of

the transformer.)

Si-IGBT (10kW) SiC-JFET (20kW) Table 6. Performance of the Si and SiC DC-DC

Core Loss HF Loss Core Loss HF Loss converters linear scaled for the 1MW systems. (Lσ

Transformer 20W 18W 35W 24W is the leakage inductance of the transformer.)

Inductor 9W 10W - -

Si-IGBT SiC-JFET

Switching Conduction Switching Conduction Number of Converters 100 50

Switch Losses 90W 189W ∼ 0W 90W Switching Frequency 20kHz 50kHz

Total Losses 336W 149W Conducting Losses 18.9kW 4.5kW

Switching Losses 9kW ∼ 0W

Transformer Core Losses 2kW 1.42kW (50◦ C)

Transformer HF Losses 1.8kW 1.3kW (50◦ C)

6. Comparison Si IGBT system - SiC

Inductor Core Losses 900W Integrated in Lσ

JFET system Inductor HF Losses 1kW Integrated in Lσ

In the previous section, the losses for the Si and the Efficiency 97% 99%

IEEJ Trans. 128-D, Vol.128, No.7, 2008 8

Bi-Directional Isolated DC-DC Converter with SiC Devices

the nominal operating point of 10kW. With a voltage References

drop of 5.9V and a RMS current of 32A, across two

IGBTs and two diodes, conduction losses of 189W, re- (1) N. Okada, ”’Control of loop distribution network and result,”’

spectively 18.9kW for the scaled 1MW system result. A Technical Meeting on Power Systems Engineering, IEEJ, 2000.

single HV SiC switch is operating at a rated current of (2) S. Inoue and H. Akagi, ”’A bi-directional isolated dc/dc con-

verter as a core circuit of the next-generation medium-voltage

4A (corresponding to 200A in the 1MW system) what

power conversion system,”’ IEEE Power Electronics Special-

leads to smaller conduction losses. With a measured ists Conference (PESC), 2006.

on-resistance of 1.4 Ω per HV switch 4.5kW conduction (3) http://www.siced.de

losses results for the 1MW system. (4) F. Krismer, S. Round, and J. W. Kolar, ”’Perfomance opti-

mization of a high current dual active bridge with a wide oper-

Due to ZVS conditions in both systems the switching ating voltage range,”’ Proc. 37th Power Electronis Specialists

losses could be reduced. The measured switching losses Conference, Jeju, Korea, June 18 - 22 2006.

in the Si system are 9kW, whereas the losses in the SiC (5) N. Schibli, ”’Symmetrical multilevel converters with two quad-

system can be neglected due to the fast switching of the rant DC-DC feeding,”’ PhD. Thesis, ETH Lausanne, 2000.

(6) B. Weis, M. Braun, P. Friedrichs, ”’Turn-off and short circuit

JFET and the relatively large output capacitance. behaviour of 4H SiC JFETs,”’ Industry Application Confer-

In the Si system Finemet FT-3M magnetic material is ence, Vol. 1, pp. 365 - 369, 30 Sept. - 4 Oct. 2001.

used for the transformer and the ferrite material PC44 (7) http://www.semikron.com

(8) R. Elpelt, P. Friedrichs, R. Schorner, K.-O. Dohnke,

for the inductor. Especially, Finemet allows a high sat-

H. Mitlehner,and D. Stephani, ”’Serial connection of SiC

uration magnetic flux density of 1.2T at a temperature VJFETs - features of a fast high voltage switch,”’ REE. Re-

of 100◦ C and shows a small temperature dependence at vue de l’Electricite et de l’Electronique, No. 2, pp. 60-68, Feb.

a range from 25◦ C to 150◦ C. In the SiC converter sys- 2004.

(9) G.G. Oggier, R. Ledhold, G.O. Garcia, A.R. Oliva, J.C. Balda,

tem the material N87 from Epcos was applied. There, F. Barlow, ”’Extending the ZVS Operating Range of Dual

an external inductor is not needed any more, because Active Bridge High-Power DC-DC Converters,”’ 37th IEEE

the transformer was designed with the necessary leak- Power Electronics Specialists Conference (PESC’06), 2006.

age inductance to transfer the rated power. This solu- (10) N. Mohan, T.M. Undeland, W.P. Robbins, ”’Chapter 9.6 in

Power Electronics - Cpnverters, Applications and Design,”’

tion allows a further reduction of the system volume and 3rd edition, John Wiley and Sons, 2003.

weight and also the magnetic losses. (11) A. Van den Bossche, V. C. Valchev, and G. B. Georgiev,

”’Measurement and Loss Model of Ferrites with Non-

7. Conclusion sinusoidal Waveforms,”’ 35th Annual IEEE Power Electronics

Specialists Conference, Aachen, Germany, Vol. 6, pp. 4814-

In this paper a bidirectional DC-DC converter based 4818, June 2004.

on high voltage SiC JFETs for a 1MW next-generation (12) J. Reinert, A. Brockmeyer, and Rik W. A. A. De Doncker,

back-to-back system of a distribution system is pre- ”’Calculation of Losses in Ferro- and Ferrimagnetic Materials

Based on the Modified Steinmetz Equation,”’ IEEE Trans-

sented and compared to a conventional Si system. For actions on Industry Applications, Vol. 37, No. 4, July/Aug.

validating the considerations a 20kW system operating 2001.

at a switching frequency of 50kHz with a DC-link volt- (13) J. Biela, J.W. Kolar, ”’Using Transformer Parasitics for Res-

onant Converters - A Review of the Calculation of the Stray

age of 6.1kV has been examined in detail and scaled

Capacitance of Transformers,”’ Conference Record of the 2005

up to 1MW. Based on a 3D CAD construction a power IEEE Industry Applications Conference 40th IAS Annual

density of 1.9kW/dm3 - 1.39kW/kg for the DC-DC con- Meeting, Hong Kong, China, Oct. 2 - 6.

verter has been determined. (14) R. D. Greul, ”’Modulare Dreiphasen-Pulsgleichrichtersysteme,”’

PhD. Thesis, ETH Zurich, 2006.

As integral part of the converter system also a

20kW/50kHz high voltage HF transformer with in-

creased leakage inductance for the dual active bridge has

Juergen Biela (Non-member) was born in Nuremberg, Ger-

been designed by analytical calculations and 3D FEM many, on July 12, 1974. He studied elec-

simulations. The power density of the transformer is trical engineering at the Friedrich-Alexander-

5.9kW/dm3 and 2.7kW/kg. Universitt Erlangen. During his studies he

For measuring the switching waveforms and the dealt in particular with resonant DC-link in-

verters at the Strathclyde University, Scot-

switching losses a high voltage test system has been con-

land and the active control of series connected

structed. Due to the fast switching of the JFETs, the IGCTs at the Technical University of Munich,

relatively large output capacitance and the ZVS opera- Germany. After he had received his diploma

tion of the DAB the switching losses are approximately degree with honours from FAU Erlangen in

negligible. With an on-resistance of 1.4Ω 90W conduc- 2000, he worked on inverters with very high switching frequen-

tion losses per 20kW DC-DC converter result. Due to cies, SiC components and EMC at the research department of

A&D Siemens, Germany. From July 2002 to Dec. 2005 he has

limitations of the current power supply the switching been a Ph.D. student at the PES, ETH Zurich. Since 2006 he is

losses have been measured only up to 5kV. Measure- working as PostDoc there and his research is focused on compact

ments at higher voltages with a new supply will be pre- DC-DC converter, magnetic components, pulsed power systems

sented in a future paper. and system optimisation.

In the comparison of the scaled 1MW Si and SiC sys-

tems the good material characteristic of SiC and the re-

sulting high operating frequency lead to a compact and

low loss system with an efficiency of approximately 99%

in contrast to 97% of the Si system.

IEEJ Trans. 128-D, Vol.128, No.7, 2008 9

Bi-Directional Isolated DC-DC Converter with SiC Devices

Daniel Aggeler (Non-member) was born on April 22, 1981. Hirofumi Akagi (Member) was born in Okayama, Japan,

He studied electrical engineering at the ETH in 1951. He received the B.S. degree from

Zurich. During his studies, he dealt with the Nagoya Institute of Technology, Nagoya,

power electronics and control engineering. His Japan, in 1974, and the M.S. and Ph.D. de-

master thesis research involved control strate- grees from the Tokyo Institute of Technology,

gies (harmonic elimination, direct power con- Tokyo, Japan, in 1976 and 1979, respectively,

trol) for 3-level grid connected inverters. Since all in electrical engineering. In 1979, he joined

2006, he is Ph.D. student at the PES, ETH the Nagaoka University of Technology, Na-

Zurich, and his current research is focused on gaoka, Japan, as an Assistant and then Asso-

high voltage, dual active bridge dc-dc convert- ciate Professor in the Department of Electrical

ers featuring SiC components. Engineering. In 1987, he was a Visiting Scientist at the Mas-

sachusetts Institute of Technology (M.I.T.), Cambridge, for ten

months. From 1991 to 1999, he was a Professor in the Department

Shigenori Inoue (Member) was born in Fujimi, Saitama, of Electrical Engineering, Okayama University, Okayama, Japan.

Japan, on January 29, 1979. He received B.S. From March to August 1996, he was a Visiting Professor at the

and M.S. degrees from the Tokyo Metropoli- University of Wisconsin-Madison and then M.I.T. Since January

tan University, in 2002 and 2004, respectively, 2000, he has been a Professor in the Department of Electrical

and the Ph.D. degree from the Tokyo Institute and Electronic Engineering, Tokyo Institute of Technology. He

of Technology in 2007. He is currently a Re- has published some 70 IEEE Transactions papers and two invited

search Fellow with the Japan Society for Pro- papers in the Proceedings of the IEEE. He has made presenta-

motion of Science (JSPS). His research inter- tions many times as a Keynote or Invited Speaker internationally.

ests include medium-voltage power conversion His research interests include power conversion systems, ac mo-

systems, bidirectional isolated dc-dc convert- tor drives, high-frequency resonant inverters for induction heating

ers, SiC/GaN-based power devices, and active power filters. and corona discharge treatment processes, and utility applications

of power electronics such as active filters for power conditioning,

self-commutated BTB systems, and FACTs devices.

Dr. Akagi received two IEEE IAS Transactions prize paper awards

in 1991 and in 2004, two IEEE PELS Transactions prize paper

awards in 1999 and in 2003, nine IEEE IAS Committee prize pa-

per awards, the IEEE William E. Newell Power Electronics Award

in 2001, and the IEEE IAS Outstanding Achievement Award in

2004. He was elected as a Distinguished Lecturer of the IEEE

Industry Applications and Power Electronics Societies for 1998-

1999. He currently is President of the IEEE Power Electronics

Society.

Johann W. Kolar (Member) studied industrial electronics

at the University of Technology Vienna, Aus-

tria, where he also received the Ph.D. degree

(summa cum laude). From 1984 to 2001 he

was with the University of Technology in Vi-

enna, where he was teaching and working in

research in close collaboration with the indus-

try. He has proposed numerous novel con-

verter topologies, e.g., the VIENNA Rectifier

and the Three-Phase AC-AC Sparse Matrix

Converter concept. Dr. Kolar has published over 200 scientific pa-

pers in international journals and conference proceedings and has

filed more than 50 patents. He was appointed Professor and Head

of the Power Electronics Systems Laboratory at the Swiss Federal

Institute of Technology (ETH) Zurich on Feb. 1, 2001. The focus

of his current research is on ultra-compact intelligent AC-AC and

DC-DC converter modules employing latest power semiconductor

technology (SiC), novel concepts for cooling and active EMI fil-

tering, multi-disciplinary simulation, bearing-less motors, power

MEMS, and wireless power transmission.

IEEJ Trans. 128-D, Vol.128, No.7, 2008 10

You might also like

- Control and Design of A Modular Multilevel Cascade BTB System Using Bidirectional Isolated DC DC ConvertersDocument8 pagesControl and Design of A Modular Multilevel Cascade BTB System Using Bidirectional Isolated DC DC Convertersjinlei chenNo ratings yet

- E1PWAX 2016 v16n4 1256 PDFDocument12 pagesE1PWAX 2016 v16n4 1256 PDFSunny ElNo ratings yet

- Liang 2019Document7 pagesLiang 2019mahesh babuNo ratings yet

- A Novel Single-Stage Full-Bridge Buck-Boost InverterDocument10 pagesA Novel Single-Stage Full-Bridge Buck-Boost InverteriiscgovindraiNo ratings yet

- 50.High-Efficiency Bidirectional Buck-BoostDocument12 pages50.High-Efficiency Bidirectional Buck-BoostPraful YadavNo ratings yet

- Aggeler SmartEnergyStrategies2008 1Document2 pagesAggeler SmartEnergyStrategies2008 1Akshay SathianNo ratings yet

- A Bidirectional DC-DC Converter For An Energy Storage System With Galvanic IsolationDocument8 pagesA Bidirectional DC-DC Converter For An Energy Storage System With Galvanic IsolationKrishnaChaitanyaNo ratings yet

- A Novel Lossless Passive Snubber For Soft-Switching Boost-Type ConvertersDocument5 pagesA Novel Lossless Passive Snubber For Soft-Switching Boost-Type ConvertersfauzanismailNo ratings yet

- 2016 Electrolytic Capacitor-LessDocument10 pages2016 Electrolytic Capacitor-Less하미드라힘No ratings yet

- Single-Phase Single-Stage Bidirectional Isolated ZVS AC-DC Converter With PFCDocument9 pagesSingle-Phase Single-Stage Bidirectional Isolated ZVS AC-DC Converter With PFCM UMAR ABBASINo ratings yet

- My First Draft Edit3Document8 pagesMy First Draft Edit3mohammed bawazeerNo ratings yet

- Jntua College of Engineering Kalikiri: Analysis of Fb-Zcs DC-DC Converter Using Dual-Capacitor CircuitDocument38 pagesJntua College of Engineering Kalikiri: Analysis of Fb-Zcs DC-DC Converter Using Dual-Capacitor CircuitAkkulagalla NagarajaNo ratings yet

- A Buck-Boost Common-Mode Transformerless Inverter For Photovoltaic ApplicationsDocument5 pagesA Buck-Boost Common-Mode Transformerless Inverter For Photovoltaic ApplicationsIndra PratamaNo ratings yet

- Lec 39-40Document46 pagesLec 39-40Siddharth KashyapNo ratings yet

- A Family of Bipolar High Step-Up ZetaBuckBoost Converter Based On Coat CircuitDocument12 pagesA Family of Bipolar High Step-Up ZetaBuckBoost Converter Based On Coat Circuitwinkavi87No ratings yet

- A Review On Single Phase To Three Phase Power Converters: Kaushal W. Kakad & Nitin R. BhasmeDocument10 pagesA Review On Single Phase To Three Phase Power Converters: Kaushal W. Kakad & Nitin R. BhasmeTJPRC PublicationsNo ratings yet

- Single Phase AC To AC Conversion Without Frequency RestrictionsDocument4 pagesSingle Phase AC To AC Conversion Without Frequency RestrictionsTaniyaNo ratings yet

- IGBT & Sic MosfetDocument7 pagesIGBT & Sic MosfetNgọc Hưng TạNo ratings yet

- Design Modelling Analysis and Implementation of Two Phase Interleaved Buck DC DC ConverterDocument8 pagesDesign Modelling Analysis and Implementation of Two Phase Interleaved Buck DC DC ConverterInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- The 1,400-MW Kii-Channel HVDC SystemDocument7 pagesThe 1,400-MW Kii-Channel HVDC SystemHashirama SenjuNo ratings yet

- A Single Switch Continuous Input Current Buck-Boost Converter With Non-Inverted Output VoltageDocument10 pagesA Single Switch Continuous Input Current Buck-Boost Converter With Non-Inverted Output VoltageSureshkumar AlagarsamyNo ratings yet

- 고전압비와 낮은 전압 스트레스를 가진 단일 스위치와 전압 체배 회로를 이용한 새로운 비절연형 DC-DC 컨버터Document5 pages고전압비와 낮은 전압 스트레스를 가진 단일 스위치와 전압 체배 회로를 이용한 새로운 비절연형 DC-DC 컨버터Armandinho CaveroNo ratings yet

- Design and Implementation of A 100 KW Sic Filter-Less PV Inverter With 5 KW/KG Power Density and 99.2% Cec EfficiencyDocument6 pagesDesign and Implementation of A 100 KW Sic Filter-Less PV Inverter With 5 KW/KG Power Density and 99.2% Cec EfficiencyadnantanNo ratings yet

- BJT Circuits - Basic Electronics GuideDocument55 pagesBJT Circuits - Basic Electronics GuideNenad Stamenović100% (1)

- Four Novel PWM Shoot-Through Control Methods For Impedance Source DC-DC ConvertersDocument10 pagesFour Novel PWM Shoot-Through Control Methods For Impedance Source DC-DC ConvertersUtkarsh PrakashNo ratings yet

- Soeiro 2010Document8 pagesSoeiro 2010wessamNo ratings yet

- 1 Megawatt, 20 KHZ, Isolated, Bidirectional 12Kv To 1.2Kv DC-DC Converter For Renewable Energy ApplicationsDocument8 pages1 Megawatt, 20 KHZ, Isolated, Bidirectional 12Kv To 1.2Kv DC-DC Converter For Renewable Energy ApplicationsJonxa BalenziagaNo ratings yet

- Electronics 07 00062Document19 pagesElectronics 07 00062sanafayaz12No ratings yet

- Design and Evaluation of A Novel Hybrid Sic-Gan Based Bidirectional Full-Bridge DC-DC ConverterDocument7 pagesDesign and Evaluation of A Novel Hybrid Sic-Gan Based Bidirectional Full-Bridge DC-DC ConverterVenkatesan SwamyNo ratings yet

- Series Parallel Switched Capacitor Based MLIDocument5 pagesSeries Parallel Switched Capacitor Based MLIabdelbassetNo ratings yet

- A New Transformerless Buck-Boost Converter With Positive Output VoltageDocument7 pagesA New Transformerless Buck-Boost Converter With Positive Output Voltagebhawna guptaNo ratings yet

- MVDC Voltage MultiplierDocument6 pagesMVDC Voltage Multiplierahmedallehyani5aNo ratings yet

- A Low-Cost Solar Micro-Inverter With Soft-SwitchingDocument6 pagesA Low-Cost Solar Micro-Inverter With Soft-Switchingmohamed parvezNo ratings yet

- Ircuit Onfiguration and Perating OdesDocument3 pagesIrcuit Onfiguration and Perating OdesMukul DasNo ratings yet

- EEM328 Electronics Laboratory - Experiment 4 - BJT BiasingDocument4 pagesEEM328 Electronics Laboratory - Experiment 4 - BJT Biasingdonatello84100% (1)

- Highly Compact AC-AC Converter Achieving A High Voltage Transfer RatioDocument8 pagesHighly Compact AC-AC Converter Achieving A High Voltage Transfer RatioRamKumarNo ratings yet

- A Fixed Frequency Zero-Voltage-Switching On-Board EV ChargerDocument9 pagesA Fixed Frequency Zero-Voltage-Switching On-Board EV Chargeraravind chukliNo ratings yet

- Filsecker 2014 ConverterDocument10 pagesFilsecker 2014 ConverterAhmadNo ratings yet

- High Efficiency AC-ACDocument11 pagesHigh Efficiency AC-ACBui DaiNo ratings yet

- JEE SampleDocument9 pagesJEE Samplejebarani.s.eeeNo ratings yet

- Comparative Analysis of Single and Three-Phase Dual Active Bridge Bidirectional DC-DC ConvertersDocument6 pagesComparative Analysis of Single and Three-Phase Dual Active Bridge Bidirectional DC-DC Convertersjeos20132013No ratings yet

- Isolated Bidirectional Grid-Tied Three-Phase Ac-Dc Power Conversion Using Series Resonant Converter Modules and A Three-Phase UnfolderDocument26 pagesIsolated Bidirectional Grid-Tied Three-Phase Ac-Dc Power Conversion Using Series Resonant Converter Modules and A Three-Phase UnfolderTajudeen TajuNo ratings yet

- Analysis of An Integrated Buck Zeta ConverterDocument9 pagesAnalysis of An Integrated Buck Zeta ConverterShravan_redNo ratings yet

- Theoretical Analysis of DC Link Capacitor Current Ripple Reduction in The HEV DC-DC Converter and Inverter System Using A Carrier Modulation MethodDocument8 pagesTheoretical Analysis of DC Link Capacitor Current Ripple Reduction in The HEV DC-DC Converter and Inverter System Using A Carrier Modulation MethodVanHieu LuyenNo ratings yet

- S4 EC1 LabDocument87 pagesS4 EC1 LabM N GeethasreeNo ratings yet

- Design and Simulation of Single Phase Z-Source Buck Boost Matrix ConverterDocument7 pagesDesign and Simulation of Single Phase Z-Source Buck Boost Matrix Convertervinay kumarNo ratings yet

- Power Converters, Control, and Energy Management For Distributed GenerationDocument5 pagesPower Converters, Control, and Energy Management For Distributed GenerationAbdelaziz IsmealNo ratings yet

- Single Phase Single Stage Bidirectional Isolated Zvs Acdc With PFCDocument8 pagesSingle Phase Single Stage Bidirectional Isolated Zvs Acdc With PFCSamyak ParakhNo ratings yet

- A Brushless DC Motor Drive-763 PDFDocument5 pagesA Brushless DC Motor Drive-763 PDFHarshal VaidyaNo ratings yet

- A Brushless DC Motor Drive-763Document5 pagesA Brushless DC Motor Drive-763Harshal VaidyaNo ratings yet

- L-1 (SSG) (Pe) ( (Ee) Nptel) 2Document5 pagesL-1 (SSG) (Pe) ( (Ee) Nptel) 2GagneNo ratings yet

- ICPE11 ImplDocument8 pagesICPE11 Implhans_fitz4134No ratings yet

- Biasing A TransistorDocument16 pagesBiasing A Transistorl_wondersNo ratings yet

- A Power Conversion System For Offshore Wind Parks: Marta - Molinas@elkraft - Ntnu.noDocument7 pagesA Power Conversion System For Offshore Wind Parks: Marta - Molinas@elkraft - Ntnu.nojohnsonNo ratings yet

- Cuk4acanddc LATEST DEVELOPMENTSDocument6 pagesCuk4acanddc LATEST DEVELOPMENTSAnonymous afzpkOo3No ratings yet

- 15 KV SiC MOSFET An Enabling Technology For Medium Voltage Solid State TransformersDocument13 pages15 KV SiC MOSFET An Enabling Technology For Medium Voltage Solid State TransformersHOD EEENo ratings yet

- A Bidirectional DC-DC Converter Topology For Low Power ApplicationDocument12 pagesA Bidirectional DC-DC Converter Topology For Low Power ApplicationHsekum RamukNo ratings yet

- Icit 2015 7125227Document6 pagesIcit 2015 7125227GosadorNo ratings yet

- A Zero-Voltage and Zero-Current Switching Full Bridge DC-DC Converter With Transformer IsolationDocument8 pagesA Zero-Voltage and Zero-Current Switching Full Bridge DC-DC Converter With Transformer IsolationJie99No ratings yet

- Power Electronics Applied to Industrial Systems and Transports, Volume 3: Switching Power SuppliesFrom EverandPower Electronics Applied to Industrial Systems and Transports, Volume 3: Switching Power SuppliesNo ratings yet

- Fuzzy Control Adaptive of A Matrix Converter For Harmonic Compensation Caused by Nonlinear LoadsDocument9 pagesFuzzy Control Adaptive of A Matrix Converter For Harmonic Compensation Caused by Nonlinear LoadsPrasad SolasaNo ratings yet

- Neural Predictive ControllerDocument10 pagesNeural Predictive ControllerPrasad SolasaNo ratings yet

- Interview List BEL Project Engineer.Document1 pageInterview List BEL Project Engineer.Prasad SolasaNo ratings yet

- JNTUADocument178 pagesJNTUAPrasad SolasaNo ratings yet

- WWW - Ssckkr.kar - Nic.in: SSC, Eastern Region SSC, Karnataka Kerala RegionDocument1 pageWWW - Ssckkr.kar - Nic.in: SSC, Eastern Region SSC, Karnataka Kerala RegionPrasad SolasaNo ratings yet

- WWW Jnanabhumi Ap Gov inDocument1 pageWWW Jnanabhumi Ap Gov inPrasad SolasaNo ratings yet

- Ee DH Ar 'S: Baahubali Chart (Tenses/ Speech / Voice / If Chart / D.O.C.)Document1 pageEe DH Ar 'S: Baahubali Chart (Tenses/ Speech / Voice / If Chart / D.O.C.)Prasad SolasaNo ratings yet

- Examinations: TR WryfevaluarronDocument3 pagesExaminations: TR WryfevaluarronPrasad SolasaNo ratings yet

- IEEE 2013 - 2012 Projects in Power Electronics, PDFDocument55 pagesIEEE 2013 - 2012 Projects in Power Electronics, PDFShashi ShekharNo ratings yet

- Railway Signalling Installation and Quality Hand BookDocument284 pagesRailway Signalling Installation and Quality Hand BookVijay Khanchi100% (21)

- Comparative Review of Modulation Techniques For Harmonic Minimization in Multilevel InverterDocument8 pagesComparative Review of Modulation Techniques For Harmonic Minimization in Multilevel InverterMYNAMENo ratings yet

- CDA 3000 - Application ManualDocument472 pagesCDA 3000 - Application ManualKarthi Keyan100% (1)

- Demag CraneDocument12 pagesDemag Cranesaleh.sajjadyNo ratings yet

- Design of A Bar Soap Making Machine For Local Soap IndustryDocument70 pagesDesign of A Bar Soap Making Machine For Local Soap IndustryOgochukwu73% (11)

- Service Guide SpecificationDocument30 pagesService Guide SpecificationLuiz Roberto Honório Alves FilhoNo ratings yet

- 3 Phase Inverter - 180 Degree Conduction: Seema MathewDocument16 pages3 Phase Inverter - 180 Degree Conduction: Seema MathewAniruddha PhalakNo ratings yet

- Chapter 1 3Document31 pagesChapter 1 3Michael Camit EsoNo ratings yet

- MP60 Series & MPS2000C Series: 16kW Modular Power Systems Designed Specifically For Telecom and Datacom IndustriesDocument4 pagesMP60 Series & MPS2000C Series: 16kW Modular Power Systems Designed Specifically For Telecom and Datacom IndustriesfouedNo ratings yet

- HEF4069UB: 1. General DescriptionDocument17 pagesHEF4069UB: 1. General DescriptionJoel PalzaNo ratings yet

- EN 647 - Distributed Generation and MicrogridsDocument53 pagesEN 647 - Distributed Generation and MicrogridsSumeet MehardaNo ratings yet

- Paper 9 PDFDocument10 pagesPaper 9 PDFLimuel EspirituNo ratings yet

- b215 A H PDFDocument84 pagesb215 A H PDFfikri rahmanNo ratings yet

- Invisimo User ManualDocument4 pagesInvisimo User ManualAzaelNo ratings yet

- 08 CET Power - Module & Controller Replacement Procedure V1.2Document2 pages08 CET Power - Module & Controller Replacement Procedure V1.2leonardomarinNo ratings yet

- Power+ A Parallel Redundant UPS - Uninterruptible Power SupplyDocument8 pagesPower+ A Parallel Redundant UPS - Uninterruptible Power SupplyGamatronicNo ratings yet

- Solar and Wind Hybrid Street Light SystemDocument70 pagesSolar and Wind Hybrid Street Light SystemTarun S75% (4)

- Solar Power Plant Project ProposalDocument29 pagesSolar Power Plant Project ProposalKhehracybercafe SahnewalNo ratings yet

- BHEL Customersisg - Ref - List PDFDocument34 pagesBHEL Customersisg - Ref - List PDFSajinNo ratings yet

- Solar PV Systems Based On Nec CodeDocument10 pagesSolar PV Systems Based On Nec CodeDomingo Ruiz100% (1)

- Cemont s1000 Mma 85a InverterDocument30 pagesCemont s1000 Mma 85a InverterJoaquim MoraisNo ratings yet

- En - Power Management Guide2019 PDFDocument92 pagesEn - Power Management Guide2019 PDFHaroldo VieiraNo ratings yet

- MC3PHACDocument36 pagesMC3PHACBảo BìnhNo ratings yet

- Catalog STM DriveDocument135 pagesCatalog STM DriveIvan SilvaNo ratings yet

- ECN3021Document10 pagesECN3021Wasang Juwi PracihnoNo ratings yet

- Service Manual LCD Monitor Dell 2209WADocument85 pagesService Manual LCD Monitor Dell 2209WAtda8362aNo ratings yet

- RAC Fault Codes: Display Error Code Flashing Lights Fault Indoor Outdoor Indoor OperationDocument7 pagesRAC Fault Codes: Display Error Code Flashing Lights Fault Indoor Outdoor Indoor Operationrenat axmerovNo ratings yet

- Catalogue 2017Document30 pagesCatalogue 2017Muhammad Muzammil EjazNo ratings yet

- York Mini VRF CatalogDocument56 pagesYork Mini VRF Cataloghamza100% (2)