Professional Documents

Culture Documents

BE EC5303 DSD Nov2021 QP2

BE EC5303 DSD Nov2021 QP2

Uploaded by

hello worldOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

BE EC5303 DSD Nov2021 QP2

BE EC5303 DSD Nov2021 QP2

Uploaded by

hello worldCopyright:

Available Formats

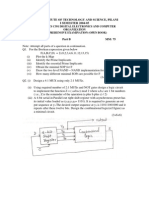

DEPT.

of ECE, CEG, ANNA UNIVERSITY

EC 5303 Digital System Design

ASSESSMENT – II

Date: 24-11-2021 Duration: 1 hr Max. Marks: 25

Part-A (5 x 2 =10 Marks)

Q.No. Marks CO BL

1 Construct JK FF using RS FF. 2 3 1

2 What is the logic required to restart (i.e. make it to go 2 3 2

to the state 0000) the 4-bit ripple counter when it

reaches the state 1010.

3 Develop the transition table for the given expression. 2 4 3

Y1 = x’y1’ + xy2

Y2 = x’y1 + x’y2’

Where y1,y2 are present states and Y1,Y2 are next states

and x is the user input.

4 Simplify the function F(A,B,C,D) = 2 4 3

∑(0,2,6,7,8,10,12). What is the modification to

required to prevent static-1 hazard the given Function.

5 (i)Draw the transition (state) diagram for the following 1+1=2 4 3

transition table.

(ii)How many flip flops are required to design a race

free asynchronous sequential circuit for the given flow

table.

where X,Y are inputs.

Part-B (7 marks)

Q.No. Marks CO BL

6a Design a synchronous counter using T FFs for the 7 3 3

states 1,0,5,7,6,1,0,5,7,6…repeat. Next state for all

the unused states is 3.

OR

7 3 3

6b Consider two flipflops A,B and one input x to design

a sequential circuit with the following flipflop inputs.

Develop the state table and its logic diagram

JA = Bx’ KA = B

JB = Ax KB = A’x’ +Ax

Part-C (8 Marks)

Q.No. Marks CO BL

7 Obtain a primitive flow table for a circuit with two 8 4 3

inputs x1 and x2 and two outputs Z1 and Z2 that satisfy

the following four conditions. Both inputs do not

change simultaneously.

i. When x1x2 = 00, the output is z1z2=00

ii. When x1 =1 and x2 changes from 0 to 1, the

output is z1z2 = 01.

iii. When x2 =1 and x1 changes from 0 to 1, the

output is z1z2 = 10.

iv. Otherwise the output does not change.

*********

CO1 CO2 CO3 CO4 CO5

- - 11 14 -

You might also like

- Rr210203 Switching Theory and Logic DesignDocument8 pagesRr210203 Switching Theory and Logic DesignSrinivasa Rao G100% (2)

- Answer Two Questions, Question No. 3 Is CompulsoryDocument3 pagesAnswer Two Questions, Question No. 3 Is CompulsoryABHILESH G KNo ratings yet

- Apr - May 2023Document3 pagesApr - May 2023Pandyselvi BalasubramanianNo ratings yet

- DLD Ques2Document2 pagesDLD Ques2mahbub mitulNo ratings yet

- DE Assignment-3Document2 pagesDE Assignment-3shivajisingh12345678123456No ratings yet

- Question Paper Code:: Y Abcababc + + +Document3 pagesQuestion Paper Code:: Y Abcababc + + +karthick VijayanNo ratings yet

- Q 6Document3 pagesQ 6Saranya MohanNo ratings yet

- ECE20022 Assignment Module 1 2 3Document3 pagesECE20022 Assignment Module 1 2 3Nandini PandeyNo ratings yet

- DSD Assessment 2Document3 pagesDSD Assessment 2hello worldNo ratings yet

- 9A04306 Digital Logic DesignDocument4 pages9A04306 Digital Logic DesignsivabharathamurthyNo ratings yet

- EE8351 Iq 16 Marks PDFDocument7 pagesEE8351 Iq 16 Marks PDFdeepika senthilNo ratings yet

- 15es3gcdec Dec 2017Document4 pages15es3gcdec Dec 2017MAHESHA GNo ratings yet

- EC8392-Digital EletronicsDocument2 pagesEC8392-Digital Eletronicssyed1188No ratings yet

- 15es3gcdec Jan 2018Document2 pages15es3gcdec Jan 2018MAHESHA GNo ratings yet

- 4 EEE EE2255-ModelDocument2 pages4 EEE EE2255-ModelBIBIN CHIDAMBARANATHANNo ratings yet

- Bca 101Document4 pagesBca 101Avirup ShomeNo ratings yet

- Name: Digital Logic Circuits (Common To ICE) Part A (20X2 40 Marks) Answer All QuestionsDocument2 pagesName: Digital Logic Circuits (Common To ICE) Part A (20X2 40 Marks) Answer All QuestionsAnonymous yO7rcec6vuNo ratings yet

- STLD3 - Question BankDocument6 pagesSTLD3 - Question Bankvidhya_bineeshNo ratings yet

- Digital Electronic Circuits (ELE 2102) RCS (MAKE UP) Dec 17Document2 pagesDigital Electronic Circuits (ELE 2102) RCS (MAKE UP) Dec 17Abhinav KumarNo ratings yet

- R13 Nov 2016Document2 pagesR13 Nov 2016Anil Kumar BNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document2 pagesQuestion Paper Code:: (10×2 20 Marks)kenny kannaNo ratings yet

- Question Bank M Tech 2ND Sem Batch 2018Document31 pagesQuestion Bank M Tech 2ND Sem Batch 2018king khanNo ratings yet

- Assignment EDES232CDocument3 pagesAssignment EDES232CPrakash DasNo ratings yet

- Digital 16 Marks.Document4 pagesDigital 16 Marks.Saranya PrabhuNo ratings yet

- Template Assignment 3Document3 pagesTemplate Assignment 3Sador YonasNo ratings yet

- Electronics and Communication Engineering: 1. WorkDocument16 pagesElectronics and Communication Engineering: 1. Workpankaj rangareeNo ratings yet

- DLD - Question - Final 2022Document2 pagesDLD - Question - Final 2022Md Israfil HossainNo ratings yet

- QBank DPSD cs2202Document6 pagesQBank DPSD cs2202kunarajNo ratings yet

- Testpaper - 1 NTDocument13 pagesTestpaper - 1 NTGattu SadashivaNo ratings yet

- Btech Biomed 4 Sem Digital Electronics Circuit Pbm4i102 2018Document3 pagesBtech Biomed 4 Sem Digital Electronics Circuit Pbm4i102 2018Narinder MauryaNo ratings yet

- Important 16 Mark Questions-19!1!2024Document5 pagesImportant 16 Mark Questions-19!1!2024FLOWERNo ratings yet

- Logic AssignmentDocument4 pagesLogic AssignmentYeshiwas KefaleNo ratings yet

- Digital Paper1Document5 pagesDigital Paper1Iyyakutti GanapathiNo ratings yet

- Obtain The 9's and 10's Complement ofDocument3 pagesObtain The 9's and 10's Complement ofNandha Kizor VNo ratings yet

- Rr210203 Switching Theory and Logic DesignDocument9 pagesRr210203 Switching Theory and Logic DesignSrinivasa Rao GNo ratings yet

- Ecs-301 Digital Logic Design 2010-11Document4 pagesEcs-301 Digital Logic Design 2010-11Satyedra MauryaNo ratings yet

- DD Co QuestionsDocument8 pagesDD Co QuestionsRohit M ANo ratings yet

- Convolutional Codes: L K StagesDocument12 pagesConvolutional Codes: L K StagesParneet KaurNo ratings yet

- Ec1312 DLCDocument5 pagesEc1312 DLCDeepak RavichandranNo ratings yet

- EE2001 Tutorial 5Document9 pagesEE2001 Tutorial 5RetheshNo ratings yet

- DLD Ques1Document2 pagesDLD Ques1mahbub mitulNo ratings yet

- 2001 Paper E2.1/ISE2.2: Digital Electronics IIDocument12 pages2001 Paper E2.1/ISE2.2: Digital Electronics IIkolkassNo ratings yet

- What Is Meant by Register TransferDocument4 pagesWhat Is Meant by Register TransferSiva GuruNo ratings yet

- W-06-part2-LogicFuncRepresentation (K-Maps)Document40 pagesW-06-part2-LogicFuncRepresentation (K-Maps)Eray GülerNo ratings yet

- L-3/T - 2/EEE Date: 28/0312022: IS) +D (I, 3,6,7)Document19 pagesL-3/T - 2/EEE Date: 28/0312022: IS) +D (I, 3,6,7)Sanjid ElahiNo ratings yet

- UCSB ECE 152a Course ReaderDocument19 pagesUCSB ECE 152a Course Readermuhd220No ratings yet

- Assignment (EEE 323) For 2017-18 BatchDocument2 pagesAssignment (EEE 323) For 2017-18 BatchMaruf MorshedNo ratings yet

- Birla Institute of Technology and Science, Pilani I SEMESTER 2004-05Document6 pagesBirla Institute of Technology and Science, Pilani I SEMESTER 2004-05navaneeth_kumarNo ratings yet

- CompoundDocument4 pagesCompounduscrNo ratings yet

- UEC001Document2 pagesUEC001Abhav BansalNo ratings yet

- 113BU032016Document2 pages113BU032016mushahedNo ratings yet

- AP Calc BC Sem 1 Final ReviewDocument12 pagesAP Calc BC Sem 1 Final ReviewJess PeraltaNo ratings yet

- 9A04306 Digital Logic DesignDocument4 pages9A04306 Digital Logic DesignMahaboob SubahanNo ratings yet

- QuestinsDocument6 pagesQuestinsSujeet KumarNo ratings yet

- Tables of the Function w (z)- e-z2 ? ex2 dx: Mathematical Tables Series, Vol. 27From EverandTables of the Function w (z)- e-z2 ? ex2 dx: Mathematical Tables Series, Vol. 27No ratings yet

- Test Bank for Precalculus: Functions & GraphsFrom EverandTest Bank for Precalculus: Functions & GraphsRating: 5 out of 5 stars5/5 (1)

- Ten-Decimal Tables of the Logarithms of Complex Numbers and for the Transformation from Cartesian to Polar Coordinates: Volume 33 in Mathematical Tables SeriesFrom EverandTen-Decimal Tables of the Logarithms of Complex Numbers and for the Transformation from Cartesian to Polar Coordinates: Volume 33 in Mathematical Tables SeriesNo ratings yet

- Syllable Stress - American EnglishDocument21 pagesSyllable Stress - American EnglishMirella Gomes da SilvaNo ratings yet

- ServiceNow Process Guide RELEASEDocument31 pagesServiceNow Process Guide RELEASEOh100% (2)

- I John 1:8-10: Literal Translation Greek/English Interlinear Overall DiagramDocument8 pagesI John 1:8-10: Literal Translation Greek/English Interlinear Overall DiagrambiblicalgeekNo ratings yet

- Department of Electronics and Communication Engineering Saintgits College of EngineeringDocument41 pagesDepartment of Electronics and Communication Engineering Saintgits College of EngineeringGeorgeyfkNo ratings yet

- A New Arabic Grammar of The Written Language 1965Document353 pagesA New Arabic Grammar of The Written Language 1965Kollektor100% (11)

- Welcome To Colaboratory - ColaboratoryDocument5 pagesWelcome To Colaboratory - ColaboratorychairahmaulidaNo ratings yet

- New Round Up 4 Student S Book-72-79Document8 pagesNew Round Up 4 Student S Book-72-79lan anh nguyenNo ratings yet

- SPM CEFR Speaking Tips Part 1 and Part 2Document1 pageSPM CEFR Speaking Tips Part 1 and Part 2JESSICA MAPONG MUYONG KPM-GuruNo ratings yet

- Melsec Iq-R Profibus-Dp Module Function Block ReferenceDocument44 pagesMelsec Iq-R Profibus-Dp Module Function Block ReferenceNguyễn Minh PhươngNo ratings yet

- Basic Ladder Logic ProgrammingDocument22 pagesBasic Ladder Logic ProgrammingJavier Ruiz Thorrens100% (1)

- OpenScape 4000 Assistant V8 Realtime Diagnosis System Administrator Documentation Issue 2Document128 pagesOpenScape 4000 Assistant V8 Realtime Diagnosis System Administrator Documentation Issue 2slimaneNo ratings yet

- Mari Beauty Full Wife Ka Safar Main Rape HuaDocument7 pagesMari Beauty Full Wife Ka Safar Main Rape HuaKING96100% (2)

- LCMS - Editing Parameters With LcmsRoadInspect PDFDocument4 pagesLCMS - Editing Parameters With LcmsRoadInspect PDFPurshottam SharmaNo ratings yet

- SS-Lab Manual (2018-22) - StudentDocument50 pagesSS-Lab Manual (2018-22) - StudentanandNo ratings yet

- Introduction To The Narragansett LanguageDocument143 pagesIntroduction To The Narragansett LanguageFrank Waabu O'Brien (Dr. Francis J. O'Brien Jr.)100% (7)

- Methods of PhilosophizingDocument13 pagesMethods of PhilosophizingZaldy Belo100% (1)

- Mover Caras Siemens NXDocument8 pagesMover Caras Siemens NXEduardo CanoNo ratings yet

- Technical English: Lecture 1: Using ArticlesDocument16 pagesTechnical English: Lecture 1: Using ArticlesZhiwar oramariNo ratings yet

- Doctype HTMLDocument9 pagesDoctype HTMLBeastboyskilLNo ratings yet

- Nepali English GlossaryDocument53 pagesNepali English GlossarySagar KhadkaNo ratings yet

- Cajero Automático Plástico de Burbujas Caja de Cartón Caja Registradora RelojDocument6 pagesCajero Automático Plástico de Burbujas Caja de Cartón Caja Registradora Relojshabin sNo ratings yet

- Dynamic HTML: Data Binding With Tabular Data Control: OutlineDocument45 pagesDynamic HTML: Data Binding With Tabular Data Control: Outlinerajalaxmi11No ratings yet

- Fractured Fairy Tale WorkbookDocument6 pagesFractured Fairy Tale Workbookapi-569001953No ratings yet

- Reading Practice Reading Passage 1Document27 pagesReading Practice Reading Passage 1LamaNo ratings yet

- 1 Goodness of God - Cece WinansDocument3 pages1 Goodness of God - Cece WinansJulius Kachen100% (1)

- Kami Export - Kami Tool GuideDocument5 pagesKami Export - Kami Tool GuidemorganNo ratings yet

- Cactus Printables (START HERE) PDFDocument408 pagesCactus Printables (START HERE) PDFPractice Makes PerfectNo ratings yet

- Chapter5 - Data Storage FullDocument16 pagesChapter5 - Data Storage FullPhan Minh TríNo ratings yet

- Sree Sai Sahasra Naamavali Telugu &english Meanings (Ist Part 1-500 Names)Document189 pagesSree Sai Sahasra Naamavali Telugu &english Meanings (Ist Part 1-500 Names)tadepalli patanjaliNo ratings yet

- đề 2Document4 pagesđề 2long nguyễnNo ratings yet