Professional Documents

Culture Documents

Name: Digital Logic Circuits (Common To ICE) Part A (20X2 40 Marks) Answer All Questions

Uploaded by

Anonymous yO7rcec6vuOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Name: Digital Logic Circuits (Common To ICE) Part A (20X2 40 Marks) Answer All Questions

Uploaded by

Anonymous yO7rcec6vuCopyright:

Available Formats

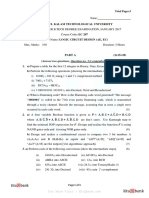

NAME: DIGITAL LOGIC CIRCUITS

(common to ICE)

PART A (20X2 = 40 marks)

ANSWER ALL QUESTIONS

1) Given that (456)r = (237)10. Find r

2) Subtract the unsigned number (10100)2 from (11011)2 using 1’s complement & 2’s

compliment method.

3) Express f(a,b,c)= a+bc’ as sum of minterms

4) Distinguish TTL&CMOS logic family

5) Realize the half adder circuit using decoder?

6) What is a multiplexer?

7) Implement the following Boolean function using three half adder circuits

F1=xyz

F2=x’yz+x y’z

F3=xyz’+(x’+y’)z

F4=xyz

8) What is priority encoder?

9) What is a sequential logic circuit?

10) What is state reduction?

11) How many flipflops are needed to design a mod 60 counter?

12) What are fundamental mode circuits?

13) Compare RAM and ROM

14) Distinguish PAL&PLA

15) What is SRAM & DRAM

16) What is FPGA?

17) What is static and dynamic Hazard?

18) what are advantages of IDDQ testing?

19)Mention the various techniques of design for Testability(DFT)

20)what is ATPG (automatic test pattern generation)

PART B (5X12 = 60 marks)

ANSWER ANY FIVE QUESTIONS

21)a)Reduce the following Boolean expression to indicated number of literals.

i)A’B(D’+C’D)+B(A+A’CD) to one literal (3)

ii)AB’C+B+BD’+ABD’+A’C to two literals (3)

b) Explain the working of a 2 input TTL NAND gate (6)

22)a)Express the following function in sum of minterms &product of maxterms

F(A,B,C,D)=B’D+A’D+BD (6)

b) Explain the working of a 2 input CMOS NAND gate (6)

23) Design and construct excess-3 to BCD code converter (12)

24) Simplify the following using Quine Mccluskey method. (12)

F(w,x,y,z)= m(1,3,4,5,9,10,11)+ d(6,8)

25) a)Describe the working of JK FF with diagram. Give its excitation table (6)

b) A sequential circuit has two JK flip-flops A and B and one input x. The circuit is described by the

following flip-flop input equations:

JA X K A B'

JB X KB A

i)Derive the state equations. (2)

ii) Draw the state diagram of the circuit. (4)

26)An Asynchronous sequential circuit is described by the following excitation &output functions

Y=x1x2’+(x1+x2’)y

Z=y

i)Draw the logic diagram of the circuit (2)

ii)Derive the transition table & output map (4)

iii)Obtain two state flow table (2)

iv)Describe the behavior of circuit (4)

27) Implement the given functions using PLA (12)

A( x, y, z) m(1, 2, 4,6)

B( x, y, z ) m(0,1,6,7)

C ( x, y, z ) m(2,6)

28) a) Find a circuit that has no static hazards Implements the Boolean function

F(A,B,C,D)= m(0,2,6,7,8,10,12) (6)

b) Explain the concept built in self list. Mention its advantages and disadvantages(6)

You might also like

- CSS NC II CORE 1: Install & Configure Computer SystemsDocument54 pagesCSS NC II CORE 1: Install & Configure Computer SystemsEric Manrique Talamisan87% (38)

- Anna University Examination Questions: EE6201-Circuit Theory NOV - 2015Document9 pagesAnna University Examination Questions: EE6201-Circuit Theory NOV - 2015Anonymous yO7rcec6vuNo ratings yet

- Quadrupole Mass Spectrometry and Its ApplicationsFrom EverandQuadrupole Mass Spectrometry and Its ApplicationsPeter H. DawsonNo ratings yet

- Anna University Examination Questions: EE6201-Circuit Theory May - 2014Document8 pagesAnna University Examination Questions: EE6201-Circuit Theory May - 2014Anonymous yO7rcec6vuNo ratings yet

- Anna University Circuit Theory QuestionsDocument7 pagesAnna University Circuit Theory QuestionsAnonymous yO7rcec6vuNo ratings yet

- Asus A6R ManualDocument74 pagesAsus A6R ManualAleksandar KovačNo ratings yet

- Lab 1 Introduction To Stm32F103 and Ide: St-Link V2 and Keil Uvision5Document33 pagesLab 1 Introduction To Stm32F103 and Ide: St-Link V2 and Keil Uvision5Kiều NguyễnNo ratings yet

- Answers to Selected Problems in Multivariable Calculus with Linear Algebra and SeriesFrom EverandAnswers to Selected Problems in Multivariable Calculus with Linear Algebra and SeriesRating: 1.5 out of 5 stars1.5/5 (2)

- Important 16 Mark Questions-19!1!2024Document5 pagesImportant 16 Mark Questions-19!1!2024FLOWERNo ratings yet

- Question Paper Code:: Y Abcababc + + +Document3 pagesQuestion Paper Code:: Y Abcababc + + +karthick VijayanNo ratings yet

- Q 6Document3 pagesQ 6Saranya MohanNo ratings yet

- QBank DPSD cs2202Document6 pagesQBank DPSD cs2202kunarajNo ratings yet

- KEE401 ASSIGNMENTS and QUESTION BANKDocument17 pagesKEE401 ASSIGNMENTS and QUESTION BANKPrince VermaNo ratings yet

- 9A04306 Digital Logic DesignDocument4 pages9A04306 Digital Logic DesignsivabharathamurthyNo ratings yet

- apr - may 2023Document3 pagesapr - may 2023Pandyselvi BalasubramanianNo ratings yet

- (WWW - Entrance-Exam - Net) - JNTU, B.tech, CSE, Digital Logic Design Sample Paper 1 PDFDocument2 pages(WWW - Entrance-Exam - Net) - JNTU, B.tech, CSE, Digital Logic Design Sample Paper 1 PDFpreethaNo ratings yet

- APR2013P21Document63 pagesAPR2013P21qsashutoshNo ratings yet

- Digital Logic DesignDocument4 pagesDigital Logic DesignShareef KhanNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document2 pagesQuestion Paper Code:: (10×2 20 Marks)kenny kannaNo ratings yet

- 08AB303 DIGITAL LOGIC CIRCUITSDocument4 pages08AB303 DIGITAL LOGIC CIRCUITSChandru RamaswamyNo ratings yet

- Ecs-301 Digital Logic Design 2010-11Document4 pagesEcs-301 Digital Logic Design 2010-11Satyedra MauryaNo ratings yet

- 113BU032016Document2 pages113BU032016mushahedNo ratings yet

- 2018 Dec. EC202-D - Ktu QbankDocument4 pages2018 Dec. EC202-D - Ktu QbankSalim ShahulNo ratings yet

- Jntuworld: R05 Set No. 2Document8 pagesJntuworld: R05 Set No. 2vanamgouthamNo ratings yet

- Pyq 2020-2023 Sem2-1Document17 pagesPyq 2020-2023 Sem2-1Aditya RajNo ratings yet

- EC207 Logic Circuit Design Exam QuestionsDocument3 pagesEC207 Logic Circuit Design Exam QuestionsABHILESH G KNo ratings yet

- B.E Degree Examinations: April/May 2016Document3 pagesB.E Degree Examinations: April/May 2016PRAVEEN O.KNo ratings yet

- B.Tech II Year I Semester (R13) Regular & Supplementary Examinations December 2015Document1 pageB.Tech II Year I Semester (R13) Regular & Supplementary Examinations December 2015jayarami reddy pNo ratings yet

- Sir Padampat Singhania University Digital Electronics ExamDocument5 pagesSir Padampat Singhania University Digital Electronics ExamIyyakutti GanapathiNo ratings yet

- Digital Electronics Question BankDocument3 pagesDigital Electronics Question BankNandha Kizor VNo ratings yet

- ECE20022 Assignment Module 1 2 3Document3 pagesECE20022 Assignment Module 1 2 3Nandini PandeyNo ratings yet

- Mtech Ee 2 Sem Digital Control System 2013Document3 pagesMtech Ee 2 Sem Digital Control System 2013AJOY BANIKNo ratings yet

- 9A04306 Digital Logic DesignDocument4 pages9A04306 Digital Logic DesignMahaboob SubahanNo ratings yet

- Ec1312 QBDocument7 pagesEc1312 QBGopinathan MuthusamyNo ratings yet

- March 2007 Paper 2Document2 pagesMarch 2007 Paper 2many1tothe11No ratings yet

- March 2008 Paper 2Document2 pagesMarch 2008 Paper 2many1tothe11No ratings yet

- ECE211 Digital ElectronicsDocument3 pagesECE211 Digital Electronicstejaputta6No ratings yet

- EC 1312 - Digital Logic Circuits Question BankDocument5 pagesEC 1312 - Digital Logic Circuits Question BankDeepak RavichandranNo ratings yet

- Ec 1202 Digital System DesignDocument8 pagesEc 1202 Digital System DesignworkubNo ratings yet

- Digital Fundamentals AssignmentDocument7 pagesDigital Fundamentals AssignmentIshmum Monjur NilockNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document4 pagesQuestion Paper Code:: (10×2 20 Marks)MohamedNo ratings yet

- r05322201 Digital and Optimal Control SystemsDocument8 pagesr05322201 Digital and Optimal Control SystemsSRINIVASA RAO GANTANo ratings yet

- Demp Mid - 1 Question BankDocument3 pagesDemp Mid - 1 Question BankMᴀɴɪ TᴇᴊᴀNo ratings yet

- DE - KOE 039 - Question BankDocument6 pagesDE - KOE 039 - Question Bankyash vatsNo ratings yet

- Question Paper Sep 2009Document3 pagesQuestion Paper Sep 2009Vignesh MuruganNo ratings yet

- Testpaper - 1 NTDocument13 pagesTestpaper - 1 NTGattu SadashivaNo ratings yet

- 07a4ec09 STLDDocument6 pages07a4ec09 STLDSRINIVASA RAO GANTANo ratings yet

- 9A04401 Switching Theory & Logic DesignDocument4 pages9A04401 Switching Theory & Logic DesignsivabharathamurthyNo ratings yet

- EC6302-Digital ElectronicsDocument14 pagesEC6302-Digital Electronicsmagy1989No ratings yet

- 2007 Anna University B.E Electrical and Electronics Digital Systems Question PaperDocument3 pages2007 Anna University B.E Electrical and Electronics Digital Systems Question PapernarencharuNo ratings yet

- 3.MDL 2 DLCDocument3 pages3.MDL 2 DLCVINOD KUMAR.J.R MEC-AP/AERONo ratings yet

- 2EC6302-Digital Electronics QBDocument12 pages2EC6302-Digital Electronics QBSurendar PNo ratings yet

- Code No: R1621042 - B. Tech I Semester Supplementary Exams October/November 2020Document2 pagesCode No: R1621042 - B. Tech I Semester Supplementary Exams October/November 2020VEMANA DHANESHNo ratings yet

- ANALOG AND DIGITAL ICs (WINTER-2018)Document3 pagesANALOG AND DIGITAL ICs (WINTER-2018)Dinesh RathiNo ratings yet

- Digital System Design QuestionsDocument5 pagesDigital System Design Questionsvijay4u4allNo ratings yet

- Digital Electronics and CircuitsDocument12 pagesDigital Electronics and CircuitsGuruKPONo ratings yet

- EE3302-DLC MODEL QP UpdatedDocument3 pagesEE3302-DLC MODEL QP UpdatedKeerthana SahadevanNo ratings yet

- 07a7ec36 Digitalcontrolsystems PDFDocument8 pages07a7ec36 Digitalcontrolsystems PDFetitahNo ratings yet

- Ect203 Logic Circuit Design, December 2021Document2 pagesEct203 Logic Circuit Design, December 2021instapc0210No ratings yet

- GATE - CS - Digital LogicDocument22 pagesGATE - CS - Digital LogicAnonymous 8pCXXsNo ratings yet

- Ect203 Scheme 2020Document8 pagesEct203 Scheme 2020ShakiraNo ratings yet

- St. Thomas College of Engineering & Technology KozhuvalloorDocument3 pagesSt. Thomas College of Engineering & Technology KozhuvalloorsyulmnmdNo ratings yet

- 9a04306-Digital Logic DesignDocument1 page9a04306-Digital Logic DesignSheikh Noor MohammadNo ratings yet

- Switching Theory and Logic Design Exam QuestionsDocument4 pagesSwitching Theory and Logic Design Exam QuestionsrangerNo ratings yet

- Basic Matrix Analysis and Synthesis: With Applications to Electronic EngineeringFrom EverandBasic Matrix Analysis and Synthesis: With Applications to Electronic EngineeringNo ratings yet

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsFrom EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsRating: 5 out of 5 stars5/5 (1)

- 5.ee6201 May 2016Document9 pages5.ee6201 May 2016Anonymous yO7rcec6vuNo ratings yet

- Anna University Circuit Theory QuestionsDocument8 pagesAnna University Circuit Theory QuestionsAnonymous yO7rcec6vuNo ratings yet

- B.E./B.Tech. DEGREE EXAM TRANSDUCER ENGINEERING APR/MAY 2017Document2 pagesB.E./B.Tech. DEGREE EXAM TRANSDUCER ENGINEERING APR/MAY 2017Anonymous yO7rcec6vuNo ratings yet

- 6.TR Nov'2017Document2 pages6.TR Nov'2017Anonymous yO7rcec6vuNo ratings yet

- 1.EI 6401 - April 15 - TR KeyDocument26 pages1.EI 6401 - April 15 - TR KeyAnonymous yO7rcec6vuNo ratings yet

- Ei 6602 PC April 2017Document12 pagesEi 6602 PC April 2017Anonymous yO7rcec6vuNo ratings yet

- Anna University Communication Engineering Questions and AnswersDocument18 pagesAnna University Communication Engineering Questions and AnswersAnonymous yO7rcec6vuNo ratings yet

- 2.EI6602 PC Nov'2016Document23 pages2.EI6602 PC Nov'2016Anonymous yO7rcec6vuNo ratings yet

- DSBSC NotesDocument17 pagesDSBSC NotesAnonymous yO7rcec6vuNo ratings yet

- Transducer Engineering Measurement SystemDocument13 pagesTransducer Engineering Measurement SystemAnonymous yO7rcec6vuNo ratings yet

- 2.EI 6401 - Nov 15 - TR KeyDocument17 pages2.EI 6401 - Nov 15 - TR KeyAnonymous yO7rcec6vuNo ratings yet

- EC8351 Electronics Devices and CircuitsDocument1 pageEC8351 Electronics Devices and CircuitsAnonymous yO7rcec6vuNo ratings yet

- EC COMMUNICATION ENGINEERING EXAM QUESTIONSDocument18 pagesEC COMMUNICATION ENGINEERING EXAM QUESTIONSAnonymous yO7rcec6vuNo ratings yet

- EI 8352 TR - Nov 17Document2 pagesEI 8352 TR - Nov 17Anonymous yO7rcec6vuNo ratings yet

- Mechatronics - Mumbai Univ - Sem 8 ElexDocument10 pagesMechatronics - Mumbai Univ - Sem 8 Elex111ashwinNo ratings yet

- Ei6801 - Computer Control of Process Part-A Answer All Questions (5x2 10)Document7 pagesEi6801 - Computer Control of Process Part-A Answer All Questions (5x2 10)Anonymous yO7rcec6vuNo ratings yet

- 1.EI 6602 PC April 16 - KeyDocument25 pages1.EI 6602 PC April 16 - KeyAnonymous yO7rcec6vuNo ratings yet

- Aptitude QuestionsDocument9 pagesAptitude QuestionsAnonymous yO7rcec6vuNo ratings yet

- Ic6501 Control Systems: UNIT-1 (2 Mark Q/A)Document6 pagesIc6501 Control Systems: UNIT-1 (2 Mark Q/A)Anonymous yO7rcec6vuNo ratings yet

- K L N College of Engineering Pottapalaym: 1 Gshs S 100Document2 pagesK L N College of Engineering Pottapalaym: 1 Gshs S 100Anonymous yO7rcec6vuNo ratings yet

- Aptitude QuestionsDocument9 pagesAptitude QuestionsAnonymous yO7rcec6vuNo ratings yet

- CS ASS2 (13-17batch)Document3 pagesCS ASS2 (13-17batch)Anonymous yO7rcec6vuNo ratings yet

- DTSSP 2mark Q&ADocument31 pagesDTSSP 2mark Q&AAnonymous yO7rcec6vuNo ratings yet

- Process Control Question Paper Code 20480Document2 pagesProcess Control Question Paper Code 20480Anonymous yO7rcec6vuNo ratings yet

- IC6701 May 18 With KeyDocument14 pagesIC6701 May 18 With KeyAnonymous yO7rcec6vuNo ratings yet

- CS ASS2 (13-17batch)Document3 pagesCS ASS2 (13-17batch)Anonymous yO7rcec6vuNo ratings yet

- Dec 3000 m300 ManualDocument312 pagesDec 3000 m300 ManualLuis CribariNo ratings yet

- Nptel: Computer Aided Power System Analysis - Video CourseDocument3 pagesNptel: Computer Aided Power System Analysis - Video Coursejrrb_jaivik100% (1)

- AFC-1000 ManualDocument44 pagesAFC-1000 Manualpaijo klimpritNo ratings yet

- Community cpl27 InstallationDocument2 pagesCommunity cpl27 InstallationNoah WestonNo ratings yet

- Multiplexing Methods ExplainedDocument10 pagesMultiplexing Methods ExplainedCharming buddyNo ratings yet

- MFA350 :: ROAL Living EnergyDocument7 pagesMFA350 :: ROAL Living EnergyMinhNo ratings yet

- Wheel Chair Engineering ProjectDocument26 pagesWheel Chair Engineering ProjectswordprakashNo ratings yet

- K00192 - 20180906092258 - W2b&3-SFE3013-PN JUNCTION-SVDocument42 pagesK00192 - 20180906092258 - W2b&3-SFE3013-PN JUNCTION-SVJohnNo ratings yet

- Overcurrent and Ground Fault Protection Relay ManualDocument19 pagesOvercurrent and Ground Fault Protection Relay ManualdomagojNo ratings yet

- c7200 Ghost c7200 Adventerprisek9 Sna Mz.150 1.m.image 127.0.0.1.ghost LogDocument1 pagec7200 Ghost c7200 Adventerprisek9 Sna Mz.150 1.m.image 127.0.0.1.ghost Logjhari_musicianNo ratings yet

- OPAL-RT (R) Brochure Lab-Volt Fev 21 2014Document8 pagesOPAL-RT (R) Brochure Lab-Volt Fev 21 2014Francisco A Torres VNo ratings yet

- 24VACDocument3 pages24VACPankaj RawatNo ratings yet

- FR - M - Bose - Cinemate Ii BlackDocument124 pagesFR - M - Bose - Cinemate Ii BlackArnaud MuyleNo ratings yet

- MZC 5 ODQ5 X01 HBN VHB F83 NTAz NV9 FTL VF X1 D TRL JFSQDocument2 pagesMZC 5 ODQ5 X01 HBN VHB F83 NTAz NV9 FTL VF X1 D TRL JFSQBrayanEspinozaNo ratings yet

- TSC TDP-225 Desktop Barcode Printer BrochureDocument2 pagesTSC TDP-225 Desktop Barcode Printer BrochureJohnny Barcode100% (1)

- 2013 Arduino PID Lab 0Document7 pages2013 Arduino PID Lab 0Uma MageshwariNo ratings yet

- Transform Analysis of LTI SystemsDocument117 pagesTransform Analysis of LTI SystemsreneeshczNo ratings yet

- Spartan 3 BoardDocument22 pagesSpartan 3 Boardsureshfm1No ratings yet

- Microprocessor and Micro ControllerDocument2 pagesMicroprocessor and Micro Controllersmg26thmayNo ratings yet

- Laboratoryexperiment2 MamaradloDocument11 pagesLaboratoryexperiment2 MamaradloErika Mae MamaradloNo ratings yet

- 739658Document2 pages739658Rodrigo AmorimNo ratings yet

- ARC156 Wiring: Technical InstructionsDocument15 pagesARC156 Wiring: Technical InstructionsshariqisakNo ratings yet

- Simple Water Level IndicatorDocument1 pageSimple Water Level IndicatorhiteshatrescribdNo ratings yet

- Indian Oil Corporation Report on PLC and DCS SystemsDocument19 pagesIndian Oil Corporation Report on PLC and DCS SystemsHimanshu SinghNo ratings yet

- Radix Based Booth MultiplierDocument6 pagesRadix Based Booth MultiplierZulfiqar AliNo ratings yet

- Hardware Billing SystemDocument2 pagesHardware Billing SystemAnsilNo ratings yet