Professional Documents

Culture Documents

Product Functional Specification 8.4 Inch SVGA Color TFT LCD Module Model Name: G084SN03 V.0

Uploaded by

Pedro HenriqueOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Product Functional Specification 8.4 Inch SVGA Color TFT LCD Module Model Name: G084SN03 V.0

Uploaded by

Pedro HenriqueCopyright:

Available Formats

w w w . D a t a S h e e t 4 U .

n e t

Version: 0.3

Total Pages: 23

Date: 2005/8/29

Product Functional Specification

8.4 inch SVGA Color TFT LCD Module

Model Name: G084SN03 V.0

(u) Preliminary Specification

( ) Final Specification

Note: This Specification is subject to change without notice.

(C) Copyright AU Optroncis, Inc.

2005 All Right Reserved. G084SN03 V.0

No Reproduction and Redistribution Allowed. 8/9

www.DataSheet4U.net

I. Contents

1.0 Handling Precautions…………………………………………………..…4

2.0 General Description……………………………………………………….5

2.1 Display Characteristics

2.2 Functional Block Diagram

3.0 Absolute Maximum Ratings……………………………………………...7

4.0 Optical Characteristics……………………………………………………8

5.0 Signal Interface……………………………………………………………10

5.1 Connectors

5.2 Signal Pin

5.3 Signal Description

5.4 Signal Electrical Characteristics

5.5 Signal for Lamp Connector

6.0 Pixel Format Image………………………………………………………14

7.0 Parameter Guide Line CFL Inverter…………………………………...15

8.0 Interface Timing..…………………………………………………………16

8.1 Timing Characteristics

8.2 Timing Definition

8.3 Timing Chart

9.0 Power Consumption……………………………………………………..19

10.0 Power ON/OFF Sequence……………………………………………….20

11.0 Reliability Test Items…………………………………………………..…21

12.0 Packing Dimension…………………………………………………….…22

13.0 Mechanical Characteristic..……………………………………………..23

(C) Copyright AU Optroncis, Inc.

2005 All Right Reserved. G084SN03 V.0

No Reproduction and Redistribution Allowed. 8/9

www.DataSheet4U.net

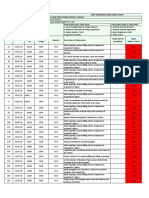

II. Record of Revision

Version and Date Page Old Description New Description Remark

0.1 2005/05/20 All N/A First draft

0.2 2005/08/09 5 N/A Add a discription of RoHs

0.3 2005/08/29 8 View angle 60/60/60/40 View angle 65/65/65/45

(C) Copyright AU Optroncis, Inc.

2005 All Right Reserved. G084SN03 V.0

No Reproduction and Redistribution Allowed. 8/9

www.DataSheet4U.net

1.0 Handing Precautions

1) Since front polarizer is easily damaged, pay attention not to scratch it.

2) Be sure to turn off power supply when inserting or disconnection from input

connector.

3) Wipe off water drop immediately. Long contact with water may cause discoloration

or spots.

4) When the panel surface is soiled, wipe it with absorbent cotton or other soft cloth.

5) Since the panel is made of glass, it may break or crack if dropped or bumped on

hard surface.

6) Since CMOS LSI is used in this module, take care of static electricity and insure

human earth when handling.

7) Do not open nor modify the module Assembly.

8) Do not press the reflector sheet at the back of the module to any directions.

9) In case if a module has to be put back into the packing container slot after once it

was taken out from the container, do not press the center of the CCFL Reflector

edge. Instead, press at the far ends of the CFL Reflector edge softly. Otherwise

the TFT module may be damaged.

10) At the insertion or removal of the Signal Interface Connector, be sure not to rotate

nor tilt the interface Connector of the TFT module.

11) After installation of the TFT module into an enclosure, do not twist nor bend the

TFT module even momentary. At designing the enclosure, it should be taken into

consideration that no bending/twisting forces are applied to the TFT module from

outside. Otherwise the TFT module may be damaged.

12) Cold cathode fluorescent lamp in LCD contains a small amount of mercury. Please

follow local ordinances or regulations for disposal.

13) Small amount of materials having no flammability grade is used in the LCD

module should be supplied by power complied with requirements of Limited Power

Source, or be applied exemption.

14) The LCD module is designed so that the CFL in it is supplied by Limited Current

Circuit. Do not connect the CFL in Hazardous Voltage Circuit.

(C) Copyright AU Optroncis, Inc.

2005 All Right Reserved. G084SN03 V.0

No Reproduction and Redistribution Allowed. 8/9

www.DataSheet4U.net

2.0 General Description

This specification applies to the 8.4 inch color TFT LCD module B084SN03 V.0.

This module is designed for General Display.

The screen format is intended to support the SVGA (800(H) x 600(V)) screen and

262k colors (RGB 6-bits data driver).

All input signals are LVDS interface compatible.

The module does not contain an inverter card for backlight.

This is an RoHs product.

2.1 Display Characteristics

The following items are characteristics summary on the table under 25℃ condition:

Items Unit Specifications

Screen Diagonal [mm] 213.4 ( 8.4 ”)

Active Area [mm] 170.4(H) x 127.8(V)

Pixel H x V 800(x3) x 600

Pixel Pitch [mm] 0.213(H) x 0.213(V)

Pixel Arrangement R.G.B. Vertical Stripe

Display Mode Normally White

2

Typical White Luminance (ICFL=4.6 mA) [cd/m ] 220 Typ. (center)

Contrast Ratio 500:1 Typ.

Optical Rise Time/Fall Time [msec] 10/25 Typ.

Nominal Input Voltage VDD [Volt] +3.3 Typ.

Typical Power Consumption [Watt] 3.3 Typ

(VDD line + VCFL line)

Weight [Grams] 215 ±10

Physical Size [mm] 203.0(W) x 142.5(H) x 5.7(D)

Electrical Interface 1 channel LVDS

Support Color Native 262K colors (RGB 6-bit driver)

Temperature Range

Operating [℃] 0 to +50

Storage(Shipping) [℃] -20 to +60

(C) Copyright AU Optroncis, Inc.

2005 All Right Reserved. G084SN03 V.0

No Reproduction and Redistribution Allowed. 8/9

www.DataSheet4U.net

2.2 Functional Block Diagram

The following diagram shows the functional block of the 8.4 inches Color TFT LCD

Module:

(C) Copyright AU Optroncis, Inc.

2005 All Right Reserved. G084SN03 V.0

No Reproduction and Redistribution Allowed. 8/9

www.DataSheet4U.net

3.0 Absolute Maximum Ratings

Absolute maximum ratings of the module is as follows:

Item Symbol Min Max Unit Conditions

Logic/LCD Drive Voltage VDD -0.3 +4.0 [Volt]

Input Voltage of Signal Vin -0.3 VDD+0.3 [Volt]

CCFL Current ICFL 3 6 [mA] rms

CCFL lgnition Voltage Vs 441 539 Vrms

Operating Temperature TOP 0 +50 [℃] Note1

Operating Humidity HOP 8 90 [%RH] Note1

Storage Temperature TST -20 +60 [℃] Note1

Storage Humidity HST 5 90 [%RH] Note1

Vibration 1.0, 10-500 [G, Hz] 2hr/axis X,Y,Z

Shock 220, 2 [G, ms] Half sine wave

Note1:Maximum Wet-Bulb should be 39 ℃ and no condensation.

(C) Copyright AU Optroncis, Inc.

2005 All Right Reserved. G084SN03 V.0

No Reproduction and Redistribution Allowed. 8/9

www.DataSheet4U.net

4.0 Optical Characteristics

The optical characteristics are measured under stable conditions as follows under

25℃ condition:

Item Unit Conditions Min. Typ. Max.

Viewing Angle [degree] Horizontal (Right) - 65 -

[degree] K = 10 (Left) 65

K:Contrast ratio [degree] Vertical (Upper) - 65 -

[degree] K = 10 (Lower) 45

White Uniformity 9 Points - - 1.6

Contrast ratio θ= 0° 300 500 -

Response Time [msec] Rising - 10 20

(Room Temp) [msec] Falling - 25 30

Color Red x 0.540 0.570 0.600

Chromaticity Red y 0.290 0.320 0.350

Coordinates(CIE) Green x 0.290 0.320 0.350

Green y 0.530 0.560 0.590

Blue x 0.120 0.150 0.180

Blue y 0.090 0.120 0.150

White x 0.280 0.310 0.340

White y 0.300 0.330 0.360

2

White Luminance [cd/m ] θ= 0° 200 220 -

(ICFL 4.6 mA) (Center) (Center)

(C) Copyright AU Optroncis, Inc.

2005 All Right Reserved. G084SN03 V.0

No Reproduction and Redistribution Allowed. 8/9

www.DataSheet4U.net

Note 1: Definition of white uniformity:

White uniformity is calculated with the following formula.

Luminance are measured at the following nine points (1~9).

Maximum Brightness of nine points

δW

Minimum Brightness of nine points

(C) Copyright AU Optroncis, Inc.

2005 All Right Reserved. G084SN03 V.0

No Reproduction and Redistribution Allowed. 8/9

www.DataSheet4U.net

5.0 Signal Interface

5.1 Connectors

Physical interface is described as for the connector on module.

These connectors are capable of accommodating the following signals and will be

following components.

Connector Name / Designation For Signal Connector

Manufacturer HIROSE

Type / Part Number HRS DF 19K-20P-1H

Mating Connector / Part Number HRS DF19G-20S-1C (WIRE TYPE))

Mating Connector / Part Number HRS DF19-20S-1F (FPC TYPE)

Connector Name / Designation For Lamp Connector

Manufacturer JST

Type / Part Number BHSR-02VS-1

Mating Connector / Part Number SM02B-BHSS-1-TB

5.2 Signal Pin

Pin No. Signal Name Pin No. Signal Name

1 VDD 2 VDD

3 GND 4 GND

5 RxIN0- 6 RxIN0+

7 GND 8 RxIN1-

9 RxIN1+ 10 GND

11 RxIN2- 12 RxIN2+

13 GND 14 CKIN-

15 CKIN+ 16 GND

17 NC 18 NC

19 GND 20 GND

(C) Copyright AU Optroncis, Inc.

2005 All Right Reserved. G084SN03 V.0

No Reproduction and Redistribution Allowed. 8/9

www.DataSheet4U.net

5.3 Signal Description

The module using a LVDS receiver. LVDS is a differential signal technology for LCD

interface and high speed data transfer device. Transmitter shall be SN75LVDS84

(negative edge sampling) or compatible.

Note:Input signals shall be low or Hi-Z state when VDD is off.

Signal Name Description

RxIN0-, RxIN0+ LVDS differential data input (Red0-Red5, Green0)

RxIN1-, RxIN1+ LVDS differential data input (Green1-Green5, Blue0-Blue1)

RxIN2-, RxIN2+ LVDS differential data input (Blue2-Blue5, Hsync, Vsync, DE)

CKIN-, CKIN+ LVDS differential clock input

VDD +3.3V Power Supply

GND Ground

NC No Connection

(C) Copyright AU Optroncis, Inc.

2005 All Right Reserved. G084SN03 V.0

No Reproduction and Redistribution Allowed. 8/9

www.DataSheet4U.net

Signal Name Description

+RED5 Red Data 5 (MSB) Red-pixel Data

+RED4 Red Data 4 Each red pixel’s brightness data consists of these

+RED3 Red Data 3 6 bits pixel data.

+RED2 Red Data 2

+RED1 Red Data 1

+RED0 Red Data 0 (LSB)

Red-pixel Data

+GREEN5 Green Data 5 (MSB) Green-pixel Data

+GREEN4 Green Data 4 Each green pixel’s brightness data consists of these

+GREEN3 Green Data 3 6 bits pixel data.

+GREEN2 Green Data 2

+GREEN1 Green Data 1

+GREEN0 Green Data 0 (LSB)

Green-pixel Data

+BLUE5 Blue Data 5 (MSB) Blue-pixel Data

+BLUE4 Blue Data 4 Each blue pixel’s brightness data consists of these

+BLUE3 Blue Data 3 6 bits pixel data.

+BLUE2 Blue Data 2

+BLUE1 Blue Data 1

+BLUE0 Blue Data 0 (LSB)

Blue-pixel Data

CLK Data Clock The typical frequency is 40MHz. The signal is

used to strobe the pixel data and DE signals.

All pixel data shall be valid at the falling edge when

the DE signal is high.

DE Display Timing This signal is strobed at the falling edge of CLK.

When the signal is high, the pixel data shall be valid

to be displayed.

VSYNC Vertical Sync The signal is synchronized to CLK.

HSYNC Horizontal Sync The signal is synchronized to CLK.

Note:Output signals from any system shall be low or Hi-Z state when VDD is off.

(C) Copyright AU Optroncis, Inc.

2005 All Right Reserved. G084SN03 V.0

No Reproduction and Redistribution Allowed. 8/9

www.DataSheet4U.net

5.4 Signal Electrical Characteristics

Input signals shall be low or Hi-Z state when VDD is off.

It is recommended to refer the specifications of SN75LVDS86(Texas Instruments) in

detail.

Signal electrical characteristics are as follows:

Item Symbol Min. Typ. Max. Unit

The differential level |VID| 0.1 - 0.6 V

The common mode input ︱VID︱ ︱VID︱

VIC - 2.4- V

voltage 2 2

The input setup time tsu 0.5 - - ns

The input hold time thd 0.5 - - ns

High-level input voltage V IAP 2.0 V

Low-level input voltage V IAM 0.8 V

Clock frequency CLK 31 68 MHz

(C) Copyright AU Optroncis, Inc.

2005 All Right Reserved. G084SN03 V.0

No Reproduction and Redistribution Allowed. 8/9

www.DataSheet4U.net

5.5 Signal for Lamp connector

Pin no. Symbol Function Remark

1 H CCFL power supply(H.V.) Cable color: Pink

2 L CCFL power supply(GND) Cable color: White

6.0 Pixel Format Image

Following figure shows the relationship of the input signals and LCD pixel format:

1 2 799 800

1st Line R G B R G B R G B R G B

600th Line R G B R G B R G B R G B

(C) Copyright AU Optroncis, Inc.

2005 All Right Reserved. G084SN03 V.0

No Reproduction and Redistribution Allowed. 8/9

www.DataSheet4U.net

7.0 Parameter guide line for CFL inverter

Parameter Min Typ Max Units Condition

2

White Luminance 200 220 - Cd/m

CCFL current (ICFL) 3.0 4.6 - mArms Note1

CCFL Frequency (FCFL) 50 60 80 KHz Note4

CCFL Ignition Voltage (Vs) - - 1070(T=0℃) Vrms Note3

820(T=25℃)

CCFL Voltage (Reference) 441 490 539 Vrms Note1

(VCFL)

CCFL Power consumption - 2.3 - W Note2

(PCFL)

Lamp Life Time 10,000 20,000 - Hr Note1, 5

Note1:T=25℃

Note2:Inverter should be designed with the characteristic of lamp. When you are designing

the inverter, the output voltage of the inverter should comply with the following conditions.

(1). The area under the positive and negative cycles of the waveform of the lamp current and

lamp voltage should be area symmetric (the symmetric ratio should be larger than 90%).

(2). There should not be any spikes in the waveform.

(3). The waveform should be sine wave as possible.

(4). Lamp current should not exceed the maximum value within the operating temperature (It is

prohibited to over the maximum lamp current even if operated in the non-guaranteed

temperature). When lamp current is over the maximum value for a long time, it may cause fire.

Therefore, it is recommend that the inverter should have the current limit circuit.

Note3:The inverter open voltage should be designed larger than the lamp starting voltage at

o

T=0 C, otherwise backlight may be blinking for a moment after turning on or not be able to turn

on. The open voltage should be measured after ballast capacitor. If an inverter has shutdown

function it should keep its open voltage for longer than 1 second even if lamp connector is

open.

Note4:Lamp frequency may produce interference with horizontal synchronous frequency and

this may cause line flow on the display. Therefore lamp frequency shall be detached from the

horizontal synchronous frequency and its harmonics as far as possible in order to avoid

interference.

Note5:Brightness (ICFL=4.6mA) to be decreased to the 50% of the initial value.

(C) Copyright AU Optroncis, Inc.

2005 All Right Reserved. G084SN03 V.0

No Reproduction and Redistribution Allowed. 8/9

www.DataSheet4U.net

8.0 Interface Timings

Basically, interface timing should match the VESA 800x600 /60Hz(VG901101)

manufacturing guide line timing.

8.1 Timing Characteristics

(a) DE mode

Item Symbol Min. Typ. Max. Unit Remark

Clock frequency Fck 38 40 48 MHz

Horizontal blanking Thb1 50 256 500 Clk

Vertical blanking Tvb1 10 28 150 Th

(b) HV mode

Item Symbol Min. Typ. Max. Unit Remark

Clock frequency Fck 38 40 48 MHz

Hsync period Th 850 1056 1300 Clk

Hsync pulse width Thw 10 128 - Clk

Hsync front porch Thf 15 40 - Clk

Hsync back porch Thb 10 88 - Clk

Hsync blanking Thb1 50 256 500 Clk

Vsync period Tv 610 628 750 Th

Vsync pulse width Tvw 1 4 - Th

Vsync front porch Tvf 0 1 - Th

Vsync blanking Tvb1 10 28 150 Th

Hsync/Vsync phase shift Tvpd 2 320 - Clk

Item Symbol Value Unit Description

Horizontal display start The 218 Clk After falling edge of Hsync, counting 218clk,

then getting valid data from 219th clk ’s data.

Vertical display start Tve 25 Th After falling edge of Vsync, counting 25th,

then getting 26th Th’s data.

(C) Copyright AU Optroncis, Inc.

2005 All Right Reserved. G084SN03 V.0

No Reproduction and Redistribution Allowed. 8/9

www.DataSheet4U.net

8.2 Timing Definition

1056 dot

H-Sync

40 dot 88 dot

128 dot

DE

800 dot

628H

V-Sync

1H 23H

4H

DE

28H 600H

(C) Copyright AU Optroncis, Inc.

2005 All Right Reserved. G084SN03 V.0

No Reproduction and Redistribution Allowed. 8/9

www.DataSheet4U.net

8.3 Timing Chart

(1 pixel / clock)

invalid

Invalid

799,Y 800,Y

X,599 X,600

Tvd

Thd

X,3

X,2

X,1

3,Y

Th

Tv

2,Y

1,Y

Tvbl

Invalid

Thbl

invalid

Fck

X,599 X,600

800,Y

RGB

RGB

CLK

DE

DE

(C) Copyright AU Optroncis, Inc.

2005 All Right Reserved. G084SN03 V.0

No Reproduction and Redistribution Allowed. 8/9

www.DataSheet4U.net

9.0 Power Consumption

Input power specifications are as follows:

Symbol Parameter Min Typ Max Units Condition

VDD Logic/LCD Drive 3.0 3.3 3.6 V

Voltage

PDD VDD Power - 0.76 - W

PDD Max VDD Power max - 0.86 - W

IDD IDD Current - 230 - mArms Note 1

IDD Max IDD Current max - 260 310 mArms Note 2

VRP Power Ripple Voltage - 100 - mVp-p

I RUSH Inrush Current - 1500 - mApeak

Note 1: Effective value (mArms) at VCC = 3.3 V/25℃.

Note 2:

(C) Copyright AU Optroncis, Inc.

2005 All Right Reserved. G084SN03 V.0

No Reproduction and Redistribution Allowed. 8/9

www.DataSheet4U.net

10.0 Power ON/OFF Sequence

VDD power and lamp on/off sequence is as follows. Interface signals are also shown

in the chart. Signals from any system shall be Hi-Z state or low level when VDD is off.

(C) Copyright AU Optroncis, Inc.

2005 All Right Reserved. G084SN03 V.0

No Reproduction and Redistribution Allowed. 8/9

w w w . D a t a S h e e t 4 U . n e t

11.0 Reliability Test Items

Test item Test Condition Remark

High temperature storage 60℃, 300Hrs Note 1, 2, 3

Low temperature storage -20℃,300Hrs Note 1, 2, 3

High temperature & high 40℃, 90%RH, 300Hrs

Note 1, 2, 3

humidity operation (No condensation)

High temperature operation 50℃, 300Hrs Note 1, 2, 3

Low temperature operation 0℃, 300Hrs Note 1, 2, 3

Temperature cycling -20℃~60℃

Note 1, 2, 3

(non-operation) 1H, 10mins, 1H, 5cycles

Electrostatic discharge 150 pF,150Ω,10kV,1 second, 9 position

Note 3

(non-operation) on the panel, 10 times each place

Vibration Sweep:1G, 10H Z ~ 500H Z ~ 10H Z /2.5min

Note 1, 2, 3

(non-operation) 2 hours for each direction X, Y, Z

Mechanical shock 50G/11ms, 220G/2ms, ±X, ±Y, ±Z

Note 1, 2, 3

(non-operation) once for each direction

Note 1: Evaluation should be tested after storage at room temperature for one hour.

Note 2: There should be no change which might affect the practical display function

when the display quality test is conducted under normal operating condition.

Note 3: Judgement: 1.Function OK.

2.No serious image quality degradation.

Display quality

The display quality of the color TFT-LCD module should be in compliance with the

AUO’s OQC inspection standard.

Handling precaution

The Handling of the TFT-LCD should be in compliance with the AUO’s handling

principle standard.

(C) Copyright AU Optroncis, Inc.

2005 All Right Reserved. G084SN03 V.0

No Reproduction and Redistribution Allowed. 8/9

w w w . D a t a S h e e t 4 U . n e t

12.0 Packing Dimension:

LCD M odule

Anti-Static

Bag

NOTE :

1. Max. Capacity : 30 LCD Modules/Carton.

EPP Cushion

2. Max. W eight : 12 Kg/Carton.

3. Meas : 600 m m *353mm *210mm .

Carton

(C) Copyright AU Optroncis, Inc.

2005 All Right Reserved. G084SN03 V.0

No Reproduction and Redistribution Allowed. 8/9

www.DataSheet4U.net

12.1 Label:

(C) Copyright AU Optroncis, Inc.

2005 All Right Reserved. G084SN03 V.0

No Reproduction and Redistribution Allowed. 8/9

www.DataSheet4U.net

13.0 Mechanical Characteristic

LCM Outline Dimension

(C) Copyright AU Optroncis, Inc.

2005 All Right Reserved. G084SN03 V.0

No Reproduction and Redistribution Allowed. 8/9

You might also like

- Microprocessors & their Operating Systems: A Comprehensive Guide to 8, 16 & 32 Bit Hardware, Assembly Language & Computer ArchitectureFrom EverandMicroprocessors & their Operating Systems: A Comprehensive Guide to 8, 16 & 32 Bit Hardware, Assembly Language & Computer ArchitectureRating: 1 out of 5 stars1/5 (1)

- G104SN02 V1Document27 pagesG104SN02 V1Waheed AhmedNo ratings yet

- The Engineering of Microprocessor Systems: Guidelines on System DevelopmentFrom EverandThe Engineering of Microprocessor Systems: Guidelines on System DevelopmentNo ratings yet

- B133ew03 V.3Document32 pagesB133ew03 V.3MauricioNo ratings yet

- Engineering the CMOS Library: Enhancing Digital Design Kits for Competitive SiliconFrom EverandEngineering the CMOS Library: Enhancing Digital Design Kits for Competitive SiliconRating: 1 out of 5 stars1/5 (1)

- Product Specification: (V) Preliminary Specification Final SpecificationDocument28 pagesProduct Specification: (V) Preliminary Specification Final SpecificationJorge TabaresNo ratings yet

- Specification for 14-inch HD LCD with LED BacklightDocument34 pagesSpecification for 14-inch HD LCD with LED BacklightweyoNo ratings yet

- Au Optronics B154EW02 V7Document35 pagesAu Optronics B154EW02 V7HansDampf2No ratings yet

- Vestel - Chassis - 17mb11 2 SERV BOLDocument71 pagesVestel - Chassis - 17mb11 2 SERV BOLsinfo338No ratings yet

- Product Specification for 15.6Document35 pagesProduct Specification for 15.6BobNo ratings yet

- B141ew04 V.5Document35 pagesB141ew04 V.5Cristiano Gonçalves de Sant'AnnaNo ratings yet

- 18.5Document30 pages18.5nick dazzleNo ratings yet

- B154ew01 V4 AuoDocument37 pagesB154ew01 V4 AuoFranklin JimenezNo ratings yet

- LCD Panel Specification and DatasheetDocument29 pagesLCD Panel Specification and DatasheetCesar Barboza RNo ratings yet

- B156XW04 V.8Document35 pagesB156XW04 V.8Juan Carlos SrafanNo ratings yet

- B156RW01 V.1Document34 pagesB156RW01 V.1максим герцовNo ratings yet

- B141ew04 - V4 (1) AuoDocument35 pagesB141ew04 - V4 (1) AuoHenryCalvaNo ratings yet

- M190en04 V5 Auo PDFDocument29 pagesM190en04 V5 Auo PDFImam MeliawanNo ratings yet

- Datasheet MosfetDocument30 pagesDatasheet Mosfetwalter andiasNo ratings yet

- Product Specification: (V) Preliminary Specifications Final SpecificationsDocument35 pagesProduct Specification: (V) Preliminary Specifications Final SpecificationsPablo JavierNo ratings yet

- Product Specification: Customer Date Approved by DateDocument35 pagesProduct Specification: Customer Date Approved by DateVi Tính Hoàng LânNo ratings yet

- B141XG09 V.3Document25 pagesB141XG09 V.3aaa bbbNo ratings yet

- B156HTN03 3-AuoDocument32 pagesB156HTN03 3-AuoRayan ElectroNo ratings yet

- Display 30 Pinos B140XTN02.4-AUODocument33 pagesDisplay 30 Pinos B140XTN02.4-AUOBobNo ratings yet

- Product Functional Specification 15 Inch XGA Color TFT LCD Module Model Name: B150XG01 V.2Document20 pagesProduct Functional Specification 15 Inch XGA Color TFT LCD Module Model Name: B150XG01 V.2gns_vcNo ratings yet

- Product Specification: Preliminary Specifications (V) Final SpecificationsDocument28 pagesProduct Specification: Preliminary Specifications (V) Final SpecificationsCesar Barboza RNo ratings yet

- Au Optronics Corporation: Product SpecificationDocument36 pagesAu Optronics Corporation: Product Specificationсергей гомзяковNo ratings yet

- B140XW01 V.0Document37 pagesB140XW01 V.0OnionNo ratings yet

- B154ew08 V1Document36 pagesB154ew08 V1Alfa alfaNo ratings yet

- B173RW01 V0 AuoDocument37 pagesB173RW01 V0 AuoclusterkukusanNo ratings yet

- B140XTT01 1-AuoDocument33 pagesB140XTT01 1-AuoRafaew OliveiraNo ratings yet

- B156HTN03 4-AuoDocument30 pagesB156HTN03 4-AuomanojNo ratings yet

- PRODUCT SPEC TITLEDocument32 pagesPRODUCT SPEC TITLExvolcanoNo ratings yet

- B141ew04 V4Document36 pagesB141ew04 V4Anthony Sotto IgnacioNo ratings yet

- B140HTN01 3-AuoDocument33 pagesB140HTN01 3-AuoTong LiuNo ratings yet

- Dell Inspiron 6400 LCD Panel - AUOptonics B154EW02-V6 DatasheetDocument36 pagesDell Inspiron 6400 LCD Panel - AUOptonics B154EW02-V6 DatasheetbackvlackoNo ratings yet

- LCD Notebook B141ew04 v4Document35 pagesLCD Notebook B141ew04 v4r2507308No ratings yet

- B156XW01 V0Document33 pagesB156XW01 V0Павел Пашко-ПащенкоNo ratings yet

- 12.1" WXGA LCD SpecsDocument35 pages12.1" WXGA LCD SpecsPablo Fernando Amaya MeloNo ratings yet

- SLCD .TW: Product SpecificationDocument31 pagesSLCD .TW: Product SpecificationjorellNo ratings yet

- B156XW02 V.2 PDFDocument31 pagesB156XW02 V.2 PDFMihael PolakNo ratings yet

- LCD Module Spec SheetDocument35 pagesLCD Module Spec SheetxvolcanoNo ratings yet

- Product Specification: Customer Date Approved by DateDocument37 pagesProduct Specification: Customer Date Approved by DateiamjameshNo ratings yet

- Product Specification: Preliminary Specifications (V) Final SpecificationsDocument32 pagesProduct Specification: Preliminary Specifications (V) Final SpecificationsCesar Barboza RNo ratings yet

- Product Specification: Preliminary Specification (V) Final SpecificationDocument28 pagesProduct Specification: Preliminary Specification (V) Final SpecificationNicolas Gandolfo100% (1)

- Panel - AOU B140XTN02.0 (HW0A) - DatasheetDocument29 pagesPanel - AOU B140XTN02.0 (HW0A) - Datasheetjob vacancyNo ratings yet

- B141ew05-V0 AuoDocument36 pagesB141ew05-V0 AuoTEGUH RIYANTONo ratings yet

- AOU B121EW09 V3 Version 1.2Document35 pagesAOU B121EW09 V3 Version 1.2divubi2004No ratings yet

- LVDS To Vga ConverterDocument26 pagesLVDS To Vga ConverterMark MorleyNo ratings yet

- B173HW02 V1 AuoDocument32 pagesB173HW02 V1 AuoMVDNo ratings yet

- Document PDFDocument34 pagesDocument PDFXavier MorenoNo ratings yet

- Product Specification: (V) Preliminary Specification Final SpecificationDocument30 pagesProduct Specification: (V) Preliminary Specification Final SpecificationBhadreshkumar SharmaNo ratings yet

- AU Optronics 14-Inch HD LCD Module SpecificationDocument29 pagesAU Optronics 14-Inch HD LCD Module SpecificationweyoNo ratings yet

- B170PW06 V.2Document33 pagesB170PW06 V.2barlow00No ratings yet

- Panel LCD m185xw01 - v8Document27 pagesPanel LCD m185xw01 - v8Antonio ChavezNo ratings yet

- Auo B140XW01 V.8Document30 pagesAuo B140XW01 V.8shareatorNo ratings yet

- B140XW03 V1 AuoDocument29 pagesB140XW03 V1 Auomladenovic.miroslav8No ratings yet

- Product Specification: Customer Date Approved by DateDocument31 pagesProduct Specification: Customer Date Approved by DateDmitry Eremin-SolenikovNo ratings yet

- B140XW01-V8 AuoDocument30 pagesB140XW01-V8 AuoCarl Luigi Carbona BalahanNo ratings yet

- B140XW01 V.8Document30 pagesB140XW01 V.8antoniormsilNo ratings yet

- Guia - Phase 3 VLM - InglDocument2 pagesGuia - Phase 3 VLM - InglPedro HenriqueNo ratings yet

- Cat Incu - IngDocument2 pagesCat Incu - IngPedro HenriqueNo ratings yet

- Man Sensitest - IngDocument36 pagesMan Sensitest - IngPedro HenriqueNo ratings yet

- ( (V) Final Specifications: 8.4 Inch Color TFT-LCD G084SN03 V1Document26 pages( (V) Final Specifications: 8.4 Inch Color TFT-LCD G084SN03 V1Pedro HenriqueNo ratings yet

- High Voltage Phase Control ThyristorDocument3 pagesHigh Voltage Phase Control ThyristorPedro HenriqueNo ratings yet

- TIB-2019-002 - Evolution® 3e T & 3e HP Software Versions 6.4.01 ReleaseDocument2 pagesTIB-2019-002 - Evolution® 3e T & 3e HP Software Versions 6.4.01 ReleasePedro HenriqueNo ratings yet

- Incident Report: CardiaidDocument11 pagesIncident Report: CardiaidPedro HenriqueNo ratings yet

- High Voltage IGBTDocument5 pagesHigh Voltage IGBTPedro HenriqueNo ratings yet

- AVEA™ Ventilator Software 4.6B: Technical SupportDocument1 pageAVEA™ Ventilator Software 4.6B: Technical SupportPedro HenriqueNo ratings yet

- PL2303G DriverInstallerv1.4.0 ReleaseNoteDocument3 pagesPL2303G DriverInstallerv1.4.0 ReleaseNoteYesith Berbel RicardoNo ratings yet

- PL2303CheckChipVersion ReadMeDocument1 pagePL2303CheckChipVersion ReadMeShafeek MakNo ratings yet

- AVEA™ Ventilator Software 4.6B: Technical SupportDocument1 pageAVEA™ Ventilator Software 4.6B: Technical SupportPedro HenriqueNo ratings yet

- PL2303CheckChipVersion ReadMeDocument1 pagePL2303CheckChipVersion ReadMeShafeek MakNo ratings yet

- TL866II InstructionsDocument54 pagesTL866II InstructionsWojciech BłądekNo ratings yet

- PL2303 Windows Driver User Manual v1.19.0 PDFDocument14 pagesPL2303 Windows Driver User Manual v1.19.0 PDFjairo becerra perezNo ratings yet

- The Manual of Free Energy Devices and SystemsDocument128 pagesThe Manual of Free Energy Devices and SystemsD'MarinhoNo ratings yet

- DC Machine L05Document16 pagesDC Machine L05luckyNo ratings yet

- Workshop Manual: Training CenterDocument9 pagesWorkshop Manual: Training CenterStas100% (1)

- HW2 SolutionDocument7 pagesHW2 SolutionAnson ChanNo ratings yet

- Capacitors and TypesDocument11 pagesCapacitors and TypesHa FaiazNo ratings yet

- Surface Drills: Commando DC130Ri T3Document3 pagesSurface Drills: Commando DC130Ri T3Mario EspinosaNo ratings yet

- Air Cooled Condenser (Acc) and Air Evacuation SystemDocument4 pagesAir Cooled Condenser (Acc) and Air Evacuation SystemCo-gen ManagerNo ratings yet

- Conectores Rele Arranque Aveo 2005Document3 pagesConectores Rele Arranque Aveo 2005Jose Luis Velasquez RomeroNo ratings yet

- OMM-XF-12T-IC Forklift-202012-EN-CEDocument106 pagesOMM-XF-12T-IC Forklift-202012-EN-CEmirko coppiniNo ratings yet

- Joint Inspection Punchpoints - 24 WTGDocument2 pagesJoint Inspection Punchpoints - 24 WTGajay varmaNo ratings yet

- User'S Manual: QD200 Series Frequency InverterDocument140 pagesUser'S Manual: QD200 Series Frequency Inverterleandro zauraNo ratings yet

- Can Bamboo Replace Steel As ReinforcemenDocument6 pagesCan Bamboo Replace Steel As ReinforcemenTesfayeNo ratings yet

- Digital Resistance Meter - Innova I63CDocument1 pageDigital Resistance Meter - Innova I63CSourabh ChoudharyNo ratings yet

- Product Details: Product Details Documents Visuals Accessories Spare Parts ReplacemDocument5 pagesProduct Details: Product Details Documents Visuals Accessories Spare Parts ReplacemPAul JoHn MeNdozaNo ratings yet

- CAT NR3000 Service ManualDocument273 pagesCAT NR3000 Service ManualKelli BrownNo ratings yet

- Read The Text and Answers The Questions Below! Biodiesel Please Look at The Picture and Explain With Your Own Words! How Is Glass RecycledDocument1 pageRead The Text and Answers The Questions Below! Biodiesel Please Look at The Picture and Explain With Your Own Words! How Is Glass RecycledRizkhi Ramadhani100% (1)

- Dvs 2207Document145 pagesDvs 2207Eduardo Rojas Araya100% (1)

- AUTODESK 500L SW Desalination Power SystemDocument1 pageAUTODESK 500L SW Desalination Power SystemMary CindyNo ratings yet

- Q400 - 12. PropellersDocument14 pagesQ400 - 12. PropellersDavid Owen100% (1)

- Year 10 Physics - MotionDocument18 pagesYear 10 Physics - MotionKevin XiaoNo ratings yet

- Lista Requisiciones Pendientes Por EquipoDocument194 pagesLista Requisiciones Pendientes Por Equipojuan carvajalNo ratings yet

- Modular FURNACE INSULATION THKNESS CALDocument2 pagesModular FURNACE INSULATION THKNESS CALRamachandra Bhat HireNo ratings yet

- Balneological Use of Thermal WatersDocument10 pagesBalneological Use of Thermal WatersMary Carmen CarrascoNo ratings yet

- PC350LC-8 (Kepb075306)Document590 pagesPC350LC-8 (Kepb075306)Augusto100% (1)

- Template ASMEDocument4 pagesTemplate ASMEELIUD SILVANo ratings yet

- Catalog D-1 Reg Sol and 3-Way Heat Reclaim ValvesDocument60 pagesCatalog D-1 Reg Sol and 3-Way Heat Reclaim ValvesviniciusschwabNo ratings yet

- Express Limited Warranty: FORM 6315 First EditionDocument2 pagesExpress Limited Warranty: FORM 6315 First EditionLei LiNo ratings yet

- Simulation Lars BrinkschulteDocument9 pagesSimulation Lars BrinkschultehathamphanNo ratings yet

- DATASHEET-valvula de Cierre de Admision de Aire positivo-RODADEACODocument2 pagesDATASHEET-valvula de Cierre de Admision de Aire positivo-RODADEACOGermán SanabriaNo ratings yet

- Kèm File Nghe: Kỳ Thi Chọn Học Sinh Giỏi Lớp 9Document9 pagesKèm File Nghe: Kỳ Thi Chọn Học Sinh Giỏi Lớp 9Anh LanNo ratings yet

- Computer Systems and Networking Guide: A Complete Guide to the Basic Concepts in Computer Systems, Networking, IP Subnetting and Network SecurityFrom EverandComputer Systems and Networking Guide: A Complete Guide to the Basic Concepts in Computer Systems, Networking, IP Subnetting and Network SecurityRating: 4.5 out of 5 stars4.5/5 (13)

- Microsoft Azure Infrastructure Services for Architects: Designing Cloud SolutionsFrom EverandMicrosoft Azure Infrastructure Services for Architects: Designing Cloud SolutionsNo ratings yet

- ITIL 4: Digital and IT strategy: Reference and study guideFrom EverandITIL 4: Digital and IT strategy: Reference and study guideRating: 5 out of 5 stars5/5 (1)

- Set Up Your Own IPsec VPN, OpenVPN and WireGuard Server: Build Your Own VPNFrom EverandSet Up Your Own IPsec VPN, OpenVPN and WireGuard Server: Build Your Own VPNRating: 5 out of 5 stars5/5 (1)

- FTTx Networks: Technology Implementation and OperationFrom EverandFTTx Networks: Technology Implementation and OperationRating: 5 out of 5 stars5/5 (1)

- AWS Certified Cloud Practitioner Study Guide: CLF-C01 ExamFrom EverandAWS Certified Cloud Practitioner Study Guide: CLF-C01 ExamRating: 5 out of 5 stars5/5 (1)

- Evaluation of Some Websites that Offer Virtual Phone Numbers for SMS Reception and Websites to Obtain Virtual Debit/Credit Cards for Online Accounts VerificationsFrom EverandEvaluation of Some Websites that Offer Virtual Phone Numbers for SMS Reception and Websites to Obtain Virtual Debit/Credit Cards for Online Accounts VerificationsRating: 5 out of 5 stars5/5 (1)

- ITIL® 4 Create, Deliver and Support (CDS): Your companion to the ITIL 4 Managing Professional CDS certificationFrom EverandITIL® 4 Create, Deliver and Support (CDS): Your companion to the ITIL 4 Managing Professional CDS certificationRating: 5 out of 5 stars5/5 (2)

- The CompTIA Network+ Computing Technology Industry Association Certification N10-008 Study Guide: Hi-Tech Edition: Proven Methods to Pass the Exam with Confidence - Practice Test with AnswersFrom EverandThe CompTIA Network+ Computing Technology Industry Association Certification N10-008 Study Guide: Hi-Tech Edition: Proven Methods to Pass the Exam with Confidence - Practice Test with AnswersNo ratings yet

- AWS Certified Solutions Architect Study Guide: Associate SAA-C02 ExamFrom EverandAWS Certified Solutions Architect Study Guide: Associate SAA-C02 ExamNo ratings yet

- Concise Guide to OTN optical transport networksFrom EverandConcise Guide to OTN optical transport networksRating: 4 out of 5 stars4/5 (2)

- Computer Networking: The Complete Beginner's Guide to Learning the Basics of Network Security, Computer Architecture, Wireless Technology and Communications Systems (Including Cisco, CCENT, and CCNA)From EverandComputer Networking: The Complete Beginner's Guide to Learning the Basics of Network Security, Computer Architecture, Wireless Technology and Communications Systems (Including Cisco, CCENT, and CCNA)Rating: 4 out of 5 stars4/5 (4)

- The Ultimate Kali Linux Book - Second Edition: Perform advanced penetration testing using Nmap, Metasploit, Aircrack-ng, and EmpireFrom EverandThe Ultimate Kali Linux Book - Second Edition: Perform advanced penetration testing using Nmap, Metasploit, Aircrack-ng, and EmpireNo ratings yet

- Software-Defined Networks: A Systems ApproachFrom EverandSoftware-Defined Networks: A Systems ApproachRating: 5 out of 5 stars5/5 (1)

- CCNA: 3 in 1- Beginner's Guide+ Tips on Taking the Exam+ Simple and Effective Strategies to Learn About CCNA (Cisco Certified Network Associate) Routing And Switching CertificationFrom EverandCCNA: 3 in 1- Beginner's Guide+ Tips on Taking the Exam+ Simple and Effective Strategies to Learn About CCNA (Cisco Certified Network Associate) Routing And Switching CertificationNo ratings yet

- The Compete Ccna 200-301 Study Guide: Network Engineering EditionFrom EverandThe Compete Ccna 200-301 Study Guide: Network Engineering EditionRating: 5 out of 5 stars5/5 (4)

- Advanced Antenna Systems for 5G Network Deployments: Bridging the Gap Between Theory and PracticeFrom EverandAdvanced Antenna Systems for 5G Network Deployments: Bridging the Gap Between Theory and PracticeRating: 5 out of 5 stars5/5 (1)

- Amazon Web Services (AWS) Interview Questions and AnswersFrom EverandAmazon Web Services (AWS) Interview Questions and AnswersRating: 4.5 out of 5 stars4.5/5 (3)

- Hacking Network Protocols: Complete Guide about Hacking, Scripting and Security of Computer Systems and Networks.From EverandHacking Network Protocols: Complete Guide about Hacking, Scripting and Security of Computer Systems and Networks.Rating: 5 out of 5 stars5/5 (2)