Professional Documents

Culture Documents

3 Esd/Eos: Intel® Manufacturing Enabling Guide May 2010

Uploaded by

Nilesh NarkhedeOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

3 Esd/Eos: Intel® Manufacturing Enabling Guide May 2010

Uploaded by

Nilesh NarkhedeCopyright:

Available Formats

3 ESD/EOS

Intel® Manufacturing Enabling Guide

May 2010

Intel® Manufacturing Enabling Guide

May 2010

ESD/EOS

Disclaimers

The information contained in this document is provided for informational purposes only and

represents the current view of Intel Corporation (“Intel”) and its contributors (“Contributors”)

on quality, as of the date of publication. Intel and the Contributors make no commitment to

update the information contained in this document, and Intel reserves the right to make

changes at any time, without notice.

THIS DOCUMENT IS PROVIDED “AS IS.” NEITHER INTEL, NOR THE CONTRIBUTORS MAKE ANY

REPRESENTATIONS OF ANY KIND WITH RESPECT TO PRODUCTS REFERENCED HEREIN,

WHETHER SUCH PRODUCTS ARE THOSE OF INTEL, THE CONTRIBUTORS, OR THIRD PARTIES.

INTEL, AND ITS CONTRIBUTORS EXPRESSLY DISCLAIM ANY AND ALL WARRANTIES, IMPLIED

OR EXPRESS, INCLUDING WITHOUT LIMITATION, ANY WARRANTIES OF MERCHANTABILITY,

FITNESS FOR ANY PARTICULAR PURPOSE, NON-INFRINGEMENT, AND ANY WARRANTY

ARISING OUT OF THE INFORMATION CONTAINED HEREIN, INCLUDING WITHOUT

LIMITATION, ANY PRODUCTS, SPECIFICATIONS, OR OTHER MATERIALS REFERENCED

HEREIN. INTEL, AND ITS CONTRIBUTORS DO NOT WARRANT THAT THIS DOCUMENT IS FREE

FROM ERRORS, OR THAT ANY PRODUCTS OR OTHER TECHNOLOGY DEVELOPED IN

CONFORMANCE WITH THIS DOCUMENT WILL PERFORM IN THE INTENDED MANNER, OR WILL

BE FREE FROM INFRINGEMENT OF THIRD PARTY PROPRIETARY RIGHTS, AND INTEL, AND ITS

CONTRIBUTORS DISCLAIM ALL LIABILITY THEREFOR.

INTEL, AND ITS CONTRIBUTORS DO NOT WARRANT THAT ANY PRODUCT REFERENCED

HEREIN OR ANY PRODUCT OR TECHNOLOGY DEVELOPED IN RELIANCE UPON THIS

DOCUMENT, IN WHOLE OR IN PART, WILL BE SUFFICIENT, ACCURATE, RELIABLE, COMPLETE,

FREE FROM DEFECTS OR SAFE FOR ITS INTENDED PURPOSE, AND HEREBY DISCLAIM ALL

LIABILITIES THEREFOR. ANY PERSON MAKING, USING OR SELLING SUCH PRODUCT OR

TECHNOLOGY DOES SO AT HIS OR HER OWN RISK.

Licenses may be required. Intel, its contributors and others may have patents or pending

patent applications, trademarks, copyrights or other intellectual proprietary rights covering

subject matter contained or described in this document. No license, express, implied, by

estoppel or otherwise, to any intellectual property rights of Intel or any other party is granted

herein. It is your responsibility to seek licenses for such intellectual property rights from Intel

and others where appropriate.

Limited License Grant. Intel hereby grants you a limited copyright license to copy this

document for your use and internal distribution only. You may not distribute this document

externally, in whole or in part, to any other person or entity.

LIMITED LIABILITY. IN NO EVENT SHALL INTEL, OR ITS CONTRIBUTORS HAVE ANY LIABILITY

TO YOU OR TO ANY OTHER THIRD PARTY, FOR ANY LOST PROFITS, LOST DATA, LOSS OF USE

OR COSTS OF PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES, OR FOR ANY DIRECT,

INDIRECT, SPECIAL OR CONSEQUENTIAL DAMAGES ARISING OUT OF YOUR USE OF THIS

DOCUMENT OR RELIANCE UPON THE INFORMATION CONTAINED HEREIN, UNDER ANY CAUSE

OF ACTION OR THEORY OF LIABILITY, AND IRRESPECTIVE OF WHETHER INTEL, OR ANY

CONTRIBUTOR HAS ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES. THESE

LIMITATIONS SHALL APPLY NOTWITHSTANDING THE FAILURE OF THE ESSENTIAL PURPOSE

OF ANY LIMITED REMEDY.

Copyright © 2010, Intel Corporation. All rights reserved.* Other names and brands may be

claimed as the property of others.

3-2 Intel® Manufacturing Enabling Guide

May 2010

ESD/EOS

Contents

3.1 ESD ··············································································· 3-4

3.1.1 Electrostatic Discharge ........................................... 3-4

3.1.2 Why Should I Care About Electronic Discharge? ......... 3-4

3.1.3 Intel’s Commitment to Eliminate ESD Damage ........... 3-4

3.1.4 What is ESD ......................................................... 3-5

3.1.5 Common Causes of ESD ......................................... 3-5

3.1.6 ESD Occurs at All Levels of Integration ..................... 3-6

3.1.7 What Can I Do To Prevent ESD? .............................. 3-6

3.1.8 Outfitting an Effective Workplace ............................. 3-7

3.1.9 Summary ............................................................. 3-8

3.2 Electrical Overstress......................................................... 3-9

3.2.1 Electrical Overstress .............................................. 3-9

3.2.2 How EOS Damages a Component............................. 3-9

3.2.3 Common Causes of EOS ....................................... 3-10

3.2.4 Prevention of EOS ............................................... 3-11

3.3 References ................................................................... 3-12

3.4 Revision Summary ......................................................... 3-13

Figures

Figure 3-1. Junction Spiking Failure ........................................... 3-9

Figure 3-2. Melted Metallization Failure .................................... 3-10

Figure 3-3. Open Bond Wire Failure .......................................... 3-10

Intel® Manufacturing Enabling Guide 3-3

May 2010

ESD/EOS

3.1 ESD

3.1.1 Electrostatic Discharge

Electrostatic discharge (ESD) costs the electronics industry millions of

dollars each year in damaged components, non-functional circuit

boards and scrambled or missing information. ESD can occur in the

manufacturing, shipping, receiving, and field handling of integrated

circuits or computer boards with no visible signs of damage. A

malfunction in these components or boards can occur immediately or

the apparatus may perform for weeks, months, or even years before

an unpredictable and premature breakdown causes a field failure.

3.1.2 Why Should I Care About Electronic Discharge?

When you incorporate electronic components or boards into your

products, ESD damage can have a direct impact on your company’s

reputation and profits. That is because electrostatic damage directly

affects the quality and reliability of your products. However, for a small

investment in time, manpower, and equipment, you can virtually

eliminate ESD-caused problems. The tangible benefits to you include:

• Higher manufacturing yields

• Less rework and inventory

• Reduced overall costs

• Fewer field failures and warranty calls

• Increased product reliability

• More repeat business resulting in greater profits

3.1.3 Intel’s Commitment to Eliminate ESD Damage

Intel manufactures and uses electronic components, and has

implemented a comprehensive ESD prevention program to ensure that

its products are delivered to customers with the highest possible

3-4 Intel® Manufacturing Enabling Guide

May 2010

ESD/EOS

reliability. Our experts would like to share with our suppliers and

customers what they have learned about ESD control. Using this

information, you can implement similar preventive practices in your

factories and warehouses. As a result, component failures can be

minimized

3.1.4 What is ESD

ESD is the transfer of electrical charge between two bodies at different

potentials, either through direct contact or through an induced

electrical field. It is the phenomenon that gives you a mild shock when

you walk across a carpeted floor and then touch a doorknob. While this

discharge gives a harmless shock to humans, it is lethal to sensitive

electronics. For example, the simple act of walking across a vinyl floor

can generate up to 12,000 V of static electricity. That is many times

the charge needed to ruin a standard Shottky TTL component.

Several technical failure mechanisms associated with ESD cause

damage to microelectronic devices, including gate oxide breakdown,

junction spiking and latch-up.

• Gate oxide failure is a breakdown of the dielectric between the

transistor gate and channel resulting in excessive leakage or a

functional failure

• Junction spiking failure is a migration of the metallization

through the source/drain junction of MOS transistors causing

leakage or a functional failure

• Latch-up failure can be triggered by ESD, causing an internal

feedback mechanism that gives rise to temporary or permanent

loss of circuit function

3.1.5 Common Causes of ESD

Electrostatic generation arising from friction between two materials is

called triboelectric charging. It occurs when two materials are

separated or rubbed together. Examples include:

Intel® Manufacturing Enabling Guide 3-5

May 2010

ESD/EOS

• Opening a common plastic bag

• Removing adhesive tape from a roll or container

• Walking across a floor

• Transporting computer boards or components around in their

rays on carts

• Sliding circuit boards on a work bench

When handling parts or their containers, ungrounded personnel can

transfer high static charges. Unless these static charges are slowly

dissipated, ESD event can inflict damage to the devices.

Electrical fields can penetrate electrical devices. An ungrounded person

handling a component or computer board in a non-static shielded

container can inadvertently create an electrical charge imbalance on

the sensitive electronic device within the container.

3.1.6 ESD Occurs at All Levels of Integration

Electrostatic discharge is not selective when affecting your products. It

can strike components directly or indirectly by passing to the

component via connectors and cables. Components mounted on circuit

boards are also susceptible. In-line film resistors between inputs and

off-board connectors provide only marginal ESD protection and are

often damaged themselves.

3.1.7 What Can I Do To Prevent ESD?

Fortunately, preventing ESD can be relatively easy and inexpensive.

Two areas of focus are:

• Eliminating static charges from the workplace

• Properly shielding components and assemblies from static fields

Eliminating static electricity in the workplace is accomplished by

selecting low-charge generating materials. Selecting low-charge

3-6 Intel® Manufacturing Enabling Guide

May 2010

ESD/EOS

generating materials minimizes charge from being formed in the first

place, grounding operators, equipment, and devices (components and

computer boards). Grounding prevents static charge buildup and

electrostatic potential differences. Electrical field damage is averted by

transporting products in special electrostatic shielding packages.

Many vendors of ESD-protective equipment are willing to audit your

facilities, recommend appropriate procedures and materials, and assist

in their implementation. You may choose to consult with such a firm to

determine your exact requirements; in the meantime, review this

chapter to gain an understanding of the basic components of a sound

ESD prevention program.

3.1.8 Outfitting an Effective Workplace

An effective workplace should be outfitted with the following items:

ESD protective clothing/smocks. Street clothing must not come in

contact with components or computer boards since the various

materials in clothing can generate high static charges. ESD protective

smocks, manufactured with conductive fibers, are recommended.

Electrostatic shielding containers or totes. These containers

(bags, boxes, etc.) are made of specially formulated materials which

protect sensitive devices during transport and storage. They must be

sealed to work as intended.

Antistatic or dissipative carriers. These provide ESD protection

during component movement in the manufacturing process. It must be

noted that antistatic materials alone will not provide complete

protection. They must be used in conjunction with other methods such

as totes or electrostatic shielding bags.

Dissipative table mat or table surface. The mat or table surface

should provide a controlled discharge of static voltages and must be

grounded. The surface resistance is designed such that sliding a

Intel® Manufacturing Enabling Guide 3-7

May 2010

ESD/EOS

computer board or component across its surface will not generate

significant voltage.

Personal grounding. A wrist strap or ESD cuff is kept in constant

contact with bare skin and has a cable for attaching it to the ESD

ground. The purpose of the wrist strap is to drain off the operator’s

static charge. The wrist strap cord has a current-limiting resistor for

personnel safety. Wrist straps must be tested frequently to ensure that

they are undamaged and operating correctly. When a wrist strap is

impractical, special heel straps or shoes can be used. These items are

effective only when used in conjunction with a dissipative floor or floor

mat.

ESD protective floor or mat. The mat must be grounded through a

current-limiting resistor. The floor or mat dissipates the static charge

of personnel approaching the work bench. Special conductive tile or

floor treatment can be used when mats are not practical or cause a

safety hazard.

ESD Chairs. ESD Chairs should be used during seated operations and

grounded via their conductive wheels. These wheels must be cleaned

periodically to minimize charge generation and allow charge dissipation

to occur.

3.1.9 Summary

Intel uses a full range of electrostatic discharge prevention techniques.

We invest in proper employee training, purchase appropriate ESD

protection equipment and supplies and adapt our handling and

manufacturing procedures for ESD prevention requirements. The same

attention to detail is required of all our suppliers, factories, repair

centers, and field service staff.

Intel is committed to helping its partners — both suppliers and

customers — to manage the ESD problem. If we can be of further

assistance in your efforts to eliminate electrostatic discharge damage,

please contact the Intel Components Quality Question Line: In the USA

1-800-628-8686 or 1-916-356-7599, or contact your local Intel Sales

Office.

3-8 Intel® Manufacturing Enabling Guide

May 2010

ESD/EOS

3.2 Electrical Overstress

3.2.1 Electrical Overstress

EOS is the number one cause of damage to IC components. This

section describes EOS and how to prevent it.

3.2.2 How EOS Damages a Component

Damage is caused by thermal overstress to a component’s circuitry.

The amount of damage caused by EOS depends on the magnitude and

duration of electrical transient pulse widths. We can broadly classify

the duration of pulse widths into long (>100 μs) and short (<100 μs)

types, and magnitude into exceeding an individual component’s EOS

threshold. For short pulse widths the most common failure mode is

junction spiking.

Figure 3-1. Junction Spiking Failure

For long electrical pulse widths the most common failure modes are

melted metallization and open bond wires.

Intel® Manufacturing Enabling Guide 3-9

May 2010

ESD/EOS

Figure 3-2. Melted Metallization Failure

Figure 3-3. Open Bond Wire Failure

3.2.3 Common Causes of EOS

Inadequate work procedures:

• Lack of standard work procedures

• Incorrect device orientation

• Insertion/removal of components with power applied

• Boards/units not well connected and then power applied

3-10 Intel® Manufacturing Enabling Guide

May 2010

ESD/EOS

Noisy Production Environments:

• Lack of power line conditioners

• Lack of AC line filters

Improper testing at device or board level can create EOS:

• Hot switching effect

• Incorrect test sequence such as application of signals to Device

Under Test (DUT) before powering up chip

• Application of excessive voltages to chip beyond spec limits

• Poorly designed electrical stress tests such as burn-in which

overstresses sensitive chips

Use of low quality power supplies:

• Poor design considerations can lead to noise sources especially in

switching power supplies

• Lack of power supply overvoltage protection circuits

• Insufficient line filtering and/or transient suppression at the

input stage of power supplies

• Incorrect selection of fuse providing inadequate protection

Lack of Proper Equipment and Line Monitoring:

• Equipment not properly grounded

• Loose connections causing intermittent transient events

• Poor wire maintenance

• AC supply lines not monitored for voltage transients or noise

3.2.4 Prevention of EOS

Establish and follow proper work procedures

Intel® Manufacturing Enabling Guide 3-11

May 2010

ESD/EOS

Conduct regular AC supply line monitoring and, if necessary, install

EOS line control equipment such as incoming line filtering and

transient suppression circuits.

Ensure proper testing of components and boards:

• Check test programs for hot switching and incorrect test

sequence

• Solicit maximum specification ratings from manufacturers to

ensure devices are not overstressed

• Ensure reliability stress tests are properly designed, especially

during burn-in

• Check for excessive noise levels

• Use “transzorbs” to clamp voltage spikes

Use quality power supplies with the following features:

• Overvoltage protection

• Proper heat dissipation

• Use of fuses at critical locations

Adhere to a strict equipment maintenance program to ensure:

• Equipment is properly grounded

• There are no loose connections

3.3 References

[1] Edward S. Yang, “Microelectronic Devices”, McGraw-Hill, 1988

[2] Kohlhass, Phil, “Controlling Potential Static Charge Problems”,

3M Nuclear Products Dept., St.Paul, MN

[3] “Electrical Overstress/Electrostatic Discharge Symposium

Proceedings”, The EOS/ESD Association and ITT Research

Institute, 1985 and 1986

[4] DOD-HNBK-263, Electrostatic Discharge Control Handbook for

Protection of Electrical and Electronic Parts, Assemblies and

Equipment”, 2 May, 1980

3-12 Intel® Manufacturing Enabling Guide

May 2010

ESD/EOS

[5] McFarland, W.Y., “The electronic benefits of an effective

electrostatic discharge awareness and control program—an

empirical analysis”. 1981 Electrical Overstress/Electrostatic

Discharge Symposium Proceedings

[6] For more information regarding PGA insertion, request a copy of

item # 8130 by calling the Intel FAXBACK line U.S. 1-800-628-

2283 or 1-916-356-3105 Europe 44-793-4960646

3.4 Revision Summary

Original publication

Intel® Manufacturing Enabling Guide 3-13

May 2010

You might also like

- F152 Installation ManualDocument84 pagesF152 Installation ManualTatiana Pérez Alvarado100% (1)

- 50 G SC200 Handbook LTRDocument129 pages50 G SC200 Handbook LTRChungwa ChanjiNo ratings yet

- Topaz User Manual (Eng)Document418 pagesTopaz User Manual (Eng)mohanraj100% (5)

- P2230 ESR Installation Manual PDFDocument13 pagesP2230 ESR Installation Manual PDFJohn Paul AmbuludiNo ratings yet

- DP-300 Current Differential Protection Relay IM EN 6 2012 PDFDocument26 pagesDP-300 Current Differential Protection Relay IM EN 6 2012 PDFElectrificationNo ratings yet

- ATL-Hiperion ODU Installation ManualDocument24 pagesATL-Hiperion ODU Installation ManualBarry RuleNo ratings yet

- Infineon - Tailored ESD Protection For Various Electronic Interfaces Application Note AN248Document11 pagesInfineon - Tailored ESD Protection For Various Electronic Interfaces Application Note AN248sanjeevsoni64No ratings yet

- F01T100 (ETP4860) Quick Installation GuideDocument63 pagesF01T100 (ETP4860) Quick Installation GuideHoa Viet LuNo ratings yet

- F01T300 Quick Installation Guide 02 PDFDocument55 pagesF01T300 Quick Installation Guide 02 PDFMarlon AdamsNo ratings yet

- ATX 12V Power Supply Design Guide v1.3Document38 pagesATX 12V Power Supply Design Guide v1.3cliftoncageNo ratings yet

- 2 12446-Asp11301Document13 pages2 12446-Asp11301Jorge rodriNo ratings yet

- UPD78F0881Document704 pagesUPD78F0881phanductrifangiaNo ratings yet

- MSX-E370x eDocument62 pagesMSX-E370x eFernando KrauchukNo ratings yet

- Taylor - TE100-ManualDocument114 pagesTaylor - TE100-Manualnetinhox4No ratings yet

- ESD Phenomena and The Reliability For MicroelectronicsDocument55 pagesESD Phenomena and The Reliability For MicroelectronicsSandesh Kumar B VNo ratings yet

- Site MasterDocument92 pagesSite MasterAlf Nanfade NanfadeNo ratings yet

- Electrostatic Discharge (ESD) Control (D-1348), Rev. FDocument25 pagesElectrostatic Discharge (ESD) Control (D-1348), Rev. FMohamad Khair Shaiful Alam100% (1)

- User'S Guide: OTP/Flash Writer EM78 SeriesDocument52 pagesUser'S Guide: OTP/Flash Writer EM78 SeriesDuy LeNo ratings yet

- Grounding Products and SystemsDocument84 pagesGrounding Products and SystemsEric Aarriaga AlpizarNo ratings yet

- Transformer: Transformer ST.., DT.. Operation Manual For TransformersDocument9 pagesTransformer: Transformer ST.., DT.. Operation Manual For TransformersΤσιμπινός ΣπύροςNo ratings yet

- Acom Ethernet Interface Unit (EIU)Document21 pagesAcom Ethernet Interface Unit (EIU)Sohaib Omer SalihNo ratings yet

- ESD WhitePaperDocument7 pagesESD WhitePaperskrishna261No ratings yet

- Equipment DamageDocument13 pagesEquipment DamagezoomNo ratings yet

- Entc-1000 Manual enDocument51 pagesEntc-1000 Manual enLiliana JaramilloNo ratings yet

- APR48-3G Manual PDFDocument116 pagesAPR48-3G Manual PDFpanincongNo ratings yet

- DS-K1T331 Series Face Recognition Terminal: User ManualDocument154 pagesDS-K1T331 Series Face Recognition Terminal: User ManualJuan Carlos BastardoNo ratings yet

- JSS - 0251 User - Handbook - AFAS - 22.08.16 (Last Update)Document49 pagesJSS - 0251 User - Handbook - AFAS - 22.08.16 (Last Update)bipinsarkar88No ratings yet

- AcNetPro - Installation Manual PDFDocument24 pagesAcNetPro - Installation Manual PDFsistemsistemNo ratings yet

- Installation Manual: Sectoral AntennasDocument40 pagesInstallation Manual: Sectoral AntennasAmerullah NiaziNo ratings yet

- Chip Pantalla TorreyMFQDocument78 pagesChip Pantalla TorreyMFQWilly Bracamonte TellesNo ratings yet

- Pasolink Neo Te Cx2200 - Instruction Manual Ver - 02.05Document0 pagesPasolink Neo Te Cx2200 - Instruction Manual Ver - 02.05Julio Perez FerrufinoNo ratings yet

- 78K0R/KE3: User's ManualDocument878 pages78K0R/KE3: User's ManualbotosionNo ratings yet

- Direct and Indirect Contact - Protection Against Electric Shock - Electronic Components. Distributor, Online Shop - Transfer Multisort ElektronikDocument9 pagesDirect and Indirect Contact - Protection Against Electric Shock - Electronic Components. Distributor, Online Shop - Transfer Multisort Elektronikhaymannoo10No ratings yet

- User's Manual Upd78f0134m5gk-9et Ren U16228ej3v1ud00 Mah 20050801Document619 pagesUser's Manual Upd78f0134m5gk-9et Ren U16228ej3v1ud00 Mah 20050801Clay CowgillNo ratings yet

- IC-ON-LINE - CN d789477 4609565Document394 pagesIC-ON-LINE - CN d789477 4609565Campean AncaNo ratings yet

- Estudio 383pDocument76 pagesEstudio 383pAddPrint AlbaniaNo ratings yet

- Wago 750-841 Ethernet Fieldbus Quick StartDocument26 pagesWago 750-841 Ethernet Fieldbus Quick StartDrago TuljNo ratings yet

- S5 135uDocument534 pagesS5 135uMiguel MacpNo ratings yet

- RH850-1 RenesasDocument53 pagesRH850-1 RenesassamirNo ratings yet

- LESSON 1 Occupational Safety and Health Module 1Document9 pagesLESSON 1 Occupational Safety and Health Module 1MELCHOR CASTRONo ratings yet

- Precision 3650 Workstation - Owners ManualDocument74 pagesPrecision 3650 Workstation - Owners ManualaashishmaruNo ratings yet

- D78F9232 NecDocument383 pagesD78F9232 NecM Amjad ZaidNo ratings yet

- MSAD Installation Ed1.1 enDocument49 pagesMSAD Installation Ed1.1 enTauseefAhmedNo ratings yet

- RH850 Users Manual HardwareDocument4,535 pagesRH850 Users Manual HardwaregezgegNo ratings yet

- Electrical Safety OffshoreDocument2 pagesElectrical Safety Offshorerw992049No ratings yet

- PRINT - CSC-121 Breaker Protection IED Technical Application Manual V1.03 (英文) PDFDocument309 pagesPRINT - CSC-121 Breaker Protection IED Technical Application Manual V1.03 (英文) PDFAldo Bona HasudunganNo ratings yet

- Solar Photovoltaic Power System HandbookDocument22 pagesSolar Photovoltaic Power System HandbookGeroldo 'Rollie' L. Querijero100% (2)

- Engineering WS II - PC Maintenance Lab Manual-4Document53 pagesEngineering WS II - PC Maintenance Lab Manual-4jehan sawaftaNo ratings yet

- PowerLink IP EquipmentManual C254-DDocument310 pagesPowerLink IP EquipmentManual C254-DINGWIRBONo ratings yet

- Quectel EC200U Series Hardware Design V1.0Document95 pagesQuectel EC200U Series Hardware Design V1.0Phan ToanNo ratings yet

- Ren U15560ej2v0um00 Mah 20030901Document41 pagesRen U15560ej2v0um00 Mah 20030901Edward MainaNo ratings yet

- DVR Evix Er-401Document82 pagesDVR Evix Er-401SaimonK100% (1)

- Manual CTIDocument206 pagesManual CTIcgrenillon35No ratings yet

- F01S200 Quick Installation GuideDocument50 pagesF01S200 Quick Installation GuideMohammadBakir100% (1)

- ESD Awareness Program - Subcon v1 0 (Read-Only)Document24 pagesESD Awareness Program - Subcon v1 0 (Read-Only)Neeraj Kumar SharmaNo ratings yet

- Metler Toledo Ind560 PLC enDocument149 pagesMetler Toledo Ind560 PLC enAndres RodriguezNo ratings yet

- Trilogy of Connectors: Basic Principles and Connector Design ExplanationsFrom EverandTrilogy of Connectors: Basic Principles and Connector Design ExplanationsRating: 5 out of 5 stars5/5 (1)

- RIoT Control: Understanding and Managing Risks and the Internet of ThingsFrom EverandRIoT Control: Understanding and Managing Risks and the Internet of ThingsRating: 5 out of 5 stars5/5 (1)

- A Study of Meachanisms of Esd Damge To Reticles Presentation ION Sya LevitDocument27 pagesA Study of Meachanisms of Esd Damge To Reticles Presentation ION Sya LevitNilesh NarkhedeNo ratings yet

- Challenging The Nimzo-Indian (David Vigorito)Document330 pagesChallenging The Nimzo-Indian (David Vigorito)Nilesh NarkhedeNo ratings yet

- ElectrostaticDischargeRoadmap-March42004Final 061405edits 000Document7 pagesElectrostaticDischargeRoadmap-March42004Final 061405edits 000Nilesh NarkhedeNo ratings yet

- Chess Brilliancies (Wenman)Document208 pagesChess Brilliancies (Wenman)Nilesh NarkhedeNo ratings yet

- (M. M Botvinnik) Alekhine vs. Euwe Return Match 19Document52 pages(M. M Botvinnik) Alekhine vs. Euwe Return Match 19Marcelo VicenteNo ratings yet

- Capablanca - Lasker Match 1921 (Capablanca, 1921)Document29 pagesCapablanca - Lasker Match 1921 (Capablanca, 1921)Luis Gabriel Bautista100% (1)

- UntitledDocument110 pagesUntitledArjun PaliwalNo ratings yet

- Trek Inc: Electrostatic VoltageDocument2 pagesTrek Inc: Electrostatic VoltageNilesh NarkhedeNo ratings yet

- Commonly Asked Questions About Esd Flooring and Static Control Floors - StaticSmaDocument5 pagesCommonly Asked Questions About Esd Flooring and Static Control Floors - StaticSmaNilesh NarkhedeNo ratings yet

- Correlation of Antibacterial Performance To Electrostatic 2022 Journal of ElDocument7 pagesCorrelation of Antibacterial Performance To Electrostatic 2022 Journal of ElNilesh NarkhedeNo ratings yet

- Colorex - Pre Formed Coved CornersDocument1 pageColorex - Pre Formed Coved CornersNilesh NarkhedeNo ratings yet

- Conductivity Enhancement and Chargeability Reduction of - 2022 - Journal of EleDocument6 pagesConductivity Enhancement and Chargeability Reduction of - 2022 - Journal of EleNilesh NarkhedeNo ratings yet

- Capablanca and His AnalystsDocument4 pagesCapablanca and His AnalystsNilesh NarkhedeNo ratings yet

- Semiconductor DevicesDocument524 pagesSemiconductor Devicesapuinwork100% (1)

- 0403 EsdDocument8 pages0403 EsddurairajalingamrNo ratings yet

- Accumulation of Spatial Charge On The Surface of Protecting - 2022 - Journal ofDocument5 pagesAccumulation of Spatial Charge On The Surface of Protecting - 2022 - Journal ofNilesh NarkhedeNo ratings yet

- Cost Effective Fabrication Approaches For Improving Outpu 2022 Journal of ElDocument10 pagesCost Effective Fabrication Approaches For Improving Outpu 2022 Journal of ElNilesh NarkhedeNo ratings yet

- Care and maintenance instructions for Colorex flooringDocument2 pagesCare and maintenance instructions for Colorex flooringNilesh NarkhedeNo ratings yet

- Emc Emc Esd and Fast Transient PulsesDocument10 pagesEmc Emc Esd and Fast Transient PulsesNilesh NarkhedeNo ratings yet

- Costof ESDDamageDocument1 pageCostof ESDDamageNilesh NarkhedeNo ratings yet

- ECS-ComponentsDocument57 pagesECS-ComponentsNilesh NarkhedeNo ratings yet

- Electro Magnetic ComplianceDocument16 pagesElectro Magnetic ComplianceNilesh NarkhedeNo ratings yet

- Southwest Association ESD: February MeetingDocument3 pagesSouthwest Association ESD: February MeetingNilesh NarkhedeNo ratings yet

- EMC For Implantable Medical DevicesDocument52 pagesEMC For Implantable Medical DevicesNilesh NarkhedeNo ratings yet

- Electric Filed Mill PartsDocument3 pagesElectric Filed Mill PartsNilesh NarkhedeNo ratings yet

- ESD Training Leaned TechDocument14 pagesESD Training Leaned TechNilesh NarkhedeNo ratings yet

- ESD Basics: Basic Concepts inDocument27 pagesESD Basics: Basic Concepts inNilesh NarkhedeNo ratings yet

- Electronic Blasting Sysytesm PresenattionDocument30 pagesElectronic Blasting Sysytesm PresenattionNilesh NarkhedeNo ratings yet

- Crestwood Technology Group, Corp.: ANSI/ESD-S20.20-1999Document1 pageCrestwood Technology Group, Corp.: ANSI/ESD-S20.20-1999Nilesh NarkhedeNo ratings yet

- Electronic Catalogue EnglishDocument13 pagesElectronic Catalogue EnglishNilesh NarkhedeNo ratings yet

- Philips+40PFL3706-F7+Chassis+PL11 1 PDFDocument55 pagesPhilips+40PFL3706-F7+Chassis+PL11 1 PDFHuanglong Zen100% (1)

- TIG Welder Troubleshooting GuideDocument23 pagesTIG Welder Troubleshooting Guideluddy812100% (2)

- Power Transformers: Rectifier Transformers - Terminal Connection Data Full Wave C.T. (Center Tap) Full Wave BridgeDocument3 pagesPower Transformers: Rectifier Transformers - Terminal Connection Data Full Wave C.T. (Center Tap) Full Wave BridgeversitechNo ratings yet

- Voltage Reference 23Document25 pagesVoltage Reference 23api-3750190No ratings yet

- Philips EnduraLED T8 Tube LED Light Installation GuideDocument3 pagesPhilips EnduraLED T8 Tube LED Light Installation GuideGreen SupplyNo ratings yet

- 6th Sem SyllabusDocument7 pages6th Sem SyllabusNitin MauryaNo ratings yet

- Water-Level-Control CircuitDocument2 pagesWater-Level-Control CircuitUYeMin Htike0% (1)

- Lab 8 ReportDocument6 pagesLab 8 Reportapi-491291595No ratings yet

- Is Now Part ofDocument25 pagesIs Now Part ofkilowatt СкворцовNo ratings yet

- Zuper 400Document4 pagesZuper 400Md Kaleem100% (1)

- What Are the Properties of the Doosan Middle Loss DS-7409D (X) PCB Material - 副本Document4 pagesWhat Are the Properties of the Doosan Middle Loss DS-7409D (X) PCB Material - 副本jackNo ratings yet

- Bab 10 Analisis Sinyal Ac FETDocument74 pagesBab 10 Analisis Sinyal Ac FETFadhlanNo ratings yet

- AutotransformerDocument26 pagesAutotransformerMonika SharmaNo ratings yet

- Rf&Me Lecture 6 - Microwave Transmission LinesDocument48 pagesRf&Me Lecture 6 - Microwave Transmission LinesBasir Usman100% (1)

- Cross Lamp ControllerDocument2 pagesCross Lamp ControllerRobertoAndrésBilliardAlvaradoNo ratings yet

- OutlineDocument18 pagesOutlineherokaboss1987No ratings yet

- PowerFlex 700s Frames 9 A 14Document220 pagesPowerFlex 700s Frames 9 A 14Obsol EtoNo ratings yet

- Vtu Syllabus 02 PDFDocument6 pagesVtu Syllabus 02 PDFAmarNo ratings yet

- CLS Aipmt-19-20 XII Phy Study-Package-6 Level-2 Chapter-14 PDFDocument40 pagesCLS Aipmt-19-20 XII Phy Study-Package-6 Level-2 Chapter-14 PDFMohammad Ashhar ImranNo ratings yet

- GXT2-10000T230 Service ManualDocument33 pagesGXT2-10000T230 Service ManualMilton Mejia80% (10)

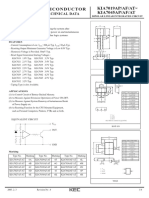

- Semiconductor KIA7019AP/AF/AT KIA7045AP/AF/AT: Technical DataDocument4 pagesSemiconductor KIA7019AP/AF/AT KIA7045AP/AF/AT: Technical DatajesadNo ratings yet

- 14 NMDocument23 pages14 NMNikhilAKothariNo ratings yet

- NTDC Internship Report on High Voltage and Short Circuit TestsDocument16 pagesNTDC Internship Report on High Voltage and Short Circuit TestsAhmad Ali0% (1)

- Project Report On Active Zinc OxideDocument6 pagesProject Report On Active Zinc OxideEIRI Board of Consultants and PublishersNo ratings yet

- A Study of Phase Noise in CMOS Oscillators: Behzad RazaviDocument13 pagesA Study of Phase Noise in CMOS Oscillators: Behzad Razavikijiji userNo ratings yet

- The SemiconductorsDocument30 pagesThe SemiconductorsPaul Ian SantillanNo ratings yet

- Diodat PDFDocument4 pagesDiodat PDFFatmir KelmendiNo ratings yet

- LM709 Operational Amplifier GuideDocument10 pagesLM709 Operational Amplifier GuidetoscanobNo ratings yet

- PQCW ODFN 020 MWL01 Datasheet PDFDocument2 pagesPQCW ODFN 020 MWL01 Datasheet PDFEd Gar YundaNo ratings yet

- Extending I2C Communication Distance With The DS28E17 - Application Note - MaximDocument3 pagesExtending I2C Communication Distance With The DS28E17 - Application Note - MaximMuhammad SaeedNo ratings yet