Professional Documents

Culture Documents

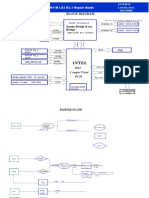

820-01055 Power Sequence

Uploaded by

tan_871714877Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

820-01055 Power Sequence

Uploaded by

tan_871714877Copyright:

Available Formats

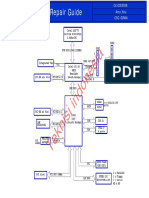

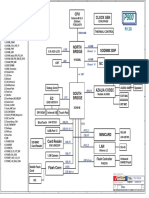

Power Sequencing Diagram

fab#sc1105

PPBUS_G3H

Suona

CHGR_EN_MVR

Suona → U6960 EN

PP3V3_G3H_RTC

U6960

PP3V3_G3H

Calpe VOUT_RTC

PP1V8_SLPS2R

Calpe Buck3

PMU_CLK32K_SOC_R

Calpe CLKOUT0_32K → H9M

PP1V8_AWAKE

Calpe Buck3 SW1 → H9M

PP1V8_SLPS2R_PMUVDDGPIO

Calpe Buck3 SW2 → Calpe

PP1V1_SLPS2R

Calpe Buck4 → H9M

PP0V8_SLPS2R

Calpe LDO0 → H9M

PP0V82_SLPS2R

Calpe Buck2 → H9M

PP3V3_AWAKE

Calpe V3P3 SW1 → H9M

PPVDDCPUSRAM_AWAKE

Calpe Buck1 → H9M

PP0V9_SLPDDR

Calpe Buck5 → H9M

P1V1_SLPDDR_SOCFET_EN

Calpe GPIO25 → U7901 EN

PP1V1_SLPDDR

U7901 → H9M

SOC_XTAL24M_IN

Enabled internally by H9M

PP1V2_AWAKE

Calpe LDO2 → H9M

PPVDDCPU_AWAKE

Calpe Buck0 → H9M

PMU_COLD_RESET_L

Calpe NRESET → H9M

PMU_SYS_ALIVE

Calpe SYS_ALIVE → H9M

PMU_ACTIVE_READY

Calpe ACTIVE_READY → H9M

<H9M loads secure ROM; SMC battery trap>

PMU_VDDMAIN_EN

Calpe VPWR_EN → U7650

PP3V3_G3H

U7650

<Calpe VOUT_RTC internal switch opens>

P3V3MAIN_PGOOD

PU to PP3V3_G3H | U7650 → Calpe GPIO1

<Calpe INIT CONFIG>

PP3V_G3H

Calpe LDO1 → PCH

PMU_CLK32K_PCH_R

Calpe CLKOUT1_32K → PCH

PCH_RTC_RESET_L

Calpe LDO1_POK → PCH

P5VG3S_EN

Calpe GPIO4 → U7650

PP5V_G3S

U7650 VR1

P3V3G3S_EN

Calpe GPIO6 → U8210

PP3V3_G3S

U8210

P1V8G3S_EN

Calpe GPIO7 → U822

PP1V8_G3S

U8220

P5VG3S_PGOOD

PU to PP1V8_G3S | U7650 → Calpe GPIO5

PMU_CLK32K_WLANBT_R

Calpe CLKOUT2_32K → WLAN/BT

<SMC checks SSD power source (Calpe or Ocarina)>

SSD_PMU_RESET_L

Ocarina | H9M GPIO19 → Ocarina PMIC_RESET*

PP1V8_SSD

Ocarina | Ocarina Buck1 → SSD

PP0V9_SSD

Ocarina | Ocarina Buck0 → SSD

SSD0_VR_P2V7_EN

Ocarina | Ocarina VEN1 → SSD

SSD0_OCARINA_WP_L

Ocarina | Ocarina WP_L → SSD

SSD0_OCARINA_PFN

Ocarina | Ocarina PFN_L → SSD

SSD0_OCARINA_LPB_L

Ocarina | Ocarina LPBN → SSD

PP1V8_SSD

Calpe | Calpe Buck10 → SSD

PP0V9_SSD

Calpe | Calpe Buck9 → SSD

NAND_DISCHARGE_EN

Calpe | Calpe GPIO21 → SSD

P2V7NAND_EN

Calpe | Calpe GPIO20 → SSD

P2V7NAND_PGOOD

Calpe | VR → Calpe GPIO19

NAND_WP_L

Calpe | Calpe GPIO23 → SSD

SSD0_OCARINA_RESET_L

Ocarina | Ocarina RESET_L → SSD

NAND_RESET_L

Calpe | Calpe GPIO22 → SSD

<SSD enabled. H9M booted to gOS.>

<Power button press>

PMU_ONOFF_L

PU to PP3V3_G3H_RTC |

Power Button → Calpe BUTTON1

PP3V3_S5

Calpe V3P3_SW2 → PCH

VCCDSW, VCCPRIM_3P3

CPU_C10_GATE_L

PU to PP3V3_S5 |

PCH → Calpe HIO_SW_EN, more

PCH_HSIO_PWR_EN

PU to PP3V3_S5 |

PCH → U8230 PP1V05_PRIMSW enable

PM_SLP_S0_L

PCH → U1930 Level Shifter

PP1V8_S5

Calpe Buck3 SW3 → PCH VCCPRIM_1P8

PM_SLP_S0_1V8_L

U1930 powered by PP1V8_S5 |

U1930 Level Shifter → H9M SLP_S0B,

Calpe SYS_SLEEP*

PPVCC_PRIM_CORE

Calpe Buck7 → PCH VCCPRIM_CORE

PP1V05_PRIM

Calpe Buck8 → PCH VCCPRIM_1P05

PP1V05_PRIMSW

U8230 FET → PCH VCCPRIM_GATED_1P05

SMC_RSMRST_L

H9M RSMRST* → PCH RSMRST* (level shifted)

<SMC waits for eSPI reset to deassert.>

<PCH will begin deasserting SLP_Sx signals over eSPI.>

EPSI_RESET_L

PCH → H9M

PCH_PWRBTN_L

PU to PP3V3_S5 |

CALPE SYS_BTN → PCH PWRBTN_L

PM_SLP_S5_L

PCH → H9M (eSPI and pin)

PM_SLP_S4_L

PCH → H9M (eSPI and pin)

PP1V8_S3

Calpe Buck3 SW4 → Memory VDD1

PVDDQ_EN

Calpe GPIO11 → U8100 enable

PP1V1_S3

U8100 → CPU VDDQ, Memory VDD2

P1V1_S3_PGOOD

PU to PVDDQ_EN |

U8100 PGOOD → U8150 enable

PP0V6_S3

U8150 → Memory VDDQ

PVDDQ_PGOOD

U8150 PGOOD → Calpe GPIO12

PM_SLP_S3_L

PCH → H9M (eSPI and pin)

PP1V05_S0

Calpe Buck8 SW2 → CPU VCCST, VCCPLL

CPU_VCCST_PWRGD

Level shifted from ALL_SYS_PWRGD, PU to

PP1V05_S0 | U1920 → CPU VCCST_PWRGD

PVCCPLLOC_EN

Calpe GPIO18 → U8245

P1V1_S0SW_FET_EN

PVCCPLLOC_EN AND CPU_C10_GATE_L → U8240

PP1V1_S0SW

U8240 → CPU VCCPLL_OC

PP1V_S5SW

Calpe HIO_SW → CPU VCCSTG

PP1V8_S0_CPU_OPVR

Calpe Buck3_SW5 → PCH VCC1P8_OPVR

CPU_OPVR_SLP_S3_L

PU to PP1V8_S0_CPU_OPVR

CPU_OPVR_C10_GATE_L

Level shifted from CPU_C10_GATE_L |

U1940 → PCH SLP_S0_N_1P8V

ALL_SYS_PWRGD

CALPE SYS_ACTIVE → PCH OPVR_EN_1P8

CPU_VR_EN

PCH OPVR_VCCIN_VR_EN_1P8 → IMVP9 VR_ENABLE

CPU_VR_READY

IMVP9 VR_READY → PCH OPVR_VCCIN_VR_RDY_1P8

PPVCC_S0_CPU

IMVP9 → CPU VCCIN

CPUVR_PGOOD

PCH OPVR_PWRGOOD_OUT_1P8V → Calpe GPIO8

SMC_SYSRST_L

H9M SYS_RESET → PCH SYS_RESET

through level shifter

SMC_PCH_PWROK

H9M PCH_PWROK → PCH PCH_PWROK

through level shifter

SMC_PCH_SYS_PWROK

H9M SYS_PWROK → PCH SYS_PWROK

through level shifter

PLT_RST_L

PCH PLTRST_L → System

You might also like

- Sequence Starup Macbook A1278Document23 pagesSequence Starup Macbook A1278Untung AriadiNo ratings yet

- Sequence Starup Macbook A1278Document23 pagesSequence Starup Macbook A1278Untung AriadiNo ratings yet

- Stm32H743IIK PinmapDocument3 pagesStm32H743IIK PinmapashleyNo ratings yet

- 09-01-2023 Ajuan DC E2EDocument257 pages09-01-2023 Ajuan DC E2EIlham Kenyut ANo ratings yet

- 8-Bit Single-Chip Microcomputer With Ad Converter D78c10agq Nec Datasheet PDFDocument66 pages8-Bit Single-Chip Microcomputer With Ad Converter D78c10agq Nec Datasheet PDFAnonymous qWeFIfN90No ratings yet

- P5G41-M LX: Troubleshooting GuideDocument4 pagesP5G41-M LX: Troubleshooting GuideRodney RibeiroNo ratings yet

- Addition - Dilution NSN HelperDocument27 pagesAddition - Dilution NSN HelperZeeshan AzizNo ratings yet

- STM32F4Discovery SchematicDocument6 pagesSTM32F4Discovery SchematicAda CsabaNo ratings yet

- DS-016 Pixhawk Autopilot V6u StandardDocument12 pagesDS-016 Pixhawk Autopilot V6u Standardali almorsedNo ratings yet

- Power PC-Data SheetDocument10 pagesPower PC-Data SheetVenkat RaoNo ratings yet

- Beaglebone Black (BBB) BoardDocument32 pagesBeaglebone Black (BBB) BoardSai TulangekarNo ratings yet

- Frdm-kl25z Pinouts (Rev 1.0)Document5 pagesFrdm-kl25z Pinouts (Rev 1.0)huiuhiuhuiNo ratings yet

- Giga Luoc Do Kich NguonDocument2 pagesGiga Luoc Do Kich NguonNguyễn Văn TặngNo ratings yet

- Giga Luoc Do Kich NguonDocument2 pagesGiga Luoc Do Kich NguonĐiện LươngNo ratings yet

- DSASW00200699Document6 pagesDSASW00200699Иван ИвановNo ratings yet

- Equipment SummaryDocument1 pageEquipment SummaryJohn Philip BuntalesNo ratings yet

- Cuav - X7 - Pinout 2020 4 7Document9 pagesCuav - X7 - Pinout 2020 4 7guidoNo ratings yet

- Tagname Ptdesc Pnttype NodenummodnumslotnumDocument3 pagesTagname Ptdesc Pnttype NodenummodnumslotnumMuna AkheelNo ratings yet

- Access Point y Accesorios: AIR-AP1131AG-A-K9 AIR-LAP1142N-A-K9Document6 pagesAccess Point y Accesorios: AIR-AP1131AG-A-K9 AIR-LAP1142N-A-K9AnibalNo ratings yet

- P5kpl-Am Se PDFDocument4 pagesP5kpl-Am Se PDFMariusz KaźmierczakNo ratings yet

- Asus Eee PC p900 PDFDocument47 pagesAsus Eee PC p900 PDFRamdas KambleNo ratings yet

- ASUS P900 Rev1.2G PDFDocument47 pagesASUS P900 Rev1.2G PDFprocesator_26No ratings yet

- LOOPS-target Date 01-12-23 (Rev-28-11)Document8 pagesLOOPS-target Date 01-12-23 (Rev-28-11)Carlos MartinezNo ratings yet

- (сервискомп-анна.рф) Asus P8H61-M LX Repair Guide PDFDocument6 pages(сервискомп-анна.рф) Asus P8H61-M LX Repair Guide PDFViktor SkvortsovNo ratings yet

- PP Aaa PP1 164Document57 pagesPP Aaa PP1 164Rabah AmidiNo ratings yet

- Asus N750JV (Repair Guide)Document7 pagesAsus N750JV (Repair Guide)Jaricsa BernaolaNo ratings yet

- DTCList EMRL1 SecondaryECU ENDocument5 pagesDTCList EMRL1 SecondaryECU ENKalin GalabovNo ratings yet

- F16C Checklist July132021Document114 pagesF16C Checklist July132021ZDENDA EDITZNo ratings yet

- Rome2 Apollo Power On SequenceDocument14 pagesRome2 Apollo Power On SequenceMabrouk Med AliNo ratings yet

- Kim Uno Rev1 SchematicDocument1 pageKim Uno Rev1 SchematicweaponNo ratings yet

- QD SubttciDocument1 pageQD SubttciHRDNo ratings yet

- SAP-TCodes Module PP-ENDocument105 pagesSAP-TCodes Module PP-ENMariya100% (1)

- Block Diagram: P8H61-M LX3 R2.1 Repair GuideDocument6 pagesBlock Diagram: P8H61-M LX3 R2.1 Repair GuideAdi copycenterNo ratings yet

- PP Aaa PP1 132Document20 pagesPP Aaa PP1 132Rabah Amidi100% (1)

- List of Chips To BuyDocument3 pagesList of Chips To BuygumilarjisutiawanNo ratings yet

- Block Diagram: B85M-E/DASH Repair GuideDocument6 pagesBlock Diagram: B85M-E/DASH Repair GuideLuiz Fernando Cavalcante GonçalvesNo ratings yet

- Aural WarningDocument1 pageAural WarningDarul KhuthuniNo ratings yet

- Um12pd1 Miscellaneous PartsDocument2 pagesUm12pd1 Miscellaneous PartsBurik8No ratings yet

- Absences For Organizational ChangeDocument2 pagesAbsences For Organizational ChangemlegsNo ratings yet

- uPD16306A uPD16306A: IC801 IC801Document4 pagesuPD16306A uPD16306A: IC801 IC801aristeusheringNo ratings yet

- L430 FRU List MT 2465, 2466, 2468: PN CRU ID DescriptionDocument11 pagesL430 FRU List MT 2465, 2466, 2468: PN CRU ID DescriptioningeverdavidNo ratings yet

- ESP32 Devkit Pinout - 19Document1 pageESP32 Devkit Pinout - 19Humberto Roddhuer100% (1)

- GECDMDocument6 pagesGECDMEmanuel SantosNo ratings yet

- Installation CDVRDocument12 pagesInstallation CDVRCandiano PopescuNo ratings yet

- 906, 908, 916, 918, 919, 920 Installation: Mushroom Cap Switch ConnectionDocument2 pages906, 908, 916, 918, 919, 920 Installation: Mushroom Cap Switch ConnectionAimee chaconNo ratings yet

- Exp 4Document5 pagesExp 4Karan PatelNo ratings yet

- Asus N550LF Repair GuideDocument7 pagesAsus N550LF Repair GuidememepiNo ratings yet

- Bom Rev2Document2 pagesBom Rev2gautamkr15No ratings yet

- Asus N550LF Repair GuideDocument7 pagesAsus N550LF Repair GuideFrancescoNo ratings yet

- Computer Communication and Networks Lab DADocument4 pagesComputer Communication and Networks Lab DAAahan JainNo ratings yet

- LG R410 Quanta QL6 Rev 4A SCHDocument39 pagesLG R410 Quanta QL6 Rev 4A SCHleethax0No ratings yet

- Nice ROBUS RB600 P RB1000 P RB500HS ManualDocument36 pagesNice ROBUS RB600 P RB1000 P RB500HS ManualGavin TranterNo ratings yet

- Duties of A System AdministratorDocument3 pagesDuties of A System AdministratorVijaya LakshmiNo ratings yet

- Computer Evolution and Performance: Julius BancudDocument39 pagesComputer Evolution and Performance: Julius BancudRed StreakNo ratings yet

- Lesson 3 ITS 204 Reviewer All About MotherboardsDocument5 pagesLesson 3 ITS 204 Reviewer All About MotherboardsEzzer DaveNo ratings yet

- General Visual Perception ProcessorDocument14 pagesGeneral Visual Perception ProcessorRishi NadhNo ratings yet

- Computer-Architecture Q&ADocument37 pagesComputer-Architecture Q&AArun Vijay100% (2)

- TOFU - Toggle Count Analysis Made Simple: Michael Gruber and Georg SiglDocument10 pagesTOFU - Toggle Count Analysis Made Simple: Michael Gruber and Georg Siglrajat835No ratings yet

- Computer Organization: Course Web SiteDocument32 pagesComputer Organization: Course Web Siterajak1No ratings yet

- Anet A8 ManualDocument19 pagesAnet A8 ManualAmar NathNo ratings yet

- Software S2 2014 2015Document34 pagesSoftware S2 2014 2015bobolalNo ratings yet

- Intel 8085 Microprocessor ArchitectureDocument10 pagesIntel 8085 Microprocessor ArchitectureemdzeiiNo ratings yet

- สำเนาของ สำเนาของ Arduino Uno R3 Driver Windows 10 64 Bit Download - ColaboratoryDocument5 pagesสำเนาของ สำเนาของ Arduino Uno R3 Driver Windows 10 64 Bit Download - Colaboratorywtaepattana pokpradidNo ratings yet

- Oracle Exadata Hardware Installation Software Configuration Online Assessment 2021Document19 pagesOracle Exadata Hardware Installation Software Configuration Online Assessment 2021abidouNo ratings yet

- UntitledDocument12 pagesUntitledHubert Reynaldo Chang EscalanteNo ratings yet

- Solidworks 2019: Visualization & VR GuideDocument12 pagesSolidworks 2019: Visualization & VR GuideAhmad SafrizalNo ratings yet

- Operating SystemDocument103 pagesOperating SystemYUVRAJ WAGH100% (1)

- 4100U Service Parts ListDocument29 pages4100U Service Parts ListAnderson Willian MendesNo ratings yet

- Supported Device List - 20210527Document1 pageSupported Device List - 20210527Karl LabagalaNo ratings yet

- BizHub C258 Series Best Practices TroubleshootingDocument55 pagesBizHub C258 Series Best Practices Troubleshootingguillermo_hernand_46No ratings yet

- Beep Codes: Beep Codes Beep Code Description Beep Codes Beep Code DescriptionDocument2 pagesBeep Codes: Beep Codes Beep Code Description Beep Codes Beep Code DescriptionAntonio Haber LamarNo ratings yet

- Computer System Hardware LabDocument104 pagesComputer System Hardware LabSoumik HazraNo ratings yet

- Dell Alienware 13 R2 LA-C901P Rev1.0 (A00) PDFDocument63 pagesDell Alienware 13 R2 LA-C901P Rev1.0 (A00) PDFdanilo chinchillaNo ratings yet

- Siemens - NanoboxPC-IPC227E - ENDocument3 pagesSiemens - NanoboxPC-IPC227E - ENCarolineNo ratings yet

- ChatLog Bizbond IT LTD 2020 - 09 - 01 02 - 25Document20 pagesChatLog Bizbond IT LTD 2020 - 09 - 01 02 - 25Taufiq AlahiNo ratings yet

- G41T R3 - Manual A PDFDocument64 pagesG41T R3 - Manual A PDFinging101285No ratings yet

- DP Videos AMD-NT 15123 DriversDocument690 pagesDP Videos AMD-NT 15123 Driversviki mikiNo ratings yet

- A Comparison of Software and Hardware Techniques For x86 VirtualizationDocument18 pagesA Comparison of Software and Hardware Techniques For x86 VirtualizationAhmed HamoudaNo ratings yet

- What Is Inside A PC SystemDocument1 pageWhat Is Inside A PC SystemáNo ratings yet

- Delivers Tomorrow: Purchase Order (OptionalDocument2 pagesDelivers Tomorrow: Purchase Order (OptionalLucas ANo ratings yet

- File 1326132307Document1 pageFile 1326132307Rodrigo KrammNo ratings yet