Professional Documents

Culture Documents

CSSE 4010 Prac2 Marking Sheet

Uploaded by

quintqasOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

CSSE 4010 Prac2 Marking Sheet

Uploaded by

quintqasCopyright:

Available Formats

CSSE4010 – Digital System Design

Marking Criteria

The pracs in this course are marked to a specific criteria. This means you must demonstrate sufficient

understanding and functionality and the marking will be done according to the rubric provided below.

You must attempt each prac (i.e., a report must be received by the due date) to pass the course. All

designs VHDL code used must be your own work. You are NOT permitted to use other VHDL code

sources, unless directed to. Plagiarism is unacceptable and please read and understand the School

Statement on Misconduct, available on the ITEE website at: http://www.itee.uq.edu.au/itee-student-

misconduct-including-plagiarism . To avoid problems make sure that your VHDL code is the product

of your work and do not let anybody else 'reuse' your code.

Marks Criteria

Simulation

0 Simulation not attempted or does not work

1 Simulation partially works for one or both designs (waveforms only)

2 Simulation fully works (no self checking) for only one design

3 Simulation fully works (self checking) for only one design

4 Simulation fully works (self checking) for both designs

Report

0 No evidence of content or work

1 Some content, insufficient explanation of circuit

2 Reasonable content, some explanation of circuit

3 Good content, reasonable explanation of circuit

4 Excellent content, good explanation of circuit

Oral assessment

0 No knowledge of the design

1 Very little knowledge of the design

2 Reasonable knowledge of the design

3 Good knowledge of the design.

4 Excellent knowledge of the design.

Total (12): Marker Initials:

Date:

Prac 2 – Registers and Combinational Logic in VHDL

You might also like

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Digital System Desgin Prac 4Document3 pagesDigital System Desgin Prac 4quintqasNo ratings yet

- Prac 2 - Registers and Combinational Logic in VHDL: Design TaskDocument4 pagesPrac 2 - Registers and Combinational Logic in VHDL: Design TaskquintqasNo ratings yet

- Digital System Desgin Tutorial 5Document1 pageDigital System Desgin Tutorial 5quintqasNo ratings yet

- Intelligent Neural Network Based STLF: January 2009Document12 pagesIntelligent Neural Network Based STLF: January 2009quintqasNo ratings yet

- Between Impunity and Accountability EnglishDocument28 pagesBetween Impunity and Accountability EnglishquintqasNo ratings yet

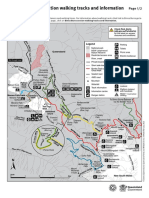

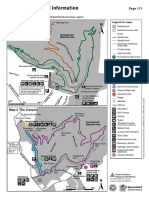

- Lamington Green Mts MapDocument2 pagesLamington Green Mts MapquintqasNo ratings yet

- ECON2070 S1 Activities TimelineDocument1 pageECON2070 S1 Activities TimelinequintqasNo ratings yet

- Digital System Desgin Course OutlineDocument1 pageDigital System Desgin Course Outlinequintqas100% (1)

- Tamborine Walking Track MapDocument1 pageTamborine Walking Track MapquintqasNo ratings yet

- Flight Details: Travel History DeclarationDocument6 pagesFlight Details: Travel History DeclarationquintqasNo ratings yet

- Public Administration Review - 2020 - Gaynor - Social Vulnerability and Equity The Disproportionate Impact of COVID 19Document7 pagesPublic Administration Review - 2020 - Gaynor - Social Vulnerability and Equity The Disproportionate Impact of COVID 19quintqasNo ratings yet

- Gearbox Assembly PDFDocument1 pageGearbox Assembly PDFquintqasNo ratings yet

- Vivado Design FlowDocument39 pagesVivado Design FlowquintqasNo ratings yet

- Springbrook Inset MapsDocument3 pagesSpringbrook Inset MapsquintqasNo ratings yet

- Lamington Binna Burra MapDocument2 pagesLamington Binna Burra MapquintqasNo ratings yet

- Week 5 Tutorial: GoalsDocument2 pagesWeek 5 Tutorial: GoalsquintqasNo ratings yet

- Prac 2 - Registers and Combinational Logic in VHDL: Design TaskDocument4 pagesPrac 2 - Registers and Combinational Logic in VHDL: Design TaskquintqasNo ratings yet

- State Machine IntroductionDocument5 pagesState Machine IntroductionpoojaNo ratings yet

- Csse1001 NotesDocument184 pagesCsse1001 NotesquintqasNo ratings yet

- Eng Us PDFDocument54 pagesEng Us PDFquintqasNo ratings yet

- 10 Predicate LogicDocument42 pages10 Predicate LogicSmitesh DamdooNo ratings yet

- Woodside Sustainability Dev Fact Sheet Eng Final Web PagesDocument4 pagesWoodside Sustainability Dev Fact Sheet Eng Final Web PagesquintqasNo ratings yet

- Waste To EnergyDocument20 pagesWaste To EnergyquintqasNo ratings yet

- Health spending trends in AfghanistanDocument2 pagesHealth spending trends in AfghanistanquintqasNo ratings yet

- Sustainable Development Report 2018Document48 pagesSustainable Development Report 2018quintqasNo ratings yet

- Building PowerlinesDocument28 pagesBuilding PowerlinesquintqasNo ratings yet

- Sustainability 10 02022 PDFDocument18 pagesSustainability 10 02022 PDFquintqas0% (1)

- Summer 2018 08. Monopoly and Imperfect Competition (2 Slides Per Page) PDFDocument26 pagesSummer 2018 08. Monopoly and Imperfect Competition (2 Slides Per Page) PDFquintqasNo ratings yet

- Thesustainabledevelopmentgoalsreport2018 PDFDocument40 pagesThesustainabledevelopmentgoalsreport2018 PDFboviao100% (1)