Professional Documents

Culture Documents

Prac 2 - Registers and Combinational Logic in VHDL: Design Task

Uploaded by

quintqasOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Prac 2 - Registers and Combinational Logic in VHDL: Design Task

Uploaded by

quintqasCopyright:

Available Formats

CSSE4010 – Digital System Design

Prac 2 – Registers and Combinational Logic in VHDL

Note: Things take time. So be prepared with the lab activity, do all the preliminary designs

and as much implementation as you can beforehand.

Design Task

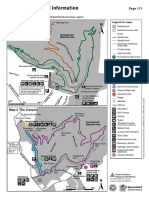

Design and simulate a 4-digit combinational lock. The system has the following inputs and outputs

(not drawn using standard schematic symbols) and the operation is described as bellow.

Digit A (4 bits)

Lock

Digit B (4 bits)

Button 1 Unlock

Button 2 Four seven segment display output

Reset

The 4 hex digits are entered to the system, two digits at a time (using Digit A and Digit B 4-bit inputs,

possibly coming from slide switches) with Button 1 and Button 2 inputs to trigger the input processing.

After reset, two hexadecimal digits are entered into the inputs Digit A and Digit B. The first button

(Button 1) is pressed and the two digits are entered to the system and show up as the first two digits

on the seven segment displays (Digit 1 and Digit 2). The user changes the Digit A and Digit B inputs to

the next two digits of the 4-digit code. The user then presses the 2nd button (Button 2) and the next

two digits are entered to the system and displayed on the remaining two seven segment displays (Digit

3 and Digit 4). If the 4-digit code is correct at this stage, the lock opens, and indicated as the Lock

output being 0 and Unlock output being 1. If the user changes the slide switches for Digit A and Digit

B inputs without pressing the Buttons, once the lock is open, the lock will remain open (i.e., the system

is not responsive to the changes of slide switches unless the values are entered by pressing the two

Buttons). When the reset button is pushed the display is cleared to 'AAAA' and the lock is locked once

again (i.e., Lock is high and Unlock is low). The correct code to open the lock is the last four digits of

your student number.

Complete this specification as you see fit and state any assumptions you make. Your VHDL must use

'data flow' or 'behavioural' description styles to implement the locking/unlocking function. For storing

the inputs, you will need sequential circuit elements. A simple approach would be to clock the 8-bit

input value into Registers using the two push buttons as two separate clocks. An example VHDL

implementation of a register is provided to you and you may modify this file accordingly or use your

own. As there are two clocks this is an asynchronous solution. A fully synchronous solution implies that

all storage elements update on a single global clock edge and in this case the push buttons can be

used as clock-enable signals. You will also need a hex-to-seven-segment decoder to convert the

hexadecimal numbers to display on seven segment display outputs.

VHDL Implementation

Implement both the synchronous and asynchronous solutions of the combinational lock as VHDL

designs. Create a source files for both implementations: locktop_sync.vhd and locktop_async.vhd file

Prac 2 – Registers and Combinational Logic in VHDL Page 1

CSSE4010 – Digital System Design

and test them for correct functionality using simulation. The locktop_sync/async files must use a

structural design approach to connect various modules you need. Create a source file lock_sync.vhd

or lock_async.vhd that implements the combinational lock functionality for synchronous and

asynchronous designs, respectively. The lock_sync/async file must use dataflow and behavioural

design approaches. You may create other VHDL files, as needed. An example of a register is:

reg_simple.vhd which is provided for you to look at and use (on BB), if you wish to do so (this file will

have added functionality which you might not need). You will also need to create a hex to seven

segment decoder module.

Refer to the textbook Roth: Chapter 1 and Chapter 2, and CSSE4010 lectures. For more detailed

references read the Vivado synthesis guide manual (on blackboard) regarding how to describe

combinational logic and registers you need in your design. Structural (or netlist of components) is not

a valid solution (for lock_sync/async files).

Simulation

Create a test bed to simulate your combinational lock for both synchronous and asynchronous

designs. The testbed should import your locktop_sync/async.vhds file as a component. The testbed

should use the following test pattern as the 8 slide switch inputs, shown below (24 bit pattern).

<8 digit student ID ><8 digit student ID XOR 0x11111111><8 digit student ID XOR 0x22222222 >

The test bed should cycle through all bits of the slide switch test pattern, left shifting the pattern by 2

digits (8bit shift), each cycle.

e.g. Test pattern is 0x12345678032547693016745A for student ID of: 12345678

cycle 0) Test pattern given to the test = 0x12

cycle 1) Test pattern given to the test = 0x34

cycle 2) Test pattern given to the test = 0x56

After each test pattern is set as the inputs, the testbed must generate a signal to simulate the push

button(s) being pressed. Create a self-checking testbed, that should display a message, when the lock

has been opened. Experiment with the waveform viewer to group signals together and display

numeric values, rather than straight binary signals (e.g. for seven segment display). You must be able

to show the waveforms for key functionality, e.g. when unlock occurs. You should be able to run the

entire simulation and then zoom in on the key sections.

Hints

Much like in regular programming, abstraction can be a useful tool in VHDL to simplify design and

production. Writing a single, complex behavioural component that handles all inputs and outputs can

be complex. However, writing a series of smaller components, which you can individually check and

can connect together structurally helps you to break the program down into smaller, more

manageable sub-systems. This is known as a top-down design approach.

This is where a circuit diagram is helpful. By drawing a diagram that divides the top-level circuit up

into distinct sections, you can break down the complexity of the whole design across a number of

simpler sections. If you can design the circuit using standard circuit elements such as a multiplexer, an

adder, a register, etc., and you have circuit that shows the structural layout of these elements, you

need only design the elements in VHDL and then connect them structurally, and you have a testable

circuit.

Prac 2 – Registers and Combinational Logic in VHDL Page 2

CSSE4010 – Digital System Design

Report Content and Format

A typeset PDF report must be submitted by the due date with the following content:

• Introduction stating the problem description, any assumptions, and design objectives

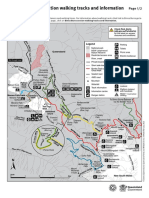

• Design description including a block diagram explaining the complete design. Block diagrams

should be drawn using standard symbols for inputs/outputs, signals and busses as shown

below.

• Detailed simulation results showing the key scenarios to prove that the design is functionally

correct and delivers the expected output.

• Register transfer level (RTL) schematic of the design obtained from Vivado tools (you should

try to back-annotate the RTL schematic and try to identify the basic sub-systems/blocks in

your design)

• Synthesis results including FPGA resource consumption

• Conclusion – a reflection of what you’ve achieved in this exercise, problems (if you had any)

and potential improvements to your design (if any)

• References (if any)

• You must have the marking sheet on the next page as the last page of your report and your

marks will be indicated on this sheet (this has also been uploaded on BB as a single pdf file

so that you can append this to your report as the last page)

Prac 2 – Registers and Combinational Logic in VHDL Page 3

CSSE4010 – Digital System Design

Marking Criteria

The pracs in this course are marked to a specific criteria. This means you must demonstrate sufficient

understanding and functionality and the marking will be done according to the rubric provided below.

You must attempt each prac (i.e., a report must be received by the due date) to pass the course. All

designs VHDL code used must be your own work. You are NOT permitted to use other VHDL code

sources, unless directed to. Plagiarism is unacceptable and please read and understand the School

Statement on Misconduct, available on the ITEE website at: http://www.itee.uq.edu.au/itee-student-

misconduct-including-plagiarism . To avoid problems make sure that your VHDL code is the product

of your work and do not let anybody else 'reuse' your code.

Marks Criteria

Simulation

0 Simulation not attempted or does not work

1 Simulation partially works for one or both designs (waveforms only)

2 Simulation fully works (no self checking) for only one design

3 Simulation fully works (self checking) for only one design

4 Simulation fully works (self checking) for both designs

Report

0 No evidence of content or work

1 Some content, insufficient explanation of circuit

2 Reasonable content, some explanation of circuit

3 Good content, reasonable explanation of circuit

4 Excellent content, good explanation of circuit

Oral assessment

0 No knowledge of the design

1 Very little knowledge of the design

2 Reasonable knowledge of the design

3 Good knowledge of the design.

4 Excellent knowledge of the design.

Total (12): Marker Initials:

Date:

Prac 2 – Registers and Combinational Logic in VHDL Page 4

You might also like

- Digital System Desgin Prac 4Document3 pagesDigital System Desgin Prac 4quintqasNo ratings yet

- final DDCOLab manual (1)Document31 pagesfinal DDCOLab manual (1)susheela NatarajuNo ratings yet

- Introduction to VHDL Lab 2Document8 pagesIntroduction to VHDL Lab 2Jawath BinaNo ratings yet

- Digital Design AssignmentDocument20 pagesDigital Design Assignmentidiot930902No ratings yet

- FPGA Lab Journal: Verilog Experiments on Comparators and AddersDocument98 pagesFPGA Lab Journal: Verilog Experiments on Comparators and AddersAFTAB ALINo ratings yet

- CE 435 Lab 1: 4-Bit Gray Code Counter Simulation and ImplementationDocument14 pagesCE 435 Lab 1: 4-Bit Gray Code Counter Simulation and ImplementationThanos GkanNo ratings yet

- Alu 32 BitDocument6 pagesAlu 32 Bitsachin_bhingareNo ratings yet

- Project1 Hardware Design With Verilog: Submission ModalitiesDocument5 pagesProject1 Hardware Design With Verilog: Submission ModalitiesZulqarnain KhanNo ratings yet

- Lab 4Document5 pagesLab 402chng.jiadeNo ratings yet

- ECE342 Lab 1Document4 pagesECE342 Lab 1kinglbfNo ratings yet

- Digital Design BEC30503 Instruction Sheet: Lab No. Lab Title Semester Session Lab Durations Independent StudiesDocument30 pagesDigital Design BEC30503 Instruction Sheet: Lab No. Lab Title Semester Session Lab Durations Independent StudiesKarti ViveygenNo ratings yet

- Lab 5Document3 pagesLab 5Arun MehraNo ratings yet

- Introduction to VHDL (IntroDocument8 pagesIntroduction to VHDL (IntroAbdul RajakNo ratings yet

- ENGR 3410: MP #1 MIPS 32-Bit Register File: Due: Before Class, 19 October 2010Document8 pagesENGR 3410: MP #1 MIPS 32-Bit Register File: Due: Before Class, 19 October 2010Happy SmileNo ratings yet

- VLSI Lab Manual Student Copy 21-22 04.10.21Document76 pagesVLSI Lab Manual Student Copy 21-22 04.10.21RanjithNo ratings yet

- BEC7L1 - Digital Cmos Vlsi-LabDocument66 pagesBEC7L1 - Digital Cmos Vlsi-LabRamkumardevendiranDevenNo ratings yet

- ModelSim TutorialDocument6 pagesModelSim TutorialyadavvlsiNo ratings yet

- Experiments of HDL Programming Lab: Numbers and Display With ISE Design Suite 14.7 ExperimentDocument13 pagesExperiments of HDL Programming Lab: Numbers and Display With ISE Design Suite 14.7 ExperimentharithNo ratings yet

- Vlsi Lab Manual 2013Document64 pagesVlsi Lab Manual 2013harish33330% (1)

- SystemC Primer 1 - 1Document79 pagesSystemC Primer 1 - 1Nguyễn Hữu TuyếnNo ratings yet

- Lab 4aDocument12 pagesLab 4awajeehaadeel57No ratings yet

- Introduction to Verilog HDL for Digital DesignDocument193 pagesIntroduction to Verilog HDL for Digital Designmhòa_43No ratings yet

- EGR244 Digital Logic Design Lab Vending Machine ProjectDocument4 pagesEGR244 Digital Logic Design Lab Vending Machine Projectosama mahyoubNo ratings yet

- CSE20221 Keyboard Interface ProjectDocument2 pagesCSE20221 Keyboard Interface ProjectpranjalNo ratings yet

- VHDL PDFDocument112 pagesVHDL PDFvivek patelNo ratings yet

- AssignmentDocument9 pagesAssignmentSumit Kumar YadavNo ratings yet

- CSE369 Lab1&2 Wi22Document5 pagesCSE369 Lab1&2 Wi22Deniz Melek TürkNo ratings yet

- ECE238L Lab 0 - Design and Simulate Logic GatesDocument37 pagesECE238L Lab 0 - Design and Simulate Logic GatesazonegrpzNo ratings yet

- ECE 353 VHDL and Lab Tools TutorialDocument19 pagesECE 353 VHDL and Lab Tools TutorialGiovanni OrsariNo ratings yet

- Xilinx WorkbookDocument94 pagesXilinx WorkbookdmctekNo ratings yet

- ECNG3016 Practical 3Document12 pagesECNG3016 Practical 3Marlon BoucaudNo ratings yet

- LAB#1Document5 pagesLAB#1Unsa Jan Abdul QayyumNo ratings yet

- Lab4 - Tasks, Functions, and TestbenchDocument6 pagesLab4 - Tasks, Functions, and Testbenchwert1a2No ratings yet

- Lab 4 Using On-Board Clock On The Nexys4 and Designing A 4-Bit CounterDocument14 pagesLab 4 Using On-Board Clock On The Nexys4 and Designing A 4-Bit CounterSherry Iran Farda TV CoolNo ratings yet

- Introduction to VHDL LabDocument3 pagesIntroduction to VHDL LabJose Alberto AnguloNo ratings yet

- Lecture01 s07Document41 pagesLecture01 s07Ali AhmadNo ratings yet

- EE 2174 Lab 9 NewDocument6 pagesEE 2174 Lab 9 NewnotdrphilNo ratings yet

- FPGA-Based-System-Design LAB JOURNAL 2Document56 pagesFPGA-Based-System-Design LAB JOURNAL 2talha42103No ratings yet

- Lab 1 Spring 13Document3 pagesLab 1 Spring 13Kumaraguru RauNo ratings yet

- Lab 1Document12 pagesLab 1roopa_kothapalliNo ratings yet

- Xilinx Project Navigator HDL Lab ManualDocument72 pagesXilinx Project Navigator HDL Lab Manualshubham100% (1)

- ISE 9.2i Software Basics: AND, OR, XOR Logic GatesDocument7 pagesISE 9.2i Software Basics: AND, OR, XOR Logic GatesMohamd barcaNo ratings yet

- Lab 3 (Verilog Implementation of Stop Light Controller)Document7 pagesLab 3 (Verilog Implementation of Stop Light Controller)Muhtasim Fuad JeetNo ratings yet

- You Could Download File D - FF.VDocument133 pagesYou Could Download File D - FF.VPradeep BabuNo ratings yet

- DLD-2014 - Practical BookDocument75 pagesDLD-2014 - Practical BookMuhammad Ishtiaq0% (1)

- Verilog: Advantages of HDL Based Design TechniqueDocument9 pagesVerilog: Advantages of HDL Based Design TechniqueRafiqul IslamNo ratings yet

- Experiment Number 1 Design of An Eight Bit Latch: Xess CorporationDocument10 pagesExperiment Number 1 Design of An Eight Bit Latch: Xess CorporationRuben DiazNo ratings yet

- Advanced Digital Electronics Lab: Comparator DesignDocument3 pagesAdvanced Digital Electronics Lab: Comparator DesignMohamd barcaNo ratings yet

- Xup Workshop 1 by Prasiddha SiwakotiDocument4 pagesXup Workshop 1 by Prasiddha SiwakotiGaihre KrishnaNo ratings yet

- 21CS43 Microcontroller and Embedded SystemsDocument4 pages21CS43 Microcontroller and Embedded SystemsNikhil chandNo ratings yet

- ECNG3016 Practical 4Document7 pagesECNG3016 Practical 4Marlon BoucaudNo ratings yet

- Verilogxl TutDocument68 pagesVerilogxl TutPrak AshNo ratings yet

- Vlsi Lab DocumentDocument18 pagesVlsi Lab DocumentRaffi SkNo ratings yet

- Create Verilog Modules & Test Fixtures TutorialDocument8 pagesCreate Verilog Modules & Test Fixtures TutorialbelpcmNo ratings yet

- System Verilog IntroductionDocument20 pagesSystem Verilog IntroductionRamakrishnaRao SoogooriNo ratings yet

- Intermediate C Programming for the PIC Microcontroller: Simplifying Embedded ProgrammingFrom EverandIntermediate C Programming for the PIC Microcontroller: Simplifying Embedded ProgrammingNo ratings yet

- Assembly Programming:Simple, Short, And Straightforward Way Of Learning Assembly LanguageFrom EverandAssembly Programming:Simple, Short, And Straightforward Way Of Learning Assembly LanguageRating: 5 out of 5 stars5/5 (1)

- Introduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDLFrom EverandIntroduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDLNo ratings yet

- Hacks To Crush Plc Program Fast & Efficiently Everytime... : Coding, Simulating & Testing Programmable Logic Controller With ExamplesFrom EverandHacks To Crush Plc Program Fast & Efficiently Everytime... : Coding, Simulating & Testing Programmable Logic Controller With ExamplesRating: 5 out of 5 stars5/5 (1)

- Python Advanced Programming: The Guide to Learn Python Programming. Reference with Exercises and Samples About Dynamical Programming, Multithreading, Multiprocessing, Debugging, Testing and MoreFrom EverandPython Advanced Programming: The Guide to Learn Python Programming. Reference with Exercises and Samples About Dynamical Programming, Multithreading, Multiprocessing, Debugging, Testing and MoreNo ratings yet

- ECON2070 S1 Activities TimelineDocument1 pageECON2070 S1 Activities TimelinequintqasNo ratings yet

- Digital System Desgin Tutorial 5Document1 pageDigital System Desgin Tutorial 5quintqasNo ratings yet

- Prac 2 - Registers and Combinational Logic in VHDL: Design TaskDocument4 pagesPrac 2 - Registers and Combinational Logic in VHDL: Design TaskquintqasNo ratings yet

- Digital System Desgin Course OutlineDocument1 pageDigital System Desgin Course Outlinequintqas100% (1)

- Springbrook Inset MapsDocument3 pagesSpringbrook Inset MapsquintqasNo ratings yet

- Flight Details: Travel History DeclarationDocument6 pagesFlight Details: Travel History DeclarationquintqasNo ratings yet

- Between Impunity and Accountability EnglishDocument28 pagesBetween Impunity and Accountability EnglishquintqasNo ratings yet

- Intelligent Neural Network Based STLF: January 2009Document12 pagesIntelligent Neural Network Based STLF: January 2009quintqasNo ratings yet

- Health spending trends in AfghanistanDocument2 pagesHealth spending trends in AfghanistanquintqasNo ratings yet

- Lamington Binna Burra MapDocument2 pagesLamington Binna Burra MapquintqasNo ratings yet

- Lamington Green Mts MapDocument2 pagesLamington Green Mts MapquintqasNo ratings yet

- Tamborine Walking Track MapDocument1 pageTamborine Walking Track MapquintqasNo ratings yet

- Public Administration Review - 2020 - Gaynor - Social Vulnerability and Equity The Disproportionate Impact of COVID 19Document7 pagesPublic Administration Review - 2020 - Gaynor - Social Vulnerability and Equity The Disproportionate Impact of COVID 19quintqasNo ratings yet

- CSSE 4010 Prac2 Marking SheetDocument1 pageCSSE 4010 Prac2 Marking SheetquintqasNo ratings yet

- Vivado Design FlowDocument39 pagesVivado Design FlowquintqasNo ratings yet

- Week 5 Tutorial: GoalsDocument2 pagesWeek 5 Tutorial: GoalsquintqasNo ratings yet

- Thesustainabledevelopmentgoalsreport2018 PDFDocument40 pagesThesustainabledevelopmentgoalsreport2018 PDFboviao100% (1)

- Eng Us PDFDocument54 pagesEng Us PDFquintqasNo ratings yet

- State Machine IntroductionDocument5 pagesState Machine IntroductionpoojaNo ratings yet

- Waste To EnergyDocument20 pagesWaste To EnergyquintqasNo ratings yet

- Csse1001 NotesDocument184 pagesCsse1001 NotesquintqasNo ratings yet

- Sustainable Development Report 2018Document48 pagesSustainable Development Report 2018quintqasNo ratings yet

- Gearbox Assembly PDFDocument1 pageGearbox Assembly PDFquintqasNo ratings yet

- 10 Predicate LogicDocument42 pages10 Predicate LogicSmitesh DamdooNo ratings yet

- Woodside Sustainability Dev Fact Sheet Eng Final Web PagesDocument4 pagesWoodside Sustainability Dev Fact Sheet Eng Final Web PagesquintqasNo ratings yet

- Building PowerlinesDocument28 pagesBuilding PowerlinesquintqasNo ratings yet

- Sustainability 10 02022 PDFDocument18 pagesSustainability 10 02022 PDFquintqas0% (1)

- Summer 2018 08. Monopoly and Imperfect Competition (2 Slides Per Page) PDFDocument26 pagesSummer 2018 08. Monopoly and Imperfect Competition (2 Slides Per Page) PDFquintqasNo ratings yet

- Roof Beam Layout - r1Document1 pageRoof Beam Layout - r1Niraj ShindeNo ratings yet

- Online test series analysis reportDocument17 pagesOnline test series analysis reportchetan kapoorNo ratings yet

- Studies of Land Restoration On Spoil Heaps From Brown Coal MiningDocument11 pagesStudies of Land Restoration On Spoil Heaps From Brown Coal MiningeftychidisNo ratings yet

- HistoryDocument20 pagesHistoryAlexandru RomînuNo ratings yet

- Williamstown Cannabis Cultivation PlanDocument48 pagesWilliamstown Cannabis Cultivation PlanOltion JaupajNo ratings yet

- Language in UseDocument1 pageLanguage in UseEvaNo ratings yet

- Cash and Cash EquivalentsDocument2 pagesCash and Cash EquivalentsMary Jullianne Caile SalcedoNo ratings yet

- VariablesDocument11 pagesVariablesKzy ayanNo ratings yet

- Home BMW F11 530D Xdrive Touring Wiring Diagrams and Functional DescriptionDocument1 pageHome BMW F11 530D Xdrive Touring Wiring Diagrams and Functional DescriptionOliver AlfaroNo ratings yet

- Smart Panels - Digitized Switchboards - Blokset Desing and Assembly GuideDocument94 pagesSmart Panels - Digitized Switchboards - Blokset Desing and Assembly Guidelorentz franklinNo ratings yet

- Sajid Bhuiya CVDocument3 pagesSajid Bhuiya CVapi-612088476No ratings yet

- Staff Nurse HallticketDocument2 pagesStaff Nurse HallticketHiking DiaryNo ratings yet

- Fundamentals Deep Learning Activation Functions When To Use ThemDocument15 pagesFundamentals Deep Learning Activation Functions When To Use ThemfaisalNo ratings yet

- Akuntansi Keuangan Lanjutan - Akuntansi Penggabungan UsahaDocument67 pagesAkuntansi Keuangan Lanjutan - Akuntansi Penggabungan UsahachendyNo ratings yet

- Analysis of Security Issues in Web Applications Through Penetration TestingDocument7 pagesAnalysis of Security Issues in Web Applications Through Penetration Testingabdel_lakNo ratings yet

- Uconnect User GuideDocument113 pagesUconnect User GuidetamilarasansrtNo ratings yet

- Hajipur Resume GVVDocument2 pagesHajipur Resume GVVRajnish JhaNo ratings yet

- Delays in Endoscope Reprocessing and The Biofilms WithinDocument12 pagesDelays in Endoscope Reprocessing and The Biofilms WithinHAITHM MURSHEDNo ratings yet

- EEE111_Multisim_ManualDocument14 pagesEEE111_Multisim_ManualSHADOW manNo ratings yet

- LinAlg CompleteDocument331 pagesLinAlg Completes0uizNo ratings yet

- Solution SellingDocument18 pagesSolution Sellingvikramgulati13090% (1)

- Recipe of Medical AirDocument13 pagesRecipe of Medical AirMd. Rokib ChowdhuryNo ratings yet

- ES Model Question Paper With Solution KeyDocument10 pagesES Model Question Paper With Solution Keyvidhya_bineeshNo ratings yet

- LFJ All OrdersDocument195 pagesLFJ All Orderskate jackNo ratings yet

- Max-OT For Dummies - Bodybuilding - Com ForumsDocument21 pagesMax-OT For Dummies - Bodybuilding - Com ForumsPhong QuachNo ratings yet

- Report-Teaching English Ministery of EduDocument21 pagesReport-Teaching English Ministery of EduSohrab KhanNo ratings yet

- Regional Campus The English and Foreign Languages UniversityDocument2 pagesRegional Campus The English and Foreign Languages UniversitySidra KhanNo ratings yet

- Cracking The SQL InterviewDocument52 pagesCracking The SQL InterviewRedouan AFLISSNo ratings yet

- Structurix MEcoDocument12 pagesStructurix MEcoPierpaolo AparoNo ratings yet

- Manhole bill of materialsDocument1 pageManhole bill of materialsjalNo ratings yet