Professional Documents

Culture Documents

ARM Instruction Set - Data Processing - II

Uploaded by

Aniket SubudhiOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

ARM Instruction Set - Data Processing - II

Uploaded by

Aniket SubudhiCopyright:

Available Formats

ARM

Instruction Set

Data Processing II

Peeyush K. P.

Assistant Professor

Department of Electronics and Communication Engineering

Amrita School of Engineering

Coimbatore

Data Processing Instructions 1

Data Processing Instr.

• Bit-wise logical operations.

AND r0, r1, r2 ; r0 = r1 and r2

ORR r0, r1, r2 ; r0 = r1 or r2

EOR r0, r1, r2 ; r0 = r1 xor r2

R1 0xFFFFFFFF

& R2 0x00000000

R0 0x00000000

R1 1111 1111 1111 1111 1111 1111 1111 1111

& R2 0000 0000 0000 0000 0000 0000 0000 0000

R0 0000 0000 0000 0000 0000 0000 0000 0000

Data Processing Instructions 2

Data Processing Instr.

• Bit-wise logical operations

BIC r0, r1, r2 ; r0 = r1 and not r2

R1 1111 1111 1111 1111 1111 1111 1111 1111

R2 0000 0000 0000 0000 0000 0000 0000 0101

& Not R2 1111 1111 1111 1111 1111 1111 1111 1010

R0 1111 1111 1111 1111 1111 1111 1111 1010

R1 0xFFFFFFFF

R2 0x00000005

R0 0xFFFFFFFA

Data Processing Instructions 3

Data Processing Instr.

• Register movement operations.

MOV r0, r2 ; r0 = r2

R2 0x00000002 R2 0000 0000 0000 0000 0000 0000 0000 0010

R0 0x00000002 R0 0000 0000 0000 0000 0000 0000 0000 0010

MVN r0, r2 ; r0 = not r2

R2 0x00000002 R2 0000 0000 0000 0000 0000 0000 0000 0010

R0 0xFFFFFFFD R0 1111 1111 1111 1111 1111 1111 1111 1101

Data Processing Instructions 4

Data Processing Instr.

• Comparison operations

CMP r1, r2 ; Set CC on r1 – r2

R1 0x00000002 R1 0000 0000 0000 0000 0000 0000 0000 0010

- R2 0x00000002 - R2 0000 0000 0000 0000 0000 0000 0000 0010

Z = 1 (No Result) Z = 1 (No Result)

R1 0x00000002 R1 0000 0000 0000 0000 0000 0000 0000 0010

- R2 0x00000003 - R2 0000 0000 0000 0000 0000 0000 0000 0011

N = 1 (No Result) N = 1 (No Result)

CC (Condition Code field of CPSR) – N,Z,C,V

No Result

Data Processing Instructions 5

Data Processing Instr.

• Comparison operations

CMN r1, r2 ; Set CC on r1 + r2

R1 0x00000000 R1 0000 0000 0000 0000 0000 0000 0000 0000

+ R2 0x00000000 - R2 0000 0000 0000 0000 0000 0000 0000 0000

Z=1 Z=1

R1 0xFFFFFFFF R1 1111 1111 1111 1111 1111 1111 1111 1111

+ R1 0x00000001 + R2 0000 0000 0000 0000 0000 0000 0000 0001

C=1 C=1

CC (Condition Code field of CPSR) – N,Z,C,V

No Result

Data Processing Instructions 6

Data Processing Instr.

• Comparison operations

TST r1, r2 ; Set CC on r1 & r2 - Test Single Bit is 1 or 0

R1 1111 1111 1111 1111 1111 1111 1111 1111 R1 0xFFFFFFFF

& R2 0000 0000 0000 0000 0000 0000 0000 0001 & R2 0x00000001

Z = 0 – So the bit is ‘1’ Z=0

R1 1111 1111 1111 1111 1111 1111 1111 1110 R1 0xFFFFFFFE

& R2 0000 0000 0000 0000 0000 0000 0000 0001 & R2 0x00000001

Z = 1 – So the bit is ‘0’ Z=1

CC (Condition Code field of CPSR) – N,Z,C,V

No Result

Data Processing Instructions 7

Data Processing Instr.

• Comparison operations

TEQ r1, r2 ; Set CC on r1 ^ r2 - Test both nos. are equal

R1 1111 1111 1111 1111 1111 1111 1111 1110 R1 0xFFFFFFFE

^ R2 1111 1111 1111 1111 1111 1111 1111 1110 ^ R2 0xFFFFFFFE

Z = 1 – Both Nos are Same Z=1

R1 1111 1111 1111 1111 1111 1111 1111 1110 R1 0xFFFFFFFE

^ R2 1111 1111 1111 1111 1111 1111 1111 1111 & R2 0xFFFFFFFF

Z = 0 – Both Nos are Not Same Z=0

CC (Condition Code field of CPSR) – N,Z,C,V

No Result

Data Processing Instructions 8

Data Processing Instr.

Shifted register operands

• LSL: logical shift left by 0 to 31 places; fill the vacated bits at the least significant

end of the word with zeros.

• LSR: logical shift right by 0 to 32 places; fill the vacated bits at the most significant end

of the word with zeros.

• ASR: arithmetic shift right by 0 to 32 places; fill the vacated bits at the most significant

end of the word with zeros if the source operand was positive, or with

ones if the source operand was negative.

• ROR: rotate right by 0 to 32 places; the bits which fall off the least significant end

of the word are used, in order, to fill the vacated bits at the most significant end

of the word.

• RRX: rotate right extended by 1 place; the vacated bit (bit 31) is filled with the old

value of the C flag and the operand is shifted one place to the right. With

appropriate use of the condition codes (see below) a 33-bit rotate of the operand

and the C flag is performed.

ADD r3, r2, r1, LSL #3 ; r3 := r2 + 8 x r1

Data Processing Instructions 9

Data Processing Instr.

Data Processing Instructions 10

Data Processing Instr.

ADD r0, r1, r1, LSL#1 ; r0 = r1 + r1 << 1

R1 0x00000001

+ R1, LSL #1 0x00000002

R0 0x0000003

R1 0000 0000 0000 0000 0000 0000 0000 0001

+ R1, LSL #1 0000 0000 0000 0000 0000 0000 0000 0010

R0 0000 0000 0000 0000 0000 0000 0000 0011

r0 = r1 + r1 << 1 = r1 + 2 x r1 = 3 x r1

Data Processing Instructions 11

Data Processing Instr.

e.g.:

if (z==1) R1=R2+(R3*4)

compiles to

ADDEQS R1,R2,R3, LSL #2

( SINGLE INSTRUCTION ! )

Data Processing Instructions 12

Thank

You

Data Processing Instructions 13

You might also like

- ARM Instruction Set - Data Processing - IDocument14 pagesARM Instruction Set - Data Processing - IAniket SubudhiNo ratings yet

- 18s Cpe221 Test1 SolutionDocument4 pages18s Cpe221 Test1 SolutionKyra LathonNo ratings yet

- KCS302-01 (Microoperations)Document8 pagesKCS302-01 (Microoperations)dp06vnsNo ratings yet

- Introduction To The ARM Instruction Set:: 1 Module - 2 - FullDocument77 pagesIntroduction To The ARM Instruction Set:: 1 Module - 2 - Fullgagan.kulal619No ratings yet

- Chapter 3: Arm Instruction Set: (Architecture Version: Armv4T)Document32 pagesChapter 3: Arm Instruction Set: (Architecture Version: Armv4T)sunilbhimuNo ratings yet

- 16 32 r0 RTN Program Counter or PC: CPE 221 Test 1 Solution Spring 2019Document4 pages16 32 r0 RTN Program Counter or PC: CPE 221 Test 1 Solution Spring 2019Kyra LathonNo ratings yet

- Lec09 ARMisaDocument101 pagesLec09 ARMisaCristian Daniel BerettaNo ratings yet

- 3.2 Arm Addressing Mode and Instruction SetDocument32 pages3.2 Arm Addressing Mode and Instruction Set727721eumt082No ratings yet

- Arm and Thumb Instruction SetDocument36 pagesArm and Thumb Instruction SetTanay DubeyNo ratings yet

- Lec08 ARMisa 4upDocument24 pagesLec08 ARMisa 4upMuthu LinganNo ratings yet

- 03 - Shift and RotateDocument32 pages03 - Shift and RotateRiver AbodNo ratings yet

- 18f Cpe221 Test1 SolutionDocument4 pages18f Cpe221 Test1 SolutionKyra LathonNo ratings yet

- ARM Instruction Set PDFDocument124 pagesARM Instruction Set PDFhod elnNo ratings yet

- CSEN701 PA2 Solution 27172 29689Document4 pagesCSEN701 PA2 Solution 27172 29689Sreeraj Pisharody100% (1)

- ATtiny13, ATtiny2313, Instruction SetDocument19 pagesATtiny13, ATtiny2313, Instruction SetMihai PaunNo ratings yet

- Cao Unit-3Document14 pagesCao Unit-3Hemanth ZNo ratings yet

- 18s Cpe221 Final SolutionDocument7 pages18s Cpe221 Final SolutionKyra LathonNo ratings yet

- BCS302 (Microoperations)Document8 pagesBCS302 (Microoperations)dp06vnsNo ratings yet

- ARM Instruction Set-With ExamplesDocument101 pagesARM Instruction Set-With ExamplesM ParvathiNo ratings yet

- Module IIIDocument58 pagesModule IIIprathyusha maddalaNo ratings yet

- CHAPTER 3 - 4-Flags and Data Processing Instructions - 3Document85 pagesCHAPTER 3 - 4-Flags and Data Processing Instructions - 3Weehao SiowNo ratings yet

- Asm2 1Document104 pagesAsm2 1EnzoVibioNo ratings yet

- Lecture 2 - ARM Instruction SetDocument42 pagesLecture 2 - ARM Instruction SetSuhaib AbugderaNo ratings yet

- Lecture 7-3Document23 pagesLecture 7-3Pardeep SinglaNo ratings yet

- Lecture 3 - Data TransferDocument12 pagesLecture 3 - Data TransferSuhaib AbugderaNo ratings yet

- Outline: A Simple MicroprocessorDocument14 pagesOutline: A Simple MicroprocessorGide BaniekNo ratings yet

- 19f Cpe221 Test1 SolutionDocument4 pages19f Cpe221 Test1 SolutionKyra LathonNo ratings yet

- Lecture 7: ARM Arithmetic and Bitwise InstructionsDocument34 pagesLecture 7: ARM Arithmetic and Bitwise InstructionsfmsarwarNo ratings yet

- 5 SignedNumbers v22Document18 pages5 SignedNumbers v22vokhacnam2k1No ratings yet

- 02 - Data Processing InstructionsDocument42 pages02 - Data Processing InstructionsRiver AbodNo ratings yet

- Arm Instruction 2 - 001Document26 pagesArm Instruction 2 - 001Ankit SanghviNo ratings yet

- Lab 1 Using Visual Emulator: Download The Emulator Answer To Questions (Q)Document13 pagesLab 1 Using Visual Emulator: Download The Emulator Answer To Questions (Q)Alejandro Sanchez LopezNo ratings yet

- Exercise 8Document4 pagesExercise 8Shriparno deyNo ratings yet

- Data Processing InstructionDocument35 pagesData Processing InstructionDado Fabrička GreškaNo ratings yet

- PI WI 14 CSE30 Lecture 8 PostDocument49 pagesPI WI 14 CSE30 Lecture 8 PostPrasad DaitNo ratings yet

- Module 3 Embeeded Systems Arm Instruction Set & AlpDocument49 pagesModule 3 Embeeded Systems Arm Instruction Set & AlpnpottiNo ratings yet

- Module 2 ExmplesDocument8 pagesModule 2 Exmplesexplainer02222No ratings yet

- 18CS44 Module2Document110 pages18CS44 Module2SharanKumarHuliNo ratings yet

- Arm NotesDocument52 pagesArm NotesSanjana GaneshNo ratings yet

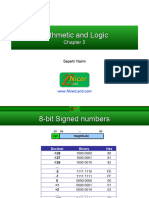

- 3 Arithmetic and Logic v22Document20 pages3 Arithmetic and Logic v22vokhacnam2k1No ratings yet

- Topic 3 ARM Instruction Set Part - 1Document47 pagesTopic 3 ARM Instruction Set Part - 1Dev PatelNo ratings yet

- Arm Instruction SetDocument54 pagesArm Instruction SetSundar VadivelanNo ratings yet

- Exercise 7 - Register Transfer Level (RTL) LogicDocument4 pagesExercise 7 - Register Transfer Level (RTL) LogicdureNo ratings yet

- Code AsemblyDocument87 pagesCode AsemblyHieu Vo QuocNo ratings yet

- MPS - Ch05 - Arithmetic and LogicDocument103 pagesMPS - Ch05 - Arithmetic and LogicPhương Nghi LiênNo ratings yet

- Arm Instruction PrgorammingDocument48 pagesArm Instruction PrgorammingkpraneethkNo ratings yet

- Data Processing - Binay EncodingDocument10 pagesData Processing - Binay EncodingAniket SubudhiNo ratings yet

- Week 2Document70 pagesWeek 2abbazh rakhondeNo ratings yet

- 8051 Assembly LanguageDocument39 pages8051 Assembly LanguagemanvithbNo ratings yet

- Arithmetic InstructionsDocument100 pagesArithmetic InstructionsdhapraNo ratings yet

- Electrical and Computer Engineering Department CPE 221 01 Test 2 Solution Spring 2016Document5 pagesElectrical and Computer Engineering Department CPE 221 01 Test 2 Solution Spring 2016Kyra LathonNo ratings yet

- CPE 221 Final Exam Solution Fall 2018Document6 pagesCPE 221 Final Exam Solution Fall 2018Kyra LathonNo ratings yet

- 8051 InstructionsDocument44 pages8051 InstructionsSoumya Ranjan PandaNo ratings yet

- 8051 Arithmetic InstDocument59 pages8051 Arithmetic InstNilesh DesaiNo ratings yet

- MES - Module 3 AIML RTDocument16 pagesMES - Module 3 AIML RTdaniel007workNo ratings yet

- 2 - Register Transfer and Microoperations - 1Document31 pages2 - Register Transfer and Microoperations - 1shabanaNo ratings yet

- Coen317 Assignment 2 SolutionDocument11 pagesCoen317 Assignment 2 SolutionMegaKingMichaelNo ratings yet

- Chapter - 03: Accessing I/O DevicesDocument42 pagesChapter - 03: Accessing I/O DevicesJoseph JohnNo ratings yet

- CM303Document17 pagesCM303api-3849444No ratings yet

- Unit 1 - MicroprocessorDocument25 pagesUnit 1 - MicroprocessorsenthilNo ratings yet

- 03 - Integrated PROFIBUS InterfaceDocument27 pages03 - Integrated PROFIBUS InterfaceIsai AnguianoNo ratings yet

- Parts of Computer and MeaningDocument2 pagesParts of Computer and MeaningRONA MASCARDONo ratings yet

- MSP430 IntroductionDocument36 pagesMSP430 IntroductionSreekanth PagadapalliNo ratings yet

- 8X300 Reference Manual Oct77 PDFDocument154 pages8X300 Reference Manual Oct77 PDFMathias GutierrezNo ratings yet

- William Stallings Computer Organization and Architecture 8 EditionDocument18 pagesWilliam Stallings Computer Organization and Architecture 8 Editionbree789No ratings yet

- Lab-Volt 32 Bit Microprocessor Instructors GuideDocument265 pagesLab-Volt 32 Bit Microprocessor Instructors GuideGary G. Shaw100% (5)

- DSP Architecture PDFDocument353 pagesDSP Architecture PDFNhật TrungNo ratings yet

- Introduction To Xinu and Kernel Programming: Bina Ramamurthy Bina@Buffalo - EduDocument40 pagesIntroduction To Xinu and Kernel Programming: Bina Ramamurthy Bina@Buffalo - Edudsangria119No ratings yet

- ESP8266 Pinout DiagramsDocument4 pagesESP8266 Pinout DiagramsShubham DesaiNo ratings yet

- SAP (Simple-As-Possible) Computers: 10-1 ArchitectureDocument24 pagesSAP (Simple-As-Possible) Computers: 10-1 ArchitectureAfrahly Afable100% (1)

- AVR Instruction Set Manual DS40002198ADocument162 pagesAVR Instruction Set Manual DS40002198AJuan Sebastian Ospina BautistaNo ratings yet

- RTL Architect™ User GuideDocument149 pagesRTL Architect™ User Guideyang hu100% (1)

- 1.1-1 Computer Hardware-Converted - EditedDocument43 pages1.1-1 Computer Hardware-Converted - EditedKel BloxNo ratings yet

- Oracle EPM 11-1-2 1 Tuning Guide v4Document58 pagesOracle EPM 11-1-2 1 Tuning Guide v4woo28850% (2)

- A Micro-Project Report On ": MotherbordDocument29 pagesA Micro-Project Report On ": MotherbordPratik GadilkarNo ratings yet

- Module1-Eipict Mod1 TGDocument115 pagesModule1-Eipict Mod1 TGKittybabyMaladyNo ratings yet

- NCM 110 Transes 2ND SemDocument27 pagesNCM 110 Transes 2ND SemTherese Melchie SantuyoNo ratings yet

- Sifive E76 Manual 20G1.03.00Document127 pagesSifive E76 Manual 20G1.03.00Ivan Vera de los SantosNo ratings yet

- Unit - 3 8085 Instruction SetDocument15 pagesUnit - 3 8085 Instruction SetMann MehtaNo ratings yet

- Multi-Core Ecu Designing Using Autosar by Deependra MagardeDocument50 pagesMulti-Core Ecu Designing Using Autosar by Deependra MagardeDeependra MagardeNo ratings yet

- Computational Sci. & Engg PDFDocument407 pagesComputational Sci. & Engg PDFVatsalya TandonNo ratings yet

- What Is Polled and Interrupt Modes of Data TransferDocument3 pagesWhat Is Polled and Interrupt Modes of Data TransferSrikrishna JanaNo ratings yet

- UGRD-CS6204A-Computer-Architecture-and-Organization-legit-not-quizzess MidALLDocument17 pagesUGRD-CS6204A-Computer-Architecture-and-Organization-legit-not-quizzess MidALLJitlee Papa100% (1)

- HP Compaq Notebook and Desktop Price ListDocument3 pagesHP Compaq Notebook and Desktop Price ListgcnlNo ratings yet

- Design of High-Confidence Embedded Operating System Based On Artificial Intelligence and Smart ChipsDocument5 pagesDesign of High-Confidence Embedded Operating System Based On Artificial Intelligence and Smart ChipsApeksha Madhukar Asst. Prof. Electrical Engg.No ratings yet

- Execution of InstructionDocument60 pagesExecution of InstructionKr RanjithNo ratings yet

- Computer Architecture and Organization Learning Module 1Document31 pagesComputer Architecture and Organization Learning Module 1Maoi ReyesNo ratings yet