Professional Documents

Culture Documents

Virtex Analog To Digital Converter: Application Note

Uploaded by

Tulasi RadhikaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Virtex Analog To Digital Converter: Application Note

Uploaded by

Tulasi RadhikaCopyright:

Available Formats

APPLICATION

Product NOTE

Obsolete/Under Obsolescence

5

APPLICATION NOTE

0

Virtex Analog to Digital Converter

XAPP155 September 23, 1999 (Version 1.1) 0 13* Application Note: John Logue

Summary

When digital systems are used in real-world applications, it is often necessary to convert an analog voltage level to a binary number. The value of this

number is directly or inversely proportional to the voltage. The analog to digital converter (ADC) described here uses a Virtex FPGA, an analog

comparator, and a few resistors and capacitors. An 8-bit ADC can be implemented in about 16 Virtex CLBs, and a 10-bit ADC requires about 19 CLBs.

Xilinx Family: Virtex Family

Introduction .

ADCref

This ADC uses the Delta-Sigma Digital to Analog converter (DAC)

described in Xilinx Application Note XAPP 154. The DAC is used to Vcco Virtex FPGA

OBUF_F_24

generate a reference voltage for the negative input to the external Comparator Verilog adc R

RP

comparator. The analog signal feeds the positive input of the comparator module

DACout

(see Figure 1). The voltage range of the DAC output is 0V to VCCO, so C

AnalogIn AgtR

that is also the range of analog voltages that may be converted. (If the ADCout [m:0]

analog input voltage is not always between 0V and VCCO, either the DAC ADCsampled

output or the analog signal itself may be biased, attenuated, or amplified

Sample

with external components to achieve the desired voltage range compat-

ibility.)

Fstm [n:0]

The analog level is determined by performing a serial binary voltage

search, starting at the middle of the voltage range. For each complete Reset

sample, only the upper bit of the DAC input is initially set, which drives

the reference voltage to midrange. Depending on the output of the

comparator, the upper bit is then cleared or it remains set, and the next 9905100102

most significant bit of the DAC input is set. This process continues for

Figure 1: ADC Symbol, RC Filter, and Comparator

each bit of the DAC input.

The DAC is one bit wider than the ADC output. This is required in order Table 1: ADC Interface Signals

for the lowest numbered bit of the ADC output to be significant. When all

of the bits have been sampled, the upper bits of the register feeding the Signal Direction Description

DAC is transferred to the ADC output register.

Because of the serial nature of both the DAC and the analog sampling DACout Output Pulse string that drives the external

process, this ADC is useful only on signals that are changing at a fairly low pass filter. See DAC application

low rate. A typical high-precision application for this ADC would be note for more information.

monitoring a physical metric, such as ambient air temperature or water (XAPP154)

pressure. It can also be used for applications with lower precision at a

ADCout[m:0] Output ADC output bus.

higher sampling rate, such as utility voice recording (for example, a

telephone answering machine). ADCsampled Output Clock enable for the ADCout regis-

If the analog input voltage changes during the sampling process, it ter. It indicates that ADCout will

effectively causes the sample point to randomly move. This adds a noise change on the next positive Clk

component that becomes larger as the input frequency increases. For edge, if AnalogIn has changed.

many applications, the strength of the additional noise will be so low that

it will be acceptable. This noise component can be removed with an Sample Output Sample/Hold. Signal is True when

external sample and hold circuit for the analog input signal. ADC is sampling upper bit of each

word. Can drive an external Sample

Figure 1 shows how the ADC is connected to the other components. As and Hold circuit.

described in the DAC application note, a 24 mA LVTTL output buffer is

normally used to drive the RC filter. Most comparators have AgtR Input Analog greater than Reference. This

uncommitted collector/drain outputs, so RP is usually needed. is the output of external comparator.

The interface to module adc in Figure 1 includes four output and four

Fstm[n:0] Input Filter Settle Time Multiplier. Static

input signals, which are defined in Table 1. All signals are active high.

value that allows the user to control

bit sample time based on the low

pass filter settle time requirements.

The bit sample time is multiplied by

(Fstm+1).

Clk Input Positive edge clock for the internal

registers.

Reset Input Initializes internal registers.

XAPP155 September 23, 1999 (Version 1.1) 1

Product Obsolete/Under Obsolescence

Virtex Analog to Digital Converter

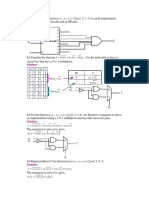

Architecture and Implementation AgtR

The ADC can be implemented in a single Verilog module that instan- ShiftIn

DACout

Shift Shift

tiates the DAC. The ADC output bus width is configurable with defined

Mask Shifter

RefShftr [8:0]

Reference

constant MSBI (MSBI specifies the most significant bit of the DAC input.

Shifter

9 M [8:0] 9

DAC

Q Q

The most significant bit of the ADC output is one less). Constant MSBR

is used to configure the width of the Filter Settle Time Counter. The ADC

RefShftr [8:1]

sample rate may be expressed as follows:

ADCSR = fClk/(2(MSBI+1) x (Fmst + 1) x (MSBI+1)) samples/second

Shift

LD

ADCout Register

Multiplier Counter

Filter Settle Time

In addition to the DAC, the ADC is comprised of the following major

elements: Fstm 4

Q

4 8

D Q

8

ADCout [7:0]

• DAC sample counter CE

• Filter settle time multiplier counter Dec

• Mask shifter

M [0]

• Reference shifter & D Q

• ADCout register ADCsampled

A description of each of these blocks follows. Refer to the Verilog code

located in “Appendix A - ADC Verilog Implementation” on page 5 and D Q

Sample

and the block diagram in Figure 2. 4

=0

FstmCntr [3:0]

DAC sample counter: This is a binary up counter that is the same width & D Q

Shift

as the DAC input. When the DAC input changes, it requires a minimum

of one complete cycle of this counter to resolve the new value at the DecFstmCntr

DAC Sample

output.

Counter

9 DACsampled

Q =0 D Q D Q

DACsampleCntr [8:0]

Filter settle time multiplier counter: In high-precision applications, a

large value for RC is selected for the DAC low pass filter to minimize

noise on the reference voltage. When this down-counter is at zero, it is 9905130102

loaded with Fstm, a constant provided by the user. Bit sample time is

effectively multiplied by Fstm+1, so the user can configure the bit Figure 2: Block Diagram

sample rate to match the filter settle time characteristics. The width of

this counter is configurable at design time with constant MSBR. A width

of four bits is adequate for most applications.

Vs = Vcco

Mask shifter: This register, which is the same width as the DAC input,

endlessly rotates a single bit right. This is effectively the state machine

RP

that controls the bit sample sequence, implemented so that correct

10.0k 1%

values can easily be loaded into the Reference shifter. VT

Reference shifter: This register drives the DAC input. It always starts a CF

sample with only the upper bit set. When only the upper bit is set, the Keystone

0.1µf

comparator output will be true if the analog input is greater than 1/2 RL108-5820-97-SP

VCCO, and it will be false if the analog input is less than 1/2 VCCO. If the

comparator output is true, the upper bit remains set, and the next lower

bit is set. If the comparator output is false, the upper bit clears, and the ADCref

next lower bit is set. This process continues all the way to the LSB, which Vcco

adc

causes voltage ADCref to home in on the analog input voltage. OBUF_F_24

RP 3k

ADCout register: This register snaps the high order bits of the 5.1k DACout

-

Reference shifter when the sample is left justified; that is, the LM319 AgtR 0.1µf

comparator output that was sensed when only the upper bit of the DAC + ADCout [8:0]

input was set is in the MSB. The ADCout register is one bit shorter than ADCsampled

the Reference shifter, making the LSB in ADCout accurate to 1/2 LSB. sample

Example Application - Thermometer DLL

4 ' b0100

50 MHz Fstm [3:0]

When a very small amount of power is dissipated in a thermistor, its ClkIn CLK2x

temperature is dependent on the surrounding ambient, so its electrical Reset

DLLlocked

resistance is a function of the ambient temperature. Under these Reset

conditions, it may be used to measure temperature.

9905100201

Figure 3 is a block diagram of a circuit using this ADC and a Keystone Figure 3: Example Application

Thermometrics precision thermistor to measure temperature. The circuit

uses an LM319 comparator.

In this circuit, thermistor voltage (VT) is inversely proportional to

temperature in Figure 4. For the temperature range 0 to +40˚C, the

relationship is almost linear. Figure 5 relates temperature and ADC

output over the same temperature range. Since this is not exactly a

linear relationship, the tabular data available from Keystone should be

used to relate the ADC output to temperature.

2 XAPP155 September 23, 1999 (Version 1.1)

Product Obsolete/Under Obsolescence

Virtex Analog to Digital Converter

A comparator has a functional range (the “Common Mode Limits”) that is that includes a DLL, 24 mA RC filter driver, etc. Note that constants

determined in part by the power supply voltages used. In the above MSBI and MSBR are defined in this module, so these definitions should

circuit, the LM319 is supplied with ground (0V), and +5V. This gives it a be removed from adc.v.

functional range of about 1.0V to 3.8V. Note from Figure 5 that VT is

within these boundaries when the temperature range is from 0 to +40˚C. Conclusion

These limits reduce the usable digital range (to about 178 to 391 in this This analog to digital converter is another example of how high speed

example). By avoiding high and low DAC limits, one also avoids the FPGAs may be used in mixed-signal systems to minimize the number of

worst case inputs to the RC filter, which reduces the noise on signal components. When circuitry is moved inside an FPGA that already

ADCref. (Note that the thermistor used in this example has a functional exists in the system, a reduction in component cost is realized as well.

range of -40 to +100˚C. The temperature range is limited primarily by the Also, FPGAs provide a level of in-field reconfigurability that cannot be

comparator common mode limits.) achieved in any other way. The speed and density of the Virtex family of

FPGAs make them ideal for a wide range of analog signal generating

Another key comparator parameter is the sensitivity, or Input Offset

and processing applications.

Voltage. This is the voltage difference between the positive and negative

inputs required to switch the output. The LM319 has a worst case Input

Offset Voltage of 8.0 mV. The Input Offset Voltage must be less than the

DAC step voltage, minus peak-to-peak noise.

It is important that the thermistor voltage, VS, be from the same source

as the OBUF_F_24 VCCO. When this is the case, variations on VCCO are

“common mode”, and are thus self-canceling.

The thermistor used in this example has an accuracy of 0.2˚Cwithout

calibration. A precision level to match this accuracy can be maintained

with a 9-bit ADC. Thermistor noise reduction capacitor CF is optional. It

may not be necessary if wire lengths are short.

See “Appendix B - ADC Top Level Verilog Code - File ADCtop.v” on

page 8 which shows an example of top-level Verilog code for the ADC

Keystone Precision Thermistor Voltage vs. Temperature, R@25 ˚C = 10.0 KΩ, Vs = 3.3V

3.00

2.50

Thermistor Voltage (Volts)

2.00

1.50

10.0

1.00

0.50

0.00 2.50 5.00 7.50 10.00 12.50 15.00 17.50 20.00 22.50 25.00 27.50 30.00 32.50 35.00 37.50 40.00

Temperature (˚C)

The number at the end of each curve is the Source resistance in K.Ω 9904300101

Figure 4: Thermistor Temperature vs. Voltage V

XAPP155 September 23, 1999 (Version 1.1) 3

Product Obsolete/Under Obsolescence

Virtex Analog to Digital Converter

Thermistor ADC Out vs. Temperature, R@25˚C = 10.0 KΩ, Vs = Vcco = 3.3 V, DAC width = 9

512

448

384

320

ADC Output

256

192

10.0

128

64

0

0.00 2.50 5.00 7.50 10.00 12.50 15.00 17.50 20.00 22.50 25.00 27.50 30.00 32.50 35.00 37.50 40.00

Temperature (˚C)

The number at the end of each curve is the Source resistance in KΩ. 9904300202

Figure 5: Thermistor Temperature vs. ADC Output

4 XAPP155 September 23, 1999 (Version 1.1)

Product Obsolete/Under Obsolescence

Virtex Analog to Digital Converter

Appendix A - ADC Verilog Implementation

' include "dac.v"

`timescale 100 ps / 10 ps

// This is an Analog to Digital Converter that uses an external

// analog comparator which compares the input voltage to a

// voltage generated by the built-in DAC. The DAC voltage starts at midrange,

// and continues to narrow down the result by successive division by 2

// until the DAC LSB is reached. This requires 'MSBI+1 (the width of

// the DAC input) samples. The width of the result is 1 bit less than the

// width of the DAC. The precision of the result is within 1/2 LSB.

module adc (ADCout, DACout, ADCsampled, Sample, Fstm, AgtR, Clk, Reset) ;

output [ `MSBI-1:0 ] ADCout; // ADC result register

output DACout; // This is the DAC average output that feeds low pass filter

output ADCsampled; // Status signal, CE for ADCout

output Sample; // Sample Analog signal when True; Hold when False

input [ `MSBR:0 ] Fstm;// Input constant. Sample time is multiplied by Fstm+1

input AgtR;// Comparator output; analog greater than Reference

input Clk;

input Reset;

reg [ `MSBR:0 ] DACsampleCntr;// DAC sample counter

reg DACsampled; // Pipelining DAC Sampled status

reg DecFstmCntr; // Pipeline DecFstmCntr

reg [ `MSBR:0] FstmCntr; // Low Pass Filter settle time counter

reg Shift; // Pipeline Shift signal

reg [ `MSBI:0] M; // Mask Shifter

reg [ `MSBI:0] RefShftr; // Reference Shifter (DAC input)

reg ADCsampled; // Pipeline ADCsampled status

reg [ `MSBI-1:0] ADCout; // ADC result buffer

reg Sample; // Sample Analog signal when True; Hold when False

// DAC sample counter. Same width as DACin. Counts up continuously.

// One cycle of this counter is the minimum time it takes for the

// DAC output to resolve to DACin.

always @ (posedge Clk or posedge Reset)

begin

if (Reset) DACsampleCntr <= #1 0;

else DACsampleCntr <= #1 DACsampleCntr + 1;

end

// pipeline DACsampled status for speed

always @ (posedge Clk or posedge Reset)

begin

if (Reset) DACsampled <= #1 1 'b0;

else DACsampled <= #1 (DACsampleCntr == 0);

XAPP155 September 23, 1999 (Version 1.1) 5

Product Obsolete/Under Obsolescence

Virtex Analog to Digital Converter

end

// pipeline DecFstmCntr signal so it is in phase with Shift Signal

always @ (posedge Clk or posedge Reset)

begin

if (Reset) DecFstmCntr <= #1 1 ' b0;

else DecFstmCntr <= #1 DACsampled;

end

// Filter settle time multiplier. This counter counts down to 0 from Fstm.

// When this counter reaches 0, the output of the comparator is sampled,

// so the DAC output reference voltage must be stable at that time.

// Fstm may be set to the lowest value that ensures a stable

// reference voltage, based on the low pass filter parameters.

always @ (posedge Clk or posedge Reset)

begin

If (Reset) FstmCntr <= #1 1;

else

begin

if (Shift) FstmCntr <= #1 Fstm;

else if (DecFstmCntr) FstmCntr <= #1 FstmCntr - 1;

end

end

wire FstmCntrEq0 = (FstmCntr == 0);

// pipeline Shift signal for speed

always @(posedge Clk or posedge Reset)

begin

if (Reset) Shift <= #1 1 'b0;

else Shift <= #1 (DACsampled & FstmCntrEq0);

end

// pipeline ADCsampled status for speed

always @(posedge Clk or posedge Reset)

begin

if (Reset) ADCsampled <= #1 1 ' b0;

else ADCsampled <= #1 (DACsampled & FstmCntrEq0 & M [ 0 ]) ;

end

// Mask shifter. Same width as DACin. A single bit rotates right endlessly.

// This bit specifies the next bit that will be sampled.

always @(posedge Clk or posedge Reset)

begin

if (Reset) M <= #1 0;

else

if (Shift)

begin

if (M [ 1 ] | ~( |M) ) M <= #1 1; // Guarantees 1 and only 1 bit set

else M <= #1 {M [ 0 ], M[ `MSBI :1] }; // shift right

6 XAPP155 September 23, 1999 (Version 1.1)

Product Obsolete/Under Obsolescence

Virtex Analog to Digital Converter

end

end

// Reference shifter. This shifter feeds DACin. Starts with only upper bit set.

// Shifts right, forcing next bit set, but conditionally clearing previous

// bit based on AgtR.

always @(posedge Clk or posedge Reset)

begin

if (Reset) RefShftr <= #1 0;

else if (Shift) RefShftr <= #1

{M[0], M [ `MSBI:1] } | (RefShftr & ~{( `MSBI+1) {M[0]}} & ~(M & ~{( `MSBI+1) {AgtR}}));

end

// ADCout register. Snaps upper bits of Refshiftr when sample is justified.

always @(posedge Clk or posedge Reset)

begin

if (Reset) ADCout <= #1 0;

else if (ADCsampled) ADCout <= #1 RefShftr [ `MSBI:1] ;

end

// Sample Latch

always @(posedge Clk or posedge Reset)

begin

if (Reset) Sample <= #1 0;

else

if (Shift)

begin

if (M [0]) Sample <= #1 1 'b1;

else Sample <= #1 1 'b0;

end

end

// Instantiate DAC

dac DC (.DACout (DACout),

.DACin (RefShiftr),

.Clk (Clk),

.Reset (Reset));

endmodule

XAPP155 September 23, 1999 (Version 1.1) 7

Product Obsolete/Under Obsolescence

Virtex Analog to Digital Converter

Appendix B - ADC Top Level Verilog Code - File ADCtop.v

`define MSBI 9 // Most Significant Bit of Dac input

`define MSBR 3 // Most Significant Bit of Filter Settle Time Multiplier

`include "adc.v"

`timescale 100 ps / 10 ps // This is a top level implementation module for adc

module ADCtop (ADCout, DACoutDrvr, ADCsampled, SampleDrvr, DLLlocked, ClkTp,

Fstm, AgtR, ClkIn, Reset);

output [ `MSBI-1:0] ADCout; // ADC result output buffer register

output DACoutDrvr; // This is the DAC output that feeds low pass filter

output ADCsampled; // Status signal, CE for ADCout register

output SampleDrvr; // Sample Analog signal when True; Hold when False

output DLLlocked; // DLL locked

output ClkTP; // 2X clock test point

input [ `MSBR:0] Fstm; // Input constant. Sample time is multiplied by Fstm+1

input AgtR; // external comparator output; analog greater than

Reference

input ClkIn;

input Reset;

IBUFG clk_pad (.I (ClkIn), .0 (clk_w));

CLKDLL DLL2X (.CLKIN(clk_w), .CLKFB(Clk), .RST(Reset), .CLK0 ()

.CLK90(), .CLK180(), .CLK270(), .CLK2X(Clk2X), .CLKDV(),

.LOCKED (DLLlocked));

BUFG CLKG (.I (Clk2X), .0 (Clk));

OBUF_F_24 CLKO (.I (Clk), .O (ClkTP)); // CLK2X test point driver

OBUF_F_24 AB ( .0 (DACoutDrvr) , .I (DACout)) ; // DACout 24ma Driver

OBUF_S_24 SD (.0 (SampleDrvr), .I (Sample)); // Sample 24 mA Driver

adc AD (.ADCout (ADCout), .DACout (DACout), .ADCsampled (ADCsampled), .Sample (Sample),

.Fstm (Fstm), .AgtR (AgtR), .Clk (Clk), .Reset (Reset));

endmodule

Revision History

0

Date Revision # Activity

7/26/99 1.0 Initial Release

9/23/99 1.1 Updated for Virtex-E devices

0

8 XAPP155 September 23, 1999 (Version 1.1)

You might also like

- Experiment No. 4 ADC PDFDocument16 pagesExperiment No. 4 ADC PDFRia Cordova0% (1)

- Cadence Based Imlementation of SuccessiveApproximation ADC Using 45nm Cmos TechnologyDocument6 pagesCadence Based Imlementation of SuccessiveApproximation ADC Using 45nm Cmos TechnologyUtsavNo ratings yet

- A/D and D/A Conversion Testing: V G 2 V VDocument7 pagesA/D and D/A Conversion Testing: V G 2 V VRichard NewbyNo ratings yet

- Dac If Xapp154Document8 pagesDac If Xapp154mubujeeNo ratings yet

- 10-Analog To Digital ConverterDocument41 pages10-Analog To Digital ConverterSamuel ChristianNo ratings yet

- Adc - DacDocument4 pagesAdc - DacShaheer TariqNo ratings yet

- Chapter 8 Data Acquisition and DistributionDocument18 pagesChapter 8 Data Acquisition and Distributionellyshacb-wp21No ratings yet

- CENG507 Fall2020 Chap6Document32 pagesCENG507 Fall2020 Chap6Anonymous phisherNo ratings yet

- ADC and DACDocument4 pagesADC and DACjeniferNo ratings yet

- Noninverting Circuit For High-To-Low Voltage Level Translation Very ImportantDocument7 pagesNoninverting Circuit For High-To-Low Voltage Level Translation Very Importantsung quekNo ratings yet

- DLC LAB - 10 - Student - ManualDocument8 pagesDLC LAB - 10 - Student - ManualImtiaj SajinNo ratings yet

- A D ConverterDocument20 pagesA D ConverterRenu TyagiNo ratings yet

- Analog-to-Digital Converter (ADC) and Digital-to-Analog Converter (DAC)Document23 pagesAnalog-to-Digital Converter (ADC) and Digital-to-Analog Converter (DAC)Pahala SamosirNo ratings yet

- Interfacing With The Analog WorldDocument20 pagesInterfacing With The Analog WorldSarah Joy ManimtimNo ratings yet

- Atmega328 - DTOADocument9 pagesAtmega328 - DTOAJohn SmithNo ratings yet

- Dec Exp 6 Student ManualDocument5 pagesDec Exp 6 Student ManualSakib MahmudNo ratings yet

- Digital to analog converters: fabrication and applicationsDocument10 pagesDigital to analog converters: fabrication and applicationsAşšAśsins BRošNo ratings yet

- Lesson Adc PWMDocument36 pagesLesson Adc PWMDavidRubeomNo ratings yet

- Stm32f3 AdcDocument65 pagesStm32f3 AdcJisNo ratings yet

- MSME Tool Room Diploma in Tool and Die Making Mechatronics CourseDocument160 pagesMSME Tool Room Diploma in Tool and Die Making Mechatronics CourseShivam SinghNo ratings yet

- Digital To Analog ConvertersDocument25 pagesDigital To Analog ConvertersAshutosh BhattNo ratings yet

- Digital Control SystemDocument23 pagesDigital Control SystemBHAVNA AGARWALNo ratings yet

- V1-Using The ADC of 80C552Document18 pagesV1-Using The ADC of 80C552Dams Ruc100% (1)

- Analog To Digital ConverterDocument57 pagesAnalog To Digital ConverterAnurag Chauhan100% (1)

- Analog To Digital & Digital To Analog ConvertersDocument66 pagesAnalog To Digital & Digital To Analog ConvertersSai Krishna Kodali100% (1)

- Introduction To Analog To Digital Converters (ADC)Document9 pagesIntroduction To Analog To Digital Converters (ADC)diether.gozumNo ratings yet

- Digital-to-Analog Analog-to-Digital Conversions: Microprocessor InterfaceDocument34 pagesDigital-to-Analog Analog-to-Digital Conversions: Microprocessor Interfaceeugen lupuNo ratings yet

- DAC Utilizing ADCDocument3 pagesDAC Utilizing ADCelfrichNo ratings yet

- Chapter 4Document23 pagesChapter 4Tejan Kumar SharmaNo ratings yet

- Applying The New CMOS Micro-Dac: National Semiconductor Application Note 271 Tim Regan September 1981Document12 pagesApplying The New CMOS Micro-Dac: National Semiconductor Application Note 271 Tim Regan September 1981Beroxi MihaiNo ratings yet

- Applications of 8085 Microprocessor Dac InterfaceDocument4 pagesApplications of 8085 Microprocessor Dac InterfaceSai PrakashNo ratings yet

- Boost Converter Using The PIC16F753 Analog Features: Performance SpecificationsDocument9 pagesBoost Converter Using The PIC16F753 Analog Features: Performance SpecificationsSheik Ashiq AmeerNo ratings yet

- Analog To Digital (ADC) and Digital To Analog (DAC) ConvertersDocument12 pagesAnalog To Digital (ADC) and Digital To Analog (DAC) ConvertersIoana IoanaNo ratings yet

- Analog To Digital Converters PresentationDocument15 pagesAnalog To Digital Converters Presentationnguyenphuonghuy1979100% (1)

- Adc 0804Document5 pagesAdc 0804gouttNo ratings yet

- Lab 11 DAC and ADC Full PackageDocument5 pagesLab 11 DAC and ADC Full PackageLoveWorldCanadaNo ratings yet

- DATA CONVERTER AND CONTROL SYSTEM LAB MANUAL EXPERIMENTSDocument45 pagesDATA CONVERTER AND CONTROL SYSTEM LAB MANUAL EXPERIMENTSSavita Kiran BNo ratings yet

- Design and Simulation of DAC On The Basis of Capacitor ArrayDocument4 pagesDesign and Simulation of DAC On The Basis of Capacitor ArrayAmitNo ratings yet

- Analog Input SignalsDocument20 pagesAnalog Input SignalsNecNo ratings yet

- Nama: Refin Ananda NIM: 3.32.17.0.20 Kelas: EK-3A Individual Presentation 2 Analog To Digital Converter 1. The Meaning of ADCDocument4 pagesNama: Refin Ananda NIM: 3.32.17.0.20 Kelas: EK-3A Individual Presentation 2 Analog To Digital Converter 1. The Meaning of ADCRifky Yoga PratamaNo ratings yet

- Accurate, Fast Settling Analog Voltages From Digital PWM SignalsDocument2 pagesAccurate, Fast Settling Analog Voltages From Digital PWM SignalsAdhi Ne CutcakrowoNo ratings yet

- DATA Converter CircuitsDocument31 pagesDATA Converter CircuitsCharefNo ratings yet

- ADCDocument2 pagesADCMayilsamy MayilNo ratings yet

- Complete Front End Solutions For Weigh Scales PDFDocument5 pagesComplete Front End Solutions For Weigh Scales PDFmahamd saiedNo ratings yet

- Digital-to-Analog Analog-to-Digital: Dr. Syed Faiz AhmedDocument69 pagesDigital-to-Analog Analog-to-Digital: Dr. Syed Faiz AhmedmuraliNo ratings yet

- AN12217 - S32K1xx ADC Guidelines, Spec andDocument26 pagesAN12217 - S32K1xx ADC Guidelines, Spec andNguyễn Mỹ KiênNo ratings yet

- Signal Processsing ElementDocument40 pagesSignal Processsing Elementkibrom atsbhaNo ratings yet

- Analog-Digital Converters: Types, Characteristics and ApplicationsDocument62 pagesAnalog-Digital Converters: Types, Characteristics and Applicationsparth bhardwajNo ratings yet

- Analog To Digital ConverterDocument4 pagesAnalog To Digital Converterzero kimochiNo ratings yet

- Adc F09Document61 pagesAdc F09abdala67No ratings yet

- 5 Digital To Analog Conversion: 5.1 Parameters of DacsDocument3 pages5 Digital To Analog Conversion: 5.1 Parameters of DacsYassine DjillaliNo ratings yet

- Analog To Digital ConverterDocument7 pagesAnalog To Digital Convertersaima alamNo ratings yet

- ADC and DAC PDFDocument23 pagesADC and DAC PDFMahendraLiyanageNo ratings yet

- Analog-To-Digital Conversion Btech IIIDocument50 pagesAnalog-To-Digital Conversion Btech IIILisa BhagatNo ratings yet

- DACDocument28 pagesDACRohith Mohan100% (1)

- Analog and Digital Signal Converter GuideDocument19 pagesAnalog and Digital Signal Converter GuidedsadasdasNo ratings yet

- Experiment No. 6: Objective: ApparatusDocument4 pagesExperiment No. 6: Objective: ApparatusNioNo ratings yet

- Adc Dac Converter NewDocument50 pagesAdc Dac Converter NewJaya PaulNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Digital Signature Paper AlgorithmDocument1 pageDigital Signature Paper AlgorithmTulasi RadhikaNo ratings yet

- Digisign Ref 1Document10 pagesDigisign Ref 1Tulasi RadhikaNo ratings yet

- CSTRNGDocument5 pagesCSTRNGTulasi RadhikaNo ratings yet

- Corrected Thesis 4 7 2020Document71 pagesCorrected Thesis 4 7 2020Tulasi RadhikaNo ratings yet

- Review 2Document37 pagesReview 2Tulasi RadhikaNo ratings yet

- ResultsDocument35 pagesResultsTulasi RadhikaNo ratings yet

- 722-4383-014 Rev C Multi-Level Engineering Bill of Materials ReportDocument18 pages722-4383-014 Rev C Multi-Level Engineering Bill of Materials Reportemail9991No ratings yet

- Frequency Response v2Document31 pagesFrequency Response v2gyyildirim21No ratings yet

- 69 - EC21101 - Practice Questions - BJT MOSFET PDFDocument3 pages69 - EC21101 - Practice Questions - BJT MOSFET PDFSubhajit BagNo ratings yet

- Assign 6Document3 pagesAssign 6DivyanshNo ratings yet

- Basic Resonance Circuit Concepts: Series Resonant Circuits Parallel Resonant CircuitsDocument20 pagesBasic Resonance Circuit Concepts: Series Resonant Circuits Parallel Resonant CircuitsHardik MehtaNo ratings yet

- Four-Channel Universal Analog Input Using The MAX11270: Hardware SpecificationDocument8 pagesFour-Channel Universal Analog Input Using The MAX11270: Hardware SpecificationcutoNo ratings yet

- Master SetDocument624 pagesMaster SetEr Lokesh MahorNo ratings yet

- Term 2, Lecture 4: Transistor Bias Circuits The DC Operating PointDocument7 pagesTerm 2, Lecture 4: Transistor Bias Circuits The DC Operating Pointrafal mahmodNo ratings yet

- 6.2 Solution::, W, W) M (1, 2, 3, 5, 6) Can Be ImplementedDocument3 pages6.2 Solution::, W, W) M (1, 2, 3, 5, 6) Can Be ImplementedYogeeswar PydaNo ratings yet

- ENcoder Notes EE101Document13 pagesENcoder Notes EE101mohitNo ratings yet

- Chapter 1 - Overview On Digital IC DesignDocument45 pagesChapter 1 - Overview On Digital IC DesignNorjuliana Muhammad TahaNo ratings yet

- UM A31G22x EngDocument503 pagesUM A31G22x EngMert DemirbasNo ratings yet

- Icl7116/Icl7117 3 Digit Adcs With Display Hold: General Description FeaturesDocument8 pagesIcl7116/Icl7117 3 Digit Adcs With Display Hold: General Description Featuressigit raharjoNo ratings yet

- Ece3002 Vlsi System Deign Cocob 2019Document3 pagesEce3002 Vlsi System Deign Cocob 2019Debasis ChandraNo ratings yet

- Department of Electronics and Communication Engineering Faculty of Engineering and Technology, SRM UniversityDocument6 pagesDepartment of Electronics and Communication Engineering Faculty of Engineering and Technology, SRM UniversityShubham Kumar GuptaNo ratings yet

- Static Random Access Memories (SRAM) : Birdy AmruturDocument9 pagesStatic Random Access Memories (SRAM) : Birdy AmruturAnudeepKrishnaNo ratings yet

- AN-CIPOS Mini-2 Reference Board-3 For IGCMxxF60GA With 3-Shunt - Ver1.0 20101021 PDFDocument14 pagesAN-CIPOS Mini-2 Reference Board-3 For IGCMxxF60GA With 3-Shunt - Ver1.0 20101021 PDFRodrigo BilheiroNo ratings yet

- ALINCO DJ-A41 Service ManualDocument29 pagesALINCO DJ-A41 Service ManualmalamigNo ratings yet

- Complete Audio Amplifier OpampDocument5 pagesComplete Audio Amplifier OpampdodifirmanNo ratings yet

- Annexure - IDocument9 pagesAnnexure - ISav ThaNo ratings yet

- Circuit Debug QuestionDocument9 pagesCircuit Debug QuestionDharang Shah100% (1)

- Voltage Limiter Circuit Using OpDocument5 pagesVoltage Limiter Circuit Using OpjcblackmoreNo ratings yet

- I-V Characteristics of Diode ExperimentDocument11 pagesI-V Characteristics of Diode Experimentabir al ahsanNo ratings yet

- Interfacing Memory Chips With 8085Document10 pagesInterfacing Memory Chips With 8085Honsyben BriansNo ratings yet

- DIGITAL LOGIC DESIGN LAB REPORT SIMPLIFICATION USING KARNAUGH MAPDocument10 pagesDIGITAL LOGIC DESIGN LAB REPORT SIMPLIFICATION USING KARNAUGH MAPZain Ullah Inayat UllahNo ratings yet

- stk412 240Document1 pagestk412 240luisclaudio31No ratings yet

- Construct Level Shifted AND Gate Voltage Truth TableDocument5 pagesConstruct Level Shifted AND Gate Voltage Truth TablekallugNo ratings yet

- Study of R2R DAC Circuits Using MultisimDocument5 pagesStudy of R2R DAC Circuits Using MultisimAnandababuNo ratings yet

- 46 Analysis PDFDocument6 pages46 Analysis PDFKrishna aug13No ratings yet

- ECE 306 Lab 4: Class AB Amplifier EfficiencyDocument8 pagesECE 306 Lab 4: Class AB Amplifier EfficiencyShehzadtajNo ratings yet