Professional Documents

Culture Documents

4 - Paper 1 May 2016

Uploaded by

Jay Prakash Narayan VermaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

4 - Paper 1 May 2016

Uploaded by

Jay Prakash Narayan VermaCopyright:

Available Formats

International Journal of Research p-ISSN: 2348-6848

e-ISSN: 2348-795X

Available at https://edupediapublications.org/journals

Volume 03 Issue 09

May 2016

Implementation of Low Power High Speed 32 bit ALU

using FPGA

J.P. Verma

Assistant Professor (Department of Electronics & Communication Engineering)

Maaz Arif; Brij Bhushan Choudhary& Nitish Kumar

Electronics & Communication Engineering SRM University, Delhi NCR Campus Modinagar-201204

ABSTRACT-

Digital design is an amazing and very broad field. operations:

The applications of digital design are present in

Arithmetic operations (addition, subtraction,

our daily life, including computers, calculators, increment , decrement , transfer) .

video cameras etc. The VHDL (VHSIC Hardware Logic operations (AND, NOT, OR, EX-OR)

Description Language) has become an essential Shift operations (LSR,LSL).

tool for designers in the world of digital design.

This paper presents implementation of a 32-bit A digital system can be represented at different

Arithmetic Logic Unit (ALU) using VHDL. Here levels of abstraction .. The highest level of

the behavioral VHDL model of ALU is designed abstraction is the behavioral level that describes a

to perform 14 operations which includes logical, system in terms of what it does (or how it

arithmetic and shift operations. The VHDL behaves) rather than in terms of its components

implementation and functionality test of the 32-bit and interconnection between them.Here the 32-

ALU is done by using the Modelsim 5.4a tool. bit ALU is implemented by using the behavioral

modeling style to describe how the operation of

1. INTRODUCTION ALU is being processed. This is accomplished by

using a hardware description language VHDL.

The Arithmetic Logic Unit (ALU) is a

fundamental building block of the Central The behavioral style makes use of a process

Processing Unit (CPU) of a computer. Even one statement. A process statement is the main

of the simplest microprocessor contains one ALU construct in behavioral modeling that allows using

for purposes such as maintaining timers. We can sequential statements to describe the behavior of a

say that ALU is a core component of all central system over time. Process is declared within an

processing unit within in a computer and is an architecture and is a concurrent statement.

integral part of the execution unit. ALU is capable However, the statements inside a process are

of calculating the results of a wide variety of basic executed sequentially.

arithmetical and logical computations. The ALU 2. 32 BIT ALU

takes as input the data to be operated on (called 32 bit ALU consists of an arithmetic unit, a logic

operands) and a code from the control unit unit, a shift unit, clock gating unit and an output

indicating which operation to perform. The output multiplexer.

is the result of the computation. The ALU

implemented will perform the following

Available online:http://internationaljournalofresearch.org/ P a g e | 418

International Journal of Research p-ISSN: 2348-6848

e-ISSN: 2348-795X

Available at https://edupediapublications.org/journals

Volume 03 Issue 09

May 2016

2.1. 32 Bit Arithmetic Unit

The Arithmetic unit performs 7 operations such as 1 1 0 A Transfer

addition, addition with carry, subtraction,

subtraction with borrow, increment, decrement, 1 1 1 A+1 Increment

transfer. The circuit consists of a 32 bit parallel

adder and thirty two numbers of single bits 4:1

multiplexer. A and B is a 32 bit input and the 2.2. 32 Bit Logic Unit

output is 33 bit result, there is 2 common selection

lines S0 and S1, Cin is carry input of the parallel The Logic unit does the following tasks logical

adder and the carry out is Cout. AND, logical OR, logical XOR, logical NOT and

complement operation. The logic unit consists of

Fig-1: 32 Bit Arithmetic Unit four gates and a 4:1 multiplexer. The output of the

gates is applied to the data inputs of the

multiplexer. Using selection lines S0 and S1 one

the data inputs of the multiplexer is selected as the

output.

Fig-2: 32 Bit Logic Unit

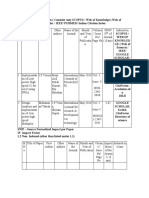

Table-1: Operation performed on Arithmetic Unit

S1 S0 Cin Result Operation

Table-2: Operation performed on Logic Unit

0 0 0 A+B Addition

0 0 1 A+B+1 Addition with S0 S1 Result Operation

Carry

0 1 0 A+ ̅ Subtraction 0 0 A.B AND

0 1 1 A+ ̅+1 Subtraction with

Borrow 0 1 A+B OR

1 0 0 A-1 Decrement

1 0 A⊕B XOR

1 0 1 A Transfer

Available online:http://internationaljournalofresearch.org/ P a g e | 419

International Journal of Research p-ISSN: 2348-6848

e-ISSN: 2348-795X

Available at https://edupediapublications.org/journals

Volume 03 Issue 09

May 2016

1 1 Not A Compliment A 2.3. 32 Bit Shift Unit

Shift unit is used to perform logical shift

operations. Shift left shifts one bit to the left

gives result which is original number multiplied by

two similarly shifting n times to the left

gives result which is equivalent to the original

number multiplied by 2n and Shift Right shifts one

bit to the right gives result which is original

number multiplied by two similarly n times to the

right gives result which is equivalent to original

number divide by 2n. For a shift unit of 32-bit, the

output will be of 33-bit with 33th bit to be the

outgoing bit.

Fig-3: 32 Bit Shift Unit

2.4. 32 Bit Arithmetic and Logical Unit

The approach used here is to split the ALU into

three modules, one Arithmetic, one Logic and one

Shift module. The arithmetic, logic and shifter

units introduced earlier can be combined into ALU

with common selection lines. The shift micro-

operations are often performed in a separate unit,

but sometimes the shifter unit made part of overall

Table-3: Operation performed on Shift Unit ALU. Since the ALU is composed of three units,

namely Arithmetic, Logic and Shifter Units. For

S Operation 32-bit ALU a 33 bit 4:1 MUX is needed. A

particular arithmetic or logic or shift operation is

selected according to the selection inputs S0 and

0 Right Shift A

S1. The final output of the ALU is determined by

the set of multiplexers with selection lines S2 and

1 Left Shift A

S3. The function table for the

Fig-4: (a) 32-bit Right Shift Operation

(b) 32-bit Left Shift Operation

Available online:http://internationaljournalofresearch.org/ P a g e | 420

International Journal of Research p-ISSN: 2348-6848

e-ISSN: 2348-795X

Available at https://edupediapublications.org/journals

Volume 03 Issue 09

May 2016

ALU is shown in the Table. 1. The table lists 14

micro-operations: 8 for arithmetic, 4 for logic and S3 S2 S1 S0 Cin Result Operation

2 for shifter unit. For shifter unit, the selection line

0 0 0 0 0 A+B Addition

S1 is used to select either left or right shift micro-

operation.

0 0 0 0 1 A+B+1 Addition with

carry

Fig-5: 32 Bit ALU Unit

0 0 0 1 0 A+ ̅ Subtraction

0 0 0 1 1 A+̅ Subtraction

with borrow

0 0 1 0 0 A-1 Decrement

0 0 1 0 1 A Transfer

0 0 1 1 0 A Transfer

0 0 1 1 1 A+1 Increment

0 1 0 0 X A •B AND

0 1 0 1 X A+B OR

0 1 1 0 X A⊕ B XOR

0 1 1 1 X ̅ Complement

1 0 0 X X LSR A Shift Right

1 0 1 X X LSL A Shift Left

Available online:http://internationaljournalofresearch.org/ P a g e | 421

International Journal of Research p-ISSN: 2348-6848

e-ISSN: 2348-795X

Available at https://edupediapublications.org/journals

Volume 03 Issue 09

May 2016

3. SIMULATIONS AND

IMPLEMENTATION

The 32 Bit ALU with clock gating is designed in 4. RTL SCHEMATIC

VHDL using Xilinx ISE 12.4 design suite. The Register Transfer Level of 32 Bit ALU

simulation is done using Modelsim Simulator

with a clock period of 1 us. After the design is

synthesized on a Spartan 3E device the design is

implemented. The process of simulation uses a

testbench to test the design whether it behaves

correctly by stimulating it with artificial input

and monitoring the output. The simulation is

carried out by using the Modelsim 5.4a tool and

having the testbench and the behavioral design

code for 32-bit ALU in the same project folder.

3.1 Simulation Waveforms

Fig-6: Simulated Waveform for Arithmetic Unit

Fig-7: Simulated Waveform for Logic Unit

5. CONCLUSION

In our project “Design and Implementation of a

32-bit ALU on Xilinx FPGA using VHDL” we

have designed and implemented a 32 bit ALU.

Arithmetic Logic Unit is the part of a computer

that performs all arithmetic computations, such

as addition and subtraction, increment,

decrement, shifting and all sorts of basic logical

operations. The ALU is one component of the

Fig-8: Simulated Waveform for Shift Unit CPU (Central Processing Unit).

Here, using VHDL we have designed a 32 bit

ALU which can perform the various arithmetic

operations of Addition, Subtraction, Increment,

Available online:http://internationaljournalofresearch.org/ P a g e | 422

International Journal of Research p-ISSN: 2348-6848

e-ISSN: 2348-795X

Available at https://edupediapublications.org/journals

Volume 03 Issue 09

May 2016

Decrement, Transfer, logical operations such as Example, 4th ed., Tata McGraw-Hill Publishing

AND, OR, XOR, NOT and also the shift Company Limited, New Delhi, 2002.

operation.

All the above mentioned operations are then [4] Geetanjali and NishantTripathi.“VHDL

verified to see whether they match theoretically Implementation of 32-Bit Arithmetic Logic

or not. The above given waveforms show that Unit (Alu)”,International Journal of

they match completely thereby verifying our Computer Science Engineering, IJCSCE

results. Special issue on“Emerging Trends in

Engineering” ICETIE 2012

6. Acknowledgement

It is our immense pleasure to find an opportunity [5] Xilinx, Spartan-3E FPGA Family: Data

to express our deep gratitude and sincerest thank Sheet, DS312 (v3.8) August 26, 2009.

to Asst. Prof. Rupali Singh (SRM,

Modinagar), Asst. Prof Meenakshi Sanadhya

(SRM, Modinagar ) and Asst. Prof Arun [6] VHDL Tutorial, Ardent Computech,

Kumar (SRM, Modinagar) for giving most PVT. LTD., 2011.

valuable suggestion, helpful guidance and

encouragement in completion of our project and

providing us all possible assistance. They have

been extremely motivating and helped during the

execution of this project work that has led us to

the successful completion of our project titled:

“Design and Synthesis of a 32-bit ALU on Xilinx

ISE v9.1i using VHDL”. We highly appreciate

the efforts and numerous suggestions that they

structured our work with their valuable tips and

accorded to us in every respect of our work. At

last, we humbly extend our sincere appreciation

to other faculty also who help and encouraged

us in some way or during our working

project environment.

6 . REFERENCES

[1] T. K. Ghosh and A. J. Pal, Computer

Organization and Architecture, Tata McGraw-

Hill Publishing Company Limited, New Delhi,

2009.

[2] Ankit Mitra., “Design and

implementation of low pow er 16 bit ALU with

clock gating”, International Journa l of Advanced

Research in Computer Engineering &

Technology (IJARCET), Volume 2, Issue 6, June

2013.

[3] Douglas L. Perry, VHDL Programming by

Available online:http://internationaljournalofresearch.org/ P a g e | 423

You might also like

- 32 Bit AluDocument4 pages32 Bit AluJanakiSreeramNo ratings yet

- Design of High Performance Radix-4 and Radix-8 Multiplier Using Verilog HDLDocument11 pagesDesign of High Performance Radix-4 and Radix-8 Multiplier Using Verilog HDLCharan UkkuNo ratings yet

- IJRAR19D1206Document8 pagesIJRAR19D1206madhuriNo ratings yet

- 4 Bit Arithmetic and Logic Unit Design Using Structural Modelling in VHDL IJERTV2IS3197 PDFDocument4 pages4 Bit Arithmetic and Logic Unit Design Using Structural Modelling in VHDL IJERTV2IS3197 PDFTanmaya Tapaswini TripathyNo ratings yet

- Half Adder Using Different Design Styles: A Review On Comparative StudyDocument8 pagesHalf Adder Using Different Design Styles: A Review On Comparative Studyjanapaneni ramadeviNo ratings yet

- Vlsi Implementation of 32 Bit Unsigned Multiplier Using An Efficient Claa and CslaDocument4 pagesVlsi Implementation of 32 Bit Unsigned Multiplier Using An Efficient Claa and CslaInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- VHDL Implementation of 8-Bit ALU: Arshabha AryaDocument7 pagesVHDL Implementation of 8-Bit ALU: Arshabha Aryamohammad aidilNo ratings yet

- Streaming SIMD Extensions - LU DecompositionDocument14 pagesStreaming SIMD Extensions - LU DecompositionAngel BravoNo ratings yet

- Answer To Question No 1-Program CounterDocument8 pagesAnswer To Question No 1-Program CounterAbdul Mannan HanifNo ratings yet

- Computer Architecture 7Document15 pagesComputer Architecture 7ARAFAT GaamanNo ratings yet

- VHDL Implementation of Arithmetic Logic Unit: April 2014Document9 pagesVHDL Implementation of Arithmetic Logic Unit: April 2014ammarNo ratings yet

- Design and Analysis of An Efficient 16-Bit MultiplierDocument6 pagesDesign and Analysis of An Efficient 16-Bit MultiplierChandra shekara mnNo ratings yet

- Design and Implementation of 256 256 Booth Multiplier and Its ApplicationsDocument4 pagesDesign and Implementation of 256 256 Booth Multiplier and Its ApplicationssurbhiNo ratings yet

- Chapter 1Document29 pagesChapter 1Gemechis GurmesaNo ratings yet

- Multiplexer-Based Design of Adders/Subtractors and Logic Gates For Low Power VLSI ApplicationsDocument8 pagesMultiplexer-Based Design of Adders/Subtractors and Logic Gates For Low Power VLSI ApplicationssunilNo ratings yet

- A Review Paper On PLC & Its Applications in Robotics and AutomationDocument6 pagesA Review Paper On PLC & Its Applications in Robotics and AutomationIbrahim ElkhatibNo ratings yet

- Design of 8 Bit Alu Using Microwind 3.1Document6 pagesDesign of 8 Bit Alu Using Microwind 3.1ijaert100% (1)

- 2:1 Multiplexer Using Different Design Styles: Comparative AnalysisDocument10 pages2:1 Multiplexer Using Different Design Styles: Comparative AnalysisVLSISD36 Edwin DominicNo ratings yet

- CO Lab Manual-MinDocument40 pagesCO Lab Manual-MinMatheen TabidNo ratings yet

- VHDL Microproject ReportDocument15 pagesVHDL Microproject ReportHitesh TumsareNo ratings yet

- csc213 AssignmentDocument8 pagescsc213 Assignmentstevefocus01No ratings yet

- 2:1 Multiplexer Using Different Design Styles: Comparative AnalysisDocument10 pages2:1 Multiplexer Using Different Design Styles: Comparative AnalysisNobitaNo ratings yet

- Design of Floating Point Arithmetic Unit Using V HDLDocument5 pagesDesign of Floating Point Arithmetic Unit Using V HDLHitesh TumsareNo ratings yet

- Radix-4 and Radix-8 Multiplier Using Verilog HDLDocument6 pagesRadix-4 and Radix-8 Multiplier Using Verilog HDLIJARTETNo ratings yet

- Design of Low Power Approximate Radix 8 Booth Multiplier IJERTCONV5IS17004Document5 pagesDesign of Low Power Approximate Radix 8 Booth Multiplier IJERTCONV5IS17004ManojNo ratings yet

- Design of 32 Bit Alu Ijert PaperDocument5 pagesDesign of 32 Bit Alu Ijert Papergollapudi vamsikrishnaNo ratings yet

- Project Report About MultipliersDocument62 pagesProject Report About Multiplierssenthilvl80% (5)

- Dokumen - Tips - 8 Bit Alu ReportDocument21 pagesDokumen - Tips - 8 Bit Alu ReportKshitize AgarwalNo ratings yet

- Design and Implementation of Floating Point ALU With Parity Generator Using Verilog HDLDocument6 pagesDesign and Implementation of Floating Point ALU With Parity Generator Using Verilog HDLIOSRjournalNo ratings yet

- Irjet V5i3295 PDFDocument3 pagesIrjet V5i3295 PDFchaitanya sNo ratings yet

- Computer Organization and Design NotesDocument7 pagesComputer Organization and Design Notesishtiaq hussainNo ratings yet

- Combinational CircuitsDocument44 pagesCombinational CircuitsWisdom tabuloNo ratings yet

- ALU MISSDV0716 G.kaladhar Design PlanDocument16 pagesALU MISSDV0716 G.kaladhar Design Plangourishettikaladhar562No ratings yet

- Existing MethodologyDocument7 pagesExisting MethodologyMichael FrancisNo ratings yet

- Title - Construction and Testing of Adder and Subtractor CircuitsDocument6 pagesTitle - Construction and Testing of Adder and Subtractor Circuitsr.samin100No ratings yet

- 32 Bit Multiplication and Division ALU Design Based On RISC StructureDocument4 pages32 Bit Multiplication and Division ALU Design Based On RISC StructureVishnu Kumar NadarNo ratings yet

- Irjet V5i11169Document13 pagesIrjet V5i11169Sumardi Sadi FT UMTNo ratings yet

- Implementation of Full Adder CircuitDocument10 pagesImplementation of Full Adder Circuitgenz2431No ratings yet

- DSD LabDocument42 pagesDSD LabArun GoyalNo ratings yet

- VHDL Implementation of 8-Bit ALU: Suchita Kamble, Prof .N. N. MhalaDocument5 pagesVHDL Implementation of 8-Bit ALU: Suchita Kamble, Prof .N. N. MhalaInternational Organization of Scientific Research (IOSR)No ratings yet

- Synthesizing Combinational Logic Circuits: Laboratory Experiment No. 4Document8 pagesSynthesizing Combinational Logic Circuits: Laboratory Experiment No. 4DervNo ratings yet

- Digital Logic Design Laboratory Course Id: It099IuDocument13 pagesDigital Logic Design Laboratory Course Id: It099IuTrương Quang TườngNo ratings yet

- Radix-4 and Radix-8 Multiplier Using Verilog HDL: (Ijartet) Vol. 1, Issue 1, September 2014Document6 pagesRadix-4 and Radix-8 Multiplier Using Verilog HDL: (Ijartet) Vol. 1, Issue 1, September 2014RalucaJulaNo ratings yet

- Ijecet: International Journal of Electronics and Communication Engineering & Technology (Ijecet)Document11 pagesIjecet: International Journal of Electronics and Communication Engineering & Technology (Ijecet)IAEME PublicationNo ratings yet

- Improving The Performance of A Multibit Arithmetic Logic UnitDocument9 pagesImproving The Performance of A Multibit Arithmetic Logic Unitkimemma063No ratings yet

- Cao NotessDocument129 pagesCao NotessRosh_MiNo ratings yet

- ALUDocument5 pagesALUsofNo ratings yet

- Copyno1 Lastone February (Final)Document153 pagesCopyno1 Lastone February (Final)Sujala PatnaikNo ratings yet

- Chapter 1 - Digital Logic DesignDocument40 pagesChapter 1 - Digital Logic DesignMerry GirmaNo ratings yet

- QB104322Document4 pagesQB104322abhirupnath666No ratings yet

- Lab Module 3 - Logic Gate ApplicationDocument6 pagesLab Module 3 - Logic Gate ApplicationFahmi Faiz RosliNo ratings yet

- Design of Efficient Multiplier Using VHDLDocument50 pagesDesign of Efficient Multiplier Using VHDLNagendra KashyapNo ratings yet

- Floating Point Multiplier With The Use of AluDocument4 pagesFloating Point Multiplier With The Use of Alubindu_ankuNo ratings yet

- VHDL Implementation of 32-Bit Arithmetic Logic Unit (Alu) : Geetanjali and Nishant TripathiDocument4 pagesVHDL Implementation of 32-Bit Arithmetic Logic Unit (Alu) : Geetanjali and Nishant TripathiRonald McJollibeeNo ratings yet

- SADGUNmajortheoryDocument51 pagesSADGUNmajortheoryKotagiri AravindNo ratings yet

- UJEEE1 JiteshshindeDocument14 pagesUJEEE1 Jiteshshindekimemma063No ratings yet

- JP Publication FormatDocument5 pagesJP Publication FormatJay Prakash Narayan VermaNo ratings yet

- J.P.Verma Research PapersDocument9 pagesJ.P.Verma Research PapersJay Prakash Narayan VermaNo ratings yet

- Annual Report JP-VERMADocument2 pagesAnnual Report JP-VERMAJay Prakash Narayan VermaNo ratings yet

- 8 - April-2018 IJERTV7IS040295Document5 pages8 - April-2018 IJERTV7IS040295Jay Prakash Narayan VermaNo ratings yet

- 9 May2019Document4 pages9 May2019Jay Prakash Narayan VermaNo ratings yet

- 11 Vijayan - Springer Sci - 2021 If-7.1Document11 pages11 Vijayan - Springer Sci - 2021 If-7.1Jay Prakash Narayan VermaNo ratings yet

- 12 Article Text-5954-1-10-20210815 2021 SNIP-11Document13 pages12 Article Text-5954-1-10-20210815 2021 SNIP-11Jay Prakash Narayan VermaNo ratings yet

- 1 - Power - Penalty1 - in - WDM - Systems - Using - Lumped - Amplifier 2014Document5 pages1 - Power - Penalty1 - in - WDM - Systems - Using - Lumped - Amplifier 2014Jay Prakash Narayan VermaNo ratings yet

- 3 - Paper 2 May 2016Document5 pages3 - Paper 2 May 2016Jay Prakash Narayan VermaNo ratings yet

- 2 - SRM IJES Sep 16 Vol-4 Number-1Document6 pages2 - SRM IJES Sep 16 Vol-4 Number-1Jay Prakash Narayan VermaNo ratings yet

- Valve & Amplifier Design, Valve EquivalentsDocument51 pagesValve & Amplifier Design, Valve EquivalentsValve Data80% (5)

- Thermal Analysis and Compensation of A Double Column Machining CentreDocument9 pagesThermal Analysis and Compensation of A Double Column Machining CentreShamanth CNo ratings yet

- Traulsen RLT - ALT Freezer DUTDocument2 pagesTraulsen RLT - ALT Freezer DUTwsfc-ebayNo ratings yet

- TH 2100Document67 pagesTH 2100KI TechnologiesNo ratings yet

- Electronic Modular Control Panel II Paralleling Emcp II P Systems Operation Troubleshooting Testing and Adjusting CaterpillarDocument200 pagesElectronic Modular Control Panel II Paralleling Emcp II P Systems Operation Troubleshooting Testing and Adjusting CaterpillarAbdo MalkiNo ratings yet

- Bluetooth PresentationDocument18 pagesBluetooth Presentationarjun_rathore8178No ratings yet

- Lecture 4: Expert Systems: What Is An Expert System?Document5 pagesLecture 4: Expert Systems: What Is An Expert System?Zerihun BekeleNo ratings yet

- SMS SRH-2D SedimentTransportDocument19 pagesSMS SRH-2D SedimentTransportthendyNo ratings yet

- 29 - CHAPTER 3 Intermolecular Forces and Potential Enegy SurfacesDocument9 pages29 - CHAPTER 3 Intermolecular Forces and Potential Enegy SurfacesMohit Kamboj100% (2)

- Theories and Methods of Two Way Slab Design-5-8-2017Document3 pagesTheories and Methods of Two Way Slab Design-5-8-2017amerta 4320No ratings yet

- 2015-NBLUCK LK260 Engine Part ListDocument16 pages2015-NBLUCK LK260 Engine Part ListPedroNo ratings yet

- Yohimbine InjectionDocument1 pageYohimbine InjectionKasidit SornchaiNo ratings yet

- Tarea Stereonet-HelpDocument32 pagesTarea Stereonet-HelpJosueHuillcaPortilloNo ratings yet

- Unit 1Document29 pagesUnit 1Biswajit MishraNo ratings yet

- TB-2100 Operational and Maintenance Manual Rev C OptimiseDocument224 pagesTB-2100 Operational and Maintenance Manual Rev C OptimisearnaudmarielNo ratings yet

- Maths Shortcuts by DayTodayGKDocument20 pagesMaths Shortcuts by DayTodayGKAnand KesarkarNo ratings yet

- Summative Test in Grade 10 Science PDF FreeDocument2 pagesSummative Test in Grade 10 Science PDF FreeMalyn ReyesNo ratings yet

- ISG Services OverviewDocument12 pagesISG Services OverviewsdonNo ratings yet

- Vogue 201602 Japan PDFDocument254 pagesVogue 201602 Japan PDFJack Douglas YooNo ratings yet

- Fire InvestigationDocument126 pagesFire InvestigationAbcede IloiloNo ratings yet

- 1SC0 2PF Exam-Paper 20180616Document20 pages1SC0 2PF Exam-Paper 20180616Thasanya AlgamaNo ratings yet

- API-650 Design Procedure ExampleDocument21 pagesAPI-650 Design Procedure Examplegdwvcd93% (14)

- MAJOR14Document14 pagesMAJOR14swathi100% (1)

- Engineering Properties of Soil PDFDocument55 pagesEngineering Properties of Soil PDFJam Apizara Chaizalee100% (1)

- Technical Support Engineer - Home AssignmentDocument5 pagesTechnical Support Engineer - Home AssignmentRahul KohliNo ratings yet

- Squall (Better) Training Manual: ModelsDocument83 pagesSquall (Better) Training Manual: ModelsSilomo-saka MambaNo ratings yet

- 1 - Classful Ip AddressingDocument6 pages1 - Classful Ip AddressingBiruk Tesfaye Legesse100% (1)

- HR Wallingford-009 - Wave - GaugeDocument2 pagesHR Wallingford-009 - Wave - GaugeSutanto HadiNo ratings yet

- Thermodynamics NotesDocument2 pagesThermodynamics Notesjpu_48No ratings yet

- Linear Algebra Cheat SheetDocument2 pagesLinear Algebra Cheat SheetBrian WilliamsonNo ratings yet