Professional Documents

Culture Documents

Design and Characterization Time Stamping Core Clock Muhammed Thaha Final Paper

Uploaded by

irfanmaoOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Design and Characterization Time Stamping Core Clock Muhammed Thaha Final Paper

Uploaded by

irfanmaoCopyright:

Available Formats

Design and Characterization of Time

Stamping IP Core for Clock Synchronization

Muhammed Thaha

thaha.thaha007@gmail.com

Abstract- In today’s modern network, time is becoming more and more critical than before, time synchronization is

significant in many different technologies and applications like test and measurement, factory automation, power plants,

robotic control, telecommunication and financial applications. Most of the communication networks are running over IP

network, which is sensitive to issues in timing and synchronization. IEEE 1588 Precision Time Protocol (PTP) is a key

standard for providing synchronization to networks, at high precision and provides both frequency and time

synchronization, through an exchange of packets over network. Stamping PTP messages accurately in physical layer

taking advantage of hardware is one of the key technologies, to achieve the objective of high precision time

synchronization. This work forward, design and characterization of re-configurable and re-useable hardware time

stamping unit along with a parser having L2, L4 PTP messages, compatible with PTP version1 and 2. It works

independently or along with a protocol stack to achieve fractional micro second level precision. The hardware unit is

synthesized with Xilinx ISE® tool implemented in virtex 6® and analyzed using Chip Scope Pro® integrated logic analyzer.

It is aimed to use with high end SOC architecture as a reconfigurable and re usable IP core.

I. INTRODUCTION

Along with the development of the electronics and electrical industry more and more electronic intelligent devices

for measurement, protection and control have been put into use to improve the stability and reliability of the system.

But there is also an increasing demand on accurate time synchronization for range of fields, most of the today’s

communication networks are running over IP network which is highly vulnerable to issues in timing and

synchronization in proper running of communication network especially telecommunication networks due to highly

unpredictable traffic flows, such as high-speed wireless networks that need to know the position of nodes and

require precise control of devices that are used in extreme situations or high precision operations [1-2].

There are two popular methods of time precision viz; location based synchronization and frequency based

synchronization. Location based method uses global position system (GPS) [3], which receives location information

from satellite for synchronization and gives micro second accuracy but with an over head due to the extra antenna

requirement. Frequency based synchronization uses Network Time Protocol (NTP) [4], which does not need any

extra module gives only millisecond accuracy. To improve this, IEEE 1588 Time Synchronization Standard was

announced in 2002 [5], as version1 and updated at 2008 [6], as version 2. IEEE 1588 is designed for spatially

localized systems with options of scalability, it aims to give microsecond to sub microsecond accuracy with

provision of redundant and fault tolerant system, having administration free operation and thus applicable for low

end to high end and low cost devices.

IEEE 1588 is typically implemented using software-based time stamping. However, software implementation delay

and jitter at the application level when packets are delivered cause problems in many cases. The best way to reduce

these problems is hardware implementation of time stamping [7- 8].

PTP’s operation principle is to exchange messages regularly in an interval to determine the offset between master

and slave but also the message transit delay through the network. Figure 1 shows how PTP messages are exchanged.

In an attempt to synchronize between two nodes, Delay and Offset should be known. Delay refers to time taken to

send a message between two nodes. Offset is the real time difference between two nodes. Delay and Offset can be

calculated using the following simple equation (1, 2).

Delay = [(t1-t2) + (t4-t3)] / 2 (1)

Offset = [(t1-t2) - (t4-t3)] / 2 (2)

© 2013 Muhammed Thaha

Figure 1.The Process of Synchronization

The slave clock requires four measured values, t1, t2, t3, t4, to calculate delay and offset. t1 and t3 are the send time

of the Synch and Delay_Req messages, t2 and t4 are the receive time of synch and delay_req messages. t2, t3 were

generated at slave side, Follow_up and Delay_Resp signals contain t1 and t4.

The PTP environment offers a verity of possible time stamp point. Stamping PTP messages accurately in physical

layer taking advantage of hardware is one of the key technologies, to achieve the objective of high precision time

synchronization.

This paper deals with the design and characterization of reconfigurable and reusable time stamping hardware unit

suitable for both master and slave, to achieve synchronization in microsecond level precision along with protocol

stack, compatible with IEEE 1588 Version1 or Version2 provides fractional microsecond range accuracy, sufficient

to stamp layer 2 and layer 4. event messages with Stacked VLAN, MPLS tags and UDP IPv4 or UDP IPv6

protocols. The hard ware unit is synthesized using Xilinx ISE ® tool implemented in Virtex6® FPGA analyzed using

Chip Scope Pro integrated logic analyzer. This paper organized as follows, section 2: Top level FSM, section 3:

Detail operation of each module, section 4: simulation and analysis results, section 5: conclusions, 6: reference.

2. Top Level FSM

Figure shows the top level finite state machine having four states: Initial state (INIT), time stamping state (STAMP),

message receiving and extraction state (PARSER) and final clock offset generation state (OFFSET).

Fig2. Top Level FSM

© 2013 Muhammed Thaha

INIT: Here provision of environment initialization by host, Offset correction of real time clock. STAMP: Time

stamping for receiving, transmitting messages. PARSER: 32 bit packet parser data path checks PTP event.

OFFSET: Offset and delay are calculated using equation (1) and (2). Use software to generate the clock offset to

achieve synchronization.

3. Hardware Implement

In this paper, the IEEE 1588 hardware is implemented with four modules, a Time Stamp, a Parser, a Real Time

Clock and a Host Interface. Figure 3 shows Top Level architecture.

Fig3. Top Level Block Diagram

A. Time Stamp

Separate Time Stamp module for receiver and transmitter, one end connected to the MII or GMII interface, by using

giga mode signal we can switch input data mode. Every cycle real time clock outs 80 bit time frame to the Time

Stamp unit. Message arrival indicated by start delimiter, it enable time stamping. Then rise valid signal for

converting 8 bit data packets to 32 bit data packets by using a data gear box.

B. parser

Parser operates on 32 bit packet size of receiving data, parser have chunk counter, it extract the receiving data entry

details belongs to different protocols layer and allows the extractor to check the condition for different stratagem to

find out PTP event message. If it satisfied, raise PTP_found high. Then extract 4bit PTP_Message_Id, 12 bit

PTP_Sequence_Id and 16 bit PTP_Check_sum are combined to form 32 bit PTP Information. This PTP

Information and Time Stamp of 80 bits are writing to receiver or transmitter FIFO. If parsed message is not a PTP

event, then burst the Time Stamp and prepare to collect other message.

C. Real Time Clock

It receives input from the system clock and generate 80 bit Time of day (TOD), one pulse per second output. 80 bit

include 48 bit second and 32 bit nanosecond field. Direct time adjustment set up, frequency set up for drift

compensation and precise time adjustment with a small time mark these are the facilities provided in RTC for

adjusting clock offset with slave and master, RTC have a power of 2^48 second time period. After computation of

offset by software stack update the system Clock, this process repeat until the slave synchronized with master

D. Host Interface

A set of 64 slice registers ordered as 32 bit in each slice offer the host interfaces, it situate environment through

update registers and drive the hardware unit in different mode with control registers, these are possible by using

protocol stack or software driver.

© 2013 Muhammed Thaha

Key Points in Implementation

PTP system with the best performance, to ensure the following:

All PTP nodes in the entire domain use the same transport protocol.

All PTP nodes in the entire domain use the same Best Master Clock algorithm.

All nodes in the domain use the same status configuration items.

All nodes in the domain use the same delay measurement mechanism.

The attributes and configurable data set members of all nodes in the system use the same default values.

The attributes of all nodes in the system have the same value range, that is, the same maximum and minimum

values.

All nodes in the domain use the same PTP template.

All nodes in the domain use the same PTP version.

Feature Description

RTC: Real Time Clock.

Standard PTP clock output with 2^48 second and 2^32 nanosecond time format.

Tunable accumulator based clock with 2^-8 and 2^-32 nanosecond time resolution period resolution.

Direct time write, with 2^-8 nanosecond resolution.

Direct frequency write, with 2^-32 nanosecond resolution.

Timed temporary time adjustment, with 2^-8 nanosecond resolution and 32bit timer.

Variety of input clock frequencies.

Clock Domain crossing hand-shaking, for SW read and write access.

TSU: Time Stamping Unit.

Two-Step PTP operation.

GMII interface monitor with line-speed PTP packet parsing.

Varieties of PTP packet formats are supported, in this fashion: Layer 2 PTP packets with stacked VLAN tags,

IPv4 UDP or IPv6 UDP PTP packet with stacked VLAN tags or stacked MPLS labels.

Configurable 8bit mask to selectively timestamp PTP event packet based on message type values, in this

manner; 0: Sync, 1: Delay_Request, 2: Pdelay_Request, 3: Pdelay_Response, 4 to 7: Reserved for future PTP

event message types

32 bit packet parser data path for easier timing closure.

15-entry timestamp queue with each entry is 128 bit; consist of 80 bit timestamp, 32bit packet identity data field

and 16 bit extra information.

Time stamping for receiving and transmitting message uses same procedure. Thus ingress and egress delays of

time Stamping unit is equal and opposite, this improve symmetry of the network.

Input Vector

Table 1: PTP message format

© 2013 Muhammed Thaha

Table1; shows the organization of input message for layer 2 and layer 4 by stacking VLAN or MPLS and UDP with

IPv4 or UDP with IPv6 protocols. Input message received from gmii or mii interface but parser unit operates on 32

bit packets. First 5 packets are PCAP header next 7 packets are used to set layer 2 or layer 4 and Packets above 14

include PTP node information’s.

4. Result of Simulation

Figure4, Shows the important case of time stamping and event message detection

Fig4. Simulation Result

Received message is Network Layer 2 event message having message id=0 (synchronous message), check

sum=0B6, sequence id =1414. Transmitted message is Network Layer 4 IPv4 UDP Event message having message

id=0 (synchronous message), check sum=114, sequence id=2121.Transmitter or receiver time stamp field is 128 bit

first 80 bit is time stamp, 32 is PTP message information and remaining 16 bit extra information

Logic Analyzer Result

Figure5, shows the Chip Scope Pro integrated logic analyzer result of time stamping and event message detection.

Figure5.Result of Logic Analyzer

© 2013 Muhammed Thaha

Received message is Network Layer 2 event message having message id=0 (synchronous message), check

sum=0B6, sequence id=1414 and 80 bit time stamp field having seconds=37sec, nanoseconds=2995B9B6nsec.

Transmitted message is Network Layer 4 IPv4, UDP event message having message id=0 (synchronous message),

Check sum=C90, sequence id=2121 and 80 bit time stamp field having seconds=36sec, nanoseconds=1BC6FE4E

nsec. Transmitter or receiver data field is 128 bit, lower 32bit is PTP message information next 80 bit field is time

stamp.

5. Conclusion

IEEE 1588 is the key protocol to providing synchronization through exchange of packets over network Objective of

hardware implement is high precision. Designing hardware that implements entire IEEE 1588 is rather complex.

This paper refers design and characterization of re configurable and re usable hardware assisted time stamping

module in Xilinx Vertex 6® FPGA with provision of software development, it works along with the protocol stack to

achieve synchronization in fractional microsecond precision. Time stamping messages in between physical and data

link layer with gmii or mii interface. To improve the symmetry of network, time stamping of receiving and

transmitting messages uses same procedure. Each module is designed with IEEE 1364 Verilog HDL and synthesized

using Xilinx ISE® tool. It is aimed to use with high end SOC architecture as re usable IP core.

Acknowledgements

We would like to thank the Institute of Electrical and Electronics Engineers (IEEE) for accepting our proposal and

funding our research.

6. Reference

[1] J.C.Eideson “Measurement, Control, and Communication Using IEEE 1588”, 2006

[2] F.Sivrikaya and B. yener,”Time synchroniza-tion in sensor networks: a survey”, Network, IEEE, vol. 18, pp.45-

50, 2004

[3] W. Lewandowski, j. Azoubib, and W.J. Klepczynski, “GPS: primary tool for time transfer,” Proceeding of the

IEEE, vol. 87, pp.163-172, 1999

[4] S. Johannessen,”Time synchronization in local area network,” control System, IEEE vol. 24 pp. 61-69, 2004.

[5] IEEE Std 1588™-2002: “IEEE Standard for a precision Clock Synchronization Protocol for Networked

Measurement and Control System”

[6] IEEE Std 1588™-2008:”IEEE Standard for a precision Clock Synchronization Protocol for Networked

Measurement and control System”

[7] D.B.H. Weibel,” IEEE 1588 Implementation and Performance of Time Stamping Techniques,” in Proceedings

of the 2004 Conference on IEEE 1588, Gaithersburg, 2004.

[8] S. Meier, H. Weibel, and K.Weber, “IEEE 1588 syntonization and Synchronization functions completely

realized in hardware," in precision Clock Synchronization for Measurement, Control and Communication,200e 8.

ISPCS 2008. IEEE International Symposium on, 2008, pp. 1-4.

© 2013 Muhammed Thaha

You might also like

- Protocol IEC 60870 5 104 MasterDocument12 pagesProtocol IEC 60870 5 104 MasterNguyễn NamNo ratings yet

- Uvm CookbookDocument547 pagesUvm CookbookShalini Priya100% (4)

- Asme B18.24-2020Document190 pagesAsme B18.24-2020윤규섭0% (1)

- Home BMW F11 530D Xdrive Touring Wiring Diagrams and Functional DescriptionDocument1 pageHome BMW F11 530D Xdrive Touring Wiring Diagrams and Functional DescriptionOliver AlfaroNo ratings yet

- PEOPLE IN MY TOWN - Song Worksheet PAULA 2019Document2 pagesPEOPLE IN MY TOWN - Song Worksheet PAULA 2019PauNo ratings yet

- Transparent Clock WhitepaperDocument19 pagesTransparent Clock WhitepaperUjjwal MaghaiyaNo ratings yet

- Yin Et Al. - 2018 - The Implementation of IEEE 1588 Clock Synchronization Protocol BaseDocument6 pagesYin Et Al. - 2018 - The Implementation of IEEE 1588 Clock Synchronization Protocol Base张奔No ratings yet

- Risk Analysis and Research Based On IEEE 1588 in Smart High Voltage SubstationDocument7 pagesRisk Analysis and Research Based On IEEE 1588 in Smart High Voltage SubstationDazahra Med NouhNo ratings yet

- Cisco DS 1Document25 pagesCisco DS 1CARLOSALBERTONo ratings yet

- Information About Precision Time ProtocolDocument16 pagesInformation About Precision Time ProtocolShareef KoyaNo ratings yet

- Implementation Modeling and Simulation of PTP Stacks: C. Gahane, D.Triupathi RaoDocument5 pagesImplementation Modeling and Simulation of PTP Stacks: C. Gahane, D.Triupathi RaoIJSREDNo ratings yet

- Precision Time Protocol (PTP) New VersionDocument14 pagesPrecision Time Protocol (PTP) New Versionnaman guptaNo ratings yet

- Cisco PTPDocument22 pagesCisco PTPMel7it87No ratings yet

- Ieee 1588v2 PTPDocument24 pagesIeee 1588v2 PTPhas100% (1)

- PTP Feature Overview Guide RevbDocument17 pagesPTP Feature Overview Guide RevbdummihaiNo ratings yet

- Cambium PTP650 Precsion Timing WhitePaperDocument11 pagesCambium PTP650 Precsion Timing WhitePaperAla'a AbdullaNo ratings yet

- SNTP Driven Event Management To Control Audio/Video/Buzzer Events by Using Streaming Media PlayerDocument4 pagesSNTP Driven Event Management To Control Audio/Video/Buzzer Events by Using Streaming Media Playersurendiran123No ratings yet

- Precision Clock Synchronization WP PDFDocument20 pagesPrecision Clock Synchronization WP PDFtimeking00No ratings yet

- Reloj Sync PTPDocument24 pagesReloj Sync PTPAngel ColindresNo ratings yet

- Best Practices For IEEE 1588/ PTP Network DeploymentDocument7 pagesBest Practices For IEEE 1588/ PTP Network DeploymentarzeszutNo ratings yet

- Network Time ProtocolDocument19 pagesNetwork Time Protocoljayanth_babluNo ratings yet

- white rabbitDocument4 pageswhite rabbithalisahaseefiNo ratings yet

- Microsemi Synchronization For Next Generation Networks White PaperDocument19 pagesMicrosemi Synchronization For Next Generation Networks White PaperasdfghjklasdfghjklNo ratings yet

- Synchronization For High Frequency Trading Networks ADocument7 pagesSynchronization For High Frequency Trading Networks Aspamaccount2No ratings yet

- Ieee 1588Document5 pagesIeee 1588raghavendran raghuNo ratings yet

- R01an0767eu sh7216Document13 pagesR01an0767eu sh7216mamathaursNo ratings yet

- A Simulation Model of IEEE 802Document6 pagesA Simulation Model of IEEE 802Durgesh AggarwalNo ratings yet

- Exhaust Fan Switch: The NTP StandardDocument3 pagesExhaust Fan Switch: The NTP StandardmanuNo ratings yet

- IEEE 1588v2: A Look at Time and Frequency SynchronizationDocument4 pagesIEEE 1588v2: A Look at Time and Frequency SynchronizationhasantonmoyNo ratings yet

- Assignment 4: Real Time System and SoftwareDocument9 pagesAssignment 4: Real Time System and SoftwareSurendra Singh ChauhanNo ratings yet

- Cisco - Ethernet OAM PTP TutorialDocument22 pagesCisco - Ethernet OAM PTP TutorialSkanda PrasadNo ratings yet

- PTP Best Practices For Media and Entertainment and Broadcast CentersDocument16 pagesPTP Best Practices For Media and Entertainment and Broadcast CentersSukrit ChaudharyNo ratings yet

- Ee 549 Undergraduate Project Ii: "Voip To PSTN Converter"Document30 pagesEe 549 Undergraduate Project Ii: "Voip To PSTN Converter"Obaweya SeyiNo ratings yet

- Research Paper Omnet++Document5 pagesResearch Paper Omnet++irfanmaoNo ratings yet

- Block Level Design Implementation of 100 Mbps Ethernet Telemetry Using Vivado TEMAC IP Core in Artix-7Document7 pagesBlock Level Design Implementation of 100 Mbps Ethernet Telemetry Using Vivado TEMAC IP Core in Artix-7International Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Esp8266 Gps NTP Stratum1 ServerDocument48 pagesEsp8266 Gps NTP Stratum1 ServerthitiponsNo ratings yet

- Time Synchronization Using ABB RelaysDocument6 pagesTime Synchronization Using ABB RelayssujithmohandasNo ratings yet

- Timing and Sync Over PSNDocument48 pagesTiming and Sync Over PSNmeo_omhtNo ratings yet

- Unit 6 CS 2204 AssignmentDocument2 pagesUnit 6 CS 2204 AssignmentZodwa MngometuluNo ratings yet

- 0-Gist of Industrial NetworkingDocument12 pages0-Gist of Industrial NetworkingsuritataNo ratings yet

- Info - Lantime m300 Gps PDFDocument5 pagesInfo - Lantime m300 Gps PDFvdaNo ratings yet

- The PTP Telecom Profiles For Frequency, Phase and Time SynchronizationDocument30 pagesThe PTP Telecom Profiles For Frequency, Phase and Time Synchronizationalmel_09No ratings yet

- MPC5xxx Programming The eTPUDocument14 pagesMPC5xxx Programming The eTPUSAABNo ratings yet

- Som (System On Module) Based Count Down Time Distribution and Reception UnitDocument6 pagesSom (System On Module) Based Count Down Time Distribution and Reception UnitTJPRC PublicationsNo ratings yet

- TAP (Telocator Alphanumeric Protocol) Specification v1 - 8Document27 pagesTAP (Telocator Alphanumeric Protocol) Specification v1 - 8skyhighsmileNo ratings yet

- Ieee 1588 Implementation On A Coldfire Processor: Application NoteDocument22 pagesIeee 1588 Implementation On A Coldfire Processor: Application NoteSenthil NathanNo ratings yet

- Kyland WhitePaper IEEE1588 ENDocument19 pagesKyland WhitePaper IEEE1588 ENNaidely Coral Geraldo OjedaNo ratings yet

- Physical Layer Ethernet Clock SynchronizationDocument12 pagesPhysical Layer Ethernet Clock SynchronizationicovinyNo ratings yet

- Clock Synchronization of PTP-based Devices Through PROFINET IO NetworksDocument4 pagesClock Synchronization of PTP-based Devices Through PROFINET IO NetworksBiplab TNo ratings yet

- A Design of Network Remote Control SystemDocument4 pagesA Design of Network Remote Control SystemPurush ArunNo ratings yet

- Amm Cheet PrintDocument7 pagesAmm Cheet PrintjokerNo ratings yet

- Meiberg LANTIME M900: Customizable NTP Timeserver PlatformDocument5 pagesMeiberg LANTIME M900: Customizable NTP Timeserver Platformborc2mNo ratings yet

- Stream Control Transmission Protocol (SCTP) : Robust and Efficient For Data Centre ApplicationsDocument5 pagesStream Control Transmission Protocol (SCTP) : Robust and Efficient For Data Centre ApplicationsIJEECSNo ratings yet

- Design of The Data Acquisition System Based On STM32: Information Technology and Quantitative Management (ITQM2013)Document7 pagesDesign of The Data Acquisition System Based On STM32: Information Technology and Quantitative Management (ITQM2013)Nguyễn Trọng TuyếnNo ratings yet

- Option34 NTP PTPDocument2 pagesOption34 NTP PTPMauricio AbregúNo ratings yet

- Option34 NTP PTP PDFDocument2 pagesOption34 NTP PTP PDFMauricio AbregúNo ratings yet

- LANTIME M300/GPS: NTP Time Server With Integrated GPS Radio ClockDocument5 pagesLANTIME M300/GPS: NTP Time Server With Integrated GPS Radio Clockjavier-jhaNo ratings yet

- Info Lantime m900 GpsDocument5 pagesInfo Lantime m900 GpsmacjolasNo ratings yet

- Energy Data ConcentratorDocument2 pagesEnergy Data ConcentratoradenijisegunNo ratings yet

- Tci6630k2l DatasheetDocument297 pagesTci6630k2l DatasheetShashank S. PrasadNo ratings yet

- Simulation of Ether SwitchDocument4 pagesSimulation of Ether SwitchvibhorkrnitrklNo ratings yet

- @@TETRA ReferencesDocument18 pages@@TETRA ReferencesmicrajacutNo ratings yet

- Realization of IEC 60870-5-104 Protocol in DTUDocument6 pagesRealization of IEC 60870-5-104 Protocol in DTUKalyan RanjanNo ratings yet

- Practical Data Acquisition for Instrumentation and Control SystemsFrom EverandPractical Data Acquisition for Instrumentation and Control SystemsNo ratings yet

- APT60D60BG DatasheetDocument9 pagesAPT60D60BG DatasheetirfanmaoNo ratings yet

- Profile IrfanDocument2 pagesProfile IrfanirfanmaoNo ratings yet

- UVM Tips TricksDocument36 pagesUVM Tips TricksirfanmaoNo ratings yet

- QuestaSIM GuideDocument3 pagesQuestaSIM GuideirfanmaoNo ratings yet

- SV - PerformanceGuidelines - Verification AcademyDocument19 pagesSV - PerformanceGuidelines - Verification AcademyirfanmaoNo ratings yet

- SV GuideDocument14 pagesSV GuideirfanmaoNo ratings yet

- Qadir ListDocument1 pageQadir ListirfanmaoNo ratings yet

- MAC Layer PaperDocument5 pagesMAC Layer PaperirfanmaoNo ratings yet

- Research Paper Omnet++Document5 pagesResearch Paper Omnet++irfanmaoNo ratings yet

- Ug FifoDocument33 pagesUg FifoirfanmaoNo ratings yet

- LUMS PresentationDocument31 pagesLUMS PresentationirfanmaoNo ratings yet

- Final DraftDocument35 pagesFinal DraftirfanmaoNo ratings yet

- Presentation IrfanDocument32 pagesPresentation IrfanirfanmaoNo ratings yet

- Pub1308 WebDocument193 pagesPub1308 WebyucemanNo ratings yet

- Pavements ConstructedDocument16 pagesPavements ConstructedjoryNo ratings yet

- Perlis V. Composer's Voices From Ives To Ellington PDFDocument506 pagesPerlis V. Composer's Voices From Ives To Ellington PDFOleksii Ternovii100% (1)

- Student quiz answer sheetsDocument26 pagesStudent quiz answer sheetsSeverus S PotterNo ratings yet

- Consumer Reports Buying Guide 2021Document227 pagesConsumer Reports Buying Guide 2021fatso68100% (1)

- Chapter 2Document5 pagesChapter 2Ayush Hooda class 12 ANo ratings yet

- Forum Ex 2 2Document5 pagesForum Ex 2 2Didan EnricoNo ratings yet

- Understanding Arthrogyposis Multiplex Congenita and Muscular DystrophiesDocument38 pagesUnderstanding Arthrogyposis Multiplex Congenita and Muscular DystrophiessmrutiptNo ratings yet

- CEO Corner New Products Powerful Pocket SimulatorDocument23 pagesCEO Corner New Products Powerful Pocket SimulatorMOHAMMA MUSANo ratings yet

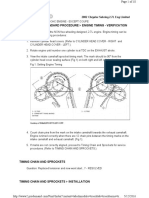

- 02+sebring+2.7+timing+chainDocument10 pages02+sebring+2.7+timing+chainMaushil Salman MarkNo ratings yet

- dgx670 Es Om b0Document116 pagesdgx670 Es Om b0rafael enrique cely rodriguezNo ratings yet

- Sustainability - Research PaperDocument18 pagesSustainability - Research PapermrigssNo ratings yet

- Research Trends On Environmental Energy and Vulnerability - 2021 - Energy andDocument27 pagesResearch Trends On Environmental Energy and Vulnerability - 2021 - Energy andCynthia Mac-beathNo ratings yet

- Piano: Grade 2: PiecesDocument4 pagesPiano: Grade 2: PiecesnolozeNo ratings yet

- Quickguide Students For CopyrightsDocument2 pagesQuickguide Students For Copyrightslordvorldomort100% (1)

- Breaugh Starke PDFDocument30 pagesBreaugh Starke PDFRichard YeongNo ratings yet

- Pharmacy Perspective on Improving Patient SafetyDocument44 pagesPharmacy Perspective on Improving Patient SafetydicodrNo ratings yet

- Orphanage Cum Old Age Home: Amruta Prakash BedmuthaDocument2 pagesOrphanage Cum Old Age Home: Amruta Prakash BedmuthaNamrata Bhandari100% (1)

- Kristine Jane T. Zipagan Assignment: 1. Parts of InfographicsDocument2 pagesKristine Jane T. Zipagan Assignment: 1. Parts of InfographicsChristyNo ratings yet

- MIT LL. Target Radar Cross Section (RCS)Document45 pagesMIT LL. Target Radar Cross Section (RCS)darin koblickNo ratings yet

- Filed & Entered: SBN 143271 SBN 165797 SBN 259014Document8 pagesFiled & Entered: SBN 143271 SBN 165797 SBN 259014Chapter 11 DocketsNo ratings yet

- PIRA - 2022 - ESTIMATED FMV As of October 2022Document48 pagesPIRA - 2022 - ESTIMATED FMV As of October 2022Aggy ReynadoNo ratings yet

- Tata Steel-MDP SessionDocument69 pagesTata Steel-MDP Sessionsasharma82No ratings yet

- Labcir - Marwa - FinalDocument119 pagesLabcir - Marwa - FinalMashavia AhmadNo ratings yet

- Cognitive Load Theory (John Sweller) : Information ProcessingDocument2 pagesCognitive Load Theory (John Sweller) : Information ProcessingNik ZazlealizaNo ratings yet

- Som-Ii Uqb 2019-20Document23 pagesSom-Ii Uqb 2019-20VENKATESH METHRINo ratings yet

- Robert K Boscarato and Matthew Skaggs Corprate Credit Book Draft 1.Document70 pagesRobert K Boscarato and Matthew Skaggs Corprate Credit Book Draft 1.Robert BoscaratoNo ratings yet