Professional Documents

Culture Documents

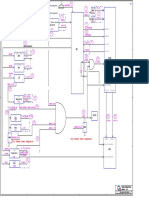

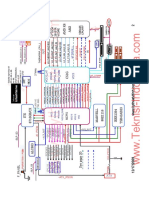

Quanta DA0QU8MB6G1 Lenovo ThinkCentre A70z 5

Quanta DA0QU8MB6G1 Lenovo ThinkCentre A70z 5

Uploaded by

ougeyfOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Quanta DA0QU8MB6G1 Lenovo ThinkCentre A70z 5

Quanta DA0QU8MB6G1 Lenovo ThinkCentre A70z 5

Uploaded by

ougeyfCopyright:

Available Formats

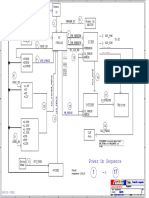

8 7 6 5 4 3 2 1

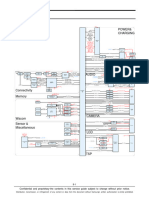

power on Sequence

SLP_M#, M3 ON

D D

+P5V_ALWAYS/+P3V3_ALWAYS

From battery

9ms

RTC_VDD

SLP_S4_N 30us,min

From battery

FM_RTCRST_N

SLP_S3_N

SLP_M# could come up as early as before SLP_S4#/SLP_S5#

+P5V_ALWAYS ICH_SLP_M# or as late as SLP_S3#,but no later.

+P1P05V_ME(VccME,VccLAN)

+P3V3_ALWAYS

From EC to Power Bottom

+VCC3_ME

PWRBTSW#

From EC PCH_MEPWROK_R/LAN_PWROK

500us,min

S5_PWRON

SPI FLASH

+P5V_S5/+P3V3_S5

From EC to PCH

10ms

PCH_REMRST_N

From PCH to EC

C

SLP_S4_N

VGA_IN C

From PCH to EC

30us,min

SLP_S3_N

From PCH VGA_PRESENT

30us,min

ICH_SLP_M

From EC

EC_Panel_ON

+VCC3_ME/+P1P05V_ME

From EC to DDR power module +P12V_monitor

SUSON

+P5V_monitor

P5V_DDR_S3/+DDR1V5_S3 30us,min

From EC +P3V_monitor

MAINON

+P12V_S0/+P5V_S0/+P3V3_S0

+P1V05_PCH_S0/CPU_VTT_S0+

+VCC1_8_PCH_S0 From NCP5380 Voltage Rails

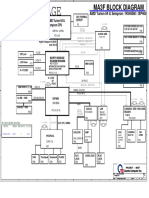

Power Voltage S0~S2 S3 S4 S5 Ctl Signal

V_AXG_S0 5V

+P5V_ALWAYS V V V V

B

From VTT power module to CPU B

3.3V V V V V

+P3V3_ALWAYS

H_VTTPWRGD

+P5V_S5 5V V V V V S5_PWRON

3.3V V V S5_PWRON

From Vcore power module to CPU +P3V3_S5

VCORE_S0 +VCC3_ME 3V V V ME_G

+P1P05V_ME 1.05V V V ICH_SLP_M

P5V_DDR_S3 5V V SUSD/MAINON

From Vcore power module to CLK,PCH

VRMPWRGD(PCH_SYSPWROK/CKPWRGD) +DDR1V5_S3 1.5V V SUSD/MAINON

+P12V_S0 12V V MAINON

99ms From EC to PCH +P5V_S0 5V V MAINON

SIO_PWRGD_3V/PWRGD_3V +P3V3_S0 3.3V V MAINON

+VCC1_8_PCH_S0 1.8V V MAINON

From PCH P15V 15V V MAINON

1ms

+P1V05_PCH_S0 1.05V V MAINON

PCH_MEPWROK_R/LAN_PWROK CPU_VTT_S0+ 1.1V MAIN0N

V

V_AXG_S0

1ms From PCH to CPU 1.1 V CPU_VTT_S0+

VCORE_S0 1.1 H_VTTPWRGD

H_DRAMPWRGD

V

+P12V_monitor 12V EC_Panel_ON

V

+P5V_monitor EC_Panel_ON

5V V

From PCH to CPU

100ms +P3V_monitor EC_Panel_ON

3V V

H_PWRGD

From PCH to TPM

SUS_TAT_N 1ms

A

From PCH A

60us

PLTRST_N

Quanta Computer Inc.

PROJECT : QU8

Size Document Number Rev

D

Power Diagram

Date: Monday, January 25, 2010 Sheet 5 of 37

8 7 6 5 4 3 2 1

You might also like

- Desktop - Power Sequence PDFDocument8 pagesDesktop - Power Sequence PDFআশিক সরকার100% (1)

- Sm-G970u SVC ManualDocument50 pagesSm-G970u SVC Manualasish dalalNo ratings yet

- sx460 Conversion ChartDocument1 pagesx460 Conversion ChartBrianHaze100% (4)

- Radial Arm Saw ManualDocument86 pagesRadial Arm Saw ManualdanstraussNo ratings yet

- ASUS A8E A8S F8S Power On SequenceDocument1 pageASUS A8E A8S F8S Power On SequenceEduinMaracuchoFernandezChaparroNo ratings yet

- Quanta Y01 Shark Bay Power SequenceDocument1 pageQuanta Y01 Shark Bay Power SequenceJoselo LópezNo ratings yet

- Samsung RV408 6 - BA41-01335A 01334A 01336ADocument1 pageSamsung RV408 6 - BA41-01335A 01334A 01336AHumberto AndujarNo ratings yet

- Quanta Jm3 Power Sequence Rev 02Document37 pagesQuanta Jm3 Power Sequence Rev 02u6k5lp l2y3z0No ratings yet

- P5kpl-Am Se PDFDocument4 pagesP5kpl-Am Se PDFMariusz KaźmierczakNo ratings yet

- SONY VGN-FZ MBX-165 ms90 - Power Sepuence - v05 - 20070227Document4 pagesSONY VGN-FZ MBX-165 ms90 - Power Sepuence - v05 - 20070227HerryNo ratings yet

- Sony Mbx-165 Ms90 - Power SequenceDocument4 pagesSony Mbx-165 Ms90 - Power SequenceMitecnomundosweb mitecnomundoswebNo ratings yet

- Acer Extensa 4220 4620 - WISTRON BIWA - POWER SEQUENCE PDFDocument1 pageAcer Extensa 4220 4620 - WISTRON BIWA - POWER SEQUENCE PDFLas DusNo ratings yet

- Quanta jm3Document37 pagesQuanta jm3CADASEDANo ratings yet

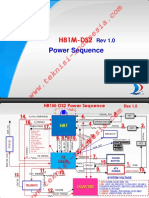

- H81M-DS2: Power SequenceDocument2 pagesH81M-DS2: Power SequenceHilario Serrano Flores100% (3)

- Mu5dc CH7DC (Rev 2.0)Document86 pagesMu5dc CH7DC (Rev 2.0)aka.virtuozNo ratings yet

- 0c323 QUANTA SA1 PDFDocument42 pages0c323 QUANTA SA1 PDFMatias GuillenNo ratings yet

- B460 Power Up SequenceDocument1 pageB460 Power Up Sequenceحسن علي نوفلNo ratings yet

- Vinafix - VN K43E RGDocument11 pagesVinafix - VN K43E RGdinnhowNo ratings yet

- Blok DiagramDocument1 pageBlok DiagramMuhammad MaimanaNo ratings yet

- GT-S5300 Service ManualDocument47 pagesGT-S5300 Service ManualNo-OneNo ratings yet

- Giga Luoc Do Kich NguonDocument2 pagesGiga Luoc Do Kich NguonNguyễn Văn TặngNo ratings yet

- Giga Luoc Do Kich NguonDocument2 pagesGiga Luoc Do Kich NguonĐiện LươngNo ratings yet

- Euro Designcon 2005Document23 pagesEuro Designcon 2005sumitbahetiNo ratings yet

- Quanta SA1Document42 pagesQuanta SA1Евгений АвазачемNo ratings yet

- Lenovo ThinkPad L410 Quanta R410 G-Note Montevina Rev1A SchematicDocument46 pagesLenovo ThinkPad L410 Quanta R410 G-Note Montevina Rev1A SchematicElvis AlejosNo ratings yet

- Gigabytes Training MotherboardDocument16 pagesGigabytes Training MotherboardsttecnicoNo ratings yet

- SM-G960U Tshoo 7Document50 pagesSM-G960U Tshoo 7valentinotyperNo ratings yet

- GT I9060i TSHOO 7Document47 pagesGT I9060i TSHOO 7Jamir Ramírez100% (1)

- Rome2 Apollo Power On SequenceDocument14 pagesRome2 Apollo Power On SequenceMabrouk Med AliNo ratings yet

- Level 3 Repair: Power& ChargingDocument41 pagesLevel 3 Repair: Power& ChargingFacundo SianNo ratings yet

- Troubleshooting PDFDocument45 pagesTroubleshooting PDFzdiciNo ratings yet

- Desktop Power Sequence 4 PDF FreeDocument8 pagesDesktop Power Sequence 4 PDF FreeAhmad Syafii LeongNo ratings yet

- SM-G610S Esquematico Completo Anibal Garcia IrepairDocument1 pageSM-G610S Esquematico Completo Anibal Garcia IrepairJoão Márlon MonteiroNo ratings yet

- Level 3 Repair: 8-1. Components LayoutDocument54 pagesLevel 3 Repair: 8-1. Components LayoutCarlos SilvaNo ratings yet

- ) Ljxuh 6Wr67Lplqj'Ldjudp: Electrical CharacteristicsDocument1 page) Ljxuh 6Wr67Lplqj'Ldjudp: Electrical Characteristicsady putraNo ratings yet

- SM-G550T Tshoo 7 PDFDocument36 pagesSM-G550T Tshoo 7 PDFWilliam SequeraNo ratings yet

- P&O MPPT Implementation Using MATLAB/SimulinkDocument4 pagesP&O MPPT Implementation Using MATLAB/SimulinkAmer SabanovicNo ratings yet

- Kim Uno Rev1 SchematicDocument1 pageKim Uno Rev1 SchematicweaponNo ratings yet

- TroubleshootingDocument47 pagesTroubleshootingEliel RodriguesNo ratings yet

- Diagrama Samsung E5Document90 pagesDiagrama Samsung E5RayNo ratings yet

- Level 3 Repair: 8-1. Components LayoutDocument30 pagesLevel 3 Repair: 8-1. Components LayoutAndroid Schematics and CircuitsNo ratings yet

- Preliminary: 6-Channel Audio Processor ICDocument18 pagesPreliminary: 6-Channel Audio Processor ICВлад ВолошинNo ratings yet

- IBM Thinkpad Z61 (Quanta BW2)Document80 pagesIBM Thinkpad Z61 (Quanta BW2)Maks ProstNo ratings yet

- Gigabyte - Mobo TrainningDocument17 pagesGigabyte - Mobo TrainningEverton DoradoNo ratings yet

- Gigabyte - Mobo TrainningDocument17 pagesGigabyte - Mobo Trainningablacon64No ratings yet

- K46CM Repair Guide: Jul/23/2012 John - Jin Csc-GrmaDocument5 pagesK46CM Repair Guide: Jul/23/2012 John - Jin Csc-Grmaanas symbianNo ratings yet

- Block Diagram: Intel P4P-MDocument58 pagesBlock Diagram: Intel P4P-Ms24.ysshinNo ratings yet

- P5100 Troubleshooting PDFDocument72 pagesP5100 Troubleshooting PDFDaniel CekulNo ratings yet

- Asus Repair LESSON 2 - CLOCKDocument13 pagesAsus Repair LESSON 2 - CLOCKHerryNo ratings yet

- Quanta KW3 - Rev ADocument36 pagesQuanta KW3 - Rev ANDCENo ratings yet

- Gateway mt6451 Quanta Ma3f Rev 1a SCHDocument35 pagesGateway mt6451 Quanta Ma3f Rev 1a SCHJavierCarreonHernandezNo ratings yet

- Power Up SequenceDocument30 pagesPower Up SequenceLshoppe BaripadaNo ratings yet

- Static Var CompensatorDocument6 pagesStatic Var Compensatoralexandre_foxtrotNo ratings yet

- A60 (Sm-A6060)Document30 pagesA60 (Sm-A6060)Jhonn arcilaNo ratings yet

- Sample Mapping DocumentDocument40 pagesSample Mapping Documentvenkata ganga dhar gorrelaNo ratings yet

- Calpella Switchable Graphic BLOCK DIAGRAM: IntelDocument47 pagesCalpella Switchable Graphic BLOCK DIAGRAM: IntelreynielNo ratings yet

- Plano Esquemático de SM-G610FDocument45 pagesPlano Esquemático de SM-G610FCarlos NaaboaanyNo ratings yet

- Quanta DA0NL8MB8E0 49Document1 pageQuanta DA0NL8MB8E0 49ougeyfNo ratings yet

- Compal LA-5811P 59Document1 pageCompal LA-5811P 59ougeyfNo ratings yet

- Quanta DAKL2FMB8F0 Lenovo Y460P 2Document1 pageQuanta DAKL2FMB8F0 Lenovo Y460P 2ougeyfNo ratings yet

- Apple MacBook Pro - A1278 - J30 - 820-3115 3Document1 pageApple MacBook Pro - A1278 - J30 - 820-3115 3ougeyfNo ratings yet

- Wistron AG1 - SA - Acer Duo Core Power On SequenceDocument10 pagesWistron AG1 - SA - Acer Duo Core Power On SequenceougeyfNo ratings yet

- Analog Circuits in 28 NM and 14 NM Finfet: Lukas Dörrer, Franz Kuttner, Francesco Conzatti, and Patrick TortaDocument15 pagesAnalog Circuits in 28 NM and 14 NM Finfet: Lukas Dörrer, Franz Kuttner, Francesco Conzatti, and Patrick TortaRodrigo SantosNo ratings yet

- Cas Ford TutorialDocument16 pagesCas Ford TutorialMicu Adrian Danut100% (1)

- Embedded Systems Unit IVDocument11 pagesEmbedded Systems Unit IVSreekanth PagadapalliNo ratings yet

- 8085 Interrupts - GDLCDocument36 pages8085 Interrupts - GDLCWilliamNo ratings yet

- Predictive Costing - Application Possibilities For Artificial Intelligence in Cost ManagementDocument3 pagesPredictive Costing - Application Possibilities For Artificial Intelligence in Cost ManagementPR.comNo ratings yet

- Hard Switched Push-Pull Topology: S.No. Name of The Sub-Title Page NoDocument26 pagesHard Switched Push-Pull Topology: S.No. Name of The Sub-Title Page NoEdilsonNo ratings yet

- JN RM 2001 Integrated Peripherals API 3v1Document288 pagesJN RM 2001 Integrated Peripherals API 3v1Fatih OkuyucuNo ratings yet

- Computer Architecture and Organization: Lecture16: Cache PerformanceDocument17 pagesComputer Architecture and Organization: Lecture16: Cache PerformanceMatthew R. PonNo ratings yet

- Ds Plantronics Blackwire 5200 PDFDocument2 pagesDs Plantronics Blackwire 5200 PDFDidi SuryadiNo ratings yet

- VTS User's Guide 4.6Document176 pagesVTS User's Guide 4.6vkky2k8120No ratings yet

- Atomic Number Element SymbolDocument4 pagesAtomic Number Element SymbolPaneyNo ratings yet

- NTA5332 - NTAG 5 Boost - 544733 - Rev33Document133 pagesNTA5332 - NTAG 5 Boost - 544733 - Rev33SuBaRu GTNo ratings yet

- Texas - Instruments LM2940CT 5.0 - NOPB DatasheetDocument20 pagesTexas - Instruments LM2940CT 5.0 - NOPB Datasheetcarlos duranNo ratings yet

- Arc Welding (SMAW)Document89 pagesArc Welding (SMAW)Muniba ArifNo ratings yet

- Nikon Speedlight SB-22s ManualDocument2 pagesNikon Speedlight SB-22s ManualAleksi LaustiNo ratings yet

- 0.992.060 Betriebsanleitung HM 850 GB V 6.03Document49 pages0.992.060 Betriebsanleitung HM 850 GB V 6.03sunanNo ratings yet

- MAIN Electrical Parts List: FirmwareDocument5 pagesMAIN Electrical Parts List: FirmwareServi-vent MorenoNo ratings yet

- Field-Effect Transistor: "FET" Redirects Here. For Other Uses, SeeDocument8 pagesField-Effect Transistor: "FET" Redirects Here. For Other Uses, Seejoneljavier002No ratings yet

- Air Force Power Supply (AFJMAN 32-1080)Document122 pagesAir Force Power Supply (AFJMAN 32-1080)EngSrakNo ratings yet

- Zelio Logic SR2B121BDDocument2 pagesZelio Logic SR2B121BDDinesh BabuNo ratings yet

- HVAC Questions 100+ PDFDocument12 pagesHVAC Questions 100+ PDFabdullahNo ratings yet

- The InductorDocument67 pagesThe Inductorleonard1971No ratings yet

- Sony Xperia S LT26i Service ManualDocument90 pagesSony Xperia S LT26i Service ManualFernando IglesiasNo ratings yet

- Hawke Gland CatalogueDocument81 pagesHawke Gland CatalogueLenzy Andre Famela100% (1)

- Senzori Miscare EnglDocument16 pagesSenzori Miscare EnglCristian GodeanuNo ratings yet

- My Wrks NCMT IncmpltDocument17 pagesMy Wrks NCMT IncmpltUnni HaridasNo ratings yet

- BZSLO NXT 24L LED WH SD-113565-220VDCDocument1 pageBZSLO NXT 24L LED WH SD-113565-220VDCAwnish KumarNo ratings yet

- Syllabus&Reference Text BooksDocument4 pagesSyllabus&Reference Text BooksRamakrishnaRao SoogooriNo ratings yet