Professional Documents

Culture Documents

As19 h1g

Uploaded by

Piter De AzizOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

As19 h1g

Uploaded by

Piter De AzizCopyright:

Available Formats

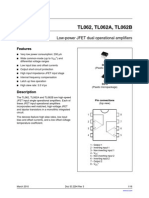

EC5579

18+1 Channel Voltage Buffers for TFT LCD

Introduction Features

General Description Wide supply voltage range 6.5V ~ 18V

The EC5579 is a 18+1 channel voltage buffers that Rail-to-rail output swing (The highest two stage &

buffers reference voltage for gamma correction in a lowest two stage)

thin film transistor liquid crystal display (TFT LCD). High slew rate 1V/μs

This device incorporating a Vcom amplifier circuits, GBWP 1 MHz

four rail to rail buffer amplifier circuits (the highest 2 MHz -3dB Bandwidth

two stage and lowest two stage) and 14 buffer Large Vcom Drive Current: ±100mA(Max)

amplifiers circuits. Ultra-small Package TQFP-48

The EC5579 is available in a space saving 48-pin

TQFP package, and the operating temperature is Applications

from –20°C to +85°C. TFT-LCD Reference Driver

Pin Configuration

A,B,Q,R: Rail to Rail OPAMPs

E-CMOS Corp. (www.ecmos.com.tw) Page 1 of 12 2007/06/29

EC5579

18+1 Channel Voltage Buffers for TFT LCD

Ordering/Marking Information

Package Part Number Marking Marking Information

EC5579-F AS19-F Lead free

EC5579-G AS19-G Green Mode

EC5579-HF AS19-HF Lead free with exposed pad (3.05x3.05 mm)

TQFP 48

EC5579-HG AS19-HG Green Mode with exposed pad (3.05x3.05 mm)

EC5579E-H1F AS19-H1F Lead free with exposed pad (5.0x5.0 mm)

EC5579E-H1G AS19-H1G Green Mode with exposed pad (5.0x5.0 mm)

Ordering Information

EC5579

EC5579XX -- X

XXX

F: Lead-Free

G:Green Mode

H: Exposed pad (3.05x3.05 mm)

H1: Exposed pad (5.0x5.0 mm)

E: Package type : TQFP48

Package Marking Indication

AS19-XX

Date Code

Lot. Number

E-CMOS Corp. (www.ecmos.com.tw) Page 2 of 12 2007/06/29

EC5579

18+1 Channel Voltage Buffers for TFT LCD

Absolute Maximum Ratings (TA=25°C)

Values beyond absolute maximum ratings may cause permanent damage to the device. These are stress ratings only;

functional device operation is not implied. Exposure to AMR conditions for extended periods may affect device reliability.

Parameter Symbol Value Unit

Supply Voltage between VS+ and VS- Vs +18 V

Input Voltage — Vs- -0.5 V

(For rail to rail) — Vs+ +0.5 V

Maximum Output Current (A ~ R Buffers) Iout ±30 mA

Maximum Output Current (Com Buffer) Iout(com) ±100 mA

Maximum junction Temperature TJ +150 °C

Storage Temperature Range TSTG -65 to +150 °C

Operating Temperature Range TOP -20 to +85 °C

Lead temperature Tlead 260 °C

ESD Voltage — 2 KV

Important Note:

All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only.

Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore: TJ = TC = TA

E-CMOS Corp. (www.ecmos.com.tw) Page 3 of 12 2007/06/29

EC5579

18+1 Channel Voltage Buffers for TFT LCD

Electrical Characteristics

VS+= +5V, VS - = -5V, RL = 10kΩ and CL = 10pF to 0V, TA = 25°C unless otherwise specified.

Parameter Description Condition Min Typ Max Units

Input Characteristics

VOS Input Offset Voltage VCM= 0V — 2 12 mV

TCVOS Average Offset Voltage Drift [1] — 5 — µV/°C

IB Input Bias Current VCM= 0V — 2 50 nA

RIN Input Impedance — — 1 — G

CIN Input Capacitance — — 1.35 — pF

Output Characteristics

VOL Output Swing Low IL= -5mA (A, B, Q, R rail-to-rail Buffers) -4.92 -4.85 V

VOH Output Swing High IL= 5mA (A, B, Q, R rail-to-rail Buffers) 4.85 4.92 — V

VOL Output Swing Low IL= -5mA (C ~ P Buffers) -3.5 — — V

VOH Output Swing High IL= 5mA (C ~ P Buffers) 3.5 — — V

ISC Short Circuit Current (A ~ R Buffers) — ±120 — mA

IOUT Output Current (A ~ R Buffers) — ±30 — mA

ISC(Com) Short Circuit Current (Com Buffer) — ±300 — mA

IOUT(Com) Output Current (Com Buffer) — ±100 — mA

Power Supply Performance

PSRR Power Supply Rejection Ratio VS is moved from ±3.25V to ±7.75V 60 80 — dB

IS Supply Current (Per Amplifier) No Load (A ~ R Buffers) — 500 750 µA

IS(Com) Supply Current (Com Buffer) — 8 — mA

Dynamic Performance

SR Slew Rate [2] -4.0V≦VOUT≦4.0V, 20% to 80% — 1 — V/µs

tS Settling to +0.1% (AV = +1) (AV = +1), VO=2V Step — 5 — µs

BW -3dB Bandwidth RL = 10KΩ, CL = 10PF — 2 — MHz

PM Phase Margin RL = 10KΩ, CL = 10PF — 60 — Degrees

CS Channel Separation f = 1 MHz — 75 — dB

1. Measured over operating temperature range

2. Slew rate is measured on rising and falling edges

E-CMOS Corp. (www.ecmos.com.tw) Page 4 of 12 2007/06/29

EC5579

18+1 Channel Voltage Buffers for TFT LCD

Typical Performance Characteristics

VCC = 10V, F: 10K

VCC = 10V, F: 10K VCC = 10V, F: 1K

Figure3. Rail to Rail Capability Figure4. Large Signal Transient Response

VCC = 10V, F: 1K VCC = 10V, F: 1K

Figure5. Large Signal Transient Response Figure6. Small Signal Transient Response

E-CMOS Corp. (www.ecmos.com.tw) Page 5 of 12 2007/06/29

EC5579

18+1 Channel Voltage Buffers for TFT LCD

Typical Performance Characteristics (Continued)

Figure7. Open Loop Gain & Phase vs. Frequency Figure8. Frequency Response for Various CL

Figure9. Frequency Response for Various RL

E-CMOS Corp. (www.ecmos.com.tw) Page 6 of 12 2007/06/29

EC5579

18+1 Channel Voltage Buffers for TFT LCD

Applications Information

Product Description

The EC5579 rail-to-rail quad channels amplifier is built on an advanced high voltage CMOS process. It’s beyond

rails input capability and full swing of output range made itself an ideal amplifier for use in a wide range of

general-purpose applications. The features of 1µS high slew rate, fast settling time, 2MHz of GBWP as well as high

output driving capability have proven the EC5579 a good voltage reference buffer in TFT-LCD for grayscale

reference applications. High phase margin and extremely low power consumption (500µA per amplifier) make the

EC5579 ideal for Connected in voltage follower mode for low power high drive applications

Supply Voltage, Input Range and Output Swing

The EC5579 can be operated with a single nominal wide supply voltage ranging from 6.5V to 18V with stable

performance over operating temperatures of -20 °C to +85 °C.

With 500mV greater than rail-to-rail input common mode voltage range and 75dB of Common Mode Rejection Ratio,

the EC5579 allows a wide range sensing among many applications without having any concerns over exceeding the

range and no compromise in accuracy. The output swings of the EC5579 typically extend to within 80mV of positive

and negative supply rails with load currents of 5mA. The output voltage swing can be even closer to the supply rails

by merely decreasing the load current. Figure 1 shows the input and output waveforms for the device in the

unity-gain configuration. The amplifier is operated under ±5V supply with a 10k. load connected to GND. The input is

a 10Vp-p sinusoid. An approximately 9.985 Vp-p of output voltage swing can be easily achieved.

Figure10. Operation with Rail-to-Rail Input and Output

Output Short Circuit Current Limit

A +/-120mA short circuit current will be limited by the EC5579 if the output is directly shorted to the positive

or the negative supply. For an indefinitely output short circuit, the power dissipation could easily increase such that

the device may be damaged. The internal metal interconnections are well designed to prevent the output continuous

current from exceeding +/-30 mA such that the maximum reliability can be well maintained.

E-CMOS Corp. (www.ecmos.com.tw) Page 7 of 12 2007/06/29

EC5579

18+1 Channel Voltage Buffers for TFT LCD

Output Phase Reversal

The EC5579 is designed to prevent its output from being phase reversal as long as the input voltage is limited from

VS--0.5V to VS+ +0.5V. Figure 2 shows a photo of the device output with its input voltage driven beyond the supply

rails. Although the phase of the device's output will not be reversed, the input's over-voltage should be avoided. An

improper input voltage exceeds supply range by more than 0.6V may result in an over stress damage.

Figure11. Operation with Beyond-the Rails Input

Power Dissipation

The EC5579 is designed for maximum output current capability. Even though momentary output shorted to ground

causes little damage to the device.

For the high drive amplifier EC5579, it is possible to exceed the 'absolute-maximum junction temperature' under

certain load current conditions. Therefore, it is important to calculate the maximum junction temperature for the

application to determine if load conditions need to be modified for the amplifier to remain in the safe operating area.

The maximum power dissipation allowed in a package is determined according to:

TJmax - TAmax

PDmax =

ΘJA

Where:

TJmax = Maximum Junction Temperature

TAmax= Maximum Ambient Temperature

ΘJA = Thermal Resistance of the Package

PDmax = Maximum Power Dissipation in the Package.

The maximum power dissipation actually produced by an IC is the total quiescent supply current times the total

power supply voltage, plus the power in the IC due to the loads, or:

PDmax =∑i[VS * ISmax + (VS+ – VO) * IL]

When sourcing, and

PDmax = ∑i[VS * ISmax + (VO – VS-) * IL]

When sinking.

E-CMOS Corp. (www.ecmos.com.tw) Page 8 of 12 2007/06/29

EC5579

18+1 Channel Voltage Buffers for TFT LCD

Where:

i = 1 to 4

VS = Total Supply Voltage

ISmax = Maximum Supply Current Per Amplifier

VO = Maximum Output Voltage of the Application

IL= Load current

RL= Load Resistance = (VS+ – VO)/IL = (VO – VS-)/ IL

A calculation for RL to prevent device from overheat can be easily solved by setting the two PDmax equations equal to

each other.

Θja Θjc

Pin Count

(℃/W) (℃/W)

TQFP-48 35 7 Exposed pad (5.0x5.0 mm)

TQFP-48 42 19.6 Exposed pad (3.05x3.05 mm)

TQFP-48 67 31 Normal

Driving Capacitive Loads

The EC5579 is designed to drive a wide range of capacitive loads. In addition, the output current handling capability

of the device allows for good slewing characteristics even with large capacitive loads. The combination of these

features make the EC5579 ideally for applications such as TFT LCD panel grayscale reference voltage buffers, ADC

input amplifiers, etc.

As load capacitance increases, however, the -3dB bandwidth of the device will decrease and the peaking increase.

The amplifiers drive 10pF loads in parallel with10KΩ. with just 1.5dB of peaking, and 100pF with 6.4dB of peaking.

If less peaking is desired in these applications, a small series resistor (usually between 5Ωand 50Ω) can be placed

in

series with the output. However, this will obviously reduce the gain slightly. Another method of reducing peaking is to

add a "snubber" circuit at the output. A snubber is a shunt load consisting of a resistor in series with a capacitor.

Values of 150Ω and 10nF are typical. The advantage of a snubber is that it improves the settling and overshooting

performance while does not draw any DC load current or reduce the gain.

Power Supply Bypassing and Printed Circuit Board Layout

With high phase margin, the EC5579 performs stable gain at high frequency. Like any high-frequency device, good

layout of the printed circuit board usually comes with optimum performance. Ground plane construction is highly

recommended, lead lengths should be as short as possible and the power supply pins must be well bypassed to

reduce the risk of oscillation. For normal single supply operation, where the VS- pin is connected to ground, a 0.1 µF

ceramic capacitor should be placed from VS+ pin to VS- pin as a bypassing capacitor. A 4.7µF tantalum capacitor

should then be connected in parallel, placed in the region of the amplifier. One 4.7µF capacitor may be used for

multiple devices. This same capacitor combination should be placed at each supply pin to ground if split supplies are

to be used.

E-CMOS Corp. (www.ecmos.com.tw) Page 9 of 12 2007/06/29

EC5579

18+1 Channel Voltage Buffers for TFT LCD

Application Circuits

E-CMOS Corp. (www.ecmos.com.tw) Page 10 of 12 2007/06/29

EC5579

18+1 Channel Voltage Buffers for TFT LCD

OUTLINE DIMENSIONS (Dimensions shown in millimeters)

H1: Exposed pad (5.0x5.0 mm)

DIMN Millimeters INCHES

NOTE

1.PACKAGE BODY SIZES EXCLUDE MOLE

MIN NOM MAX MIN NOM MAX FLASH AND GATE BURRS.

A — — 1.15 — — 0.046 2.DIMENSION L IS MEASURED IN GAGE

PLANE.

A1 0.05 — 0.15 0.002 — 0.006

3.TOLERANCE 0.10mm UNLESS

A2 0.95 1.00 1.05 0.037 0.039 0.041

OTHERWISE SPECIFIED.

b 0.17 0.22 0.27 0.006 0.008 0.011 4. CONTROLLING DIMENSION IS

C 0.09 — 0.20 0.003 — 0.008 MILLIMETER CONVERTED INCH

D1 6.90 7.00 7.10 0.271 0.275 0.279 DIMENSIONS ARE NOT NECESSARILY

EXACT.

D 8.80 9.00 9.20 0.346 0.354 0.362

5.DIE PA D EXPOSURE SIZE IS ACCORING

E1 6.90 7.00 7.10 0.271 0.275 0.279 TO LEAD FRAME DESIGN.

E 8.80 9.00 9.20 0.346 0.354 0.362 6.FOLLOWED FORM JEDEC MO-136.

e — 0.5(TYP) — — 0.02(TYP) —

L 0.45 0.6 0.75 0.018 0.024 0.029

L1 — 1.00(REF) — — 0.039(REF) —

Q1 0˚ 3.5˚ 7˚ 0˚ 3.5˚ 7˚

ccc — — 0.08 — — 0.003

E-CMOS Corp. (www.ecmos.com.tw) Page 11 of 12 2007/06/29

EC5579

18+1 Channel Voltage Buffers for TFT LCD

OUTLINE DIMENSIONS (Dimensions shown in millimeters)

H: Exposed pad (3.05x3.05 mm)

THERNALLY ENHANCED DINENSIONS (SHOW IN WW)

PAD SIZE E2 D2

MIN. MAX. MIN. MAX.

160X16E 3.05 4.06 3.05 4.06

DIMN MM

MIN NOM MAX NOTE

A — — 1.20 1. JEDEC OUTLINE:

NS-026 ABC

A1 0.05 — 0.15

NS-026 ABC-HD (THERNALLY ENHANCED VARIATIONS ONLY)

A2 0.95 1.00 1.05

2. DATUN PLANE H IS LOCATED AT THE BOTTOM OF THE MOLE

b 0.17 0.20 0.23 PATTING LINE COINCIDENT WITH WHERE THE LEAD EXITS THE

c 0.09 — 0.16 BODY.

3. DIMENSIONS D1 AND E1 DO NOR INCLUDE MOLD

D 9.00 BSC

PROTRUSION.ALLOWABLE PROTRUSION IS 0.25mm PER

D1 7.00 BSC

SIDE.DIMENSICNS D1 AND E1 DO INCLUDE MOLD MISWATCH

E 9.00 BSC AND ARE DETERMINED AT DATUN PLANE H

E1 7.00 BSC 4.DINENSION b DOES NOT INCLUDE DANBAR PROTRUSION.

e 0.50 BSC

L 0.45 0.60 0.75

L1 1.00(REF)

Q 0˚ 3.5˚ 7˚

E-CMOS Corp. (www.ecmos.com.tw) Page 12 of 12 2007/06/29

You might also like

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- As19 HGDocument12 pagesAs19 HGКрасимир КостадиновNo ratings yet

- AS15GDocument12 pagesAS15Gjailton1958No ratings yet

- High Performance CMOS Quad Operational Amplifier: FeaturesDocument14 pagesHigh Performance CMOS Quad Operational Amplifier: FeaturesAnonymous oyUAtpKNo ratings yet

- AS1710 12 Datasheet EN v4Document20 pagesAS1710 12 Datasheet EN v4Amr HalabyNo ratings yet

- Unisonic Technologies Co., LTD: 4 X 41W Quad Bridge Car Radio AmplifierDocument5 pagesUnisonic Technologies Co., LTD: 4 X 41W Quad Bridge Car Radio AmplifierEmerson TurquesNo ratings yet

- Programmable Quad Bipolar Operational Amplifier: LM146 LM246 LM346Document6 pagesProgrammable Quad Bipolar Operational Amplifier: LM146 LM246 LM346Alejandro Borrego DominguezNo ratings yet

- Itr8307 S17 TR8Document10 pagesItr8307 S17 TR8cointoinNo ratings yet

- IRAMS10UP60B: Series 10A, 600VDocument17 pagesIRAMS10UP60B: Series 10A, 600VAngel VelasquezNo ratings yet

- LMD18200 3A, 55V H-Bridge: Features ApplicationsDocument19 pagesLMD18200 3A, 55V H-Bridge: Features ApplicationsLe NhanNo ratings yet

- PM 150 CSD 120Document7 pagesPM 150 CSD 120elecompinnNo ratings yet

- Acs 102Document8 pagesAcs 102Alexis RamonNo ratings yet

- Ta 78033Document10 pagesTa 78033Federico GMNo ratings yet

- LC1209 Datasheet (V1.0)Document7 pagesLC1209 Datasheet (V1.0)gusguicorNo ratings yet

- TL062, TL062A, TL062B: Low-Power JFET Dual Operational AmplifiersDocument16 pagesTL062, TL062A, TL062B: Low-Power JFET Dual Operational AmplifierswojtektmNo ratings yet

- Ec48324 FV PDFDocument11 pagesEc48324 FV PDFАлександрNo ratings yet

- Unisonic Technologies Co., LTD: General Purpose, Low Voltage, Rail-To-Rail Output Operational AmplifiersDocument12 pagesUnisonic Technologies Co., LTD: General Purpose, Low Voltage, Rail-To-Rail Output Operational AmplifiersJonathan NuñezNo ratings yet

- Ca3130, Ca3130aDocument17 pagesCa3130, Ca3130aproctepNo ratings yet

- Boost (Step-Up) WLED Driver With OVP: General DescriptionDocument8 pagesBoost (Step-Up) WLED Driver With OVP: General DescriptiondneprashNo ratings yet

- Adc 10158Document26 pagesAdc 10158Felipe LorenziNo ratings yet

- Photorécepteur PDFDocument7 pagesPhotorécepteur PDFmrd9991No ratings yet

- TC4538BP Datasheet en 20140301Document9 pagesTC4538BP Datasheet en 20140301Strati YovchevNo ratings yet

- Low Noise Dual Operational Amplifiers: (Plastic Package)Document5 pagesLow Noise Dual Operational Amplifiers: (Plastic Package)Liver Haro OrellanesNo ratings yet

- ADC0808/ADC0809 8-Bit P Compatible A/D Converters With 8-Channel MultiplexerDocument14 pagesADC0808/ADC0809 8-Bit P Compatible A/D Converters With 8-Channel MultiplexerYenny RozaNo ratings yet

- LM 2893Document26 pagesLM 2893Jack DiNo ratings yet

- Unisonic Technologies Co., LTD: Low Power Single Op AmpDocument7 pagesUnisonic Technologies Co., LTD: Low Power Single Op AmpSolihin iingNo ratings yet

- Infineon BTS740S2Document15 pagesInfineon BTS740S2dasho1No ratings yet

- Low Power Quad Voltage Comparators: LM139, A LM239, A - LM339, ADocument11 pagesLow Power Quad Voltage Comparators: LM139, A LM239, A - LM339, Alinguyen1No ratings yet

- AM2837 V0.3 EngDocument9 pagesAM2837 V0.3 Engjuanito35731057No ratings yet

- RCLAMP0503NDocument7 pagesRCLAMP0503NAisya NurcahyaNo ratings yet

- LM-339 Data SheetDocument11 pagesLM-339 Data SheetThorik AchsanNo ratings yet

- Unitronics JZ20-XX-UA24 - JZ20-UN20 - JZ20-J-UN20-SPECDocument6 pagesUnitronics JZ20-XX-UA24 - JZ20-UN20 - JZ20-J-UN20-SPECbtj.avtomatikaNo ratings yet

- Audio Processor: NJW1138M NJW1138LDocument21 pagesAudio Processor: NJW1138M NJW1138LRahulAnymationNo ratings yet

- PWM Constant-Current Control Stepper Motor Driver: Monolithic Linear ICDocument27 pagesPWM Constant-Current Control Stepper Motor Driver: Monolithic Linear ICДмитрий СамарцевNo ratings yet

- Unisonic Technologies Co., LTD: Pre-Amplifier For Mems MicrophoneDocument7 pagesUnisonic Technologies Co., LTD: Pre-Amplifier For Mems MicrophoneImamNo ratings yet

- Ps 21245Document9 pagesPs 21245pukymottoNo ratings yet

- Tfms 5360Document6 pagesTfms 5360Ecaterina IrimiaNo ratings yet

- Railclamp Low Capacitance Tvs Array: Protection Products - Railclamp Description FeaturesDocument8 pagesRailclamp Low Capacitance Tvs Array: Protection Products - Railclamp Description FeaturesHemantkumarNo ratings yet

- QMODP1xx 2010Document3 pagesQMODP1xx 2010mishu_gNo ratings yet

- Stepmotor and Gear AssemblyDocument3 pagesStepmotor and Gear Assemblydhawk94No ratings yet

- Unisonic Technologies Co., LTD: Description 1Document5 pagesUnisonic Technologies Co., LTD: Description 1alexjcc10No ratings yet

- Unisonic Technologies Co., LTD: High Speed Operational AmplifierDocument6 pagesUnisonic Technologies Co., LTD: High Speed Operational AmplifierTioRamadhanNo ratings yet

- Fotransistor HexingDocument8 pagesFotransistor HexingFranco BerterameNo ratings yet

- TSM103/A: Dual Operational Amplifier and Voltage ReferenceDocument10 pagesTSM103/A: Dual Operational Amplifier and Voltage ReferenceTùng NguyễnNo ratings yet

- TSOP17Document6 pagesTSOP17Walt WhimpennyNo ratings yet

- Infrared Sensor Datasheet - TSOP-4838 PDFDocument8 pagesInfrared Sensor Datasheet - TSOP-4838 PDFraphaelsantanasouzaNo ratings yet

- El5120 - El5220 - El5420Document13 pagesEl5120 - El5220 - El5420Cristina NistorNo ratings yet

- DAC0800/DAC0802 8-Bit Digital-to-Analog Converters: General DescriptionDocument0 pagesDAC0800/DAC0802 8-Bit Digital-to-Analog Converters: General DescriptionMiguel Angel García ValerioNo ratings yet

- LM759/LM77000 Power Operational Amplifiers: General Description FeaturesDocument15 pagesLM759/LM77000 Power Operational Amplifiers: General Description FeaturesgustavoblimaNo ratings yet

- IES DsDocument14 pagesIES DsSubramani KarurNo ratings yet

- AP358 DatasheetDocument13 pagesAP358 DatasheetRafael OliveiraNo ratings yet

- Ps 21 A 79Document10 pagesPs 21 A 79Omar LeonNo ratings yet

- Ltc1629/Ltc1629-Pg Polyphase, High Efficiency, Synchronous Step-Down Switching RegulatorsDocument28 pagesLtc1629/Ltc1629-Pg Polyphase, High Efficiency, Synchronous Step-Down Switching Regulatorscatsoithahuong84No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1From EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Rating: 4.5 out of 5 stars4.5/5 (3)

- Bat 41Document3 pagesBat 41Fernando QueirozNo ratings yet

- Effect of Anode Type and Position On The Cathodic Protection of Carbon Steel in Sea WaterDocument8 pagesEffect of Anode Type and Position On The Cathodic Protection of Carbon Steel in Sea WatersaishankarlNo ratings yet

- 2202acdc Service Manual PDFDocument91 pages2202acdc Service Manual PDFex-215660% (5)

- Woodward Egcp-2 DatasheetDocument4 pagesWoodward Egcp-2 DatasheetbambangNo ratings yet

- UntitledDocument171 pagesUntitledButter TeaNo ratings yet

- Design and Development of Small Active and Passive Loop Antennas For Measurement of Shielding Effectiveness Per IEEE Std.299Document5 pagesDesign and Development of Small Active and Passive Loop Antennas For Measurement of Shielding Effectiveness Per IEEE Std.299Andrea QuadriNo ratings yet

- M61 Guide en-USDocument2 pagesM61 Guide en-USJuan OlivaNo ratings yet

- A Detailed Investigation of Overhead Line Insulators: June 2006Document76 pagesA Detailed Investigation of Overhead Line Insulators: June 2006Classic LipuNo ratings yet

- Technical SpecificationDocument14 pagesTechnical SpecificationbinodeNo ratings yet

- FSCQ1565RT: Green Mode Fairchild Power Switch (FPS) For Quasi-Resonant Switching ConverterDocument25 pagesFSCQ1565RT: Green Mode Fairchild Power Switch (FPS) For Quasi-Resonant Switching ConverterPaulo Roberto s freireNo ratings yet

- Devicenet: Leoni Special Cables GMBHDocument2 pagesDevicenet: Leoni Special Cables GMBHLeodoletaNo ratings yet

- 2011 KICKER Catalog Rev1 WebDocument44 pages2011 KICKER Catalog Rev1 Webautoperi2010No ratings yet

- Ac Machine MotorDocument10 pagesAc Machine MotorPatoriku KunNo ratings yet

- CPC 100 Testrano 600 Appnote Dynamic Oltc Scan 2019 EnuDocument21 pagesCPC 100 Testrano 600 Appnote Dynamic Oltc Scan 2019 EnudanielsampermNo ratings yet

- E3MUPS100KHSDocument4 pagesE3MUPS100KHSZak zsNo ratings yet

- DSD Lab Manual AitdDocument31 pagesDSD Lab Manual Aitdprathameshbhat88No ratings yet

- The Electronic Experimenter's Manual FindlayDocument176 pagesThe Electronic Experimenter's Manual FindlayTEDY-RNo ratings yet

- 8698Document4 pages8698Hrishikesh KakatyNo ratings yet

- Cea 311 ReportDocument2 pagesCea 311 ReportFaher Gaosel WatamamaNo ratings yet

- (Troubleshooting) Komatsu Excavator Fault Code Fault Code PDFDocument17 pages(Troubleshooting) Komatsu Excavator Fault Code Fault Code PDFkiagengbrantas heavyequipment100% (6)

- TDA75610LV: 4 X 45 W Power Amplifier With Full I C Diagnostics, High Efficiency and Low Voltage OperationDocument42 pagesTDA75610LV: 4 X 45 W Power Amplifier With Full I C Diagnostics, High Efficiency and Low Voltage Operationmanuel fernandezNo ratings yet

- Beyma BookDocument91 pagesBeyma BookRajuNo ratings yet

- Harmonic Elimination in Three-Phase Voltage SourceDocument9 pagesHarmonic Elimination in Three-Phase Voltage SourceDaniloNo ratings yet

- 5827 Simulation Intro LTspiceDocument13 pages5827 Simulation Intro LTspiceChihiro SatoNo ratings yet

- Block Diagram of I.C. Timer (Such As 555) and Its WorkingDocument4 pagesBlock Diagram of I.C. Timer (Such As 555) and Its Workingkaran007_mNo ratings yet

- SUMBA ISLAND, IndonesiaDocument21 pagesSUMBA ISLAND, Indonesiaarjuna naibahoNo ratings yet

- UWW-301 WIRE WELDER FLYER v7 (August 2021)Document3 pagesUWW-301 WIRE WELDER FLYER v7 (August 2021)Chris TeohNo ratings yet

- HP 5328A Service ManualDocument219 pagesHP 5328A Service ManualDragan LazicNo ratings yet

- Semiconductor and Digital Circuit 1693007493Document4 pagesSemiconductor and Digital Circuit 1693007493samsuzzaman sahinNo ratings yet

- The Development of Flexible Integrated Circuits Based On Thin-Film TransistorsDocument10 pagesThe Development of Flexible Integrated Circuits Based On Thin-Film TransistorsJOAM MANUEL RINCÓN ZULUAGANo ratings yet