Professional Documents

Culture Documents

BGR Design Techniques

Uploaded by

sachin saxenaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

BGR Design Techniques

Uploaded by

sachin saxenaCopyright:

Available Formats

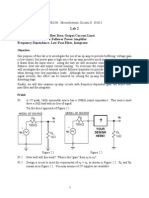

Fast transient capacitor-less LDO regulator The response of an LDO to a load current change is characterised in two

using low-power output voltage detector sections: the initial step responses of Dt1 and Dt3 and the settling times

of Dt2 and Dt4. The step response represented by Dt1 in Fig. 1 is a

Y.-I. Kim and S.-S. Lee function of the ERR AMP bandwidth (BW) and ISR , and Dt1 is given by

1 DV

An output-capacitor-less low-dropout regulator (LDO) with a low- Dt1 ≃ + Cp (1)

BW Isr

power output voltage detector (OVD) is proposed. The OVD is based

on an R/C highpass filter which is able to detect the fast-changing where BW is the closed-loop bandwidth of the LDO negative feedback,

voltage at the LDO output and activate an additional path to control DV is the voltage variation at the gate of the PWR TR, and ISR is the

the power transistor. The OVD consumes only additional quiescent current for driving the Cp of the PWR TR. To minimise Dt1 and Dt3 ,

current to monitor the variation in output voltage in the steady state. the LDO requires a wide closed-loop BW and a higher SR. Also, by

In the simulated load-transient response, a maximum undershoot of using a small output capacitor and a higher SR for driving the Cp, the

1.2 V and a settling time (Dt2) of 67 ns are observed with the proposed

settling times of Dt2 and Dt4 can be minimised [6].

OVD for a load current variation from 1 to 50 mA at a rise time of 1 ns.

These results are 0.2 V and 473 ns better than the results obtained

without the proposed OVD. Proposed scheme description: As shown in Fig. 1, the LDO undergoes

a small-signal response when the output current of the LDO increases

(or decreases) rapidly over the BW of the LDO. The LDO cannot instan-

Introduction: Currently, low-dropout (LDO) regulators are widely used taneously respond to the charge needed to decrease (or increase) the

in battery-powered mobile systems, which require small size and a clean PWR TR gate voltage owing to the limited BW. The LDO produces a

supply voltage. To prolong battery life and to improve power efficiency, large signal response when there is a large change in the load current.

reductions in the quiescent current and the dropout voltage are necess- The decrease (or increase) of the gate voltage of the PWR TR is

ary. However, a low quiescent current unavoidably slows the transient constrained by the limited SR of the driver for the PWR TR.

responses of an LDO regulator. Minimising the quiescent current and Immediately, a rapid and large change in load current causes a serious

dropout voltage to increase power efficiency while maintaining good problem in the initial peak voltage drop and the settling time. The

regulation and a fast response time is the main issue of LDO regulator proposed LDO in this Letter is formed by an OVD which has a

design [1]. For portable applications, external components such as higher frequency range than the main loop bandwidth, as shown in

output capacitors should be minimised to reduce the printed circuit Fig. 2. The OVD is based on an R/C highpass filter (HPF), which is

board (PCB) layout space and to speed up the manufacturing process, implemented by a simple RC structure [7]. The sensing parts of the

so an output capacitor-less LDO regulator is preferred. However, OVD always activate to monitor the variation in output voltage, but

because of the limited on-chip size, the internal on-chip output capacitor the other MP_UP, MN_DN , MP_ONOFF, and MN_ONOFF transistors are

is smaller and the ESR is increased. This will lead to severe output deactivated in steady state operation. When a rapid and large change

voltage changes during a fast-load current transient [1]. Recently, in load current is detected, an additional path that has a wide BW and

many researchers have proposed various strategies for improving the low gain is activated to control the PWR TR. The full circuit with the

power efficiency and the transient response performance of the output OVD is shown in Fig. 3.

capacitor-less LDO regulators. Using the capacitor coupling effect for

the transient response performance [1 – 3] and modifying the driver of VIN

the power transistor to improve the slew rate have been proposed [4]. ERR_AMP

However, these methods need additional circuitry and current, which Vref

buffer

causes considerable degradation of the power efficiency. +

Pwr. Tr.

To solve these problems, the output voltage detector (OVD) is based

on a highpass filter (HPF) that is able to detect the initial peak output – OVD

C

voltage. The sensed signal activates an additional path to control the output voltage

Vout

detector

power transistor to improve the load-transient response. For low-power

ESR

operation, the OVD block consumes only additional quiescent current R1

to monitor the variation in the output voltage in steady state.

Cout

R2 GND

Vout t3

Iout t4 GND

Iout

Vout LDO main loop bandwidth

overlapping

frequency

t2

output voltage detector

t1

time, s Fig. 2 Frequency range of OVD and block diagram

Fig. 1 Transient response of step load current VIN

< OTA > < buffer > < output voltage detector >

5uA 10uA 5uA 10uA 15uA ON/OFF 5uA ON/OFF 1.5uA 1.5uA ON/OFF 1.5uA 1.5uA Iq_tot=46uA

MP_ON/OFF

Vb1

MP_UP

VB1 Vb3

LDO description: Fig. 2 displays a three-stage LDO regulator structure VA

MNA

P.W.R Tr.

consisting of an error amplifier (ERR-AMP), buffer (BUF), a power Vref VFB

Vout CA

1

+

rop Vout

CB

transistor (PWR TR), and feedback resistors. The ERR-AMP generates gmn gmnron

MN_ON/OFF

ESR

MNB

R1

VFB

the error signal based on a comparison between the reference voltage Cout VB

MN_DN

Vb2 Vb4

R2

and the feedback signal from a resistive-divided output voltage. In the

GND

output-capacitor-less LDO structure, the dominant pole is located in

the PWR TR gate node, not in the output node. Therefore, using a

buffer with low input capacitance and a high output resistance character- Fig. 3 Full circuit with OVD

istic guarantee the stability of the circuit operation [5]. To supply a large

output current, the PWR TR has to be large compared to the other tran- (i) Undershoot: When the load current increases suddenly, the output

sistors. Therefore, the parasitic capacitor (Cp) at the gate of the PWR TR voltage undershoot increases dramatically. This signal will couple

is very large, in the range of tens to hundreds of picofarads. A large Cp through CA and amplify through MN_A and MP_ONOFF transistor acti-

limits the slew rate performance. Fig. 1 shows the details of a typical vation. The additional drain current of MN_DN will then flow from the

LDO response to a load current step. The transient response time of Cp of the PWR TR gate to supply additional output current. As a

an LDO to a load current step is a critical specification in applications. result, the output of the undershoot can be recovered more quickly.

ELECTRONICS LETTERS 2nd February 2012 Vol. 48 No. 3

(ii) Overshoot: When the load current decreases suddenly, the output Conclusion: Presented is a method to improve the load-transient

voltage overshoot increases dramatically. This signal will couple response of the output-capacitor-less LDO using a low-power OVD.

through CB and will amplify through MP_B and MN_ONOFF transistor The proposed OVD consists of two R/C HPFs which are able to

activation. The additional drain current of MP_UP will then flow to the detect the fast-changing peak drop voltage at the LDO output and acti-

PWR TR gate to reduce the output current. As a result, the output of vate an additional path to control the power transistor to improve

the overshoot can be recovered more quickly. responses. The proposed OVD consumes only additional quiescent

Since all of the nodes in this signal path are connected to a small current to monitor the variation in the output voltage in the steady

parasitic capacitance and consist of a low impedance node, this signal state. This scheme solves the problems of limited BW and SR in the

propagation time is expected to be fast. Therefore, the proposed LDO conventional LDO by applying a simple and effective modification to

will have good performance in terms of undershoot/overshoot. the LDO circuit.

In the steady state, the VA voltage level is set between VDD 2 |VTHP|

to VDD 2 VOD and the VB voltage level between VOD to VTHN by the Acknowledgments: This work was supported by ‘BK21’, ‘IDEC’ and

current mirror configuration, so the MP_UP, MN_DN , MP_ONOFF, and ‘HYNIX’.

MN_ONOFF transistors are deactivated for low-power operation. The

common mode feedback circuit (CMFB) could be used for more # The Institution of Engineering and Technology 2012

robust VA and VB voltage levels. The CMFB signal loops are from 8 December 2011

VA to Vb2 and from VB to Vb3 , respectively. doi: 10.1049/el.2011.3671

One or more of the Figures in this Letter are available in colour online.

Simulation results: This LDO is implemented in a 110 nm CMOS tech-

nology provided by Dongbuhiteck. The internal output capacitor is 5 nF Y.-I. Kim and S.-S. Lee (Department of Nanoscale Semiconductor

and the ESR is 1 V. The LDO output voltage ranges from 1.6 to 3.6 V Engineering, Hanyang University, 222 Wangshimniro, Seongdong-gu,

with a minimum dropout voltage of 200 mV and a maximum output Seoul 133-791, Republic of Korea)

current of 200 mA. The LDO operates with a supply voltage ranging E-mail: ssnlee@hanyang.ac.kr

from 1.8 to 3.8 V, and its quiescent current is 46 mA for a 3.3 V

supply voltage, not including the bandgap circuitry, as calculated in References

Fig. 3. Of particular importance is the fact that the proposed OVD 1 Ho, E.N.Y., and Mok, P.K.T.: ‘A capacitor-less CMOS active feedback

block consumes only 6 mA in the steady state. The LDO stability and low-dropout regulator with slew-rate enhancement for portable on-chip

its specifications are ensured for all of the process corners and over a application’, IEEE Trans. Circuits Syst. II, 2010, 2, pp. 80– 84

temperature range from 220 to 1008C. In the simulated load-transient 2 Or, P.Y., and Leung, K.N.: ‘An output-capacitorless low-dropout

response, a maximum undershoot of 1.2 V and a settling time (Dt2) of regulator with direct voltage-spike detection’, IEEE J. Solid-State

67 ns are observed with the proposed OVD for a load current variation Circuits, 2010, 45, pp. 458– 466

from 1 m to 50 mA at a rise time of 1 ns. As shown in Fig. 4, these 3 Leung, K., and Ng, Y.S.: ‘A CMOS low-dropout regulator with a

results are 0.2 V and 473 ns better than the results obtained without momentarily current-boosting voltage buffer’, IEEE Trans. Circuits

the proposed OVD. The simulated loop gain is from 88 to 80 dB, the Syst. I, 2010, 57, pp. 2312–2319

4 Man, T.Y., and Mok, P.K.T.: ‘A high slew-rate push– pull output

unit gain frequency is 9 MHz, and the phase margin is from 558 to amplifier for low-quiescent current low-dropout regulators with

908 for a load current variation from 1 to 200 mA. transient-response improvement’, IEEE Trans. Circuits Syst. II, 2007,

9, pp. 755 –759

ldo

V(out)

V(out)

2.4 Vout

9.6u 9.8u 10u

10/19/2011 03:38:38

10.2u

t2 with PVD = 67nsec

10.4u 10.6u 10.8u

waveview 1

t2 without PVD = 540nsec I_load[mA]

5 Al-Shyoukh, M., and Lee, H.: ‘A transient-enhanced low-quiescent

473nsec is reduced by OVD

2.2 current low-dropout regulator with buffer impedance attenuation’,

2

1.8

2.25V

IEEE J. Solid-State Circuits, 2007, 8, pp. 1732–1742

V[V]

1.6

1.4

VA 6 Oh, W., and Bakkaloglu, B.: ‘A CMOS low-dropout regulator with

1.2

(With OVD) 1.05V

VB

current-mode feedback buffer amplifier’, IEEE Trans. Circuits Syst. II,

1 0.2V is reduced by OVD

i(iout) 50m

I_load

0.85V (without OVD)

I_load I [mA]

2007, 10, pp. 922– 926

40m

50mA I_MN_DN

0A 7 Coulot, T., Rouat, E., Fournier, J.-M., Lauga, E., and Hasbani, F.: ‘High

30m I_MP_UP

0A power supply rejection low-dropout regulator for ultra-low-power

20m Vout[V] radiofrequency functions’, Electron. Lett., 2011, 47, (20), pp. 117 –118

10m

1mA

rising time : 1nsec

9.6u 9.8u 10u 10.2u 10.4u 10.6u 10.8u

printed Wed Oct 19 2011 04:04:04:16 by yikim on localhost.localdomain sec (lin) synopsys, Inc. (c) 2000-2009 time [sec]

Fig. 4 Simulation results

ELECTRONICS LETTERS 2nd February 2012 Vol. 48 No. 3

You might also like

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Book BindingDocument14 pagesBook Bindingpesticu100% (2)

- Genie GS-1930 Parts ManualDocument194 pagesGenie GS-1930 Parts ManualNestor Matos GarcíaNo ratings yet

- ST 36Document4 pagesST 36ray72roNo ratings yet

- Killer Kohler Part I IDocument17 pagesKiller Kohler Part I Irusyn100% (1)

- 40 RT-flex Control-System Rev01Document68 pages40 RT-flex Control-System Rev01Mayvon Botelho100% (2)

- Sch3u Exam Review Ws s2018 PDFDocument4 pagesSch3u Exam Review Ws s2018 PDFwdsfNo ratings yet

- Accsap 10 VHDDocument94 pagesAccsap 10 VHDMuhammad Javed Gaba100% (2)

- Assignment 4 SolutionsDocument9 pagesAssignment 4 SolutionsNengke Lin100% (2)

- Propert 447-445Document11 pagesPropert 447-445LUNA100% (1)

- All Pop SongsDocument53 pagesAll Pop SongsMadeleneQuiogueNo ratings yet

- 1.1 Introduction To Buck ConverterDocument44 pages1.1 Introduction To Buck Converterapi-19810277No ratings yet

- Design of A Low Voltage Low Drop Out LDO Voltage Cmos RegulatorDocument6 pagesDesign of A Low Voltage Low Drop Out LDO Voltage Cmos Regulatorsantosh kumar gangalaNo ratings yet

- How To Predict Stability in Linear RegulatorsDocument7 pagesHow To Predict Stability in Linear RegulatorssureshchattuNo ratings yet

- ICDocument16 pagesICMuhammad Usman100% (1)

- An Analysis of Buck Converter Efficiency in PWM/PFM Mode With SimulinkDocument6 pagesAn Analysis of Buck Converter Efficiency in PWM/PFM Mode With SimulinkAli RazaNo ratings yet

- Polezero Tracking Frequency Compensation For Low Dropout RegulatorDocument4 pagesPolezero Tracking Frequency Compensation For Low Dropout Regulatorabhishekmath123No ratings yet

- Capacitor-Less Low Dropout Voltage Regulator With Improved Transient Response in 65nm CMOS Technology ProcessDocument6 pagesCapacitor-Less Low Dropout Voltage Regulator With Improved Transient Response in 65nm CMOS Technology ProcessJoshua KoppinNo ratings yet

- Moon 2019Document8 pagesMoon 2019Deniz GülerNo ratings yet

- An Ultra-Low Quiescent Current CMOS Low-Dropout Regulator With Small Output Voltage VariationsDocument6 pagesAn Ultra-Low Quiescent Current CMOS Low-Dropout Regulator With Small Output Voltage VariationsMehanathan Maggie MikeyNo ratings yet

- Design Analysis of Low Drop-Out Voltage Regulator With Current Buffer CompensationDocument5 pagesDesign Analysis of Low Drop-Out Voltage Regulator With Current Buffer Compensationkhang npNo ratings yet

- A Fast-Transient Low-Dropout Regulator With Load-Tracking Impedance Adjustment and Loop-Gain Boosting TechniqueDocument5 pagesA Fast-Transient Low-Dropout Regulator With Load-Tracking Impedance Adjustment and Loop-Gain Boosting Techniquecflin1979No ratings yet

- Enhanced Switching Characteristics of DC-DC Boost Converter SystemsDocument7 pagesEnhanced Switching Characteristics of DC-DC Boost Converter Systemsmhd ali mustofah nstNo ratings yet

- Carrier Based Sinusodial PWM Scheme For The Nine Switch ConverterDocument6 pagesCarrier Based Sinusodial PWM Scheme For The Nine Switch ConverterShankar MukalNo ratings yet

- Slua 053Document13 pagesSlua 053carlosibaNo ratings yet

- Biasing The TL431 For Improved Output ImpedanceDocument2 pagesBiasing The TL431 For Improved Output ImpedancerlevrinoNo ratings yet

- Operational Amplifiers Theory and Practice Roberge Trang 361 405Document45 pagesOperational Amplifiers Theory and Practice Roberge Trang 361 405Tuyên NguyễnNo ratings yet

- An Active-Frequency Compensation Scheme For CMOS Low-Dropout Regulators With Transient-Response ImprovementDocument5 pagesAn Active-Frequency Compensation Scheme For CMOS Low-Dropout Regulators With Transient-Response ImprovementCosmin PlesaNo ratings yet

- Design and Analysis of A Transformer-Less Single-Phase Grid-Tie Photovoltaic Inverter Using Boost Converter With Immittance Conversion TopologyDocument8 pagesDesign and Analysis of A Transformer-Less Single-Phase Grid-Tie Photovoltaic Inverter Using Boost Converter With Immittance Conversion Topologyangel monroyNo ratings yet

- Voltage-Follower Control in Zero-Current-Switched Quasi-Resonant Power Factor PreregulatorsDocument12 pagesVoltage-Follower Control in Zero-Current-Switched Quasi-Resonant Power Factor PreregulatorsNitish SinglaNo ratings yet

- LL$TF,:: Analysis of Low-Dropout Regulator Topologies For Low-Voltage RegulationDocument4 pagesLL$TF,:: Analysis of Low-Dropout Regulator Topologies For Low-Voltage RegulationJinwoo JungNo ratings yet

- ECE3204 D2013 Lab2Document9 pagesECE3204 D2013 Lab2Khalil2097No ratings yet

- Freq Compensation Tech LdoDocument4 pagesFreq Compensation Tech LdoManish SrivastavaNo ratings yet

- Cao 2021Document5 pagesCao 2021blackyNo ratings yet

- Current-Source Resonant Converter in Power Factor CorrectionDocument7 pagesCurrent-Source Resonant Converter in Power Factor CorrectionJie99No ratings yet

- Design and Optimization of On-Chip Voltage Regulators For High Performance ApplicationsDocument4 pagesDesign and Optimization of On-Chip Voltage Regulators For High Performance ApplicationsBaluvu JagadishNo ratings yet

- Investigation and Analysis of Switching Performance of Boost ConverterDocument6 pagesInvestigation and Analysis of Switching Performance of Boost ConvertererpublicationNo ratings yet

- Design Considerations For An LLC Resonant ConverterDocument9 pagesDesign Considerations For An LLC Resonant ConverterBOLFRANo ratings yet

- Stability Analysis of Low-Dropout Linear Regulators With A PMOS Pass ElementDocument4 pagesStability Analysis of Low-Dropout Linear Regulators With A PMOS Pass Elementkothari_rubinNo ratings yet

- LdoDocument17 pagesLdoKAMARUDHEEN KPNo ratings yet

- Simulation and Analysis of LLC Resonant Converter Using Closed Loop PI ControllerDocument3 pagesSimulation and Analysis of LLC Resonant Converter Using Closed Loop PI ControllerijaertNo ratings yet

- IJETR021998Document3 pagesIJETR021998erpublicationNo ratings yet

- AN848 DynamicDocument9 pagesAN848 DynamicAnonymous QakmLc3kTINo ratings yet

- 4.3 Hysteretic PresentationDocument13 pages4.3 Hysteretic PresentationAjay KrishnaNo ratings yet

- Fairchild AnDocument17 pagesFairchild AnhvhNo ratings yet

- High-Voltage Pulse Generator Based On Capacitor-Diode Voltage Multiplier Centrally Fed From DC-DC Boost ConverterDocument4 pagesHigh-Voltage Pulse Generator Based On Capacitor-Diode Voltage Multiplier Centrally Fed From DC-DC Boost ConverterNareshNo ratings yet

- Semiconductor AN721: Motorola Application NoteDocument16 pagesSemiconductor AN721: Motorola Application NotevedhhNo ratings yet

- AimDocument12 pagesAimkarakeriNo ratings yet

- Turkish PDFDocument13 pagesTurkish PDFramiNo ratings yet

- Buck ConvertersDocument15 pagesBuck Convertersחי לוגסיNo ratings yet

- Basic DC To DCDocument36 pagesBasic DC To DCstrelectronicsNo ratings yet

- VL Sics 040309Document10 pagesVL Sics 040309Anonymous e4UpOQEPNo ratings yet

- Experiment 5 Integrator, Differentiator and Non-Linear Properties of OpampsDocument7 pagesExperiment 5 Integrator, Differentiator and Non-Linear Properties of OpampsEnes AyduranNo ratings yet

- LDO FastsettlingDocument5 pagesLDO FastsettlingKini FamilyNo ratings yet

- Journal Paper-Design and Development of Compact DC DC ConverterDocument30 pagesJournal Paper-Design and Development of Compact DC DC ConverterSunsets.nNo ratings yet

- Power Factor Correction by PFC Boost TopDocument5 pagesPower Factor Correction by PFC Boost TopMilind TagareNo ratings yet

- Application Note AN-1043: Stabilize The Buck Converter With Transconductance AmplifierDocument12 pagesApplication Note AN-1043: Stabilize The Buck Converter With Transconductance AmplifierMaurício YoshimotoNo ratings yet

- A High Slew-Rate Push-Pull Output Amplifier For Low-Quiescent Current Low-Dropout Regulators With Transient-Response ImprovementDocument5 pagesA High Slew-Rate Push-Pull Output Amplifier For Low-Quiescent Current Low-Dropout Regulators With Transient-Response ImprovementsonofalexanderNo ratings yet

- Presentation - On-Chip Current Sensing Technique For Cmos Monolithic Switch-ModeDocument30 pagesPresentation - On-Chip Current Sensing Technique For Cmos Monolithic Switch-Modesohailasghar_tNo ratings yet

- Topic 3 LynchDocument26 pagesTopic 3 Lynchsunil251No ratings yet

- Assignment # 1 Principles of Steady-State Converter AnalysisDocument20 pagesAssignment # 1 Principles of Steady-State Converter AnalysisMandanas, John MaledrexNo ratings yet

- Jlpea 10 00005 v2Document11 pagesJlpea 10 00005 v2erikboutNo ratings yet

- An 7517Document9 pagesAn 7517MallickarjunaNo ratings yet

- Actuators: 3.1 SwitchesDocument16 pagesActuators: 3.1 SwitchesNesa Al NeshaNo ratings yet

- A Current-Fed Parallel Resonant Push-Pull Inverter With A New Cascaded Coil Flux Control For Induction Heating ApplicationsDocument7 pagesA Current-Fed Parallel Resonant Push-Pull Inverter With A New Cascaded Coil Flux Control For Induction Heating ApplicationsLuiz Daniel S. BezerraNo ratings yet

- Capless LDO DESIGNDocument6 pagesCapless LDO DESIGNbhasin_hemantNo ratings yet

- BJT Frequency Responce PDFDocument57 pagesBJT Frequency Responce PDFAlpha RomeoNo ratings yet

- Small-Signal Analysis A DC-DC Converter With A Non-Symmetric Phase Integral-Lead ControllerDocument8 pagesSmall-Signal Analysis A DC-DC Converter With A Non-Symmetric Phase Integral-Lead ControllerVinhNo ratings yet

- L-3 (DK) (Pe) ( (Ee) Nptel) 7Document5 pagesL-3 (DK) (Pe) ( (Ee) Nptel) 7GagneNo ratings yet

- The Benefits of The Coupled Inductor TechnologyDocument10 pagesThe Benefits of The Coupled Inductor Technologyaarumugam_rajendranNo ratings yet

- Predictive Maintenance Attempts To Detect The Onset of A Degradation Mechanism With The Goal of Correcting That Degradation Prior To Signiicant Deterioration in The Component or EquipmentDocument6 pagesPredictive Maintenance Attempts To Detect The Onset of A Degradation Mechanism With The Goal of Correcting That Degradation Prior To Signiicant Deterioration in The Component or EquipmentTodd BenjaminNo ratings yet

- Material Requirement Planning (MRP)Document55 pagesMaterial Requirement Planning (MRP)Lisa CarlsonNo ratings yet

- History and Philo of ScienceDocument5 pagesHistory and Philo of ScienceJan Oliver YaresNo ratings yet

- Guidelines For The Management of Brain InjuryDocument26 pagesGuidelines For The Management of Brain InjuryfathaNo ratings yet

- S590 Machine SpecsDocument6 pagesS590 Machine SpecsdilanNo ratings yet

- Product Lifecycle Management and Sustainable Development in The Context of Industry 4.0: A Systematic Literature ReviewDocument10 pagesProduct Lifecycle Management and Sustainable Development in The Context of Industry 4.0: A Systematic Literature ReviewJosip StjepandicNo ratings yet

- GLP BmsDocument18 pagesGLP BmsDr.Subhashish TripathyNo ratings yet

- Full Download Short Term Financial Management 3rd Edition Maness Test BankDocument35 pagesFull Download Short Term Financial Management 3rd Edition Maness Test Bankcimanfavoriw100% (31)

- Tran-Effects of Assisted JumpingDocument5 pagesTran-Effects of Assisted JumpingyoungjessNo ratings yet

- Pythagorean Theorem WorksheetDocument11 pagesPythagorean Theorem WorksheetJames ChanNo ratings yet

- Datasheet Ark XH Battery System EngDocument2 pagesDatasheet Ark XH Battery System EngLisa CowenNo ratings yet

- AR BuildingDocument819 pagesAR BuildingShithin KrishnanNo ratings yet

- Plato: Epistemology: Nicholas WhiteDocument2 pagesPlato: Epistemology: Nicholas WhiteAnonymous HCqIYNvNo ratings yet

- LPG GasDocument39 pagesLPG Gasv prasanthNo ratings yet

- Texto CuritibaDocument1 pageTexto CuritibaMargarida GuimaraesNo ratings yet

- Opex and CapexDocument5 pagesOpex and CapexATM Shafiq Ul AlamNo ratings yet

- Analysis of LaminatedDocument31 pagesAnalysis of LaminatedKaustubh JadhavNo ratings yet

- Chapter Three: 1 - The Coarse Grain SoilsDocument21 pagesChapter Three: 1 - The Coarse Grain SoilsSalih MohayaddinNo ratings yet

- ODA X9 2SL DatasheetDocument8 pagesODA X9 2SL DatasheetYudy UtamaNo ratings yet