Professional Documents

Culture Documents

Intel: Merom Clock Generator

Intel: Merom Clock Generator

Uploaded by

Barton EletronicsOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Intel: Merom Clock Generator

Intel: Merom Clock Generator

Uploaded by

Barton EletronicsCopyright:

Available Formats

1 2 3 4 5 6 7 8

PCB STACK UP www.bufanxiu.com

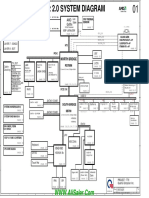

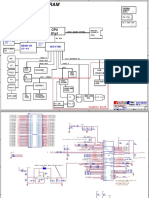

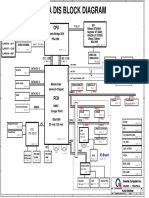

BU1 Block Diagram

LAYER 1 : TOP

LAYER 2 : SGND

Intel

LAYER 3 : IN1

CLOCK GENERATOR

Merom CK505

A A

LAYER 4 : IN2 (35W) ICS9LPR363

Page 2

LAYER 5 : VCC Page 3,4

LAYER 6 : BOT FSB(667/800MHZ)

R.G.B

CRT

Page 18

VCC_CORE 533/ 667 MHZ DDR II DDRII-SODIMM1

LVDS X1

LCD(WXGA 13W) Crestline GM DDRII-SODIMM2

Page 18 Page 12,13

+1.5V

SATA Page 5,7,8,9,10,11

SATA - HDD

Page 19 G SENSOR

+1.05V

PATA

IDE - ODD DMI(x2/x4)

Page 19

B +1.25V B

System 0

Page 24 USB PORT 0

PCI-Express

+1.8VSUS System 1

Page 24 USB PORT 1

ICH8M MINI CARD MINI CARD NEW CARD 100/10 LAN

+3VPCU System 2

WLAN RTL8101E

+3V_S5 Page 24 USB PORT 2 USB 2.0 Page 23 Page 23 (BOT) Page 24 (BOT) Page 20

+3VSUS

+3V WLAN

+5VPCU Page 23 USB PORT 3

+5V_S5 Connector

DAUGHTER Azalia PCI Bus

RJ11/RJ45/USB DAUGHTER BOARD

+5V BORD

Finger Printer (BOT) Page 14,15,16,17

SMDDR_VTERM Page 24 USB PORT 4

SMDDR_VREF PCMCIA Card RJ45 RJ11 USB

Bluetooth (BOT) LPC

32.768KHz

Controller Reader/1394

Page 24 USB PORT 5 (CB 1410) (R5C833)

Page 21 (BOT) Page 22

C New Card (BOT) C

Page 24 USB PORT 6 PCMCIA 1394

(BOT)

5 IN 1 (BOT)

Reserved (BOT)

WPC8763LDG

Page 23 USB PORT 7

PCI ROUTING

Page 26

TABLE IDSEL INTERUPT DEVICE

Camera (BOT)

REQ0# / GNT0# AD17 INTA#,INTB# R5C832

Page 18 USB PORT 8 REQ1# / GNT1# AD20 INTC# CB1410

FAN Touch Key FLASH

AUDIO/FM/USB DAUGHTER BOARD PAD Board ROM

HP HP AMP AUDIO CODEC

(ALC262) Connector

INT SPK SPK AMP BTO BOM OPTION

MDC 1.5 CB@ : CARD BUS

FP@ : FINGER PRINTER

D BT@ : BLUETOOTH D

Page 25 CM@ : CAMERA

GS@ : G-SENSOR

NEW@ : NEW CARD

USB LCD@ : LCD TYPE PANEL

LED@ : LED TYPE PANEL

1394@ : 1394

Quanta Computer Inc.

RJ11 PROJECT : BU1 Santa Rosa

Size Document Number Rev

Block Diagram 1A

Date: Monday, March 26, 2007 Sheet 1 of 33

1 2 3 4 5 6 7 8

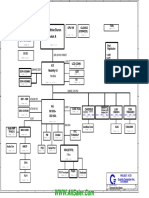

5 4 3 2 1

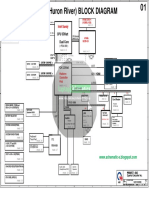

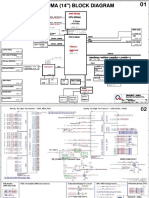

Clock Generator www.bufanxiu.com

Clock Gen Differential IO power +1.25V_VDD +1.25V

L25

+3V L26 PBY160808T-301Y-N_6 C411 .1U_4 PBY160808T-301Y-N_6

'EMI FILTER BKP1608HS181-T(180,1.5A)'

C426 C427 C428 C422 C425 C424 C419 C420 C416

R90

C414 .1U_4 *10U_810U_8 .1U_4 .1U_4 .1U_4 .1U_4 .1U_4 .1U_4

10U_8

D 0_6 C408 10U_8 D

H=1.2mm ICS9LPRS365BGLFT

0.1U close to each VDD_IO Power pin

SLG8SP512T: AL8SP512K05

C43 .1U_4 U22 IC(64P) ICS9LPRS365BGLFT(TSSOP)

VDD_CK_VDD_PCI 2 48

C418 .1U_4 VDD_CK_VDD_48 VDD_PCI IO_VOUT

9 VDD_48

VDD_CK_VDD_PCI 16 64 CGCLK_SMB

VDD_CK_VDD_REF VDD_PLL3 SCLK CGDAT_SMB

61 VDD_REF SDA 63

R404 CK505

C412 .1U_4 VDD_CK_VDD_PCI 39 38 PM_STPPCI# [16]

VDD_CK_VDD_CPU VDD_SRC SRC5/PCI_STOP#

55 VDD_CPU SRC5#/CPU_STOP# 37 PM_STPCPU# [16]

0_6

R68 +1.25V_VDD 12 54 CLK_CPU_BCLK_R RP50 1 2 0X2

VDD_96_IO CPU0 CLK_CPU_BCLK [3]

C415 .1U_4 20 53 CLK_CPU_BCLK#_R 3 4

VDD_PLL3_IO CPU0# CLK_CPU_BCLK# [3]

26 VDD_SRC_IO_1

0_6 45 51 CLK_MCH_BCLK_R RP52 1 2 0X2

VDD_SRC_IO_3 CPU1 CLK_MCH_BCLK [5]

36 50 CLK_MCH_BCLK#_R 3 4

VDD_SRC_IO_2 CPU1# CLK_MCH_BCLK# [5]

49 VDD_CPU_IO

SRC8/ITP 47

SRC8#/ITP# 46

R85 56_4 PCLK_DEBUG_R 1 35 CLK_PCIE_3GPLL#_R RP58 1 2 0X2

[23,26] PCLK_DEBUG PCI0/CR#_A SRC10# CLK_PCIE_3GPLL# [6]

<check list> 34 CLK_PCIE_3GPLL_R 3 4

SRC10 CLK_PCIE_3GPLL [6]

PCI4/SRC5_EN: PU be used, R81 56_4 PCLK_PCM_R 3

[21] PCLK_PCM PCI1/CR#_B

the CK505 will be configured to +3V R86 10K_4 33 CLK_MCH_OE#_R R410 475_4 CLK_MCH_OE# [6]

R78 56_4 PCLK_R5C833_R SRC11/CR#_H NEW_CLKREQ#_R R412 475_4

use Pin37/38 to SRC5 clock.If [22] PCLK_R5C833 4 32 NEW_CLKREQ# [24]

R82 *10K_4 PCI2/TME SRC11#/CR#_G

PD be detect at powe-on,the

CK505 will setting Pin 37/38 to R405 56_4 PCLK_591_R 5 30 CLK_PCIE_NEW_R RP59 3 4 0X2

[26] PCLK_591 PCI3 SRC9 CLK_PCIE_NEW [24]

PCI_STOP/CUP_SOTP(Default +3V R74 *10K_4 31 CLK_PCIE_NEW_R# 1 2

SRC9# CLK_PCIE_NEW# [24]

is setting to R73 22_4 PCI_CLK_SIO_R 6

R79 10K_4 PCI4/SRC5_EN CLK_PCIE_MINI2_R RP54

PCI_STOP/CUP_SOTP) SRC7/CR#_F 44 1 2 0X2 CLK_PCIE_MINI2 [23]

C R406 56_4 PCLK_ICH_R CLK_PCIE_MINI2#_R C

7 PCIF5/ITP_EN SRC7#/CR#_E 43 3 4 CLK_PCIE_MINI2# [23]

+3V R409 *10K_4

CG_XIN 60 41 CLK_PCIE_MINI_R RP56 1 2 0X2

[15] PCLK_ICH XTAL_IN SRC6 CLK_PCIE_MINI [23]

R407 10K_4 40 CLK_PCIE_MINI#_R 3 4

SRC6# CLK_PCIE_MINI# [23]

<check list> CG_XOUT 59 XTAL_OUT CLK_PCIE_LAN_R RP57

PCIF5/ITP_EN: PU be used,

SRC4 27 3 4 0X2 CLK_PCIE_LAN [20]

the CK505 will be configured R71 33_4 FSA 10 28 CLK_PCIE_LAN#_R 1 2

[16] CLKUSB_48 USB_48/FSA SRC4# CLK_PCIE_LAN# [20]

to use Pin46/47 to CPU ITP CLK_BSEL0 R72 2.2K_4

clock.If PD be detect at CLK_BSEL1 57 24 CLK_PCIE_ICH_R RP55 3 4 0X2

FSB/TEST/MODE SRC3/CR#_C CLK_PCIE_ICH [15]

powe-on,the CK505 will setting 25 CLK_PCIE_ICH#_R 1 2

SRC3#/CR#_D CLK_PCIE_ICH# [15]

Pin 46/47 to SRC8(Default is CLK_BSEL2 R87 2.2K_4 FSC 62 REF0/FSC/TESTSEL CLK_PCIE_SATA_R RP53

setting to SRC8) SRC2/SATA 21 3 4 0X2 CLK_PCIE_SATA [14]

R88 33_4 8 22 CLK_PCIE_SATA#_R 1 2

[16] 14M_ICH VSS_PCI SRC2#/SATA# CLK_PCIE_SATA# [14]

11 VSS_48

15 17 DREFSSCLK_R RP13 1 2 0X2

VSS_IO SRC1/SE1 DREFSSCLK [6]

19 18 DREFSSCLK#_R 3 4

VSS_PLL3 SRC1#/SE2 DREFSSCLK# [6]

52 VSS_CPU

23 13 DREFCLK_R RP51 3 4 0X2

VSS_SRC1 SRC0/DOT96 DREFCLK [6]

29 14 DREFCLK#_R 1 2

VSS_SRC2 SRC0#/DOT96# DREFCLK# [6]

42 VSS_SRC3

58 VSS_REF CKPWRGD/PWRDWN# 56 CK_PWRGD [16]

ICS9LPRS365AGLFT/ SLG8SP512T During initial power-up be used to

sample FSB speed with FSA/B/C

H=1.5mm

C407 30P_4 CG_XIN <check list>

(1)PCI2/TME: PU be used, the CK505 cannot over clock any of the clock for Trust Mode security purposes.

2

Y6

CL=20p (2)PCI4/SRC5_EN: PU be used, the CK505 will be configured to use Pin37/38 to SRC5 clock.

14.318MHZ If PD be detect at powe-on,the CK505 will setting Pin 37/38 to PCI_STOP/CUP_SOTP

Clock Gen I2C

(Default is setting to PCI_STOP/CUP_SOTP) +3V

1

B C406 30P_4 CG_XOUT B

<check list> (3)PCIF5/ITP_EN: PU be used, the CK505 will be configured to use Pin46/47 to CPU ITP clock. Q3

XTAL length < 500mils If PD be detect at powe-on,the CK505 will setting Pin 46/47 to SRC8 RHU002N06 R94

2

(Default is setting to SRC8)

10K_4

3 1 CGDAT_SMB

[13,16,19,23,24] SDATA

(4)SLG8SP512 Pin 6 select Pin 17, 18 output is LCDCLK or 27 M, PD is LCDCLK, PU is 27 M ,

Pin 37, 38 will fixed be use CPU_Stop and PCI_Stop.

(5)SLG505YC64 CK505 Standar parts follow standar setting +3V

Q4

CPU Clock select

RHU002N06 R95

2

BSEL Frequency Select Table [3] CPU_BSEL0

R59 0_4 CLK_BSEL0

MCH_BSEL0 [6]

10K_4

3 1 CGCLK_SMB

[13,16,19,23,24] SCLK

FSC FSB FSA Frequency

+1.05V R66 *56_4

0 0 0 266Mhz

FSA

R65 *1K_4

0 0 1 133Mhz

+3V

0 1 1 166Mhz

R80 0_4 CLK_BSEL1

[3] CPU_BSEL1 MCH_BSEL1 [6]

0 1 0 200Mhz R411 10K_4 NEW_CLKREQ#_R

R77 *0_4

A

1 1 0 400Mhz

A1A: (9/20) Remove 0ohm FSB A

+1.05V R408 *1K_4

1 1 1 Reserved

1 0 1 100Mhz R55 0_4 CLK_BSEL2

[3] CPU_BSEL2 MCH_BSEL2 [6]

R62 *0_4

Quanta Computer Inc.

1 0 0 333Mhz

FSC PROJECT : BU1 Santa Rosa

+1.05V R56 *1K_4 Size Document Number Rev

CLK. GEN./ CK505 1A

Date: Monday, March 26, 2007 Sheet 2 of 33

5 4 3 2 1

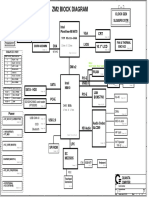

5 4 3 2 1

www.bufanxiu.com

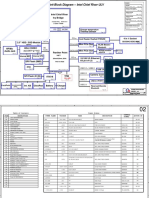

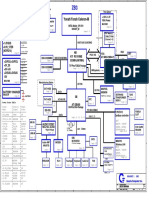

CPU Thermal monitor

U24A

[5] H_A#[16:3]

H_A#3 J4 H1

A[3]# ADS# H_ADS# [5]

CPU(HOST)

H_A#4

ADDR GROUP 0

L5 A[4]# BNR# E2 H_BNR# [5]

H_A#5 L4 G5 +3V

A[5]# BPRI# H_BPRI# [5]

H_A#6 K5

H_A#7 A[6]#

M3 A[7]# DEFER# H5 H_DEFER# [5]

H_A#8 N2 F21

A[8]# DRDY# H_DRDY# [5]

H_A#9 J1 E1

A[9]# DBSY# H_DBSY# [5]

H_A#10 N3

H_A#11 A[10]#

P5 A[11]# BR0# F1 H_BREQ#0 [5]

H_A#12 P2 A[12]#

CONTROL

H_A#13 L2 D20 H_IERR# R16 56.2_4 +1.05V

H_A#14 A[13]# IERR# +3V R431 R432 R437

P4 A[14]# INIT# B3 H_INIT# [14]

H_A#15 P1

H_A#16 A[15]# Q33 10K_4 10K_4 200_6

R1 A[16]# LOCK# H4 H_LOCK# [5]

2

D RHU002N06 LM86VCC D

[5] H_ADSTB0# M1 ADSTB[0]#

[5] H_REQ#[4:0] RESET# C1 H_CPURST# [5]

H_REQ#0 K3 F3 [18,26,27] MBCLK 3 1 C455

REQ[0]# RS[0]# H_RS#0 [5]

H_REQ#1 H2 F4

REQ[1]# RS[1]# H_RS#1 [5]

H_REQ#2 K2 G3 .1U_4

H_REQ#3 J3

REQ[2]# RS[2]#

G2

H_RS#2 [5]

+3V

H=1.75mm

REQ[3]# TRDY# H_TRDY# [5]

H_REQ#4 L1 U23

REQ[4]# Q34 H_THERMDA

[5] H_A#[35:17] HIT# G6 H_HIT# [5]

2

H_A#17 Y2 E4 RHU002N06 8 1

A[17]# HITM# H_HITM# [5] SCLK VCC

H_A#18 U5

H_A#19 A[18]# C454

R3 A[19]# BPM[0]# AD4 [18,26,27] MBDATA 3 1 7 SDA DXP 2

H_A#20

ADDR GROUP 1

W6 A[20]# BPM[1]# AD3

H_A#21 U4 AD1 6 3 2200P_4

XDP/ITP SIGNALS

H_A#22 A[21]# BPM[2]# ALERT# DXN

Y5 A[22]# BPM[3]# AC4

H_A#23 U1 AC2 *10K_4 4 5 H_THERMDC

H_A#24 A[23]# PRDY# R434 OVERT# GND

R4 A[24]# PREQ# AC1 +3V

H_A#25 T5 AC5 XDP_TCK

H_A#26 A[25]# TCK XDP_TDI MAX6657

T3 A[26]# TDI AA6

H_A#27 W2 AB3 [16] THERM_ALERT# R435 *0_4 THERM_ALERT#_R ADDRESS: 98H

H_A#28 A[27]# TDO XDP_TMS

W5 A[28]# TMS AB5

H_A#29 Y4 AB6 XDP_TRST# +3V R438 10K_4 THER_SHD# <check list>

H_A#30 A[29]# TRST# XDP_DBRESET# R19 0_4

U2 A[30]# DBR# C20 SYS_RST# [16] Layout Note:Routing 10:10 mils and away

H_A#31 V4

H_A#32 W3

A[31]# from noise source with ground gard

H_A#33 A[32]# R17 56.2_4

AA4 A[33]# THERMAL +1.05V

H_A#34 AB2

H_A#35 A[34]#

AA3 A[35]# PROCHOT# D21 H_PROCHOT_R# R18 *2.2K_4

H_PROCHOT# [29]

[5] H_ADSTB1# V1 ADSTB[1]# THERMDA A24 H_THERMDA

CPU FAN

THERMDC B25 H_THERMDC

[14] H_A20M# A6 A20M# <check list> +3V

THERMTRIP#_PWR

ICH

[14] H_FERR# A5 FERR# THERMTRIP# C7 Default PU 56ohm if no use.

[14] H_IGNNE# C4

C IGNNE# Serial R NC, If connect to power side PU 68ohm. Serial R 2.2K R458 C

R26 0_4 H_STPCLK_R# D5 330_4

[14] H_STPCLK# STPCLK#

[14] H_INTR C6 H CLK +3V

LINT0

[14] H_NMI B4 LINT1 BCLK[0] A22 CLK_CPU_BCLK [2]

[14] H_SMI# A3 A21 Q37

SMI# BCLK[1] CLK_CPU_BCLK# [2]

2

MMBT3904

TP_CPU_RSVD01 M4 R1

T3 RSVD[01]

TP_CPU_RSVD02 N5 THER_SHD# 1 3

T5 RSVD[02] SYS_SHDN# [28]

TP_CPU_RSVD03 T2 10K_4

T8 RSVD[03]

TP_CPU_RSVD04 V3

T1 RSVD[04]

TP_CPU_RSVD05 B2

T146 RSVD[05]

RESERVED

TP_CPU_RSVD06 C3

T7 RSVD[06]

TP_CPU_RSVD07 D2 [26] FANSIG

T6

TP_CPU_RSVD08 D22

RSVD[07] H=1.75mm

T9 RSVD[08] CN34

TP_CPU_RSVD09 D3 U26

T4 RSVD[09]

TP_CPU_RSVD10 F6 2 3 TH_FAN_POWER

T12 RSVD[10] +5V VIN VO 1 4

GND 5 2

C290 .1U_4 1 6

/FON GND C489 C491 C9 3 5

GND 7

Merom Ball-out Rev 1a 4 8 PTI_CWY030-B0G1Z

[5] H_D#[15:0] H_D#[47:32] [5] [26] VFAN VSET GND

U24B 10U_8 .01U_4 *.01U_4

H_D#0 E22 Y22 H_D#32 G995

H_D#1 D[0]# D[32]# H_D#33

F24 D[1]# D[33]# AB24

H_D#2 E26 V24 H_D#34

H_D#3 G22

D[2]# D[34]#

V26 H_D#35 FANPWR = 1.6*VSET

H_D#4 D[3]# D[35]# H_D#36

DATA GRP 0

F23 D[4]# D[36]# V23

H_D#5 G25 T22 H_D#37

H_D#6 D[5]# D[37]# H_D#38

E25 D[6]# D[38]# U25

PU/PD (ITP700) Thermal Trip

H_D#7 E23 U23 H_D#39

H_D#8 D[7]# D[39]# H_D#40

K24 Y25

DATA GRP 2

H_D#9 D[8]# D[40]# H_D#41 +1.05V

G24 D[9]# D[41]# W22

H_D#10 J24 Y23 H_D#42

B H_D#11 D[10]# D[42]# H_D#43 B

J23 D[11]# D[43]# W24

H_D#12 H22 W25 H_D#44 +1.05V

D[12]# D[44]#

3

H_D#13 F26 AA23 H_D#45

H_D#14 D[13]# D[45]# H_D#46

K22 D[14]# D[46]# AA24

H_D#15 H23 AB25 H_D#47

D[15]# D[47]# Q1 R23 D3

[5] H_DSTBN#0 J26 DSTBN[0]# DSTBN[2]# Y26 H_DSTBN#2 [5] [6,16,29] DELAY_VR_PWRGOOD 2

[5] H_DSTBP#0 H26 DSTBP[0]# DSTBP[2]# AA26 H_DSTBP#2 [5]

H25 U22 FDV301N *10K_4 *BAS316

[5] H_DINV#0 DINV[0]# DINV[2]# H_DINV#2 [5]

[5] H_D#[31:16] H_D#[63:48] [5]

1

H_D#16 N22 AE24 H_D#48 XDP_TMS R7 39_4 +1.05V C35 *1U_6

H_D#17 D[16]# D[48]# H_D#49

K25 D[17]# D[49]# AD24

H_D#18 P26 AA21 H_D#50

H_D#19 D[18]# D[50]# H_D#51

R23 D[19]# D[51]# AB22

H_D#20 L23 AB21 H_D#52 XDP_TDI R6 150_4

H_D#21 D[20]# D[52]# H_D#53 R25

DATA GRP 1

M24 D[21]# D[53]# AC26

H_D#22 L22 AD20 H_D#54

H_D#23 D[22]# D[54]# H_D#55 56.2_4 Q2

M23 D[23]# D[55]# AE22

2

H_D#24 P25 AF23 H_D#56 MMBT3904

+1.05V H_D#25 D[24]# D[56]# H_D#57

P23 D[25]# D[57]# AC25

H_D#26 P22 AE21 H_D#58 THERMTRIP#_PWR 1 3

DATA GRP 3

D[26]# D[58]# SYS_SHDN# [28]

<Check list & CRB> H_D#27 T24 AD21 H_D#59 <Check list & CRB>

H_D#28 D[27]# D[59]# H_D#60 XDP_TCK R5 27_4

Layout note: Z=55 ohm R24 D[28]# D[60]# AC22 Layout note: L<0.5"

H_D#29 L25 AD23 H_D#61

H_GTLREF<0.5" H_D#30 T25

D[29]# D[61]#

AF22 H_D#62 COMP0/2 Z=27.4ohm

H_D#31 D[30]# D[62]# H_D#63 COMP1/3 Z=54.9 R24 *0_4

N25 D[31]# D[63]# AC23 PM_THRMTRIP# [6,14]

R11 L26 AE25 XDP_TRST# R4 680_4

[5] H_DSTBN#1 DSTBN[1]# DSTBN[3]# H_DSTBN#3 [5]

1K_4 M26 AF24

[5] H_DSTBP#1 DSTBP[1]# DSTBP[3]# H_DSTBP#3 [5]

[5] H_DINV#1 N24 DINV[1]# DINV[3]# AC20 H_DINV#3 [5] <CRB & Design guide>

Layout Note:Connect from

H_GTLREF AD26

GTLREF COMP[0] R26 COMP0 R14 27.4_6

SB and daisy chain to CPU <CRB & Design guide>

R21 *1K_4 CPU_TEST1 C23 MISC U26 COMP1 R13 54.9_4 Layout Note: Thermal trip should connect to ICH8 & GMCH without T-ing

A R20 *1K_4 CPU_TEST2 D25 TEST1 COMP[1] COMP2 R10 27.4_6 CORE VR.Not use T A

AA1

CPU_TEST3 C24 TEST2 COMP[2]

Y1 COMP3 R8 54.9_4 connect.(SB/VR/CPU/NB) (ZS1 default NC)

T10 TEST3 COMP[3]

C14 *.1U_4 CPU_TEST4 AF26

CPU_TEST5 AF1 TEST4

T2 TEST5 DPRSTP# E5 ICH_DPRSTP# [6,14,29]

CPU_TEST6 A26 B5

T11 TEST6 DPSLP# H_DPSLP# [14]

R9 D24

DPWR# H_DPWR# [5]

2K_6 B22 D6

[2] CPU_BSEL0 BSEL[0] PWRGOOD H_PWRGD [14]

B23 D7

[2] CPU_BSEL1

[2] CPU_BSEL2 C21

BSEL[1]

BSEL[2]

SLP#

PSI# AE6

H_CPUSLP# [5]

PSI# [29]

Quanta Computer Inc.

Merom Ball-out Rev 1a

PROJECT : BU1 Santa Rosa

Size Document Number Rev

CPU(1 of 2)/FAN/Thermal 3A

Date: Monday, March 26, 2007 Sheet 3 of 33

5 4 3 2 1

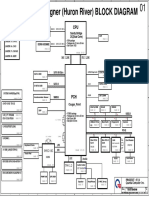

5 4 3 2 1

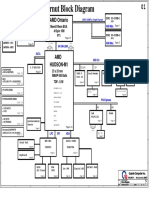

CPU(Power)

VCC_CORE www.bufanxiu.com

U24D

A4 VSS[001] VSS[082] P6

A8 VSS[002] VSS[083] P21

A11 VSS[003] VSS[084] P24

A14 VSS[004] VSS[085] R2

U24C A16 R5

VSS[005] VSS[086]

A7 VCC[001] VCC[068] AB20 <REV.NO. 0.5/REF.NO.19343> A19 VSS[006] VSS[087] R22

C465 C25 C466 C461 C473 C472 C477 C471 C21 C476 A9 AB7 A23 R25

VCC[002] VCC[069] VSS[007] VSS[088]

A10 AC7 AF2 T1

D 10U_8 10U_8 10U_8 10U_8 10U_8 10U_8 10U_8 10U_8 10U_8 10U_8 A12

VCC[003] VCC[070]

AC9

Ivcc Max 52A B6

VSS[008] VSS[089]

T4 D

VCC[004] VCC[071] VSS[009] VSS[090]

A13 VCC[005] VCC[072] AC12 B8 VSS[010] VSS[091] T23

A15 VCC[006] VCC[073] AC13 Ivccp Max 6A(VCCP supply before Vcc stable) B11 VSS[011] VSS[092] T26

A17 VCC[007] VCC[074] AC15 Max 2A(VCCP supply after Vcc stable) B13 VSS[012] VSS[093] U3

A18 VCC[008] VCC[075] AC17 B16 VSS[013] VSS[094] U6

A20 VCC[009] VCC[076] AC18 B19 VSS[014] VSS[095] U21

B7 AD7 Ivcca Max 130mA B21 U24

VCC[010] VCC[077] VSS[015] VSS[096]

B9 VCC[011] VCC[078] AD9 B24 VSS[016] VSS[097] V2

B10 VCC[012] VCC[079] AD10 C5 VSS[017] VSS[098] V5

B12 VCC[013] VCC[080] AD12 C8 VSS[018] VSS[099] V22

C475 C469 C463 C474 C464 C19 C20 C23 C459 C460 B14 AD14 C11 V25

VCC[014] VCC[081] +1.05V VSS[019] VSS[100]

B15 VCC[015] VCC[082] AD15 C14 VSS[020] VSS[101] W1

10U_8 10U_8 10U_8 10U_8 10U_8 10U_8 10U_8 10U_8 10U_8 10U_8 B17 AD17 C16 W4

VCC[016] VCC[083] VSS[021] VSS[102]

B18 VCC[017] VCC[084] AD18 C19 VSS[022] VSS[103] W23

B20 VCC[018] VCC[085] AE9 C2 VSS[023] VSS[104] W26

C9 VCC[019] VCC[086] AE10 C22 VSS[024] VSS[105] Y3

C10 VCC[020] VCC[087] AE12 C25 VSS[025] VSS[106] Y6

C12 AE13 C16 C18 C17 C456 C15 C22 D1 Y21

VCC[021] VCC[088] VSS[026] VSS[107]

C13 VCC[022] VCC[089] AE15 D4 VSS[027] VSS[108] Y24

C15 AE17 .1U_6 .1U_6 .1U_6 .1U_6 .1U_6 .1U_6 D8 AA2

VCC[023] VCC[090] VSS[028] VSS[109]

C17 VCC[024] VCC[091] AE18 D11 VSS[029] VSS[110] AA5

DESIGN GUIDE C18 VCC[025] VCC[092] AE20 D13 VSS[030] VSS[111] AA8

C31 C28 C470 C462 C30 C467 D9 AF9 D16 AA11

CHANGE FROM 22UF *20 TO 10UF *32 D10

VCC[026] VCC[093]

AF10 D19

VSS[031] VSS[112]

AA14

10U_8 10U_8 10U_8 10U_8 10U_8 10U_8 VCC[027] VCC[094] VSS[032] VSS[113]

D12 VCC[028] VCC[095] AF12 D23 VSS[033] VSS[114] AA16

D14 VCC[029] VCC[096] AF14 D26 VSS[034] VSS[115] AA19

D15 VCC[030] VCC[097] AF15 E3 VSS[035] VSS[116] AA22

D17 VCC[031] VCC[098] AF17 E6 VSS[036] VSS[117] AA25

D18 AF18 <CRB> +1.05V E8 AB1

VCC[032] VCC[099] VSS[037] VSS[118]

E7 VCC[033] VCC[100] AF20 R for test only E11 VSS[038] VSS[119] AB4

E9 VCC[034] E14 VSS[039] VSS[120] AB8

E10 G21 CPU_G21 R15 0_4 E16 AB11

C VCC[035] VCCP[01] CPU_V6 R12 0_4 VSS[040] VSS[121] C

E12 VCC[036] VCCP[02] V6 E19 VSS[041] VSS[122] AB13

E13 VCC[037] VCCP[03] J6 E21 VSS[042] VSS[123] AB16

C468 C27 C458 C24 C26 C457 E15 K6 + C36 E24 AB19

VCC[038] VCCP[04] VSS[043] VSS[124]

10U_8 E17 VCC[039] VCCP[05] M6 <Check list> F5 VSS[044] VSS[125] AB23

10U_8 10U_8 10U_8 10U_8 10U_8 CH6102K9A01 E18 J21 330U_7343 ESR=12m ohm F8 AB26

'CAP CHIP 10U 10V(+-10%,X5R,0805)' VCC[040] VCCP[06] VSS[045] VSS[126]

E20 VCC[041] VCCP[07] K21 F11 VSS[046] VSS[127] AC3

F7 VCC[042] VCCP[08] M21 F13 VSS[047] VSS[128] AC6

F9 VCC[043] VCCP[09] N21 F16 VSS[048] VSS[129] AC8

F10 VCC[044] VCCP[10] N6 F19 VSS[049] VSS[130] AC11

F12 VCC[045] VCCP[11] R21 F2 VSS[050] VSS[131] AC14

F14 VCC[046] VCCP[12] R6 F22 VSS[051] VSS[132] AC16

F15 VCC[047] VCCP[13] T21 F25 VSS[052] VSS[133] AC19

+ C32 + C13 + C29 F17 T6 G4 AC21

VCC[048] VCCP[14] +1.5V VSS[053] VSS[134]

F18 VCC[049] VCCP[15] V21 <CRB> G1 VSS[054] VSS[135] AC24

F20 VCC[050] VCCP[16] W21 .01U near to B26 ball G23 VSS[055] VSS[136] AD2

330U_7343 *330U_7343 330U_7343 AA7 G26 AD5

VCC[051] +VCCA_PROC R22 0_6 VSS[056] VSS[137]

AA9 VCC[052] VCCA[01] B26 H3 VSS[057] VSS[138] AD8

AA10 VCC[053] VCCA[02] C26 H6 VSS[058] VSS[139] AD11

AA12 VCC[054] H21 VSS[059] VSS[140] AD13

AA13 AD6 VCC_CORE C33 C34 H24 AD16

VCC[055] VID[0] H_VID0 [29] VSS[060] VSS[141]

AA15 VCC[056] VID[1] AF5 H_VID1 [29] J2 VSS[061] VSS[142] AD19

<Check list> AA17 VCC[057] VID[2] AE5 H_VID2 [29]

.01U_4 10U_8 J5 VSS[062] VSS[143] AD22

Option1:330U*6(ESR=1.5m ohm aggregate , ESL=0.8nH/6) and 22U*20(ESR=3mohm typ/20 , ESL=0.6nH/20) AA18 VCC[058] VID[3] AF4 H_VID3 [29] J22 VSS[063] VSS[144] AD25

AA20 AE3 R2 J25 AE1

Option2:330U*6(ESR=1.5m ohm aggregate , ESL=1.8nH/6) and 22U*32(ESR=3mohm typ/32 , ESL=0.6nH/32) VCC[059] VID[4] H_VID4 [29] VSS[064] VSS[145]

AB9 VCC[060] VID[5] AF3 H_VID5 [29] K1 VSS[065] VSS[146] AE4

AC10 AE2 100/F_6 K4 AE8

VCC[061] VID[6] H_VID6 [29] VSS[066] VSS[147]

AB10 VCC[062] K23 VSS[067] VSS[148] AE11

AB12 VCC[063] K26 VSS[068] VSS[149] AE14

AB14 VCC[064] VCCSENSE AF7 VCCSENSE [29] L3 VSS[069] VSS[150] AE16

AB15 VCC[065] L6 VSS[070] VSS[151] AE19

AB17 VCC[066] L21 VSS[071] VSS[152] AE23

AB18 VCC[067] VSSSENSE AE7 VSSSENSE [29] L24 VSS[072] VSS[153] AE26

B B

M2 VSS[073] VSS[154] A2

Merom Ball-out Rev 1a M5 AF6

VSS[074] VSS[155]

. <Demo board> M22 VSS[075] VSS[156] AF8

R3 Routing 27.4ohm with 50mils spacing M25 AF11

VSS[076] VSS[157]

N1 AF13

100/F_6 PU/PD near to CPU 1" N4

VSS[077] VSS[158]

AF16

VSS[078] VSS[159]

N23 VSS[079] VSS[160] AF19

N26 VSS[080] VSS[161] AF21

P3 VSS[081] VSS[162] A25

VSS[163] AF25

Merom Ball-out Rev 1a

.

A A

Quanta Computer Inc.

PROJECT : BU1 Santa Rosa

Size Document Number Rev

CPU(2 of 2) 1A

Date: Monday, March 26, 2007 Sheet 4 of 33

5 4 3 2 1

5 4 3 2 1

NB(HOST) www.bufanxiu.com

U21A

H_A#[35:3] [3]

[3] H_D#[63:0]

J13 H_A#3

H_D#0 H_A#_3 H_A#4

E2 H_D#_0 H_A#_4 B11

+1.05V H_D#1 G2 C11 H_A#5

H_D#2 H_D#_1 H_A#_5 H_A#6

G7 H_D#_2 H_A#_6 M11

H_D#3 M6 C15 H_A#7

H_D#4 H_D#_3 H_A#_7 H_A#8

H7 H_D#_4 H_A#_8 F16

H_D#5 H3 L13 H_A#9

R416 H_D#6 H_D#_5 H_A#_9 H_A#10

D G4 H_D#_6 H_A#_10 G17 D

H_D#7 F3 C14 H_A#11

221/F_4 H_D#8 H_D#_7 H_A#_11 H_A#12

N8 H_D#_8 H_A#_12 K16

H_D#9 H2 B13 H_A#13

H_SWING H_D#10 H_D#_9 H_A#_13 H_A#14

M10 H_D#_10 H_A#_14 L16

H_D#11 N12 J17 H_A#15

H_D#12 H_D#_11 H_A#_15 H_A#16

N9 H_D#_12 H_A#_16 B14

R417 C436 <check list> H_D#13 H5 K19 H_A#17

100/F_4 H_D#14 H_D#_13 H_A#_17 H_A#18

0.1U close to B3 P13 H_D#_14 H_A#_18 P15

.1U_4 H_D#15 K9 R17 H_A#19

H_D#16 H_D#_15 H_A#_19 H_A#20

M2 H_D#_16 H_A#_20 B16

H_D#17 W10 H20 H_A#21

H_D#18 H_D#_17 H_A#_21 H_A#22

Y8 H_D#_18 H_A#_22 L19

H_D#19 V4 D17 H_A#23

H_D#20 H_D#_19 H_A#_23 H_A#24

M3 H_D#_20 H_A#_24 M17

H_D#21 J1 N16 H_A#25

H_D#22 H_D#_21 H_A#_25 H_A#26

N5 H_D#_22 H_A#_26 J19

H_D#23 N3 B18 H_A#27

H_D#24 H_D#_23 H_A#_27 H_A#28

W6 H_D#_24 H_A#_28 E19

H_D#25 W9 B17 H_A#29

H_D#26 H_D#_25 H_A#_29 H_A#30

N2 H_D#_26 H_A#_30 B15

H_RCOMP H_D#27 Y7 E17 H_A#31

H_D#28 H_D#_27 H_A#_31 H_A#32

Y9 H_D#_28 H_A#_32 C18 H_A#[35:32] are not supported in

<check list> H_D#29 P4 A19 H_A#33 Calero Interposer

R415 H_D#30 H_D#_29 H_A#_33 H_A#34

10:20 mils(Width:Spacing) W3 B19

C

H_D#31 N1

H_D#_30 H_A#_34

N19 H_A#35 Crestline support 36 bit address C

24.9/F_4 H_D#32 H_D#_31 H_A#_35

AD12 H_D#_32

H_D#33 AE3 G12

H_D#_33 H_ADS# H_ADS# [3]

H_D#34 AD9 H17

HOST

H_D#_34 H_ADSTB#_0 H_ADSTB0# [3]

H_D#35 AC9 G20

H_D#_35 H_ADSTB#_1 H_ADSTB1# [3]

H_D#36 AC7 C8

H_D#_36 H_BNR# H_BNR# [3]

H_D#37 AC14 E8

H_D#_37 H_BPRI# H_BPRI# [3]

H_D#38 AD11 F12

H_D#_38 H_BREQ# H_BREQ#0 [3]

H_D#39 AC11 D6

H_D#_39 H_DEFER# H_DEFER# [3]

H_D#40 AB2 C10

+1.05V H_D#_40 H_DBSY# H_DBSY# [3]

H_D#41 AD7 AM5

H_D#_41 HPLL_CLK CLK_MCH_BCLK [2]

H_D#42 AB1 AM7

H_D#_42 HPLL_CLK# CLK_MCH_BCLK# [2]

H_D#43 Y3 H8

H_D#_43 H_DPWR# H_DPWR# [3]

H_D#44 AC6 K7

H_D#_44 H_DRDY# H_DRDY# [3]

H_D#45 AE2 E4

H_D#_45 H_HIT# H_HIT# [3]

R76 H_D#46 AC5 C6

H_D#_46 H_HITM# H_HITM# [3]

H_D#47 AG3 G10

H_D#_47 H_LOCK# H_LOCK# [3]

54.9/F_4 <check list> H_D#48 AJ9 B7

H_D#_48 H_TRDY# H_TRDY# [3]

Impedance 55ohm H_D#49 AH8

H_SCOMP H_D#50 H_D#_49

AJ14 H_D#_50

H_D#51 AE9

H_D#52 H_D#_51

AE11 H_D#_52 H_DINV#[3:0] [3]

H_D#53 AH12 K5 H_DINV#0

H_D#54 H_D#_53 H_DINV#_0 H_DINV#1

AJ5 H_D#_54 H_DINV#_1 L2

B H_D#55 AH5 AD13 H_DINV#2 B

+1.05V H_D#56 H_D#_55 H_DINV#_2 H_DINV#3

AJ6 H_D#_56 H_DINV#_3 AE13

H_D#57 AE7 H_D#_57 H_DSTBN#[3:0] [3]

H_D#58 AJ7 M7 H_DSTBN#0

H_D#59 H_D#_58 H_DSTBN#_0 H_DSTBN#1

AJ2 H_D#_59 H_DSTBN#_1 K3

H_D#60 AE5 AD2 H_DSTBN#2

R75 H_D#61 H_D#_60 H_DSTBN#_2 H_DSTBN#3

AJ3 H_D#_61 H_DSTBN#_3 AH11

<check list> H_D#62 AH2 H_D#_62 H_DSTBP#[3:0] [3]

54.9/F_4 Impedance 55ohm H_D#63 AH13 L7 H_DSTBP#0

H_D#_63 H_DSTBP#_0 H_DSTBP#1

H_DSTBP#_1 K2

H_SCOMP# AC2 H_DSTBP#2

H_SWING H_DSTBP#_2 H_DSTBP#3

B3 H_SWING H_DSTBP#_3 AJ10

H_RCOMP C2

+1.05V H_RCOMP H_REQ#[4:0] [3]

M14 H_REQ#0

H_SCOMP H_REQ#_0 H_REQ#1

W1 H_SCOMP H_REQ#_1 E13

H_SCOMP# W2 A11 H_REQ#2

H_SCOMP# H_REQ#_2 H_REQ#3

H_REQ#_3 H13

B6 B12 H_REQ#4

[3] H_CPURST# H_CPURST# H_REQ#_4

R418 E5

[3] H_CPUSLP# H_CPUSLP# H_RS#[2:0] [3]

E12 H_RS#0

1K_4 H_RS#_0 H_RS#1

H_RS#_1 D7

D8 H_RS#2

H_AVREF H_RS#_2

B9 H_AVREF

A9 H_DVREF

A A

R422 C432 <check list> CRESTLINE_1p0

0.1U close to B9

2K_4 .1U_4

Quanta Computer Inc.

PROJECT : BU1 Santa Rosa

Size Document Number Rev

1A

GMCH HOST(1 of 7)

Date: Monday, March 26, 2007 Sheet 5 of 33

5 4 3 2 1

5 4 3 2 1

www.bufanxiu.com

U21B

+VCC_PEG

MCH_RSVD1 P36 U21C

T30 RSVD1

MCH_RSVD2 P37 AV29

T32 RSVD2 SM_CK_0 M_CLK_DDR0 [13]

MCH_RSVD3 R35 BB23 J40

T31 RSVD3 SM_CK_1 M_CLK_DDR1 [13] [18] INT_LVDS_PWM L_BKLT_CTRL

MCH_RSVD4 N35 BA25 H39 N43 EXP_A_COMPX R67 24.9_4

T28 RSVD4 SM_CK_3 M_CLK_DDR3 [13] [18,26] INT_LVDS_BLON L_BKLT_EN PEG_COMPI

MCH_RSVD5 AR12 AV23 +3V R414 10K_4 E39 M43

T40 RSVD5 SM_CK_4 M_CLK_DDR4 [13] L_CTRL_CLK PEG_COMPO

MCH_RSVD6 AR13 R429 10K_4 E40

T41 RSVD6 L_CTRL_DATA

MCH_RSVD7 AM12 AW30 C37

T36 RSVD7 SM_CK#_0 M_CLK_DDR#0 [13] [18] INT_LVDS_EDIDCLK L_DDC_CLK

MCH_RSVD8 AN13 BA23 D35 J51

T37 RSVD8 SM_CK#_1 M_CLK_DDR#1 [13] [18] INT_LVDS_EDIDDATA L_DDC_DATA PEG_RX#_0

MCH_RSVD9 J12 AW25 K40 L51

T22 RSVD9 SM_CK#_3 M_CLK_DDR#3 [13] [18] INT_LVDS_DIGON L_VDD_EN PEG_RX#_1

MCH_RSVD10

RSVD

T39 AR37 RSVD10 SM_CK#_4 AW23 M_CLK_DDR#4 [13] PEG_RX#_2 N47

MCH_RSVD11 AM36 R57 2.4K_4 LVDS_IBG L41 T45

T38 RSVD11 LVDS_IBG PEG_RX#_3

MCH_RSVD12 AL36 BE29 L43 T50

T35 RSVD12 SM_CKE_0 M_CKE0 [12,13] T25 LVDS_VBG PEG_RX#_4

MCH_RSVD13 AM37 AY32 N41 U40

D T34 RSVD13 SM_CKE_1 M_CKE1 [12,13] LVDS_VREFH PEG_RX#_5

MCH_RSVD14 D20 BD39 N40 Y44 D

T14 RSVD14 SM_CKE_3 M_CKE3 [12,13] LVDS_VREFL PEG_RX#_6

SM_CKE_4 BG37 M_CKE4 [12,13] [18] INT_TXLCLKOUT- D46 LVDSA_CLK# PEG_RX#_7 Y40

[18] INT_TXLCLKOUT+ C45 LVDSA_CLK PEG_RX#_8 AB51

C41 .1U_4 BG20 D44 W49

SM_CS#_0 M_CS#0 [12,13] LVDSB_CLK# PEG_RX#_9

SM_CS#_1 BK16 M_CS#1 [12,13] E42 LVDSB_CLK PEG_RX#_10 AD44

LVDS

SM_CS#_2 BG16 M_CS#2 [12,13] PEG_RX#_11 AD40

MCH_RSVD20 H10 BE13 G51 AG46

T18 RSVD20 SM_CS#_3 M_CS#3 [12,13] [18] INT_TXLOUT0- LVDSA_DATA#_0 PEG_RX#_12

MCH_RSVD21 B51 E51 AH49

MUXING

T125 RSVD21 [18] INT_TXLOUT1- LVDSA_DATA#_1 PEG_RX#_13

MCH_RSVD22 BJ20 BH18 F49 AG45

T112 RSVD22 SM_ODT_0 M_ODT0 [12,13] [18] INT_TXLOUT2- LVDSA_DATA#_2 PEG_RX#_14

MCH_RSVD23 BK22 BJ15 AG41

T113 RSVD23 SM_ODT_1 M_ODT1 [12,13] PEG_RX#_15

GRAPHICS

MCH_RSVD24 BF19 BJ14

T47 RSVD24 SM_ODT_2 M_ODT2 [12,13]

MCH_RSVD25 BH20 BE16 G50 J50

T51 RSVD25 SM_ODT_3 M_ODT3 [12,13] [18] INT_TXLOUT0+ LVDSA_DATA_0 PEG_RX_0

MCH_RSVD26 BK18 E50 L50

T116 RSVD26 [18] INT_TXLOUT1+ LVDSA_DATA_1 PEG_RX_1

MCH_RSVD27 BJ18 BL15 M_RCOMP F48 M47

T53 RSVD27 SM_RCOMP [18] INT_TXLOUT2+ LVDSA_DATA_2 PEG_RX_2

MCH_RSVD28 BF23 BK14 M_RCOMP# U44

T49 RSVD28 SM_RCOMP# SMDDR_VREF PEG_RX_3

MCH_RSVD29 BG23 T49

T50 RSVD29 PEG_RX_4

MCH_RSVD30 BC23 BK31 SM_RCOMP_VOH G44 T41

T48 RSVD30 SM_RCOMP_VOH LVDSB_DATA#_0 PEG_RX_5

MCH_RSVD31 BD24 BL31 SM_RCOMP_VOL B47 W45

T46

DDR

RSVD31 SM_RCOMP_VOL LVDSB_DATA#_1 PEG_RX_6

[12,13] M_A_A14 BJ29 RSVD32 B45 LVDSB_DATA#_2 PEG_RX_7 W41

BE24 AR49 SMDDR_VREF_MCH R108 0_6 AB50

[12,13] M_B_A14 RSVD33 SM_VREF_0 PEG_RX_8

MCH_RSVD34 BH39 AW4 Y48

T45 RSVD34 SM_VREF_1 PEG_RX_9

MCH_RSVD35 AW20 R107 *10K_6 +1.8VSUS E44 AC45

T44 RSVD35 LVDSB_DATA_0 PEG_RX_10

MCH_RSVD36 BK20 R98 *10K_6 A47 AC41

T52 RSVD36 LVDSB_DATA_1 PEG_RX_11

MCH_RSVD37 C48 A45 AH47

T141 RSVD37 LVDSB_DATA_2 PEG_RX_12

MCH_RSVD38 DREFCLK

PCI-EXPRESS

T15 D47 RSVD38 DPLL_REF_CLK B42 DREFCLK [2] PEG_RX_13 AG49

MCH_RSVD39 B44 C42 DREFCLK# AH45

T132 RSVD39 DPLL_REF_CLK# DREFCLK# [2] PEG_RX_14

MCH_RSVD40 C44 H48 DREFSSCLK AG42

T135 RSVD40 DPLL_REF_SSCLK DREFSSCLK [2] PEG_RX_15

MCH_RSVD41 A35 H47 DREFSSCLK#

T142 RSVD41 DPLL_REF_SSCLK# DREFSSCLK# [2]

MCH_RSVD42 B37 E27 N45

T145 RSVD42 TVA_DAC PEG_TX#_0

MCH_RSVD43 B36 K44 G27 U39

T129 RSVD43 PEG_CLK CLK_PCIE_3GPLL [2] TVB_DAC PEG_TX#_1

CLK

MCH_RSVD44 B34 K45 K27 U47

T138 RSVD44 PEG_CLK# CLK_PCIE_3GPLL# [2] TVC_DAC PEG_TX#_2

MCH_RSVD45

TV

T131 C34 RSVD45 PEG_TX#_3 N51

C C

DMI_TXN[3:0] [15] F27 TVA_RTN PEG_TX#_4 R50

J27 TVB_RTN PEG_TX#_5 T42

AN47 DMI_TXN0 L27 Y43

DMI_RXN_0 DMI_TXN1 TVC_RTN PEG_TX#_6

DMI_RXN_1 AJ38 PEG_TX#_7 W46

AN42 DMI_TXN2 M35 W38

DMI_RXN_2 DMI_TXN3 TV_DCONSEL_0 PEG_TX#_8

DMI_RXN_3 AN46 DMI_TXP[3:0] [15] P33 TV_DCONSEL_1 PEG_TX#_9 AD39

PEG_TX#_10 AC46

AM47 DMI_TXP0 R34 *0_4 AC49

DMI_RXP_0 DMI_TXP1 R37 *0_4 PEG_TX#_11

[2] MCH_BSEL0 P27 CFG_0 DMI_RXP_1 AJ39 PEG_TX#_12 AC42

N27 AN41 DMI_TXP2 AH39

[2] MCH_BSEL1 CFG_1 DMI_RXP_2 PEG_TX#_13

N24 AN45 DMI_TXP3 AE49

[2] MCH_BSEL2 CFG_2 DMI_RXP_3 DMI_RXN[3:0] [15] PEG_TX#_14

MCH_CFG_3 C21 AH44

T130 CFG_3 PEG_TX#_15

MCH_CFG_4 C23 AJ46 DMI_RXN0

T134 CFG_4 DMI_TXN_0

[11] MCH_CFG_5 F23 CFG_5 DMI_TXN_1 AJ41 DMI_RXN1 [18] CRT_B

CRT_B H32 CRT_BLUE PEG_TX_0 M45

MCH_CFG_6 N23 AM40 DMI_RXN2 G32 T38

T29 CFG_6 DMI_TXN_2 CRT_BLUE# PEG_TX_1

MCH_CFG_7 G23 AM44 DMI_RXN3 CRT_G K29 T46

T19 CFG_7 DMI_TXN_3 DMI_RXP[3:0] [15] [18] CRT_G CRT_GREEN PEG_TX_2

MCH_CFG_8 J20 J29 N50

T20

DMI

CFG_8 CRT_GREEN# PEG_TX_3

AJ47 DMI_RXP0 CRT_R

CFG

[11] MCH_CFG_9 C20 CFG_9 DMI_TXP_0 [18] CRT_R F29 CRT_RED PEG_TX_4 R51

MCH_CFG_10 AJ42 DMI_RXP1

VGA

T33 R24 CFG_10 DMI_TXP_1 E29 CRT_RED# PEG_TX_5 U43

MCH_CFG_11 L23 AM39 DMI_RXP2 W42

T27 CFG_11 DMI_TXP_2 PEG_TX_6

[11] MCH_CFG_12 J23 CFG_12 DMI_TXP_3 AM43 DMI_RXP3 PEG_TX_7 Y47

[11] MCH_CFG_13 E23 DDCCLK K33 Y39

CFG_13 [18] DDCCLK CRT_DDC_CLK PEG_TX_8

MCH_CFG_14 E20 DDCDAT G35 AC38

T13 CFG_14 [18] DDCDAT CRT_DDC_DATA PEG_TX_9

MCH_CFG_15 K23 R41 30_4 HSYNC_A F33 AD47

T23 CFG_15 [18] HSYNC CRT_HSYNC PEG_TX_10

[11] MCH_CFG_16 M20 R419 1.3K_6 CRTIREF C32 AC50

MCH_CFG_17 CFG_16 R40 30_4 VSYNC_A CRT_TVO_IREF PEG_TX_11

T26 M24 CFG_17 [18] VSYNC E33 CRT_VSYNC PEG_TX_12 AD43

GRAPHICS VID

MCH_CFG_18 L32 AG39

T21 CFG_18 PEG_TX_13

[11] MCH_CFG_19 N33 CFG_19 PEG_TX_14 AE50

[11] MCH_CFG_20 L35 CFG_20 PEG_TX_15 AH43

E35 T16 CRESTLINE_1p0

B R50 0_4 PM_BMBUSY#_R GFX_VID_0 T144 B

[16] PM_BMBUSY# G41 PM_BM_BUSY# GFX_VID_1 A39

[3,14,29] ICH_DPRSTP# R45 0_4 ICH_DPRSTP#_R L39 C38 T133

PM_EXTTS#0 PM_DPRSTP# GFX_VID_2 T140

[13] PM_EXTTS#0 L36 PM_EXT_TS#_0 GFX_VID_3 B39

R38 0_4 PM_EXTTS#1_R T143 R46 150_4 CRT_B

PM

[13] PM_EXTTS#1 J36 PM_EXT_TS#_1 GFX_VR_EN E36

3,16,29] DELAY_VR_PWRGOOD AW49 PWROK

R97 100_4RST_IN#_MCH AV20 R52 150_4 CRT_G

[15] PLTRST#_NB RSTIN# +1.25V_AXD

[3,14] PM_THRMTRIP# R64 PM_THRMTRIP#_GMCH N20

*0_4

R42 0_4PM_DPRSLPVR_GMCH G36 THERMTRIP# R49 150_4 CRT_R

[16,29] PM_DPRSLPVR DPRSLPVR

AM49 R84

CL_CLK CL_CLK0 [16]

CL_DATA AK50 CL_DATA0 [16]

T122 TP_MCH_NC1 BJ51 AT43 1K_4

NC_1 CL_PWROK MPWROK [16]

T123 TP_MCH_NC2 BK51 AN49

ME

NC_2 CL_RST# CL_RST#0 [16]

T120 TP_MCH_NC3 BK50 AM50 +1.25V_CL_VREF

TP_MCH_NC4 NC_3 CL_VREF

T118 BL50

TP_MCH_NC5 NC_4

T114 BL49

TP_MCH_NC6 NC_5 C67 R83

T117 BL3

TP_MCH_NC7 NC_6

T115 BL2

TP_MCH_NC8 NC_7 .1U_4 392_6

NC

T121 BK1

TP_MCH_NC9 NC_8 T17

T124 BJ1 H35

TP_MCH_NC10 NC_9 SDVO_CTRL_CLK T24

T126 E1 K36

MISC

TP_MCH_NC11 NC_10 SDVO_CTRL_DATA

T139 A5 NC_11 CLK_REQ# G39 CLK_MCH_OE# CLK_MCH_OE# [2]

T127 TP_MCH_NC12 C51 G40

NC_12 ICH_SYNC# MCH_ICH_SYNC# [16]

T128 TP_MCH_NC13 B50

TP_MCH_NC14 NC_13

T137 A50

TP_MCH_NC15 NC_14

T136 A49 NC_15 TEST_1 A37 GMCH_TEST1 R428 0_4

T119 TP_MCH_NC16 BK2 R32 GMCH_TEST2 R70 20K_4

NC_16 TEST_2

CRESTLINE_1p0

+1.8VSUS R106 1K_4 SM_RCOMP_VOH

A R104 C93 C95 A

3.01K_4 .01U_4 2.2U_6

M_RCOMP# +1.8VSUS +3V

R102 SM_RCOMP_VOL

R105 R44 10K_4 CLK_MCH_OE#

20_4

20_4 R39 10K_4 PM_EXTTS#0

Quanta Computer Inc.

R103 C97 C98

M_RCOMP R32 10K_4 PM_EXTTS#1 PROJECT : BU1 Santa Rosa

1K_4 .01U_4 2.2U_6 Size Document Number Rev

GMCH DMI/VIDEO(2 of 7) 1A

Date: Monday, March 26, 2007 Sheet 6 of 33

5 4 3 2 1

5 4 3 2 1

NB(Memory controller) www.bufanxiu.com

[13] M_A_DQ[63:0] [13] M_B_DQ[63:0]

U21D U21E

D M_A_DQ0 AR43 BB19 M_B_DQ0 AP49 AY17 D

SA_DQ_0 SA_BS_0 M_A_BS#0 [12,13] SB_DQ_0 SB_BS_0 M_B_BS#0 [12,13]

M_A_DQ1 AW44 BK19 M_B_DQ1 AR51 BG18

SA_DQ_1 SA_BS_1 M_A_BS#1 [12,13] SB_DQ_1 SB_BS_1 M_B_BS#1 [12,13]

M_A_DQ2 BA45 BF29 M_B_DQ2 AW50 BG36

SA_DQ_2 SA_BS_2 M_A_BS#2 [12,13] SB_DQ_2 SB_BS_2 M_B_BS#2 [12,13]

M_A_DQ3 AY46 M_B_DQ3 AW51

SA_DQ_3 M_A_CAS# [12,13] SB_DQ_3 M_B_CAS# [12,13]

M_A_DQ4 AR41 BL17 M_B_DQ4 AN51 BE17

M_A_DQ5 SA_DQ_4 SA_CAS# M_B_DQ5 SB_DQ_4 SB_CAS#

AR45 SA_DQ_5 M_A_DM[7:0] [13] AN50 SB_DQ_5 M_B_DM[7:0] [13]

M_A_DQ6 AT42 AT45 M_A_DM0 M_B_DQ6 AV50 AR50 M_B_DM0

M_A_DQ7 SA_DQ_6 SA_DM_0 M_A_DM1 M_B_DQ7 SB_DQ_6 SB_DM_0 M_B_DM1

AW47 SA_DQ_7 SA_DM_1 BD44 AV49 SB_DQ_7 SB_DM_1 BD49

M_A_DQ8 BB45 BD42 M_A_DM2 M_B_DQ8 BA50 BK45 M_B_DM2

M_A_DQ9 SA_DQ_8 SA_DM_2 M_A_DM3 M_B_DQ9 SB_DQ_8 SB_DM_2 M_B_DM3

BF48 SA_DQ_9 SA_DM_3 AW38 BB50 SB_DQ_9 SB_DM_3 BL39

M_A_DQ10 BG47 AW13 M_A_DM4 M_B_DQ10 BA49 BH12 M_B_DM4

M_A_DQ11 SA_DQ_10 SA_DM_4 M_A_DM5 M_B_DQ11 SB_DQ_10 SB_DM_4 M_B_DM5

BJ45 SA_DQ_11 SA_DM_5 BG8 BE50 SB_DQ_11 SB_DM_5 BJ7

M_A_DQ12 BB47 AY5 M_A_DM6 M_B_DQ12 BA51 BF3 M_B_DM6

M_A_DQ13 SA_DQ_12 SA_DM_6 M_A_DM7 M_B_DQ13 SB_DQ_12 SB_DM_6 M_B_DM7

BG50 SA_DQ_13 SA_DM_7 AN6 AY49 SB_DQ_13 SB_DM_7 AW2

M_A_DQ14 BH49 M_B_DQ14 BF50

SA_DQ_14 M_A_DQS[7:0] [13] SB_DQ_14 M_B_DQS[7:0] [13]

M_A_DQ15 BE45 AT46 M_A_DQS0 M_B_DQ15 BF49 AT50 M_B_DQS0

A

SA_DQ_15 SA_DQS_0 SB_DQ_15 SB_DQS_0

B

M_A_DQ16 AW43 BE48 M_A_DQS1 M_B_DQ16 BJ50 BD50 M_B_DQS1

M_A_DQ17 SA_DQ_16 SA_DQS_1 M_A_DQS2 M_B_DQ17 SB_DQ_16 SB_DQS_1 M_B_DQS2

BE44 SA_DQ_17 SA_DQS_2 BB43 BJ44 SB_DQ_17 SB_DQS_2 BK46

M_A_DQ18 BG42 BC37 M_A_DQS3 M_B_DQ18 BJ43 BK39 M_B_DQS3

M_A_DQ19 SA_DQ_18 SA_DQS_3 M_A_DQS4 M_B_DQ19 SB_DQ_18 SB_DQS_3 M_B_DQS4

BE40 SA_DQ_19 SA_DQS_4 BB16 BL43 SB_DQ_19 SB_DQS_4 BJ12

M_A_DQ20 BF44 BH6 M_A_DQS5 M_B_DQ20 BK47 BL7 M_B_DQS5

MEMORY

SA_DQ_20 SA_DQS_5 SB_DQ_20 SB_DQS_5

MEMORY

M_A_DQ21 BH45 BB2 M_A_DQS6 M_B_DQ21 BK49 BE2 M_B_DQS6

M_A_DQ22 SA_DQ_21 SA_DQS_6 M_A_DQS7 M_B_DQ22 SB_DQ_21 SB_DQS_6 M_B_DQS7

BG40 SA_DQ_22 SA_DQS_7 AP3 M_A_DQS#[7:0] [13] BK43 SB_DQ_22 SB_DQS_7 AV2 M_B_DQS#[7:0] [13]

M_A_DQ23 BF40 AT47 M_A_DQS#0 M_B_DQ23 BK42 AU50 M_B_DQS#0

M_A_DQ24 SA_DQ_23 SA_DQS#_0 M_A_DQS#1 M_B_DQ24 SB_DQ_23 SB_DQS#_0 M_B_DQS#1

C

AR40 SA_DQ_24 SA_DQS#_1 BD47 BJ41 SB_DQ_24 SB_DQS#_1 BC50 C

M_A_DQ25 AW40 BC41 M_A_DQS#2 M_B_DQ25 BL41 BL45 M_B_DQS#2

M_A_DQ26 SA_DQ_25 SA_DQS#_2 M_A_DQS#3 M_B_DQ26 SB_DQ_25 SB_DQS#_2 M_B_DQS#3

AT39 SA_DQ_26 SA_DQS#_3 BA37 BJ37 SB_DQ_26 SB_DQS#_3 BK38

M_A_DQ27 AW36 BA16 M_A_DQS#4 M_B_DQ27 BJ36 BK12 M_B_DQS#4

M_A_DQ28 SA_DQ_27 SA_DQS#_4 M_A_DQS#5 M_B_DQ28 SB_DQ_27 SB_DQS#_4 M_B_DQS#5

AW41 SA_DQ_28 SA_DQS#_5 BH7 BK41 SB_DQ_28 SB_DQS#_5 BK7

M_A_DQ29 AY41 BC1 M_A_DQS#6 M_B_DQ29 BJ40 BF2 M_B_DQS#6

M_A_DQ30 SA_DQ_29 SA_DQS#_6 M_A_DQS#7 M_B_DQ30 SB_DQ_29 SB_DQS#_6 M_B_DQS#7

AV38 SA_DQ_30 SA_DQS#_7 AP2 BL35 SB_DQ_30 SB_DQS#_7 AV3

M_A_DQ31 AT38 M_B_DQ31 BK37

SA_DQ_31 M_A_A[13:0] [12,13] SB_DQ_31 M_B_A[13:0] [12,13]

M_A_DQ32 AV13 BJ19 M_A_A0 M_B_DQ32 BK13 BC18 M_B_A0

M_A_DQ33 SA_DQ_32 SA_MA_0 M_A_A1 M_B_DQ33 SB_DQ_32 SB_MA_0 M_B_A1

SYSTEM

AT13 SA_DQ_33 SA_MA_1 BD20 BE11 SB_DQ_33 SB_MA_1 BG28

SYSTEM

M_A_DQ34 AW11 BK27 M_A_A2 M_B_DQ34 BK11 BG25 M_B_A2

M_A_DQ35 SA_DQ_34 SA_MA_2 M_A_A3 M_B_DQ35 SB_DQ_34 SB_MA_2 M_B_A3

AV11 SA_DQ_35 SA_MA_3 BH28 BC11 SB_DQ_35 SB_MA_3 AW17

M_A_DQ36 AU15 BL24 M_A_A4 M_B_DQ36 BC13 BF25 M_B_A4

M_A_DQ37 SA_DQ_36 SA_MA_4 M_A_A5 M_B_DQ37 SB_DQ_36 SB_MA_4 M_B_A5

AT11 SA_DQ_37 SA_MA_5 BK28 BE12 SB_DQ_37 SB_MA_5 BE25

M_A_DQ38 BA13 BJ27 M_A_A6 M_B_DQ38 BC12 BA29 M_B_A6

M_A_DQ39 SA_DQ_38 SA_MA_6 M_A_A7 M_B_DQ39 SB_DQ_38 SB_MA_6 M_B_A7

BA11 SA_DQ_39 SA_MA_7 BJ25 BG12 SB_DQ_39 SB_MA_7 BC28

M_A_DQ40 BE10 BL28 M_A_A8 M_B_DQ40 BJ10 AY28 M_B_A8

M_A_DQ41 SA_DQ_40 SA_MA_8 M_A_A9 M_B_DQ41 SB_DQ_40 SB_MA_8 M_B_A9

BD10 SA_DQ_41 SA_MA_9 BA28 BL9 SB_DQ_41 SB_MA_9 BD37

M_A_DQ42 BD8 BC19 M_A_A10 M_B_DQ42 BK5 BG17 M_B_A10

M_A_DQ43 SA_DQ_42 SA_MA_10 M_A_A11 M_B_DQ43 SB_DQ_42 SB_MA_10 M_B_A11

AY9 SA_DQ_43 SA_MA_11 BE28 BL5 SB_DQ_43 SB_MA_11 BE37

M_A_DQ44 BG10 BG30 M_A_A12 M_B_DQ44 BK9 BA39 M_B_A12

M_A_DQ45 SA_DQ_44 SA_MA_12 M_A_A13 M_B_DQ45 SB_DQ_44 SB_MA_12 M_B_A13

AW9 SA_DQ_45 SA_MA_13 BJ16 BK10 SB_DQ_45 SB_MA_13 BG13

DDR

M_A_DQ46 BD7 M_B_DQ46 BJ8

SA_DQ_46 SB_DQ_46

DDR

M_A_DQ47 BB9 M_B_DQ47 BJ6 AV16

SA_DQ_47 SB_DQ_47 SB_RAS# M_B_RAS# [12,13]

M_A_DQ48 BB5 BE18 M_B_DQ48 BF4 AY18 TP_SB_RCVEN#

SA_DQ_48 SA_RAS# M_A_RAS# [12,13] SB_DQ_48 SB_RCVEN# T42

B M_A_DQ49 AY7 AY20 TP_SA_RCVEN# M_B_DQ49 BH5 B

SA_DQ_49 SA_RCVEN# T43 SB_DQ_49

M_A_DQ50 AT5 M_B_DQ50 BG1 BC17

SA_DQ_50 SB_DQ_50 SB_WE# M_B_WE# [12,13]

M_A_DQ51 AT7 BA19 M_B_DQ51 BC2

SA_DQ_51 SA_WE# M_A_WE# [12,13] SB_DQ_51

M_A_DQ52 AY6 M_B_DQ52 BK3

M_A_DQ53 SA_DQ_52 M_B_DQ53 SB_DQ_52

BB7 SA_DQ_53 BE4 SB_DQ_53

M_A_DQ54 AR5 M_B_DQ54 BD3

M_A_DQ55 SA_DQ_54 M_B_DQ55 SB_DQ_54

AR8 SA_DQ_55 BJ2 SB_DQ_55

M_A_DQ56 AR9 M_B_DQ56 BA3

M_A_DQ57 SA_DQ_56 M_B_DQ57 SB_DQ_56

AN3 SA_DQ_57 BB3 SB_DQ_57

M_A_DQ58 AM8 M_B_DQ58 AR1

M_A_DQ59 SA_DQ_58 M_B_DQ59 SB_DQ_58

AN10 SA_DQ_59 AT3 SB_DQ_59

M_A_DQ60 AT9 M_B_DQ60 AY2

M_A_DQ61 SA_DQ_60 M_B_DQ61 SB_DQ_60

AN9 SA_DQ_61 AY3 SB_DQ_61

M_A_DQ62 AM9 M_B_DQ62 AU2

M_A_DQ63 SA_DQ_62 M_B_DQ63 SB_DQ_62

AN11 SA_DQ_63 AT2 SB_DQ_63

CRESTLINE_1p0 CRESTLINE_1p0

A A

Quanta Computer Inc.

PROJECT : BU1 Santa Rosa

Size Document Number Rev

MCH DDR(3 of 7) 1A

Date: Monday, March 26, 2007 Sheet 7 of 33

5 4 3 2 1

5 4 3 2 1

www.bufanxiu.com

+3V_VCCSYNC +1.05V

NB(Power-1) R61 10_4 VCCGFPLLOW D4 1 2 PDZ5.6B

+1.05V

+1.05V ADD 10ohm

U21G THEY ONLY USE IN UMA (GM OR GML)

AT35 U21F

VCC_1

AT34 VCC_2 VCC_AXG_NCTF_1 T17

AH28 VCC_3 VCC_AXG_NCTF_2 T18 +1.05V AB33 VCC_NCTF_1

AC32 VCC_5 VCC_AXG_NCTF_3 T19 AB36 VCC_NCTF_2

D

AC31 VCC_4 VCC_AXG_NCTF_4 T21 AB37 VCC_NCTF_3 D

AK32 T22 + C423 C74 C59 C73 C63 AC33 T27

VCC_6 VCC_AXG_NCTF_5 VCC_NCTF_4 VSS_NCTF_1

AJ31 VCC_7 VCC_AXG_NCTF_6 T23 AC35 VCC_NCTF_5 VSS_NCTF_2 T37

AJ28 T25 330U_3528 22U_8 .22U_4 .22U_4 .1U_4 AC36 U24

VCC_8 VCC_AXG_NCTF_7 VCC_NCTF_6 VSS_NCTF_3

AH32 VCC_9 VCC_AXG_NCTF_8 U15 AD35 VCC_NCTF_7 VSS_NCTF_4 U28

VCC CORE

AH31 VCC_10 VCC_AXG_NCTF_9 U16 AD36 VCC_NCTF_8 VSS_NCTF_5 V31

AH29 VCC_11 VCC_AXG_NCTF_10 U17 AF33 VCC_NCTF_9 VSS_NCTF_6 V35

AF32 VCC_12 VCC_AXG_NCTF_11 U19 AF36 VCC_NCTF_10 VSS_NCTF_7 AA19

VCC_AXG_NCTF_12 U20 AH33 VCC_NCTF_11 VSS_NCTF_8 AB17

VSS NCTF

VCC_AXG_NCTF_13 U21 AH35 VCC_NCTF_12 VSS_NCTF_9 AB35

VCC_AXG_NCTF_14 U23 AH36 VCC_NCTF_13 VSS_NCTF_10 AD19

R69 0_4 +1.05V_VCC_GMCH_VCC13 R30 U26 AH37 AD37

VCC_13 VCC_AXG_NCTF_15 VCC_NCTF_14 VSS_NCTF_11

VCC_AXG_NCTF_16 V16 AJ33 VCC_NCTF_15 VSS_NCTF_12 AF17

VCC_AXG_NCTF_17 V17 AJ35 VCC_NCTF_16 VSS_NCTF_13 AF35

VCC_AXG_NCTF_18 V19 AK33 VCC_NCTF_17 VSS_NCTF_14 AK17

VCC_AXG_NCTF_19 V20 AK35 VCC_NCTF_18 VSS_NCTF_15 AM17

VCC_AXG_NCTF_20 V21 AK36 VCC_NCTF_19 VSS_NCTF_16 AM24

V23 +1.05V AK37 AP26

VCC_AXG_NCTF_21 VCC_NCTF_20 VSS_NCTF_17

VCC_AXG_NCTF_22 V24 AD33 VCC_NCTF_21 VSS_NCTF_18 AP28

+1.8VSUS +1.8VSUS Y15 AJ36 AR15

POWER VCC_AXG_NCTF_23 VCC_NCTF_22 VSS_NCTF_19

VCC NCTF

VCC_AXG_NCTF_24 Y16 AM35 VCC_NCTF_23 VSS_NCTF_20 AR19

VCC_AXG_NCTF_25 Y17 AL33 VCC_NCTF_24 VSS_NCTF_21 AR28

AU32 Y19 + C413 + C417 C81 C61 C57 C58 C76 C60 AL35

VCC_SM_1 VCC_AXG_NCTF_26 VCC_NCTF_25

AU33 VCC_SM_2 VCC_AXG_NCTF_27 Y20 AA33 VCC_NCTF_26

AU35 Y21 330U_3528 .47U_6 1U_6 10U_8 22U_8 .1U_4 .1U_4 AA35

VCC_SM_3 VCC_AXG_NCTF_28 330U_3528 VCC_NCTF_27

AV33 VCC_SM_4 VCC_AXG_NCTF_29 Y23 AA36 VCC_NCTF_28

C89 C102 C108 AW33 Y24 AP35

VCC_SM_5 VCC_AXG_NCTF_30 VCC_NCTF_29

AW35 VCC_SM_6 VCC_AXG_NCTF_31 Y26 AP36 VCC_NCTF_30

.1U_4 22U_8 22U_8 AY35 Y28 AR35

VCC_SM_7 VCC_AXG_NCTF_32 VCC_NCTF_31

BA32 VCC_SM_8 VCC_AXG_NCTF_33 Y29 AR36 VCC_NCTF_32

C BA33 VCC_SM_9 VCC_AXG_NCTF_34 AA16 Y32 VCC_NCTF_33

C

BA35 AA17 Y33

BB33

BC32

VCC_SM_10

VCC_SM_11

VCC_SM_12

VCC_AXG_NCTF_35

VCC_AXG_NCTF_36

VCC_AXG_NCTF_37

AB16

AB19

Y35

Y36

VCC_NCTF_34

VCC_NCTF_35

VCC_NCTF_36

POWER

BC33 VCC_SM_13 VCC_AXG_NCTF_38 AC16 Y37 VCC_NCTF_37 VSS_SCB1 A3

BC35 VCC_SM_14 VCC SM VCC_AXG_NCTF_39 AC17 T30 VCC_NCTF_38 VSS_SCB2 B2

VSS SCB

BD32 VCC_SM_15 VCC_AXG_NCTF_40 AC19 T34 VCC_NCTF_39 VSS_SCB3 C1

BD35 VCC_SM_16 VCC_AXG_NCTF_41 AD15 T35 VCC_NCTF_40 VSS_SCB4 BL1

BE32 VCC_SM_17 VCC_AXG_NCTF_42 AD16 U29 VCC_NCTF_41 VSS_SCB5 BL51

BE33 VCC_SM_18 VCC_AXG_NCTF_43 AD17 U31 VCC_NCTF_42 VSS_SCB6 A51

BE35

BF33

VCC_SM_19 VCC GFX NCTF VCC_AXG_NCTF_44 AF16

AF19

U32

U33

VCC_NCTF_43

VCC_SM_20 VCC_AXG_NCTF_45 VCC_NCTF_44

BF34 VCC_SM_21 VCC_AXG_NCTF_46 AH15 U35 VCC_NCTF_45

BG32 VCC_SM_22 VCC_AXG_NCTF_47 AH16 U36 VCC_NCTF_46

BG33 AH17 V32 +1.05V

VCC_SM_23 VCC_AXG_NCTF_48 VCC_NCTF_47

BG35 VCC_SM_24 VCC_AXG_NCTF_49 AH19 V33 VCC_NCTF_48

BH32 AJ16 V36 R89

VCC_SM_25 VCC_AXG_NCTF_50 VCC_NCTF_49

BH34 VCC_SM_26 VCC_AXG_NCTF_51 AJ17 V37 VCC_NCTF_50

BH35 VCC_SM_27 VCC_AXG_NCTF_52 AJ19

BJ32 AK16 AT33 0_6

VCC_SM_28 VCC_AXG_NCTF_53 VCC_AXM_1

BJ33 VCC_SM_29 VCC_AXG_NCTF_54 AK19 VCC_AXM_2 AT31

+1.05V

VCC AXM

BJ34 VCC_SM_30 VCC_AXG_NCTF_55 AL16 VCC_AXM_3 AK29

BK32 VCC_SM_31 VCC_AXG_NCTF_56 AL17 VCC_AXM_4 AK24

BK33 VCC_SM_32 VCC_AXG_NCTF_57 AL19 VCC_AXM_5 AK23

BK34 VCC_SM_33 VCC_AXG_NCTF_58 AL20 AL24 VCC_AXM_NCTF_1 VCC_AXM_6 AJ26

BK35 VCC_SM_34 VCC_AXG_NCTF_59 AL21 AL26 VCC_AXM_NCTF_2 VCC_AXM_7 AJ23

BL33 VCC_SM_35 VCC_AXG_NCTF_60 AL23 AL28 VCC_AXM_NCTF_3

AU30 AM15 C66 C70 C71 C62 C69 C64 AM26

VCC_SM_36 VCC_AXG_NCTF_61 VCC_AXM_NCTF_4

VCC AXM NCTF

VCC_AXG_NCTF_62 AM16 AM28 VCC_AXM_NCTF_5

+1.05V AM19 22U_8 .22U_4 .22U_4 .1U_4 .1U_4 .1U_4 AM29

B VCC_AXG_NCTF_63 VCC_AXM_NCTF_6 B

VCC_AXG_NCTF_64 AM20 AM31 VCC_AXM_NCTF_7

VCC_AXG_NCTF_65 AM21 AM32 VCC_AXM_NCTF_8

R20 VCC_AXG_1 VCC_AXG_NCTF_66 AM23 AM33 VCC_AXM_NCTF_9

T14 VCC_AXG_2 VCC_AXG_NCTF_67 AP15 AP29 VCC_AXM_NCTF_10

W13 VCC_AXG_3 VCC_AXG_NCTF_68 AP16 AP31 VCC_AXM_NCTF_11

W14 VCC_AXG_4 VCC_AXG_NCTF_69 AP17 AP32 VCC_AXM_NCTF_12

Y12 VCC_AXG_5 VCC_AXG_NCTF_70 AP19 AP33 VCC_AXM_NCTF_13

AA20 VCC_AXG_6 VCC_AXG_NCTF_71 AP20 AL29 VCC_AXM_NCTF_14

AA23 VCC_AXG_7 VCC_AXG_NCTF_72 AP21 AL31 VCC_AXM_NCTF_15

AA26 VCC_AXG_8 VCC_AXG_NCTF_73 AP23 AL32 VCC_AXM_NCTF_16

AA28 VCC_AXG_9 VCC_AXG_NCTF_74 AP24 AR31 VCC_AXM_NCTF_17

AB21 VCC_AXG_10 VCC_AXG_NCTF_75 AR20 AR32 VCC_AXM_NCTF_18

AB24 VCC_AXG_11 VCC_AXG_NCTF_76 AR21 AR33 VCC_AXM_NCTF_19

AB29 VCC_AXG_12 VCC_AXG_NCTF_77 AR23

AC20 VCC_AXG_13 VCC_AXG_NCTF_78 AR24

VCC GFX

AC21 VCC_AXG_14 VCC_AXG_NCTF_79 AR26

AC23 VCC_AXG_15 VCC_AXG_NCTF_80 V26

AC24 V28 CRESTLINE_1p0

VCC_AXG_16 VCC_AXG_NCTF_81

AC26 VCC_AXG_17 VCC_AXG_NCTF_82 V29

AC28 VCC_AXG_18 VCC_AXG_NCTF_83 Y31

AC29 VCC_AXG_19

AD20 VCC_AXG_20

AD23 VCC_AXG_21

AD24 AW45 VCCSM_LF1

VCC_AXG_22 VCC_SM_LF1 VCCSM_LF2

AD28 VCC_AXG_23 VCC_SM_LF2 BC39

VCCSM_LF3

VCC SM LF

AF21 VCC_AXG_24 VCC_SM_LF3 BE39

AF26 BD17 VCCSM_LF4

VCC_AXG_25 VCC_SM_LF4 VCCSM_LF5

AA31 VCC_AXG_26 VCC_SM_LF5 BD4

AH20 AW8 VCCSM_LF6

VCC_AXG_27 VCC_SM_LF6 VCCSM_LF7

A AH21 VCC_AXG_28 VCC_SM_LF7 AT6 A

AH23 VCC_AXG_29

AH24 C82 C84 C90 C88 C92 C86 C85

VCC_AXG_30

AH26 VCC_AXG_31

AD31 .1U_4 .1U_4 .22U_4 .22U_4 .47U_6 1U_6 1U_6

VCC_AXG_32

AJ20 VCC_AXG_33

AN14 VCC_AXG_34 Quanta Computer Inc.

PROJECT : BU1 Santa Rosa

Size Document Number Rev

CRESTLINE_1p0

GMCH Power-1(4 of 7) 1A

Date: Thursday, February 01, 2007 Sheet 8 of 33

5 4 3 2 1

5 4 3 2 1

NB(Power-2)

+3V R33 0_6

+3V_VCCSYNC

www.bufanxiu.com

CRT/TV Disable/Enable guideline

LVDS Disable/Enable guideline

External VGA with EV@part,Internal VGA with IV@ part

If SDVO Disable If SDVO enable If SDVO enable

'IND CHIP 10UH(20%,100MA,LB2012T100MR)' C45 Ball Enable Disable Ball Enable Disable Signal LVDS Disable LVDS Disable LVDS enable

<FAE>

INT VGA disable .1U_4 VCCA_CRT 3.3V GND VCCA_C_TVO 3.3V GND VCCD_LVDS GND 1.8V 1.8V

+1.25V L1 10UH_8

VCCSYNC connect to GND VCCD_CRT 1.5V GND VCCD_TVO 1.5V 1.5V VCCA_LVDS GND GND 1.8V

+ C451 C39 VCCDQ_CRT 1.5V GND VCCABG_DAC 3.3V GND VCCTX_LVDS GND GND 1.8V

+3V L29 PBY160808T-301Y-N_6

470U_7343 .1U_4 VCCA_A_TVO 3.3V GND VSSABG_DAC GND GND

C446 C430 C448 R421 EXTERNAL INTERNAL

D VCCA_B_TVO 3.3V GND VCC_SYNC 3.3V GND D

*22U_8 .1U_4 22N_4 *0_4

+1.05V

U21H

+1.05V

J32 VCCSYNC VTT_1 U13

+1.25V L2 10UH_8 +3V_TV_DAC R426 0_6 U12

+3V_VCCA_CRT_DAC VTT_2

A33 VCCA_CRT_DAC_1 VTT_3 U11

C429 C438 R425 B33 U9 C53 C51 C52 C56 + C421

+ C452 C44 VCCA_CRT_DAC_2 VTT_4

VTT_5 U8

.1U_4 22N_4 *0_4 4.7U_8 4.7U_8 2.2U_8 .47U_6 330U_3528

CRT

VTT_6 U7

470U_7343 .1U_4 +3V_VCCA_DAC_BG A30 U5

VCCA_DAC_BG VTT_7

VTT_8 U3

B32 U2 +1.25V_AXD

VSSA_DAC_BG VTT_9

VTT_10 U1

VTT_11 T13

+1.25V_VCCA_DPLLA R93 0_6

VTT

B49 VCCA_DPLLA VTT_12 T11 +1.25V

VTT_13 T10

+1.25V_VCCA_DPLLB H49 T9

'EMI FILTER BKP1608HS181-T(180,1.5A)' VCCA_DPLLB VTT_14 C83 C77

VTT_15 T7

L23 PBY160808T-301Y-N_6 +1.25VM_VCCA_HPLL

PLL

+1.25V AL2 VCCA_HPLL VTT_16 T6

T5 1U_6 *22U_8

C410 C72 +1.25VM_VCCA_MPLL VTT_17

AM2 VCCA_MPLL VTT_18 T3

VTT_19 T2

22U_8 .1U_4 R3

+1.8VSUS_VCC_TX_LVDS VTT_20 R424 0_6

A LVDS

A41 VCCA_LVDS VTT_21 R2 +1.25V

VTT_22 R1

B41 VSSA_LVDS

L24 PBY160808T-301Y-N_6 C435 C443 C442

VCC_AXD_1 AT23

1000P_4 AU28 1U_6 10U_8

C75 VCC_AXD_2

K50 VCCA_PEG_BG VCC_AXD_3 AU24

C R403 R53 0_8 +3V_VCCA_PEG_BG C

AXD

+3V VCC_AXD_4 AT29

0.5_6 .1U_4 K49 AT25

C48 VSSA_PEG_BG VCC_AXD_5

A PEG

VCC_AXD_6 AT30

C409 22U_8 V1.25M_MPLL_RC R91 0_6 +1.25V

.1U_4 +1.25V_VCCD_PEG_PLL U51 AR29

VCCA_PEG_PLL VCC_AXD_NCTF C68

+1.25V R118 0_6 +1.25VM_VCCA_SM AW18 B23 +1.25V_VCC_AXF .1U_4

VCCA_SM_1 VCC_AXF_1

AV19 B21

C399 C103 C79 C110 C80 VCCA_SM_2

POWER VCC_AXF_2

AXF

AU19 VCCA_SM_3 VCC_AXF_3 A21

+ AU18 L5 1UH_8 +1.8VSUS

100U_3528 *22U_8 4.7U_6 22U_8 1U_6 VCCA_SM_4

AU17 VCCA_SM_5 VCC_DMI AJ50 +1.25V_VCC_DMI

C94 C96

R109 1_6 +V1.8_SMCK_RC C119 22U_8

A SM

AT22 VCCA_SM_7

AT21 VCCA_SM_8 VCC_SM_CK_1 BK24 +1.8VSUS_VCC_SM_CK .1U_4 22U_8

SM CK

AT19 VCCA_SM_9 VCC_SM_CK_2 BK23

AT18 VCCA_SM_10 VCC_SM_CK_3 BJ24

+1.25V R110 0_6 AT17 BJ23

VCCA_SM_11 VCC_SM_CK_4

AR17 VCCA_SM_NCTF_1

C105 C106 C107 C87 AR16 VCCA_SM_NCTF_2

+3V_TV_DAC +1.8VSUS

L28 *1U_6 *1U_6 22U_8 .1U_4 A43 +1.8VSUS_VCC_TX_LVDS L27 1UH_8

PBY160808T-301Y-N_6 +1.25VM_VCCA_SM_CK VCC_TX_LVDS

A CK

BC29 VCCA_SM_CK_1

+3V BB29 VCCA_SM_CK_2

C40 +3V_VCC_HV C434 + C450

C433 C447 R413 VCC_HV_1

C25 VCCA_TVA_DAC_1 VCC_HV_2 B40

1000P_4 220U_7343

HV

B25 VCCA_TVA_DAC_2

.1U_4 22N_4 *0_4 C27 VCCA_TVB_DAC_1

B27 VCCA_TVB_DAC_2 VCC_PEG_1 AD51

TV

B28 VCCA_TVC_DAC_1 VCC_PEG_2 W50

+VCC_PEG

PEG

A28 VCCA_TVC_DAC_2 VCC_PEG_3 W51

R60 *0_4 V49

B VCC_PEG_4 B

VCC_PEG_5 V50

R31 0_6 +1.5V_VCCD_CRT

D TV/CRT

M32 VCCD_CRT

+1.5V_VCCD_TVDAC L29

C441 C444 R427 VCCD_TVDAC

VCC_RXR_DMI_1 AH50

+1.5V_VCCD_QDAC

DMI

N28 VCCD_QDAC VCC_RXR_DMI_2 AH51

.1U_4 22N_4 *0_4

+1.25V R92 0_6 +1.25VM_MCH_VCCD_HPLL AN2 VCCD_HPLL L22 91nH

VTTLF1 A7 +1.05V

C78 +1.25V_VCCD_PEG_PLL

VTTLF

U48 VCCD_PEG_PLL VTTLF2 F2

VTTLF3 AH1

.1U_4 C54 J41 C405 + C400

VCCD_LVDS_1 LVDS C65 C42 C437

H42 VCCD_LVDS_2

C445 C449 C439 C431 R423 .1U_4 10U_8

.47U_4 .47U_4 .47U_4 330U_3528

22U_8 10U_8 .1U_4 22N_4 *0_4 +1.25V L3 PBY160808T-301Y-N_6

CRESTLINE_1p0 <FAE>

VCC_RXR_DMI and VCC_PEG

R43 C55 connect to+1.05V

1_8 .1U_4

+V1.25S_PEGPLL_FB

C40

10U_8

+1.5V R30 0_6

C47 C38

.1U_4 22N_4 +1.05V D26 2 1 PDZ5.6B +1.05V_SD

A A

+3V_VCC_HV

+1.8VSUS R420 0_6 +1.8V_VCCD_LVDS R436

10_4

R29 100/F_6 C46 C440

+3V R433 0_4

1U_6 *10U_8

C50 C37 C49

C453

Quanta Computer Inc.

.1U_4 22N_4 1U_6 <CRB> PROJECT : BU1 Santa Rosa

+1.25V AND +1.25M shall be .1U_4

Size Document Number Rev

+1.5V for Calero Interposer

GMCH Power-2(5 of 7) 1A

Date: Tuesday, February 06, 2007 Sheet 9 of 33

5 4 3 2 1

5 4 3 2 1

NB(Power-3)

U21I

www.bufanxiu.com

U21J

A13 VSS_1 VSS_100 AW24 C46 VSS_199 VSS_287 W11

A15 VSS_2 VSS_101 AW29 C50 VSS_200 VSS_288 W39

A17 VSS_3 VSS_102 AW32 C7 VSS_201 VSS_289 W43

A24 VSS_4 VSS_103 AW5 D13 VSS_202 VSS_290 W47

AA21 VSS_5 VSS_104 AW7 D24 VSS_203 VSS_291 W5

AA24 VSS_6 VSS_105 AY10 D3 VSS_204 VSS_292 W7

AA29 VSS_7 VSS_106 AY24 D32 VSS_205 VSS_293 Y13

AB20 VSS_8 VSS_107 AY37 D39 VSS_206 VSS_294 Y2

D AB23 AY42 D45 Y41 D

VSS_9 VSS_108 VSS_207 VSS_295

AB26 VSS_10 VSS_109 AY43 D49 VSS_208 VSS_296 Y45

AB28 VSS_11 VSS_110 AY45 E10 VSS_209 VSS_297 Y49

AB31 VSS_12 VSS_111 AY47 E16 VSS_210 VSS_298 Y5

AC10 VSS_13 VSS_112 AY50 E24 VSS_211 VSS_299 Y50

AC13 VSS_14 VSS_113 B10 E28 VSS_212 VSS_300 Y11

AC3 VSS_15 VSS_114 B20 E32 VSS_213 VSS_301 P29

AC39 B24 E47 T29 VSS_GMCH_T29 R35 0_4

VSS_16 VSS_115 VSS_214 VSS_302 VSS_GMCH_T31 R27 0_4

AC43 VSS_17 VSS_116 B29 F19 VSS_215 VSS_303 T31

AC47 B30 F36 T33 VSS_GMCH_T33 R28 0_4

VSS_18 VSS_117 VSS_216 VSS_304 VSS_GMCH_R28 R63 0_4

AD1 VSS_19 VSS_118 B35 F4 VSS_217 VSS_305 R28

AD21 VSS_20 VSS_119 B38 F40 VSS_218

AD26 VSS_21 VSS_120 B43 F50 VSS_219

AD29 VSS_22 VSS_121 B46 G1 VSS_220

AD3 VSS_23 VSS_122 B5 G13 VSS_221 VSS_306 AA32

AD41 VSS_24 VSS_123 B8 G16 VSS_222 VSS_307 AB32

AD45 VSS_25 VSS_124 BA1 G19 VSS_223 VSS_308 AD32

AD49 VSS_26 VSS_125 BA17 G24 VSS_224 VSS_309 AF28

AD5 VSS_27 VSS_126 BA18 G28 VSS_225 VSS_310 AF29

AD50 VSS_28 VSS_127 BA2 G29 VSS_226 VSS_311 AT27

AD8 VSS_29 VSS_128 BA24 G33 VSS_227 VSS_312 AV25

AE10 VSS_30 VSS_129 BB12 G42 VSS_228 VSS_313 H50

AE14 VSS_31 VSS_130 BB25 G45 VSS_229

AE6 VSS_32 VSS_131 BB40 G48 VSS_230

AF20 BB44 G8

AF23

AF24

VSS_33

VSS_34

VSS_35

VSS VSS_132

VSS_133

VSS_134

BB49

BB8

H24

H28

VSS_231

VSS_232

VSS_233

AF31 VSS_36 VSS_135 BC16 H4 VSS_234

C AG2 VSS_37 VSS_136 BC24 H45 VSS_235 C

AG38 VSS_38 VSS_137 BC25 J11 VSS_236

AG43 VSS_39 VSS_138 BC36 J16 VSS_237

AG47 VSS_40 VSS_139 BC40 J2 VSS_238

AG50 VSS_41 VSS_140 BC51 J24 VSS_239

AH3 VSS_42 VSS_141 BD13 J28 VSS_240

AH40 BD2 J33

AH41

AH7

VSS_43

VSS_44

VSS_45

VSS_142

VSS_143

VSS_144

BD28

BD45

J35

J39

VSS_241

VSS_242

VSS_243

VSS

AH9 VSS_46 VSS_145 BD48

AJ11 VSS_47 VSS_146 BD5 K12 VSS_245

AJ13 VSS_48 VSS_147 BE1 K47 VSS_246

AJ21 VSS_49 VSS_148 BE19 K8 VSS_247

AJ24 VSS_50 VSS_149 BE23 L1 VSS_248

AJ29 VSS_51 VSS_150 BE30 L17 VSS_249

AJ32 VSS_52 VSS_151 BE42 L20 VSS_250

AJ43 VSS_53 VSS_152 BE51 L24 VSS_251

AJ45 VSS_54 VSS_153 BE8 L28 VSS_252

AJ49 VSS_55 VSS_154 BF12 L3 VSS_253

AK20 VSS_56 VSS_155 BF16 L33 VSS_254

AK21 VSS_57 VSS_156 BF36 L49 VSS_255

AK26 VSS_58 VSS_157 BG19 M28 VSS_256

AK28 VSS_59 VSS_158 BG2 M42 VSS_257

AK31 VSS_60 VSS_159 BG24 M46 VSS_258

AK51 VSS_61 VSS_160 BG29 M49 VSS_259

AL1 VSS_62 VSS_161 BG39 M5 VSS_260

AM11 VSS_63 VSS_162 BG48 M50 VSS_261

AM13 VSS_64 VSS_163 BG5 M9 VSS_262

B AM3 VSS_65 VSS_164 BG51 N11 VSS_263 B

AM4 VSS_66 VSS_165 BH17 N14 VSS_264

AM41 VSS_67 VSS_166 BH30 N17 VSS_265

AM45 VSS_68 VSS_167 BH44 N29 VSS_266

AN1 VSS_69 VSS_168 BH46 N32 VSS_267

AN38 VSS_70 VSS_169 BH8 N36 VSS_268

AN39 VSS_71 VSS_170 BJ11 N39 VSS_269

AN43 VSS_72 VSS_171 BJ13 N44 VSS_270

AN5 VSS_73 VSS_172 BJ38 N49 VSS_271

AN7 VSS_74 VSS_173 BJ4 N7 VSS_272

AP4 VSS_75 VSS_174 BJ42 P19 VSS_273

AP48 VSS_76 VSS_175 BJ46 P2 VSS_274

AP50 VSS_77 VSS_176 BK15 P23 VSS_275

AR11 VSS_78 VSS_177 BK17 P3 VSS_276

AR2 VSS_79 VSS_178 BK25 P50 VSS_277

AR39 VSS_80 VSS_179 BK29 R49 VSS_278

AR44 VSS_81 VSS_180 BK36 T39 VSS_279

AR47 VSS_82 VSS_181 BK40 T43 VSS_280

AR7 VSS_83 VSS_182 BK44 T47 VSS_281

AT10 VSS_84 VSS_183 BK6 U41 VSS_282

AT14 VSS_85 VSS_184 BK8 U45 VSS_283

AT41 VSS_86 VSS_185 BL11 U50 VSS_284

AT49 VSS_87 VSS_186 BL13 V2 VSS_285

AU1 VSS_88 VSS_187 BL19 V3 VSS_286

AU23 VSS_89 VSS_188 BL22

AU29 VSS_90 VSS_189 BL37

AU3 BL47 CRESTLINE_1p0

VSS_91 VSS_190

AU36 VSS_92 VSS_191 C12

AU49 VSS_93 VSS_192 C16

A A

AU51 VSS_94 VSS_193 C19

AV39 VSS_95 VSS_194 C28

AV48 VSS_96 VSS_195 C29

AW1 VSS_97 VSS_196 C33

AW12 VSS_98 VSS_197 C36

AW16 C41

VSS_99 VSS_198 Quanta Computer Inc.

CRESTLINE_1p0

PROJECT : BU1 Santa Rosa

Size Document Number Rev

GMCH Power-3(6 of 7) 1A

Date: Thursday, February 01, 2007 Sheet 10 of 33

5 4 3 2 1

5 4 3 2 1

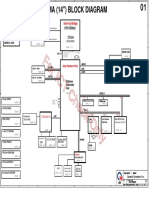

Strap table

All strap are sampled with respect to the leading edge of the GMCH Power OK(PWROK) Signal

CFG[17:3] Have internal Pull-up

www.bufanxiu.com

CFG[18:19] Have internal Pull-down

Any CFG signal strapping option not list below should be left NC Pin

Pin Name Strap description Configuration

CFG[2:0] FSB Frequency Select 010 = FSB 800MHz

D 011 = FSB 667MHz D

CFG[4:3] Reserved

CFG5 DMI X2 Select 0 = DMI X2

1 = DMI X4(Default)

CFG6 Reserved

CFG7 CPU Strap 0 = Reserved

1 = Mobile CPU(Default)

CFG8 Low power PCI Express 0 = Normal mode

1 = Low Power mode

CFG9 PCI Express Graphics Lane Reversal 0 = Reverse Lanes

1 = Normal operation(Default)

CFG[11:10] Reserved

C C

CFG[13:12] XOR/ALLZ 00 = Reserved

01 = XOR Mode Enable

10 = All-Z Mode Enabled

11 = Normal operation(Default)

CFG[15:14] Reserved

CFG16 FSB Dynamic ODT 0 = Dynamic ODT disable

1 = Dynamic ODT Enable(Default)

CFG[18:17] Reserved

SDVO_CTRLDATA SDVO Present 0 = No SDVO Card present(Default)

1 = SDVO Card Present

CFG19 DMI Lane Reversal 0 = Normal operation(Default)

1 = Reverse Lanes

CFG20 SDVO/PCIe concurrent 0 = Only SDVO or PCIE x1 is operation(Default)

1 = SDVO and PCIE x1 are operating simultaneously via the PEG port

B B

DMI X2 Select DMI Lane Reversal XOR /ALLz /Clock Un-gating PCI Express Graphics SDVO Present

MCH_CFG_5 Low = DMIX2 MCH_CFG_19 Low = Normal operation(Default) MCH_CFG_12MCH_CFG_13 Configuration MCH_CFG_9 Low = Reverse Lane Strap define at External

High = IDMIX4(Default) High = Reverse Lane High = Normal operation(Default)

DVI control page

0 0 Clock gating disable

+3V

[6] MCH_CFG_5 [6] MCH_CFG_9

0 1 XOR Mode Enable

1 0 ALL-z Mode Enable

R51 R47

R36

*4.02K_4 1 1 Normal operation(Default) *4.02K_4

*4.02K_4

[6] MCH_CFG_19

FSB Dynamic ODT SDVO/PCIE Concurrent operation

Low = Only SDVO or PCIE X1 is

MCH_CFG_16 Low = ODT Disable MCH_CFG_20 operational(Default)

High = ODT Enable(Default) High = SDVO andPCIE X1 are operating

simultaneously via the PEG port

[6] MCH_CFG_12

A [6] MCH_CFG_13 A

[6] MCH_CFG_16 +3V

R48 R54

R58

*4.02K_4 *4.02K_4

*4.02K_4 R430

*4.02K_4

Quanta Computer Inc.

PROJECT : BU1 Santa Rosa

Size Document Number Rev

[6] MCH_CFG_20 GMCH Strap(7 of 7) 1A

Date: Monday, March 26, 2007 Sheet 11 of 33

5 4 3 2 1

1 2 3 4 5 6 7 8

DDR2 Dual channel A/B PU www.bufanxiu.com

A A

M_A_A[13..0]

M_A_A[13..0] [7,13]

M_B_A[13..0]

M_B_A[13..0] [7,13]

DDRII A CHANNEL DDRII B CHANNEL

SMDDR_VTERM SMDDR_VTERM

C176 C145 C143 C148 C195 C146 C230 C201 C228 C227 C142 C173 C200 C174 C172 C177 C175 C231 C196 C197 C199 C171 C144 C226 C147 C225

.1U_4 .1U_4 .1U_4 .1U_4 .1U_4 .1U_4 .1U_4 .1U_4 .1U_4 .1U_4 .1U_4 .1U_4 .1U_4 .1U_4 .1U_4 .1U_4 .1U_4 .1U_4 .1U_4 .1U_4 .1U_4 .1U_4 .1U_4 .1U_4 .1U_4 .1U_4

Place one cap close to every 2 pull-up resistor terminated to SMDDR_VTERM

B B

M_A_A3 RP16 1 2 56X2 SMDDR_VTERM

M_A_A1 3 4

M_A_A9 RP18 1 2 56X2 M_A_A7 RP22 1 2 56X2 SMDDR_VTERM

M_A_A5 3 4 M_A_A6 3 4

M_A_A2 RP21 1 2 56X2 RP32 1 2 56X2

[6,13] M_CKE3

M_A_A4 3 4 [7,13] M_B_BS#2 3 4

M_A_A11 RP23 1 2 56X2 RP14 1 2 56X2

[6,13] M_ODT1

[6,13] M_CKE1 3 4 [6,13] M_CS#1 3 4

RP19 1 2 56X2

[6,13] M_CKE0

M_A_A8 3 4 [6,13] M_ODT3 RP33 1 2 56X2

[7,13] M_B_BS#0 3 4

M_A_A12 RP20 1 2 56X2

3 4 M_A_A10 RP17 1 2 56X2

[7,13] M_A_BS#2

[7,13] M_A_BS#0 3 4

RP25 1 2 56X2

[7,13] M_A_BS#1

M_A_A0 3 4 RP15 1 2 56X2

[7,13] M_A_CAS#

[7,13] M_A_WE# 3 4

C C

RP26 1 2 56X2

[6,13] M_CS#0

[7,13] M_A_RAS# 3 4

M_B_A10 RP30 1 2 56X2 SMDDR_VTERM

[7,13] M_B_WE# 3 4 [7,13] M_B_CAS# RP29 1 2 56X2

[6,13] M_CS#3 3 4

M_B_A3 RP31 1 2 56X2

M_B_A1 3 4 M_B_A6 RP39 1 2 56X2

[6,13] M_CKE4 3 4

RP38 1 2 56X2

[7,13] M_B_BS#1

M_B_A0 3 4 [6,13] M_ODT2 RP37 1 2 56X2

[7,13] M_B_RAS# 3 4

M_B_A7 RP35 1 2 56X2

M_B_A11 3 4 [6,13] M_ODT0 RP24 1 2 56X2

M_A_A13 3 4

M_B_A8 RP27 1 2 56X2

M_B_A5 3 4 M_B_A13 RP36 1 2 56X2

[6,13] M_CS#2 3 4

M_B_A2 RP34 1 2 56X2

M_B_A4 3 4

M_B_A9 RP28 1 2 56X2

D M_B_A12 3 4 D

INTEL FAE (08/17)

ADD MA14 FOR DUAL LAYERS RAM

R199 56_4 SMDDR_VTERM

Quanta Computer Inc.

[6,13] M_A_A14

R219 56_4

[6,13] M_B_A14 PROJECT : BU1 Santa Rosa

Size Document Number Rev

DDR RES. ARRAY 1A

Date: Monday, March 26, 2007 Sheet 12 of 33

1 2 3 4 5 6 7 8

1 2 3 4 5 6 7 8

DDR2 Dual channel A/B CONN

www.bufanxiu.com

SMDDR_VREF_DIMM

M_A_DM[0..7] [7] M_B_DM[0..7] [7]

SMDDR_VREF_DIMM

M_A_DQ[0..63] [7] M_B_DQ[0..63] [7]

+1.8VSUS

M_A_DQS[0..7] [7] M_B_DQS[0..7] [7]

+1.8VSUS +1.8VSUS +1.8VSUS +1.8VSUS

M_A_DQS#[0..7] [7] M_B_DQS#[0..7] [7]

CN25

M_A_A[0..13] [7,12] M_B_A[0..13] [7,12]

CN30 1 2

VREF VSS46 M_B_DQ4

1 VREF VSS46 2 3 VSS47 DQ4 4

3 4 M_A_DQ4 M_B_DQ0 5 6 M_B_DQ1

M_A_DQ6 VSS47 DQ4 M_A_DQ0 M_B_DQ5 DQ0 DQ5 + C370 C376 C379 C367 C368 C380

5 DQ0 DQ5 6 7 DQ1 VSS15 8

M_A_DQ5 7 8 9 10 M_B_DM0

DQ1 VSS15 M_A_DM0 M_B_DQS#0 VSS37 DM0 330U_3528 2.2U_6 2.2U_6 2.2U_6 2.2U_6 2.2U_6

9 VSS37 DM0 10 11 DQS#0 VSS5 12

M_A_DQS#0 11 12 M_B_DQS0 13 14 M_B_DQ2

M_A_DQS0 DQS#0 VSS5 M_A_DQ7 DQS0 DQ6 M_B_DQ6

13 DQS0 DQ6 14 15 VSS48 DQ7 16

15 16 M_A_DQ1 M_B_DQ7 17 18

M_A_DQ2 VSS48 DQ7 M_B_DQ3 DQ2 VSS16 M_B_DQ12

17 DQ2 VSS16 18 19 DQ3 DQ12 20

A M_A_DQ3 M_A_DQ13 M_B_DQ13 A

19 DQ3 DQ12 20 21 VSS38 DQ13 22

21 22 M_A_DQ12 M_B_DQ9 23 24

M_A_DQ9 VSS38 DQ13 M_B_DQ8 DQ8 VSS17 M_B_DM1

23 DQ8 VSS17 24 25 DQ9 DM1 26

M_A_DQ8 25 26 M_A_DM1 27 28

DQ9 DM1 M_B_DQS#1 VSS49 VSS53 +1.8VSUS SMDDR_VREF_DIMM +3V

27 VSS49 VSS53 28 29 DQS#1 CK0 30 M_CLK_DDR3 [6]

M_A_DQS#1 29 30 M_B_DQS1 31 32

DQS#1 CK0 M_CLK_DDR0 [6] DQS1 CK0# M_CLK_DDR#3 [6]

M_A_DQS1 31 32 33 34

DQS1 CK0# M_CLK_DDR#0 [6] VSS39 VSS41

33 34 M_B_DQ11 35 36 M_B_DQ14

M_A_DQ14 VSS39 VSS41 M_A_DQ10 M_B_DQ10 DQ10 DQ14 M_B_DQ15 C185 C183 C369 C182 C202 C198 C141 C150

35 DQ10 DQ14 36 37 DQ11 DQ15 38

M_A_DQ11 37 38 M_A_DQ15 39 40

DQ11 DQ15 VSS50 VSS54 .1U_4 .1U_4 .1U_4 .1U_4 .1U_4 2.2U_6 2.2U_6 .1U_4

39 VSS50 VSS54 40

41 VSS18 VSS20 42

41 42 M_B_DQ20 43 44 M_B_DQ16

PC4800 DDR2 SDRAM

M_A_DQ17 VSS18 VSS20 M_A_DQ16 M_B_DQ17 DQ16 DQ20 M_B_DQ21

43 DQ16 DQ20 44 45 DQ17 DQ21 46

M_A_DQ20 45 46 M_A_DQ21 47 48

DQ17 DQ21 M_B_DQS#2 VSS1 VSS6

PC4800 DDR2 SDRAM

47 VSS1 VSS6 48 49 DQS#2 NC3 50 PM_EXTTS#1 [6]

M_A_DQS#2 49 DQS#2 NC3 50 PM_EXTTS#0 [6] M_B_DQS2 51 DQS2 DM2 52 M_B_DM2 Close to DIMM0

M_A_DQS2 51 52 M_A_DM2 53 54

SO-DIMM (200P)

DQS2 DM2 M_B_DQ22 VSS19 VSS21 M_B_DQ18

53 VSS19 VSS21 54 55 DQ18 DQ22 56

M_A_DQ23 55 56 M_A_DQ18 M_B_DQ23 57 58 M_B_DQ19

M_A_DQ19 DQ18 DQ22 M_A_DQ22 DQ19 DQ23

SO-DIMM (200P)

57 DQ19 DQ23 58 59 VSS22 VSS24 60

59 60 M_B_DQ29 61 62 M_B_DQ24

M_A_DQ28 VSS22 VSS24 M_A_DQ29 M_B_DQ28 DQ24 DQ28 M_B_DQ25

61 DQ24 DQ28 62 63 DQ25 DQ29 64

M_A_DQ25 63 64 M_A_DQ24 65 66 +1.8VSUS

DQ25 DQ29 M_B_DM3 VSS23 VSS25 M_B_DQS#3

65 VSS23 VSS25 66 67 DM3 DQS#3 68

M_A_DM3 67 68 M_A_DQS#3 69 70 M_B_DQS3

DM3 DQS#3 M_A_DQS3 NC4 DQS3

69 NC4 DQS3 70 71 VSS9 VSS10 72

71 72 M_B_DQ26 73 74 M_B_DQ30

M_A_DQ26 VSS9 VSS10 M_A_DQ30 M_B_DQ27 DQ26 DQ30 M_B_DQ31 + C364 C375 C365 C377 C366 C378

73 DQ26 DQ30 74 75 DQ27 DQ31 76

M_A_DQ27 75 76 M_A_DQ31 77 78

DQ27 DQ31 VSS4 VSS8 330U_3528 2.2U_6 2.2U_6 2.2U_6 2.2U_6 2.2U_6

77 VSS4 VSS8 78 [6,12] M_CKE3 79 CKE0 CKE1 80 M_CKE4 [6,12]

[6,12] M_CKE0 79 CKE0 CKE1 80 M_CKE1 [6,12] 81 VDD7 VDD8 82

B B

81 VDD7 VDD8 82 83 NC1 A15 84

83 NC1 A15 84 [7,12] M_B_BS#2 85 A16_BA2 A14 86 M_B_A14 [6,12] INTEL FAE (08/17)

[7,12] M_A_BS#2 85 86 M_A_A14 [6,12] 87 88

87

A16_BA2 A14

88 M_B_A12 89

VDD9 VDD11

90 M_B_A11 ADD MA14 FOR DUAL LAYERS RAM

M_A_A12 VDD9 VDD11 M_A_A11 M_B_A9 A12 A11 M_B_A7

89 A12 A11 90 91 A9 A7 92

M_A_A9 91 92 M_A_A7 M_B_A8 93 94 M_B_A6 +1.8VSUS SMDDR_VREF_DIMM +3V

A9 A7 INTEL FAE (08/17) A8 A6

M_A_A8 93 94 M_A_A6 95 96

95

A8 A6

96

ADD MA14 FOR DUAL LAYERS RAM M_B_A5 97

VDD5 VDD4

98 M_B_A4

M_A_A5 VDD5 VDD4 M_A_A4 M_B_A3 A5 A4 M_B_A2

97 A5 A4 98 99 A3 A2 100

M_A_A3 99 100 M_A_A2 M_B_A1 101 102 M_B_A0 C184 C187 C181 C186 C149 C140 C193 C194

M_A_A1 A3 A2 M_A_A0 A1 A0

101 A1 A0 102 103 VDD10 VDD12 104

103 104 M_B_A10 105 106 .1U_4 .1U_4 .1U_4 .1U_4 .1U_4 2.2U_6 2.2U_6 .1U_4

VDD10 VDD12 A10/AP BA1 M_B_BS#1 [7,12]

M_A_A10 105 106 [7,12] M_B_BS#0 107 108

A10/AP BA1 M_A_BS#1 [7,12] BA0 RAS# M_B_RAS# [7,12]

[7,12] M_A_BS#0 107 BA0 RAS# 108 M_A_RAS# [7,12] [7,12] M_B_WE# 109 WE# S0# 110 M_CS#2 [6,12]

[7,12] M_A_WE# 109 WE# S0# 110 M_CS#0 [6,12] 111 VDD2 VDD1 112

111 VDD2 VDD1 112 [7,12] M_B_CAS# 113 CAS# ODT0 114 M_ODT2 [6,12]

113 114 115 116 M_B_A13

[7,12] M_A_CAS# CAS# ODT0 M_ODT0 [6,12] [6,12] M_CS#3 S1# A13

[6,12] M_CS#1 115 S1# A13 116 M_A_A13 117 VDD3 VDD6 118 Close to DIMM1

117 VDD3 VDD6 118 [6,12] M_ODT3 119 ODT1 NC2 120

[6,12] M_ODT1 119 ODT1 NC2 120 121 VSS11 VSS12 122

121 122 M_B_DQ37 123 124 M_B_DQ32

M_A_DQ36 VSS11 VSS12 M_A_DQ32 M_B_DQ38 DQ32 DQ36 M_B_DQ36

123 DQ32 DQ36 124 125 DQ33 DQ37 126

M_A_DQ37 125 126 M_A_DQ33 127 128

DQ33 DQ37 M_B_DQS#4 VSS26 VSS28 M_B_DM4

127 VSS26 VSS28 128 129 DQS#4 DM4 130

M_A_DQS#4 129 130 M_A_DM4 M_B_DQS4 131 132

M_A_DQS4 DQS#4 DM4 DQS4 VSS42 M_B_DQ39

131 DQS4 VSS42 132 133 VSS2 DQ38 134

133 134 M_A_DQ35 M_B_DQ34 135 136 M_B_DQ33 +3V

M_A_DQ39 VSS2 DQ38 M_A_DQ38 M_B_DQ35 DQ34 DQ39

135 DQ34 DQ39 136 137 DQ35 VSS55 138

M_A_DQ34 137 138 139 140 M_B_DQ44

DQ35 VSS55 M_A_DQ44 M_B_DQ40 VSS27 DQ44 M_B_DQ45

139 VSS27 DQ44 140 141 DQ40 DQ45 142

M_A_DQ40 141 142 M_A_DQ45 M_B_DQ41 143 144

M_A_DQ41 DQ40 DQ45 DQ41 VSS43 M_B_DQS#5 Q9 R225 R224

143 DQ41 VSS43 144 145 VSS29 DQS#5 146

C M_A_DQS#5 M_B_DM5 M_B_DQS5 C

145 VSS29 DQS#5 146 147 DM5 DQS5 148

2

M_A_DM5 147 148 M_A_DQS5 149 150 RHU002N06 10K_4 10K_4

DM5 DQS5 M_B_DQ46 VSS51 VSS56 M_B_DQ42

149 VSS51 VSS56 150 151 DQ42 DQ46 152

M_A_DQ42 151 152 M_A_DQ43 M_B_DQ43 153 154 M_B_DQ47 3 1 DDRDAT_SMB

DQ42 DQ46 DQ43 DQ47 [2,16,19,23,24] SDATA

M_A_DQ46 153 154 M_A_DQ47 155 156

DQ43 DQ47 M_B_DQ53 VSS40 VSS44 M_B_DQ52

155 VSS40 VSS44 156 157 DQ48 DQ52 158

M_A_DQ53 157 158 M_A_DQ48 M_B_DQ49 159 160 M_B_DQ48

M_A_DQ49 DQ48 DQ52 M_A_DQ52 DQ49 DQ53 +3V

159 DQ49 DQ53 160 161 VSS52 VSS57 162

161 VSS52 VSS57 162 163 NCTEST CK1 164 M_CLK_DDR4 [6]

163 164 165 166 Q8

NCTEST CK1 M_CLK_DDR1 [6] VSS30 CK1# M_CLK_DDR#4 [6]

165 166 M_B_DQS#6 167 168

VSS30 CK1# M_CLK_DDR#1 [6] DQS#6 VSS45

2

M_A_DQS#6 167 168 M_B_DQS6 169 170 M_B_DM6 RHU002N06

M_A_DQS6 DQS#6 VSS45 M_A_DM6 DQS6 DM6

169 DQS6 DM6 170 171 VSS31 VSS32 172

171 172 M_B_DQ51 173 174 M_B_DQ55 3 1 DDRCLK_SMB

VSS31 VSS32 DQ50 DQ54 [2,16,19,23,24] SCLK

M_A_DQ50 173 174 M_A_DQ54 M_B_DQ54 175 176 M_B_DQ50

M_A_DQ51 DQ50 DQ54 M_A_DQ55 DQ51 DQ55

175 DQ51 DQ55 176 177 VSS33 VSS35 178

177 178 M_B_DQ56 179 180 M_B_DQ60

M_A_DQ56 VSS33 VSS35 M_A_DQ61 M_B_DQ57 DQ56 DQ60 M_B_DQ61

179 DQ56 DQ60 180 181 DQ57 DQ61 182

M_A_DQ60 181 182 M_A_DQ57 183 184

DQ57 DQ61 M_B_DM7 VSS3 VSS7 M_B_DQS#7

183 VSS3 VSS7 184 185 DM7 DQS#7 186

M_A_DM7 185 186 M_A_DQS#7 187 188 M_B_DQS7

DM7 DQS#7 M_A_DQS7 M_B_DQ59 VSS34 DQS7

187 VSS34 DQS7 188 189 DQ58 VSS36 190

M_A_DQ62 189 190 M_B_DQ62 191 192 M_B_DQ63

M_A_DQ63 DQ58 VSS36 M_A_DQ58 DQ59 DQ62 M_B_DQ58 SMDDR_VREF_DIMM

191 DQ59 DQ62 192 193 VSS14 DQ63 194

193 194 M_A_DQ59 DDRDAT_SMB 195 196

DDRDAT_SMB VSS14 DQ63 DDRCLK_SMB SDA VSS13 R217 10K_4

195 SDA VSS13 196 197 SCL SA0 198

DDRCLK_SMB 197 198 R202 10K_4 +3V 199 200 R216 10K_4

+3V SCL SA0 R201 10K_4 VDD(SPD) SA1

+3V 199 VDD(SPD) SA1 200

TYCO_292564-4 +3V R208 0_6 SMDDR_VREF

TYCO_1-1734071-1

SO-DIMM0 SPD Address is 0xA0 SO-DIMM1 SPD Address is 0xA4

SO-DIMM0 TS Address is 0x30 SO-DIMM1 TS Address is 0x34 R209 *10K_4 R117 *10K_4 +1.8VSUS

D D

H: 5.6mm H: 10.1mm

CLOCK 0,1 CLOCK 3,4

CKE 0,1 CKE 2,3 Quanta Computer Inc.

PROJECT : BU1 Santa Rosa

Size Document Number Rev

DDR SO-DIMM(200P) 3A

Date: Monday, March 26, 2007 Sheet 13 of 33

1 2 3 4 5 6 7 8

5 4 3 2 1

RTC

D11

VCCRTC

CH500H-40 VCCRTC C247 1U_6

www.bufanxiu.com

+3VPCU

<check list>

Delay 18~25ms C383 15P_4

VCCRTC_4 D12 CH500H-40 R232 20K_6

1

R246 R226 G1 C237 Y4 R375

1K_4 1U_6 32.768KHZ 10M_6

U16A

2

D 1M_6 *SHORT_PAD D

CLK_32KX1 AG25 E5

RTCX1 FWH0/LAD0 LAD0 [23,26]

C386 15P_4 CLK_32KX2 AF24 F5

RTCX2 FWH1/LAD1 LAD1 [23,26] +1.05V_V_CPU_IO

CN24 G8

FWH2/LAD2 LAD2 [23,26]

1 1 RTCRST# AF23 F6

RTCRST# FWH3/LAD3 LAD3 [23,26]

2 2

SM_INTRUDER# AD22 C4 +1.05V_V_CPU_IO

INTRUDER# FWH4/LFRAME# LFRAME# [23,26]

ACS_85204-0200L

ICH_INTVRMEN

RTC

LPC

AF25 INTVRMEN LDRQ0# G9 T68

CMOS Setting G1 LAN100_SLP AD21 LAN100_SLP LDRQ1#/GPIO23 E6 LDRQ#1

LDRQ#1 [23]

R165 R164

Clear CMOS Short B24 AF13 GATEA20 *56.2_4 *56.2_4 R175

Keep CMOS Open GLAN_CLK A20GATE GATEA20 [26]

A20M# AG26 H_A20M# [3]

D22 56.2_4

LAN_RSTSYNC H_DPRSTP#_R R161 0_4

DPRSTP# AF26 ICH_DPRSTP# [3,6,29]

C21 AE26 H_DPSLP#_R R169 0_4

LAN_RXD0 DPSLP# H_DPSLP# [3]

B21 LAN_RXD1

C22 LAN_RXD2 FERR# AD24 H_FERR# [3]

VCCRTC_3

LAN / GLAN

D21 AG29 H_PWRGD_R R153 0_4

LAN_TXD0 CPUPWRGD/GPIO49 H_PWRGD [3]

E20 LAN_TXD1

C20 LAN_TXD2 IGNNE# AF27 H_IGNNE# [3]

+5VPCU AH21 AE24

GLAN_DOCK#/GPIO13 INIT# H_INIT# [3]

INTR AC20 H_INTR [3]

R222 *24.9_4 GLAN_COMP_SB RCIN# +1.05V_V_CPU_IO

CPU

+1.5V_PCIE D25 GLAN_COMPI RCIN# AH14 RCIN# [26]

R245 8.66K/F_4 VCCRTC_1 R240 8.66K/F_4 VCCRTC_2 3 1 C25 GLAN_COMPO

NMI AD23 H_NMI [3]

ACZ_BCLK AJ16 AG28 H_SMI#_R R154 0_4 R206

HDA_BIT_CLK SMI# H_SMI# [3]

R248 Q10 ACZ_SYNC AJ15 HDA_SYNC

2

STPCLK# AA24 H_STPCLK# [3]

56.2_4 Placement close SB L<2"

4.7K_4 MMBT3904 ACZ_RST# AE14

C HDA_RST# H_THERMTRIP_R R203 24_6 R205 *0_4 C

THRMTRIP# AE27 PM_THRMTRIP# [3,6]

[24] ACZ_SDIN0 AJ17 HDA_SDIN0

AH17 AA23 ICH_TP8

[25] ACZ_SDIN1 HDA_SDIN1 TP8 T63

ACZ_SDIN2 AH15 HDA_SDIN2 PDD[15:0] [19]

R247 T109 ACZ_SDIN3 AD13 V1 PDD0

IHDA

T58 HDA_SDIN3 DD0 PDD1

+3V DD1 U2

15K_4 R480 ACZ_SDOUT AE13 V3 PDD2

*10K_4 HDA_SDOUT DD2 PDD3 +3V +3V

DD3 T1

AE10 V4 PDD4

T56 HDA_DOCK_EN#/GPIO33 DD4 PDD5

AG14 HDA_DOCK_RST#/GPIO34 DD5 T5

T54 AB2 PDD6

DD6

[25] SATA_LED#

SATA_LED# AF10 SATALED# DD7 T6 PDD7 0810 UR FAE: R131 R379

T3 PDD8

C136 3900P_4 SATA_RXN0_C AF6

DD8

R2 PDD9 RCIN# DOESN'T NEED PU 10K_4 8.2K_4

[19] SATA_RXN0 SATA0RXN DD9

C138 3900P_4 SATA_RXP0_C AF5 T4 PDD10

[19] SATA_RXP0 SATA0RXP DD10

C135 3900P_4 SATA_TXN0_C AH5 V6 PDD11 RCIN#

[19] SATA_TXN0 SATA0TXN DD11

C132 3900P_4 SATA_TXP0_C AH6 V5 PDD12 GATEA20

[19] SATA_TXP0 SATA0TXP DD12

U1 PDD13

DD13 PDD14

AG3 SATA1RXN DD14 V2

AG4 U6 PDD15

SATA1RXP DD15

IDE

AJ4 SATA1TXN PDA[2:0] [19]

AJ3 AA4 PDA0

SATA1TXP DA0 PDA1

DA1 AA1

PDA2

SATA

AF2 SATA2RXN DA2 AB3

AF1 SATA2RXP

AE4 SATA2TXN DCS1# Y6 PDCS1# [19]

AE3 Y5

SATA Disable SATA2TXP DCS3# PDCS3# [19]

[2] CLK_PCIE_SATA# AB7 SATA_CLKN DIOR# W4 PDIOR# [19]

1.Connect to GND: SATA[2:0]RXp/n , SATARBIAS , SATARBIAS# , SATA_CLKP , SATACLKN [2] CLK_PCIE_SATA AC6 SATA_CLKP DIOW# W3 PDIOW# [19]

2.NC: SATA[2:0]TXp/n , SATALED# DDACK# Y2 PDDACK# [19]

AG1 Y3 IRQ14 [19]

B 3.VccSATAPLL should be connected directly to Vcc1_5,Filter cap are not required R139 24.9_4 SATA_BIAS AG2

SATARBIAS# IDEIRQ

Y1 B

4.BIOS disable SATARBIAS IORDY PDIORDY [19]

DDREQ W5 PDDREQ [19]

<check list>

L<500mils ICH8M REV 1.0

SB Strap HDA

XOR Chain Entrance Strap

ICH8-M Internal VR Enable strap ICH8-M LAN100_SLP Strap ACZ_SDOUT R392 33_4

(Internal VR for Vccsus1_05,VccSus1_5 and VccCL1_5) (Internal VR for VccLAN1_05 and VccCL1.05) ACZ_SDOUT_AUDIO [24]

ICH_RSV0 HDA_SDOUT Description

R393 33_4

ACZ_SDOUT_MDC [25]

INTVRMEN Low = Internal VR disable LAN100_SLP Low = Internal VR disable 0 0 RSVD

High = Internal VR enable(Default) High = Internal VR enable(Default)

0 1 Enter XOR Chain ACZ_SYNC R130 33_4

ACZ_SYNC_AUDIO [24]

1 0 Normal opration(Default) R129 33_4

ACZ_SYNC_MDC [25]

1 1 Set PCIE port config bit 1

ACZ_BCLK R364 33_4

BIT_CLK_AUDIO [24]

R365 33_4

VCCRTC +3V BIT_CLK_MDC [25]

VCCRTC

ACZ_RST# R172 33_4

A ACZ_RST#_AUDIO [24] A

R149 R394 R167 33_4

ACZ_RST#_MDC [25]

332K_6 R147 *1K_6

332K_6

ICH_INTVRMEN ACZ_SDOUT

LAN100_SLP

ICH_TP3 [16]

R162

*0_4 R150

Quanta Computer Inc.

*0_4 R361

*1K_4 PROJECT : BU1 Santa Rosa

Size Document Number Rev

ICH8M HOST(1 of 4) 2A

Date: Tuesday, March 27, 2007 Sheet 14 of 33

5 4 3 2 1

5 4 3 2 1

SB-PCIE/USB/DMI

U16D

www.bufanxiu.com

[23] PCIE_RXN1 P27 PERN1 DMI0RXN V27 DMI_RXN0 [6] A16 SWAP Override strap

To WLAN [23] PCIE_RXP1 P26 PERP1 DMI0RXP V26 DMI_RXP0 [6]

C204 .1U_4 PCIE_TXN1_C N29 U29

[23] PCIE_TXN1 PETN1 DMI0TXN DMI_TXN0 [6]

C192 .1U_4 PCIE_TXP1_C N28 U28 PCI_GNT#3 Low = A16 swap override enabled

[23] PCIE_TXP1 PETP1 DMI0TXP DMI_TXP0 [6]

Direct Media Interface

High = Default

[20] PCIE_RXN4 M27 PERN2 DMI1RXN Y27 DMI_RXN1 [6]

To LAN [20] PCIE_RXP4 M26 PERP2 DMI1RXP Y26 DMI_RXP1 [6]

C222 .1U_4 PCIE_TXN4_C L29 W29 GNT3# R227 *1K_4

[20] PCIE_TXN4 PETN2 DMI1TXN DMI_TXN1 [6]

C219 .1U_4 PCIE_TXP4_C L28 W28

D [20] PCIE_TXP4 PETP2 DMI1TXP DMI_TXP1 [6] D

PCI-Express

[23] PCIE_RXN3 K27 PERN3 DMI2RXN AB26 DMI_RXN2 [6] ICH8 Boot BIOS select

To 3G [23] PCIE_RXP3 K26 PERP3 DMI2RXP AB25 DMI_RXP2 [6]

C214 .1U_4 PCIE_TXN3_C J29 AA29

[23] PCIE_TXN3 PETN3 DMI2TXN DMI_TXN2 [6]

C209 .1U_4 PCIE_TXP3_C J28 AA28 PCI_GNT#0 SPI_CS#1 Boot BIOS Location

[23] PCIE_TXP3 PETP3 DMI2TXP DMI_TXP2 [6]

[24] PCIE_RXN2 H27 PERN4 DMI3RXN AD27 DMI_RXN3 [6]

To New Card H26 AD26 +1.5V_PCIE 0 1 SPI(Default)

[24] PCIE_RXP2 PERP4 DMI3RXP DMI_RXP3 [6]

C229 .1U_4 PCIE_TXN2_C G29 AC29

[24] PCIE_TXN2 PETN4 DMI3TXN DMI_TXN3 [6]

C234 .1U_4 PCIE_TXP2_C G28 AC28

[24] PCIE_TXP2 PETP4 DMI3TXP DMI_TXP3 [6]

1 0 PCI

F27 T26 R186

T71 PERN5 DMI_CLKN CLK_PCIE_ICH# [2]

T69 F26 PERP5 DMI_CLKP T25 CLK_PCIE_ICH [2]

E29 24.9_4 1 1 LPC

T103 PETN5

T102 E28 PETP5 DMI_ZCOMP Y23

Y24 DMI_IRCOMP_R

DMI_IRCOMP

T76 D27 PERN6/GLAN_RXN

D26 G3 SPI_CS1# R220 *1K_4

T72 PERP6/GLAN_RXP USBP0N USBP0- [24]

T78 C29 PETN6/GLAN_TXN USBP0P G2 USBP0+ [24] To USB BOARD(Audio)

C28 H5 GNT0# R223 *1K_4

T74 PETP6/GLAN_TXP USBP1N USBP1- [24]

USBP1P H4 USBP1+ [24] To USB BOARD(Audio)

T77 C23 SPI_CLK USBP2N H2 USBP8- [18]

T101 B23 SPI_CS0# USBP2P H1 USBP8+ [18] To Camera

SPI_CS1# E22 J3

T75 SPI_CS1# USBP3N USBP3- [23]

SPI

USBP3P J2 USBP3+ [23] To WLAN

T73 D23 SPI_MOSI USBP4N K5 USBP4- [24]

T70 F21 SPI_MISO USBP4P K4 USBP4+ [24] To Finger Printer

USBP5N K2 USBP5- [24]

USBOC#0 AJ19 K1 To Bluetooth

OC0# USBP5P USBP5+ [24]