Professional Documents

Culture Documents

Uart Controller v1 1

Uploaded by

Mitu MitzOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Uart Controller v1 1

Uploaded by

Mitu MitzCopyright:

Available Formats

chipmunklogic.

com Chipmunk Logic™

UART Controller v1.1

IP Documentation

June 2021

UART Controller v1.1 P a g e 1 | 10

chipmunklogic.com Chipmunk Logic™

Licensing Notice

UART Controller v1.1 is a fully tested, portable, configurable, and synthesisable soft IP core provided

by Chipmunk Logic™. The IP source files are complied with IEEE VHDL/Verilog/System-Verilog

standards. All the source codes are open-source licensed and hence may be used, modified, and

shared without any restrictions or conflicts of interest with the original developer.

Chipmunk Logic™ shall not be liable or held accountable for any loss or damage (direct or indirect)

resulting from the use of any product, as the designs are not intended to be fail-safe or for use in any

application requiring fail-safe performance. Hence, the user shall assume sole risk and liability for the

use of any of our products in any of their applications.

UART Controller v1.1 P a g e 2 | 10

chipmunklogic.com Chipmunk Logic™

Table of Contents

1. UART Controller .............................................................................................................................. 4

2. Features .......................................................................................................................................... 4

3. Overview ......................................................................................................................................... 5

4. Top-level Ports/Interfaces .............................................................................................................. 6

5. Designing with the IP ...................................................................................................................... 7

5.1 Clocking and Reset .................................................................................................................. 7

5.2 Configuring the IP.................................................................................................................... 7

5.3 Handshaking with IP................................................................................................................ 7

UART Controller v1.1 P a g e 3 | 10

chipmunklogic.com Chipmunk Logic™

1. UART Controller

UART Controller IP Core provides a simple asynchronous serial interface for data

transmission and reception. UART signalling is implemented at the serial interface. The core

also provides a parallel data interface and control interface to control the data flow. It performs

parallel-to-serial conversion of data received at parallel data interface, and serial-to-parallel

conversion of data received at serial interface.

2. Features

✓ Full duplex communication, 8-bit data.

✓ Simple valid-ready handshaking at the data interface of Transmitter and Receiver for

ease of integration with FIFOs.

✓ Configurable parity: odd, even, or no parity.

✓ Configurable baud rate.

✓ Built-in CDC synchronizer at receiver line.

UART Controller v1.1 P a g e 4 | 10

chipmunklogic.com Chipmunk Logic™

3. Overview

Fig 3.1 shows the top-level block diagram of UART Controller. Various interfaces and sub-

blocks are:

• Control Interface: Set of signals to control the operation of the IP, like baud rate, packet

format etc.

• Data Interface: Parallel data and handshaking interface.

• TX and RX: Serial data interface for transmission and reception.

• Status flags: Status flags for errors in communication.

• Clock and Reset: System clock and reset.

• UART Transmitter: Converts parallel data to serial data and sends via TX.

• UART Receiver: Converts serial data received via RX to parallel data.

• Baud Generator: Controls baud rate.

Fig 3.1: UART Controller – Block Diagram

UART Controller v1.1 P a g e 5 | 10

chipmunklogic.com Chipmunk Logic™

4. Top-level Ports/Interfaces

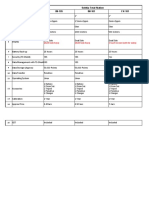

Table 4.1 lists all top-level I/O ports/interfaces of the IP.

Signal Name Direction Width Description

clk input 1 Core clock

rstn input 1 Core reset (active-low)

Control Interface

i_baudrate input 16 Baud rate configuration, see here for details.

i_parity_mode input 2 Parity mode configuration.

“00” or “10” – No parity bit in serial data

“01” – Odd parity bit

“11” – Even parity bit

i_frame_mode input 0 No. of start and stop bits in serial data.

‘0’ – 1 start bit and 1 stop bit

‘1’ – 1 start bit and 2 stop bits

i_tx_en input 1 To enable Transmitter and its baud clock.

Disabling will reset the transmitter.

i_rx_en input 1 To enable Receiver and its baud clock.

Disabling will reset the receiver.

Transmitter – Data Interface

i_data input 8 Byte to be transmitted

i_data_valid input 1 Byte valid

o_ready output 1 Transmitter ready to accept the byte to be

transmitted

o_tx output 1 Serial data out

Receiver – Data Interface

i_rx input 1 Serial data in

o_data output 8 Byte which is received

o_data_valid output 1 Byte valid

i_ready input 1 To read out the byte received at Receiver

Status flags

o_parity_err output 1 Indicates that parity error has occurred for the

last byte received. The received byte is still

available to read out from Receiver.

o_frame_err output 1 Indicates that frame error (one or more stop

bits not detected) has occurred for the last

byte received. The received byte is ignored

and not available to read out from Receiver.

Table 4.1: Top-level Ports/Interfaces

UART Controller v1.1 P a g e 6 | 10

chipmunklogic.com Chipmunk Logic™

5. Designing with the IP

This chapter discusses guidelines, performance, and other known limitations while designing

with the IP.

5.1 Clocking and Reset

The core clock clk synchronizes the complete operation of the core. Baud clocks for

Transmitter and Receiver are generated from this clock. Reset rstn is synchronous active-

low and is recommended to be pulsed for multiple clock cycles to do a proper reset of the

core.

5.2 Configuring the IP

The IP after reset, is dynamically configured for baud rate, parity mode, frame mode.

Transmitter/Receiver or both are then enabled.

Baud Rate Configuration

The integer value B to be configured in i_baudrate to set the baud rate of serial data transfer

at Transmitter and Receiver, can be calculated as follows:

𝑐𝑜𝑟𝑒 𝑐𝑙𝑜𝑐𝑘 𝑓𝑟𝑒𝑞𝑢𝑒𝑛𝑐𝑦

𝐵=

𝑏𝑎𝑢𝑑 𝑟𝑎𝑡𝑒 𝑟𝑒𝑞𝑢𝑖𝑟𝑒𝑑

For e.g., if the core clock is 100 MHz, and baud rate required is 9600, then B is configured as:

100 × 106

≈ 𝟏𝟎𝟒𝟏𝟔

9600

𝑐𝑜𝑟𝑒 𝑐𝑙𝑜𝑐𝑘 𝑓𝑟𝑒𝑞𝑢𝑒𝑛𝑐𝑦

The maximum achievable baud rate for a given core clock is .

16

Receiver samples serial data at 8x. i.e., internally, 8x baud clock is used by Receiver.

Maximum tolerable baud rate error is ±5%. Since B can be configured only as integer, it

introduces a rounding-off error in baud clock rate. It is imperative that this error is kept within

the prescribed range. Use higher-frequency core clock to achieve more accurate baud clock

generation, especially if higher baud rates are targeted.

5.3 Handshaking with IP

The core has implemented a simple valid-ready handshaking at the parallel data interface.

The byte to be sent/received has to be properly communicated with the core using handshake

signals: valid and ready. Fig 5.1 shows how a typical handshaking is done with the core to

transmit and receive two bytes.

UART Controller v1.1 P a g e 7 | 10

chipmunklogic.com Chipmunk Logic™

Figure 5.1: Valid-Ready Handshaking with IP

Writing a Byte to Core

User may assert i_data_valid when a byte has to be transmitted via o_tx. The byte is

written on i_data. User needs not wait for o_ready to be asserted. The core asserts o_ready

when it has finished the transmission of the previous byte, and is ready to accept a new byte.

It needs not wait for i_data_valid to be asserted. However, the byte is written to the core

only when both i_data_valid and o_ready are high.

Reading a Byte from Core

The core asserts o_data_valid when a byte has been received via i_rx. The byte is

available on o_data. It needs not wait for i_ready to be asserted. User may assert i_ready

to read the byte. It’s not mandatory that i_ready should be asserted only after

o_data_valid; it may be asserted in advance. However, the byte is read from the core only

when both o_data_valid and i_ready are high.

FIFO Integration

The IP has no FIFOs integrated at Transmitter or Receiver. However, the valid-ready

handshaking at the parallel data interface eases the integration of FIFOs at user’s will. The

valid and ready signals can directly manipulate enqueue, dequeue, full, and empty flags of a

typical FIFO with minimal/no glue-logic.

UART Controller v1.1 P a g e 8 | 10

chipmunklogic.com Chipmunk Logic™

Appendix

a) FPGA Resource Utilization

FPGA Targeted Basys-3 Board (XC7A-35T-CPG236-1)

Synthesiser Vivado 2015.4

Targeted clock frequency 200 MHz

LUTs 129

Registers 98

b) Test Report

FPGA Targeted Basys-3 Board (XC7A-35T-CPG236-1)

Synthesiser Vivado 2015.4

Core clock 100 MHz

Baud rates tested 300 to 115200

Parity modes tested All modes

Frame modes tested All modes

Test mode Loop back, and with other UART devices

Test result Successfully passed

UART Controller v1.1 P a g e 9 | 10

chipmunklogic.com Chipmunk Logic™

UART Controller v1.1

An open-source licensed IP core

Developer : Mitu Raj

Vendor : Chipmunk Logic™, chip@chipmunklogic.com

Website : chipmunklogic.com

UART Controller v1.1 P a g e 10 | 10

You might also like

- BEAT-900 Service ManualDocument86 pagesBEAT-900 Service Manualidrovodi50% (2)

- SofarHYD ES ME3000SP Modbus ProtocolDocument61 pagesSofarHYD ES ME3000SP Modbus ProtocolPIPPO PAPPONo ratings yet

- Acer AL1714 PDFDocument9 pagesAcer AL1714 PDFweelun yapNo ratings yet

- Plugin Alliance - All Plugins 2013 R3, All Bundle 2015.1.0, Lindell 100 Bundle 1.1.0, Unfiltered Audio 100 Bundle 1.0.0 (NO INSTALLDocument7 pagesPlugin Alliance - All Plugins 2013 R3, All Bundle 2015.1.0, Lindell 100 Bundle 1.1.0, Unfiltered Audio 100 Bundle 1.0.0 (NO INSTALLMuhammad WahidNo ratings yet

- Ebook Windows Server 2022 New Roadmap Fewer Editions More SecurityDocument26 pagesEbook Windows Server 2022 New Roadmap Fewer Editions More SecurityRemiche100% (1)

- MC C5.1 Serial Communication Rv01 - HC v19.1Document22 pagesMC C5.1 Serial Communication Rv01 - HC v19.1BodeaGabrielaNo ratings yet

- How to Get a Second Asynchronous Interface on a 80C51 MicrocontrollerDocument8 pagesHow to Get a Second Asynchronous Interface on a 80C51 Microcontrollerscribduser100% (1)

- Serial Communications: ObjectivesDocument26 pagesSerial Communications: ObjectivesAmy OliverNo ratings yet

- An 8Document45 pagesAn 8ThanhvicNo ratings yet

- Serial PortDocument31 pagesSerial Porttariq7868100% (2)

- An Introduction To Serial Port InterfacingDocument31 pagesAn Introduction To Serial Port InterfacingVeerendra SimplyMeNo ratings yet

- Lecture Slide 4Document48 pagesLecture Slide 4Sunil SahooNo ratings yet

- I2C DataSheetDocument14 pagesI2C DataSheetDeepika RaoNo ratings yet

- Unit Iii I/O Interfacing Reference: Chapter 9 Microcomputer Systems, Cheng Liu, Glenn GibsonDocument337 pagesUnit Iii I/O Interfacing Reference: Chapter 9 Microcomputer Systems, Cheng Liu, Glenn GibsonGomathi PsNo ratings yet

- Serial Communication Programming in CDocument28 pagesSerial Communication Programming in CDr Narayana Swamy RamaiahNo ratings yet

- Tampering Detection of Transmission Line: AbstractDocument9 pagesTampering Detection of Transmission Line: AbstractJayant KumarNo ratings yet

- Device Communication ModesDocument141 pagesDevice Communication ModesDevashishNo ratings yet

- 8051 FeaturesDocument8 pages8051 FeaturesnakranimahenderNo ratings yet

- UART Communication Protocol - How It Works - Codrey ElectronicsDocument14 pagesUART Communication Protocol - How It Works - Codrey ElectronicsPhogat Ashish100% (1)

- Experiment No. 1 (B) : Interfacing UART of LPC2148 To Transmit and Receive MessageDocument4 pagesExperiment No. 1 (B) : Interfacing UART of LPC2148 To Transmit and Receive MessageJohn FarandisNo ratings yet

- Interrupt Initiated I/O and DMA in Computer OrganizationDocument67 pagesInterrupt Initiated I/O and DMA in Computer Organizationjinto0007No ratings yet

- Es Notes Unit 5Document33 pagesEs Notes Unit 51balamanianNo ratings yet

- RS232 Serial Communication Configuration and BasicsDocument31 pagesRS232 Serial Communication Configuration and Basicsjaigodara100% (1)

- Universal - Asynchronous - Receiver-Transmitter - ENDocument12 pagesUniversal - Asynchronous - Receiver-Transmitter - ENArturo Yanez S.G.No ratings yet

- Project Objective:: Universal Asynchronous Receiver and TransmitterDocument16 pagesProject Objective:: Universal Asynchronous Receiver and Transmitterapi-3742890No ratings yet

- Testplan OdsDocument68 pagesTestplan OdsHòa Nguyễn Lê MinhNo ratings yet

- Uart Core Ug v3.6Document18 pagesUart Core Ug v3.6haniamani37No ratings yet

- Lecture12 Serial IODocument20 pagesLecture12 Serial IOecevitmert1453No ratings yet

- Mevi Hub: How To Interface UART With 8051Document16 pagesMevi Hub: How To Interface UART With 8051Javier ParedesNo ratings yet

- Arm Ep9302 UartDocument15 pagesArm Ep9302 UartBala ChandranNo ratings yet

- AVR Microcontroller: Prepared By: Eng. Ashraf DarwishDocument28 pagesAVR Microcontroller: Prepared By: Eng. Ashraf DarwishHectorLopez100% (2)

- TDE6115 01 UserGuideDocument24 pagesTDE6115 01 UserGuidevanlang87No ratings yet

- FESD Unit2 AVR PDFDocument115 pagesFESD Unit2 AVR PDFvarshaNo ratings yet

- Interrupcions: Processor - I/O Speed MismatchDocument18 pagesInterrupcions: Processor - I/O Speed MismatchRonyVargasNo ratings yet

- Embedded Systems & Micro-Controllers - 01-09-2022Document32 pagesEmbedded Systems & Micro-Controllers - 01-09-2022anirudhNo ratings yet

- Serial Communication Using AVR Lab 8 PDFDocument5 pagesSerial Communication Using AVR Lab 8 PDFlovelyosmile253100% (1)

- Abb PSTX Fieldbus ProfibusDocument11 pagesAbb PSTX Fieldbus ProfibusFarouk MechtaNo ratings yet

- Agilent HP 34907A PDFDocument3 pagesAgilent HP 34907A PDFTiago GalloNo ratings yet

- UartDocument25 pagesUartWajeed Mohamad100% (2)

- XBee ZB Command Reference Tables - in Alphabetical FormDocument8 pagesXBee ZB Command Reference Tables - in Alphabetical FormDenz ChoeNo ratings yet

- Serial UART Communication Using MicrocontrollerDocument12 pagesSerial UART Communication Using MicrocontrollerGaurav Gupta100% (1)

- ST NDDocument9 pagesST NDsrikaanth3811No ratings yet

- MPMC Unit 5Document62 pagesMPMC Unit 5ganeshNo ratings yet

- Serial Communication With 8051Document25 pagesSerial Communication With 8051prakriti sankhlaNo ratings yet

- Serial CommunicationDocument52 pagesSerial CommunicationDr Narayana Swamy RamaiahNo ratings yet

- ADE Vas App PPT NewDocument39 pagesADE Vas App PPT NewHarish MahadevanNo ratings yet

- RS232CDocument17 pagesRS232CRam PrahaNo ratings yet

- IoT Communication Protocols and Data Transmission ExamplesDocument83 pagesIoT Communication Protocols and Data Transmission ExamplesVyshnavi Challa ObullaNo ratings yet

- UARTDocument26 pagesUARTShantanu Tripathi100% (2)

- Chapter 5 Serial IO InterfaceDocument51 pagesChapter 5 Serial IO InterfacetesfayebbNo ratings yet

- Infrared Data Transmission With The PIC MicrocontrollerDocument9 pagesInfrared Data Transmission With The PIC MicrocontrollerVenkatesan RamamoorthyNo ratings yet

- Using UART of PIC Microcontroller With Hi-Tech CDocument13 pagesUsing UART of PIC Microcontroller With Hi-Tech CYoussef KhairaneNo ratings yet

- The UART Project: Applying What We've Learned About Linux Device-Drivers To The PC's Serial-Port ControllerDocument43 pagesThe UART Project: Applying What We've Learned About Linux Device-Drivers To The PC's Serial-Port ControllerPradeep KumarNo ratings yet

- 8051 Microcontroller IntroductionDocument116 pages8051 Microcontroller IntroductionVivek ThotaNo ratings yet

- Es 2Document31 pagesEs 2sanjay.sampath.kNo ratings yet

- Universal Asynchronous Receiver Transmitter (UART)Document38 pagesUniversal Asynchronous Receiver Transmitter (UART)Chandresh Trivedi100% (1)

- 4.1. Starting A SwitchDocument34 pages4.1. Starting A SwitchQuân Lâm MinhNo ratings yet

- SPEED CHECKER FOR HI-WAsYSDocument26 pagesSPEED CHECKER FOR HI-WAsYSAbhinav KumaarNo ratings yet

- 嵌入式系統 Introduction to Embedded System Design: Part 5: Serial Communication (UART)Document26 pages嵌入式系統 Introduction to Embedded System Design: Part 5: Serial Communication (UART)N26094354鐘筠凱No ratings yet

- 8051 - Serial CommunicationDocument44 pages8051 - Serial CommunicationDr-Samson ChepuriNo ratings yet

- Serial Port MicrocontrollerDocument30 pagesSerial Port MicrocontrollerguestNo ratings yet

- Wireless Communication Systems Error Correction CodesDocument32 pagesWireless Communication Systems Error Correction Codesnabeel hasanNo ratings yet

- UART Using System VerilogDocument4 pagesUART Using System VerilogJaiNo ratings yet

- Base SAS QuestionsDocument34 pagesBase SAS QuestionsAmlen Singha100% (1)

- Replacing Compact Flash On A 7x50 v09Document11 pagesReplacing Compact Flash On A 7x50 v09dilligas1234No ratings yet

- Ecc G100Document2 pagesEcc G100Davor PredavecNo ratings yet

- ARK - Intel® Core™ i7-3630QM Processor (6M Cache, Up To 3Document3 pagesARK - Intel® Core™ i7-3630QM Processor (6M Cache, Up To 3OtonielCardenasNo ratings yet

- Data Sheet: Graphics Displays and Interface/adaptor CardsDocument8 pagesData Sheet: Graphics Displays and Interface/adaptor CardsSergey DNo ratings yet

- BMXP342020: Bảng thông số sản phẩmDocument4 pagesBMXP342020: Bảng thông số sản phẩmquangNo ratings yet

- Best Practice GuideDocument50 pagesBest Practice GuideSalvatore MammolaNo ratings yet

- Solaris - Sys Admin 1Document419 pagesSolaris - Sys Admin 1pradipgudale2000No ratings yet

- ADXL317 (中文版)Document38 pagesADXL317 (中文版)vaoa188No ratings yet

- Passport 8600 Product BriefDocument96 pagesPassport 8600 Product BriefKevin Lopo1100% (2)

- Sony Vaio Pricelist LatestDocument1 pageSony Vaio Pricelist LatestgcnlNo ratings yet

- Name: - Tengku Muhammad Firdaus - ID: Section: - 01 - Date: - 16/11/2021 - Quiz 1Document2 pagesName: - Tengku Muhammad Firdaus - ID: Section: - 01 - Date: - 16/11/2021 - Quiz 1TENGKU FIRDAUSNo ratings yet

- S.No Particular Sokkia Total Station IM-105 IM-101 FX-101Document4 pagesS.No Particular Sokkia Total Station IM-105 IM-101 FX-101AshokNo ratings yet

- Telegra-TGI RFCDocument6 pagesTelegra-TGI RFCVinod Kumar MalikNo ratings yet

- X-DSL Original XBOX ManualDocument38 pagesX-DSL Original XBOX ManualFelipe LimaNo ratings yet

- 01 IntroductionDocument29 pages01 IntroductionindhumathiNo ratings yet

- iCE40 Hardware Checklist: FPGA-TN-02006-1.8Document13 pagesiCE40 Hardware Checklist: FPGA-TN-02006-1.8RamiroNo ratings yet

- Siemens Digsi 5 EngineeringDocument144 pagesSiemens Digsi 5 EngineeringYM6BNo ratings yet

- COA Lecture 20Document26 pagesCOA Lecture 20Chhaveesh AgnihotriNo ratings yet

- Ideacentre Yoga-A940-27icb HMM 20190114Document65 pagesIdeacentre Yoga-A940-27icb HMM 20190114umeshNo ratings yet

- Access card delivers Gigabit Ethernet interfacesDocument3 pagesAccess card delivers Gigabit Ethernet interfacesmehdi_mehdiNo ratings yet

- 8086 Min Max ModesDocument31 pages8086 Min Max ModeschakrimvnNo ratings yet

- Distributed Operating: Systems Spring 2005Document23 pagesDistributed Operating: Systems Spring 2005Aasia QayoumNo ratings yet

- WC5335 PDFDocument140 pagesWC5335 PDFPhú LêNo ratings yet

- GD25Q80 GigaDevice PDFDocument34 pagesGD25Q80 GigaDevice PDFanshumantech anshumantechNo ratings yet

- MR20H40 / MR25H40: FeaturesDocument30 pagesMR20H40 / MR25H40: Featureshobsol05569No ratings yet