Professional Documents

Culture Documents

2015-2016 Co Dap An

2015-2016 Co Dap An

Uploaded by

Tài Vũ Hoàng0 ratings0% found this document useful (0 votes)

6 views4 pagesde thi Thiet ke he thong so

Original Title

2015-2016 CO DAP AN

Copyright

© © All Rights Reserved

Available Formats

DOC, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Documentde thi Thiet ke he thong so

Copyright:

© All Rights Reserved

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

6 views4 pages2015-2016 Co Dap An

2015-2016 Co Dap An

Uploaded by

Tài Vũ Hoàngde thi Thiet ke he thong so

Copyright:

© All Rights Reserved

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

You are on page 1of 4

BM01a/QT01/KT

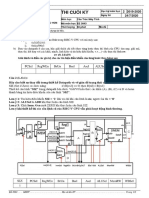

ĐỀ THI HỌC KỲ III LẦN 1 NĂM HỌC 2015 - 2016

Ngành/Lớp : 13DDT, 13LDDT, 15HDT

Môn thi : Thiết Kế Hệ Thống Số

Mã môn học : 401088 Số ĐVHT/TC: 2

KHOA CƠ – ĐIỆN – ĐIỆN TỬ

Ngày thi : ………………....…………………

Thời gian làm bài: 60 phút.

Mã đề (Nếu có) : ……………..………………….....

SỬ DỤNG TÀI LIỆU: CÓ KHÔNG

Đề 3

CÂU 1.( 3 điểm ): Một hệ thống số có 4 ngõ vào ABCD và 1 ngõ ra Y. Ngõ ra Y

= 1 khi giá trị thập phân của tổ hợp biến ngõ vào là 0, 1, 3, 5, 12, 14.

a) Rút gọn hàm Y bằng phương pháp Quin MC Clusky

b) Viết chương trình Abel mô tả hàm Y

c) Viết chương trình VHDL mô tả hàm y

CÂU 2. ( 2 điểm ): .

Dùng PAL thiết kế mạch tổ hợp thực hiện các hàm logic sau:

;

CÂU 3. (2 điểm ) :

Viết chương trình bằng ngôn ngữ VHDL mô tả : Mạch so sánh 2 số nhị phân 8

bit.

CÂU 4 ( 3 đểm):

Viết chương trình bằng ngôn ngữ VHDL mô tả : JK-FF. PRESET (PR),

CLEAR (CLR) tích cực mức cao, Clock tác động cạnh lên

Cán bộ coi thi không được giải thích gì thêm.

BM01a/QT01/KT

BM01a/QT01/KT

BM01a/QT01/KT

You might also like

- 2014-2015 Co Dap AnDocument5 pages2014-2015 Co Dap AnTài Vũ HoàngNo ratings yet

- De Thi Hoc Ky - de 1Document2 pagesDe Thi Hoc Ky - de 1Tài Vũ HoàngNo ratings yet

- 2018-2018 Co Dap AnDocument5 pages2018-2018 Co Dap AnTài Vũ HoàngNo ratings yet

- Thi CTMT 192Document2 pagesThi CTMT 192Vỹ TrầnNo ratings yet

- FILE - 20220513 - 083405 - Đề thi KTS HK2 2015-2016Document2 pagesFILE - 20220513 - 083405 - Đề thi KTS HK2 2015-2016Huỳnh Thanh ĐôNo ratings yet

- DeThiMau Gui SVDocument3 pagesDeThiMau Gui SVlukhanhduy0122No ratings yet

- THI - BM03 (De Thi Thuc Hanh)Document20 pagesTHI - BM03 (De Thi Thuc Hanh)Hanh DovanNo ratings yet

- 003 VXLDocument1 page003 VXLDien NguyenNo ratings yet

- De 1 - D06CNTT - ThilaiDocument4 pagesDe 1 - D06CNTT - Thilaicaungoi1278No ratings yet

- VXL HK1N1920 01 Rev2Document1 pageVXL HK1N1920 01 Rev2Đạt HuỳnhNo ratings yet

- Nhóm 11 - Đ Án Chuyên Ngành - Tuan5Document3 pagesNhóm 11 - Đ Án Chuyên Ngành - Tuan5Đức MinhNo ratings yet

- 2021 2022 hk1 Final CQ 01Document6 pages2021 2022 hk1 Final CQ 01ngtrung72005No ratings yet

- đề thi tổ chứuc cấu trúc máy tính 4Document5 pagesđề thi tổ chứuc cấu trúc máy tính 4Đang Bùi KhánhNo ratings yet

- UEB - THCS2 - K2 - 22 - 23 - ĐỀ THI HẾT MÔN HỌC KÌDocument4 pagesUEB - THCS2 - K2 - 22 - 23 - ĐỀ THI HẾT MÔN HỌC KÌLy PhạmNo ratings yet

- KHHT Chuan Bi Vao HK Fall 2023Document47 pagesKHHT Chuan Bi Vao HK Fall 2023Esteem WilsonNo ratings yet

- KHHT - Chuan Bi Vao HK Spring 2023Document48 pagesKHHT - Chuan Bi Vao HK Spring 2023Nguyen Trung Kien (K18 HL)No ratings yet

- GTCKT CK 03Document2 pagesGTCKT CK 03Dũng VươngNo ratings yet

- De 1 KTS - 8 - 2021Document1 pageDe 1 KTS - 8 - 2021minhquangbvmiNo ratings yet

- De - Thi - DLDKBMT TD17 003 004Document2 pagesDe - Thi - DLDKBMT TD17 003 004Phan Quốc Nghĩa100% (1)

- ESD Cuoi Ky 2021 2022 HK1 CQ 21 12 2021Document3 pagesESD Cuoi Ky 2021 2022 HK1 CQ 21 12 2021Lillian TranNo ratings yet

- 002 VXLDocument1 page002 VXLDien NguyenNo ratings yet

- Logic-Kha-Trinh Dethi TKLG DTVT Thang01 Nam17 - (Cuuduongthancong - Com)Document3 pagesLogic-Kha-Trinh Dethi TKLG DTVT Thang01 Nam17 - (Cuuduongthancong - Com)Minh Phương NguyenNo ratings yet

- Ghép đề vxlDocument57 pagesGhép đề vxl22129029No ratings yet

- Nhóm 11 - Đ Án Chuyên Ngành - Tuan6Document3 pagesNhóm 11 - Đ Án Chuyên Ngành - Tuan6Đức MinhNo ratings yet

- VXL HK2NH2021 CK2OL S3 345 Rev1Document1 pageVXL HK2NH2021 CK2OL S3 345 Rev1Vo Hoang QuocNo ratings yet

- 001 VXLDocument1 page001 VXLDien NguyenNo ratings yet

- Nhóm 11 - Đ Án Chuyên Ngành - Tuan2Document3 pagesNhóm 11 - Đ Án Chuyên Ngành - Tuan2Đức MinhNo ratings yet

- Nhóm 11 - Đ Án Chuyên Ngành - Tuan1Document5 pagesNhóm 11 - Đ Án Chuyên Ngành - Tuan1Đức MinhNo ratings yet

- 2019Aug20-DeCuongHTMT-NNLT - 2019-07-22-Chi Tiet - UpdatedDocument12 pages2019Aug20-DeCuongHTMT-NNLT - 2019-07-22-Chi Tiet - UpdatedHuy HoàngNo ratings yet

- Đề thi KTS HK1 2019-2020 CLC - 21 - 12 - 2019Document2 pagesĐề thi KTS HK1 2019-2020 CLC - 21 - 12 - 2019Quang MinhNo ratings yet

- VXL-Cau 5-TVTDocument18 pagesVXL-Cau 5-TVTHauvuNo ratings yet

- AT15C3 - Hệ thống viễn thông - 06-8-2021Document2 pagesAT15C3 - Hệ thống viễn thông - 06-8-2021Dim DimNo ratings yet

- dethiKTVXL2021-CTTT Y SinhDocument2 pagesdethiKTVXL2021-CTTT Y SinhKhánh Ly TrịnhNo ratings yet

- De-Thi HTDKN HK1 1617Document1 pageDe-Thi HTDKN HK1 1617Phùng Tiến ĐạtNo ratings yet

- 26 - 10 - Ca3 - TOAN HOC TO HOP CAC LÓP 19CTT - LVHopDocument1 page26 - 10 - Ca3 - TOAN HOC TO HOP CAC LÓP 19CTT - LVHopOrianeNo ratings yet

- Aesd 2022 2023 HK2Document1 pageAesd 2022 2023 HK2TRƯỜNG NGUYỄN XUÂNNo ratings yet

- DTCN - LT10Document1 pageDTCN - LT10kyukyu01112002No ratings yet

- De So 01 2023Document2 pagesDe So 01 2023vansoncbvn11No ratings yet

- DTCN - LT15Document1 pageDTCN - LT15kyukyu01112002No ratings yet

- BaitapThuchanh WordDocument8 pagesBaitapThuchanh WordHiệuNo ratings yet

- DTCN - LT06Document1 pageDTCN - LT06kyukyu01112002No ratings yet

- DethivvvDocument60 pagesDethivvvPhương ĐôngNo ratings yet

- 004 VXLDocument1 page004 VXLDien NguyenNo ratings yet

- De 1 SPSSDocument1 pageDe 1 SPSShlpt2004No ratings yet

- FILE 20220424 135332 403036 LTĐKTĐ1 CK Ma-De-03Document2 pagesFILE 20220424 135332 403036 LTĐKTĐ1 CK Ma-De-03Đạt Ngô MinhNo ratings yet

- D16 2Document1 pageD16 2Uyên VươngNo ratings yet

- De Thi CAD-CAM Online 2021-De2Document1 pageDe Thi CAD-CAM Online 2021-De2Quyền VănNo ratings yet

- Đề và Đáp án 2016 - 2017 - HK 1Document4 pagesĐề và Đáp án 2016 - 2017 - HK 1Chí ChơnNo ratings yet

- DTCN 309 VXL Truong 05 2022 HK1 CLC CSL1Document2 pagesDTCN 309 VXL Truong 05 2022 HK1 CLC CSL1Đạt HuỳnhNo ratings yet

- Thi ĐKLG PLC - 20211Document10 pagesThi ĐKLG PLC - 20211Linh Chi NguyenNo ratings yet

- Cuối kỳ 223 - HTMTDocument5 pagesCuối kỳ 223 - HTMTdat.nguyenxuanNo ratings yet

- KT - QT01 03A de Thi 01Document1 pageKT - QT01 03A de Thi 01bquang11012003No ratings yet

- BM03.Mẫu bản mô tả kỹ thuật bài thường xuyên 1 03032021Document4 pagesBM03.Mẫu bản mô tả kỹ thuật bài thường xuyên 1 03032021Trí ThanhNo ratings yet

- De Thi VXLDocument2 pagesDe Thi VXLhoaithanh1309.idolNo ratings yet

- Bai 1Document14 pagesBai 1Phạm Đức HuyNo ratings yet

- Đề thi HTMT (TX) - Hk2-2022-2023 (Ngày thi 12-6-2023)Document5 pagesĐề thi HTMT (TX) - Hk2-2022-2023 (Ngày thi 12-6-2023)David Anthony MonkeyNo ratings yet

- VXL-HK2NH2021 2Document1 pageVXL-HK2NH2021 2Vo Hoang QuocNo ratings yet

- Kiem Tra TNTH d12vt FinalDocument5 pagesKiem Tra TNTH d12vt FinalHoang ThanNo ratings yet