Professional Documents

Culture Documents

Up7701 uPISemiconductor

Up7701 uPISemiconductor

Uploaded by

LEONOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Up7701 uPISemiconductor

Up7701 uPISemiconductor

Uploaded by

LEONCopyright:

Available Formats

uP7701

3A Ultra Low Dropout Linear Regulator

General Description Features

The uP7701 is a 3A ultra low dropout linear regulator Works with 1.0V~5.5V VIN

specifically designed for motherboard,notebook and graphic Adjustable Output Voltage, Down to 0.8V

card applications. This device works with dual supplies, a

1.5% Initial Accuracy

control input for the control circuitry and a power input as

low as 1.0V for providing current to output. The uP7701 Excellent Line and Load Regulation

delivers high-current and ultra-low-drop output voltage as 3A Guaranteed Output Current

low as 0.8V for applications where VOUT is very close to

300mV @ 3A Dropout Voltage

VIN.

Very Low On-Resistance

The uP7701 features comprehensive control and protection

functions: a power on reset (POR) circuit for monitoring Ω typical

100mΩ

both control and power inputs for proper operation; an EN VOUT Pull Low Resistance when Disabled

input for enabling or disabling the device, a power OK with Low Reverse Leakage (Output to Input )

time delay for indicating the output voltage status, a

VOUT Power OK Signal

foldback current limit function, and a thermal shutdown

function. Fast Transient Response

The uP7701 is available in PSOP-8 package with very low Low External Component Count

thermal resistance. Low Cost and Easy to Use

Enable Pin

Applications

Over Current and Over Temperature Protection

Desktop PCs, Notebooks, and Workstations

Graphic Cards Ordering Information

Low Voltage Logic Supplies

Order Number Package Type Remark

Microprocessor and Chipset Supplies

uP7701U8 PSOP-8

Split Plane Microprocessor Supplies

Advanced Graphics Cards Supplies Note: uPI products are compatible with the current IPC/

SoundCards and Auxiliary Power Supplies JEDEC J-STD-020 and RoHS requirements. They are 100%

matte tin (Sn) plating and suitable for use in SnPb or Pb-

SMPS Post Regulators

free soldering processes.

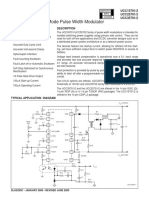

Pin Configuration & Typical Application Circuit

5VCC

R4 CNTL

10R

4

EN POK

2 1

POK 1 8 GND

R3

EN 2 7 FB 10K VOUT

VIN VIN VOUT

uP7701

GND 3 6

VIN 3 6 VOUT R2

12.5K C4

CNTL 4 5 NC C1 option

FB

1uF NC 5 7

uP7701 C3

C2 R1

8 10K 10uF

4.7uF

GND

uPI Semiconductor Corp., http://www.upi-semi.com 1

Rev. 00, 2007, April

uP7701

Functional Pin Description

Pin No. Name Pin Function

Pow er OK Indication. This pin is an open-drain output and is set high impedance once VOUT

1 POK

reaches 92% of its rating voltage.

Enable Input. Pulling this pin below 0.4V turns the regulator off, reducing the quiescent current

2 EN

to a fraction of its operating value.

Input Voltage. This is the drain input to the power device that supply current to the output pin.

Large bulk capacitors with low ESR should be placed physically close to this pin o prevent the

3 VIN input rail from dropping during large load transient. A 4.7uF ceramic capacitor is recommended

at this pin. VIN cannot be forced higher than VCNTL otherwise the current limit function may be false

triggered and disable the output voltage.

Supply Input for Control Circuit. This pin provides bias voltage to the control circuitry and

driver for the pass transistor.The driving capability of output current is proportioned to the VCNTL.

4 CNTL

For the device to regulate, the voltage on this pin must be at least 1.5V greater than the output

voltage, and no less than VCNTL_MIN.

5 NC Not Internally Connected

Output Voltage. This pin is power output of the device. A pull low resistance exists when the

device is disabled by pulling low the EN pin. To maintain adequate transient response to large

6 VOUT

load change, typical value of 1000uF Al electrolytic capacitor with 10uF ceramic capacitors are

recommended to reduce the effects of current transients on VOUT.

Feedback Voltage. This pin is the inverting input to the error amplifier. A resistor divider from

7 FB

the output to GND is used to set the regulation voltage as VOUT = 0.8x(R1+R2)/R1 (V)

8 GND Ground.

Exposed Ground. The exposed pad acts the dominant power dissipation path and should be soldered

GND

P ad to well design PCB pads as described in the Application Inform ations Chapter.

Functional Block Diagram

EN CNTL VIN

2 4 3

Power On

Thermal Limit

Reset

Softstart &

Current Limit

Control Logic

FB 7

0.8V

6 VOUT

Delay

92% VREF

1 8

POK GND

uPI Semiconductor Corp., http://www.upi-semi.com 2

Rev. 00, 2007, April

uP7701

Functional Description

Definitions Output Voltage Programming

Some important terminologies for LDO are specified below. Figure 1 shows a typical application of 2.5V to 1.8V

conversion with a 5.0V control supply. The output voltage

Dropout Voltage

is sensed through a voltage divider and regulated to internal

The input/output voltage differential at which the regulator reference voltage VREF. The output voltage is programmed

output no longer maintains regulation against further as:

reductions in input voltage. Measured when the output drops

VOUT = VREF x (R1+R2) / R1 = 0.8V x (22.5k/10k) = 1.8V

2% below its nominal value. Dropout voltage is affected by

junction temperature, load current and minimum input It’s recommended to maintain 50-100uA through the output

supply requirements. divider network for a tight load and line regulation. The

internal voltage reference is VREF = 0.8V with 1.5% initial

Line Regulation

accuracy. This commands the use of 0.5% or better

The change in output voltage for a change in input voltage. accuracy resistors to build a precision power supply.

The measurement is made under conditions of low

dissipation or by using pulse techniques such that average 5VCC

chip temperature is not significantly affected. R4 CNTL

10R

4

Load Regulation EN POK

2 1

The change in output voltage for a change in load current R3

10K VOUT

at constant chip temperature. The measurement is made VIN VIN VOUT

uP7701

3 6

under conditions of low dissipation or by using pulse R2

12.5K C4

techniques such that average chip temperature is not C1 FB

option

1uF NC 5 7

significantly affected. C2 R1 C3

8 10K 10uF

4.7uF

Maximum Power Dissipation GND

The maximum total device dissipation for which the

regulator will operate within specifications.

Figure 1. Typical application of 2.5V to 1.8V conversion

Quiescent Bias Current with a 5.0V control supply

Current which is used to operate the regulator chip and is Over Current Protection

not delivered to the load.

The uP7701 features a foldback over current protection

The quiescent current IQ is defined as the supply current function as shown in Figure 2. The current limit threshold

used by the regulator itself that does not pass into the level is proportinal to VOUT/VNOM and is typically 4A when

load. It typically includes all bias currents required by the VOUT = VNOM, where VNOM is the target output voltage. If the

LDO and any drive current for the pass transistor. output continuously demands more current than the

Initialization maximum current, output voltage will eventually drops below

its nominal value. This, in turns, will lower its OCP threshold

The uP7701 automatically initiates upon the receipt of level. This will limit power dissipation in the device when

supply voltage and power voltage. A power on reset circuit

over current limit happens. The power dissipation is near

continuously monitors VIN and CNTL pins voltages with

zero when the output is short circuited to ground.

rising threshold levels of 0.6V and 2.7V respectively.

Chip Enable and Soft Start

VNOM

Output Voltage (V)

The uP7701 features an enable pin for enable/disable

control of the chip. Pulling VEN lower than 0.8V disables

the chip and reduces its quiescent current down to 12uA. 1V

When disabled, an internal MOSFET of 90Ω RDS(ON) turns P

on to pull output voltage to ground. Pulling VEN higher than SC

1.6V enables the output voltage, providing POR is

1A 2A 3A 4A

recognized. The uP7701 features soft start function that

Output Current (A)

limits inrush current for charging the output capacitors. The

soft start time is typically 5ms.

Figure 2. Current Limit Behavior

uPI Semiconductor Corp., http://www.upi-semi.com 3

Rev. 00, 2007, April

uP7701

Absolute Maximum Rating

Control Input Voltage VCNTL (Note 1) ------------------------------------------------------------------------------------------------- -0.3V to +6V

Power Input Voltage VIN -------------------------------------------------------------------------------------------------------------------- -0.3V to +6V

Other Pins --------------------------------------------------------------------------------------------------------------- -0.3V to (VCNTL + 0.3V)

Storage Temperature Range ----------------------------------------------------------------------------------------------------------- -65OC to +150OC

Junction Temperature ------------------------------------------------------------------------------------------------------------------------------------ 150OC

Lead Temperature (Soldering, 10 sec) ------------------------------------------------------------------------------------------------------------ 260OC

ESD Rating (Note 2)

HBM (Human Body Mode) --------------------------------------------------------------------------------------------------------------------- 2kV

MM (Machine Mode) ----------------------------------------------------------------------------------------------------------------------------- 200V

Thermal Information

Package Thermal Resistance (Note 3)

PSOP-8 θJA ---------------------------------------------------------------------------------------------------------------------------------- 52°C/W

PSOP-8 θJC ---------------------------------------------------------------------------------------------------------------------------------- 15°C/W

Power Dissipation, PD @ TA = 25°C

PSOP-8 ------------------------------------------------------------------------------------------------------------------------------------------- 1.9W

Recommended Operation Conditions

Operating Junction Temperature Range (Note 4) ------------------------------------------------------------------------ -40°C to +125°C

Operating Ambient Temperature Range -------------------------------------------------------------------------------------- -40°C to +85°C

Supply Input Voltage, VCNTL ------------------------------------------------------------------------------------------------------------ +4.5V to +5.5V

Power Input Voltage, VIN ------------------------------------------------------------------------------------------------------------ +1.0V to VCNTL

Electrical Characteristics

(VCNTL = 5V, TA = 25OC, unless otherwise specified)

Parameter Symbol Test Conditions Min Typ Max Units

Supply Input Voltage

Control Input Voltage VCNTL VOUT = VREF 3.0 -- 5.5 V

POR Threshold VCNTLRTH -- 2.7 2.9 V

POR Hysteresis VCNTLHYS -- 0.2 -- V

Power Input Voltage VIN VOUT = VREF 1.0 -- VCNTL V

Control Input Current in

ICNTL_SD VCNTL = VIN = 5.0V, IOUT = 0A, VEN = 0V -- 20 40 uA

Shutdown

Control Input Current ICNTL VCNTL = VIN = VEN = 5.0V, IOUT = 0A, VOUT = VREF -- 1.0 1.5 mA

Quiescent Current IQ VCNTL = VIN = VEN = 5.0V, IOUT = 0A, VOUT = VREF -- 1.0 1.5 mA

Feedback Voltage

Reference Voltage VREF VCNTL = VIN = VEN = 5.0V, IOUT = 0A. VOUT = VREF 0.788 0.8 0.812 V

Feedback Input Current IFB -- 20 -- nA

1.0V < VIN < 5.0V, VCNTL = VEN = 5.0V, IOUT = 0A. VOUT =

VIN Line Regulation VREF(LINE) -- 0.1 0.3 %/V

VREF

VCNTL Line Regulation VREF(CNTL) 3.0V < VCNTL < 5.0V,VIN = 1.2V, IOUT = 0A. VOUT = VREF -- 0.1 0.3 %/V

Load Regulation VREF(LOAD) 0mA < IOUT < 3A, VCNTL = VIN = VEN = 5.0V, VOUT = VREF -- 0.5 1.0 %/A

Load Regulation over 0mA < IOUT < 2A, VCNTL = VIN = VEN = 5.0V, VOUT = VREF,

VREF(TOTAL) -- 1.0 2 %

Temperature -40OC < TJ < 125OC, by design

uPI Semiconductor Corp., http://www.upi-semi.com 4

Rev. 00, 2007, April

uP7701

Electrical Characteristics

Parameter Symbol Test Conditions Min Typ Max Units

Feedback Voltage (VREFIN = VCNTL)

On Resistance RDS(ON) IOUT = 100mA, VCNTL = VEN = 5.0V, VOUT = 1.6V -- 100 120 mΩ

IOUT = 2A, VCNTL = VEN = 5.0V, VOUT = 1.6V, by design -- 200 240

Dropout Voltage VDROP mV

IOUT = 3A, VCNTL = VEN = 5.0V, VOUT = 1.6V, by design 300 360

VOUT Pull Low Resistance VCNTL = VIN = 5.0V, VEN = 0V, by design -- 90 -- Ω

Enable

Enable High Level V EN -- -- 1.6 V

Disable Low Level V SD 0.4 -- -- V

EN Source Current IEN VEN = 0V, VCNTL = 5.0V -- 12 20 uA

EN Input Impedance ZEN -- 65 -- KΩ

PWROK

FB Power OK Threshold VPOKTH IOUT = 0A, VCNTL = VIN = VEN = 5.0V, VOUT = VREF -- 92 -- %

Power OK Hysteresis VPOKHYS IOUT = 0A, VCNTL = VIN = VEN = 5.0V, VOUT = VREF -- 8 -- %

POK Delay Time From VOUT > 92% VNOM to POK rising -- 1 -- ms

Overcurrent Protection

OCP Threshold Level IOCP VCNTL = VIN = VEN = 5.0V, VOUT = VREF 3.5 -- -- A

Output Short Circuit

ISC VCNTL = VIN = VEN = 5.0V, VOUT = 0V -- 100 -- mA

Current

Thermal Protection

Thermal Shutdown

TSD IOUT = 0A, VCNTL = VIN = VEN = 5.0V, VOUT = VREF -- 170 -- O

C

Temperature

Thermal Shutdown

TSDHYS IOUT = 0A, VCNTL = VIN = VEN = 5.0V, VOUT = VREF -- 30 -- O

C

Hysteresis

Note 1. Stresses listed as the above “Absolute Maximum Ratings” may cause permanent damage to the device.

These are for stress ratings. Functional operation of the device at these or any other conditions beyond those

indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum

rating conditions for extended periods may remain possibility to affect device reliability.

Note 2. Devices are ESD sensitive. Handling precaution recommended.

Note 3. θJA is measured in the natural convection at TA = 25°C on a low effective thermal conductivity test board of

JEDEC 51-3 thermal measurement standard.

Note 4. The device is not guaranteed to function outside its operating conditions.

uPI Semiconductor Corp., http://www.upi-semi.com 5

Rev. 00, 2007, April

uP7701

Typical Operation Characteristics

Power On from VIN Power On from VCNTL

V CNTL (2V/Div)

V IN (2V/Div)

V OUT (1V/Div) V OUT (1V/Div)

POK (5V/Div) POK (5V/Div)

I IN (1A/Div) I IN (1A/Div)

1ms/Div 1ms/Div

VCNTL =5V, VIN = 3.3V, COUT = 1000uF, No Load. VCNTL =5V, VIN = 3.3V, COUT = 1000uF, No Load.

Turn On from EN Dropout Voltage vs. Output Current

V EN (5V/Div)

300mV

Dropout Voltgae (mV)

V OUT (1V/Div)

200mV

POK (5V/Div)

100mV

IIN (1A/Div)

0mV

0A 1A 2A 3A

1ms/Div Output Current (A)

VCNTL =5V, VIN = 3.3V, COUT = 1000uF, No Load.

Output Short Circuit Ouput Voltage vs. Ouptut Current

Output Voltage Deviation (mV)

2V

Output Voltage (V)

1.5V

0A 1A 2A 3A

1V 0mV

0.5V 2mV

0V 4mV

0A 1A 2A 3A 4A 5A

Output Current (A) Output Current (A)

uPI Semiconductor Corp., http://www.upi-semi.com 6

Rev. 00, 2007, April

uP7701

Typical Operation Characteristics

Load Transient Response Quiescent Current vs. Input Voltage

1000

900

Quiescent Current (uA)

V OUT

(5mV/Div)

800

700

600

I OUT 500

(1A/Div)

400

25us/Div 2.5 3 3.5 4 4.5 5 5.5

COUT = 22uF/X5R Input Voltage VCNTL = VIN (V)

Shutdown Current vs. Input Voltage Line Regulation

30 0.81

25

Feedback Voltage VFB (V)

Shutdown Current (uA)

0.805

20

15 0.8

10

0.795

5

0 0.79

2.5 3 3.5 4 4.5 5 5.5 2.5 3 3.5 4 4.5 5 5.5

Input Voltage VCNTL = VIN (V) Input Voltage VCNTL = VIN (V)

Enable/Disable Threshold vs Input Voltage On Resistance vs. Input Voltage

1.4 140

1.3

Enable/Disable Threshold (V)

130

1.2

On Resistance (mΩ)

120

1.1

110

1

100

0.9

0.8 90

Disable

0.7 80

Enable

0.6 70

2.5 3 3.5 4 4.5 5 5.5 2.5 3 3.5 4 4.5 5 5.5

Input Voltage VCNTL = VIN (V) Input Voltage VCNTL = 5V, VOUT = 0.8V

uPI Semiconductor Corp., http://www.upi-semi.com 7

Rev. 00, 2007, April

uP7701

Typical Operation Characteristics

FB Voltage vs. Temperature On Resistance vs. Temperature

810 140

120

Feedback Voltage VFB (mV)

805

On Resistance (mΩ)

100

80

800

60

40

795

20

790 0

-50 -25 0 25 50 75 100 125 -50 -25 0 25 50 75 100 125

Junction Temperature (OC) Junction Temperature (OC)

VCNTL = 5V, VIN = VOUT + 1V VCNTL = 5V, VOUT = 1.6V

Quiescent Current vs. Temperature EN Source Current vs. Temperature

1400 30

1200 25

EN Pin Source Current (uA)

Quiescent Current (uA)

1000

20

800

15

600

10

400

200 5

0 0

-50 -25 0 25 50 75 100 125 -50 -25 0 25 50 75 100 125 150

Junction Temperature ( C)

O

Junction Temperature (OC)

VCNTL = VIN = 5V VCNTL = 5V

uPI Semiconductor Corp., http://www.upi-semi.com 8

Rev. 00, 2007, April

uP7701

Application Information

The uP7701 is a high performance linear regulator bulk capacitance on the rail. Additionally, bulk capacitance

specifically designed to deliver up to 3A output current with may be added closely to the input supply pin of the uP7701

very low input voltage and ultra low dropout voltage. With to ensure that VIN does not sag, improving load transient

dual-supply configuration, the uP7701 operates with a wide response.

input voltage VIN range from 1.0V to 5.5V and is ideal for Output capacitor: A minimum bulk capacitance of 10uF,

applications where VOUT is very close to VIN . along with a 0.1uF ceramic decoupling capacitor is

Supply Voltage for Control Circuit VCNTL recommended. Increasing the bulk capacitance will improve

Unlike other linear regulators that use a P-Channel the overall transient response. The use of multiple lower

MOSFET as the pass transistor, the uP7701 uses an N- value ceramic capacitors in parallel to achieve the desired

Channel as the pass transistor. N-Channel MOSFET bulk capacitance will not cause stability issues. Although

provides lower on-resistance and better stability meeting designed for use with ceramic output capacitors, the uP7701

stringent requirements of current generation is extremely tolerant of output capacitor ESR values and

microprocessors and other sensitive electronic devices. thus will also work comfortably with tantalum output

The drain of N-Channel MOSFET is connected to VIN and capacitors.

the source is connected to VOUT. This requires that the Thermal Consideration

supply voltage VCNTL for control circuit is at least 1.5V higher The uP7701 integrates internal thermal limiting function to

than the output voltage to provide enough overdrive capability protect the device from damage during fault conditions.

for the pass transistor thus to achieve low dropout and fast However, continuously keeping the junction near the thermal

transient response. It is highly recommended to bias the shutdown temperature may remain possibility to affect

device with 5V voltage source if available. device reliability. It is highly recommended to keep the

Use a minimum 0.1uF ceramic capacitor plus a 10Ω junction temperature below the recommended operation

resistor to locally bypass the control voltage. condition 125OC for maximum reliability.

Input/Output Capacitor Selection Power dissipation in the device is calculated as:

The uP7701 has a fast transient response that allows it to PD = (VIN - VOUT) x IOUT + VCNTL x ICNTL

handle large load changes associated with high current It is adequate to neglect power loss with respective to

applications. Proper selection of the of the output capacitor control circuit VCNTL x ICNTL when considering thermal

and it’s ESR value determines stable operation and management in uP7701 Take the following moderate

optimizes performance. The typical application circuit operation condition as an example: VIN = 2.5V, VOUT = 1.5V,

shown in Figure 1 was tested with a wide range of different IOUT = 2A, the power dissipation is:

capacitors. The circuit was found to be unconditionally

stable with capacitor values from 10uF to 2200uF and ESR PD = (1.8V- 1.2V) x 2A = 2.0W

ranging from 0.5mΩ to greater then 75mΩ. This power dissipation is conducted through the package

into the ambient environment, and, in the process, the

5VCC temperature of the die (TJ) rises above ambient. Large power

R4 CNTL dissipation may cause considerable temperature raise in

10R

4

EN POK the regulator in large dropout applications. The geometry

2 1

of the package and of the printed circuit board (PCB) greatly

R3

VIN VIN VOUT

10K VOUT influence how quickly the heat is transferred to the PCB

uP7701

3 6 and away from the chip. The most commonly used thermal

R2

12.5K C4

option

metrics for IC packages are thermal resistance from the

C1 FB

1uF NC 5 7 chip junction to the ambient air surrounding the package

R1 C3

C2

8 10K 10uF (θJA):

4.7uF

GND

θJA = ( TJ -TA ) / PD

θJA specified in the Thermal Information section is measured

Figure 1. Typical Application Circuit in the natural convection at TA = 25OC on a high effective

thermal conductivity test board (4 Layers, 2S2P) of JEDEC

Input capacitor: A minimum of 4.7uF ceramic capacitor 51-7 thermal measurement standard. The case point of

is recommended to be placed directly next to the VIN pin. θJC is on the exposed pad for PSOP-8 package.

This allows for the device being some distance from any

uPI Semiconductor Corp., http://www.upi-semi.com 9

Rev. 00, 2007, April

uP7701

Application Information

Given power dissipation PD, ambient temperature and

VOUT

thermal resistance θ JA, the junction temperature is

GND

NC

FB

calculated as:

TJ = TA + ∆TJA = TA + PD x θJA

8

7

6

5

To limit the junction temperature within its maximum rating,

uP7701

GND

the allowable maximum power dissipation is calculated

as:

1

2

3

4

PD(MAX) = ( TJ(MAX) -TA ) /θJA

where T J(MAX) is the maximum operation junction

VIN

POK

EN

CNTL

temperature 125OC, TA is the ambient temperature and the

θJA is the junction to ambient thermal resistance. θJA of

PSOP-8 packages is 75OC/W on JEDEC 51-7 (4 layers, Figure 4. Recommended PCB Layout.

2S2P) thermal test board with minimum copper area. The

maximum power dissipation at TA = 25OC can be calculated Layout Consideration

as: 1. Place a local bypass capacitor as closed as possible

PD(MAX) = (125 C - 25 C) / 75 C/W = 1.33W O O O to the VIN pin. Use short and wide traces to minimize

parasitic resistance and inductance.

The thermal resistance θJA highly depends on the PCB

design. Copper plane under the exposed pad is an effective 2. The exposed pad should be soldered on GND plane

heatsink and is useful for improving thermal conductivity. with maximum area and with multiple vias to inner layer

Figure 3 show the relationship between thermal resistance of ground place for improving thermal performance.

θJA vs. copper area on a standard JEDEC 51-7 (4 layers, 3. Connect voltage divider directly to the point where

2S2P) thermal test board at TA = 25OC. A 50mm2 copper regulation is required. Place voltage divider close to

plane reduces θJA from 75OC/W to 52OC/W and increases the device.

maximum power dissipation from 1.33W to 1.9W.

100

90

Thermal Resistance θ JA (OC/W)

80

70

60

50

40

30

0 10 20 30 40 50 60 70

Copper Area (mm2)

Figure 3. Thermal Resistance θJA vs. Copper Area

Figure 4 illustrated the recommended PCB layout for best

thermal performance.

uPI Semiconductor Corp., http://www.upi-semi.com 10

Rev. 00, 2007, April

uP7701

Application Information

0.76 REF

1.27 REF

4.80 - 5.00

2.29 BSC

1.85 REF

2.39 REF

5.80 - 6.20

3.80 - 4.00

2.29 BSC

6.15 REF

2.39 REF

8.00 MIN

4.00 MIN

1.27 BSC 0.32 - 0.52

Recommended Solder Pad Layout

1.45 - 1.60

0.20 BSC 0.18 - 0.25

0.10 - 0.25

0.41 - 0.89 1.75 MAX 3.81 BSC

Note

1.Package Outline Unit Description:

BSC: Basic. Represents theoretical exact dimension or dimension target

MIN: Minimum dimension specified.

MAX: Maximum dimension specified.

REF: Reference. Represents dimension for reference use only. This value is not a device specification.

TYP. Typical. Provided as a general value. This value is not a device specification.

2.Dimensions in Millimeters.

3.Drawing not to scale.

4.These dimensions no not include mold flash or protrusions. Mold flash or protrusions shell not exceed 0.15mm.

uPI Semiconductor Corp., http://www.upi-semi.com 11

Rev. 00, 2007, April

You might also like

- Report On PmuDocument15 pagesReport On PmuMohan Sainath AvvaruNo ratings yet

- Air Comperssor Test Rig ReciprocatingDocument4 pagesAir Comperssor Test Rig ReciprocatingShashank pNo ratings yet

- Design and Rating of Fired HeatersDocument33 pagesDesign and Rating of Fired HeatersRishabh Jain100% (1)

- Water Treatment Handbook UNITORDocument46 pagesWater Treatment Handbook UNITORplatastur100% (26)

- Up 7704Document13 pagesUp 7704Delwar HossainNo ratings yet

- uPI Confidential: 3A Ultra Low Dropout Linear RegulatorDocument13 pagesuPI Confidential: 3A Ultra Low Dropout Linear RegulatorLEONNo ratings yet

- Data SheetDocument15 pagesData Sheetzakie wahyuNo ratings yet

- Synchronous-Rectified Buck MOSFET Drivers: Features General DescriptionDocument5 pagesSynchronous-Rectified Buck MOSFET Drivers: Features General DescriptionTeles SilvaNo ratings yet

- UP1962SDocument14 pagesUP1962Stechgamebr85No ratings yet

- 5V/12V Synchronous Buck PWM DC-DC Controller: Features General DescriptionDocument17 pages5V/12V Synchronous Buck PWM DC-DC Controller: Features General DescriptionLuis Dark-passengerNo ratings yet

- U P6103Document15 pagesU P6103Selmar CavalcantiNo ratings yet

- 1707S uPISemiconductorDocument13 pages1707S uPISemiconductordulah kemprohNo ratings yet

- Up1605 uPISemiconductorDocument23 pagesUp1605 uPISemiconductorRBN HMNo ratings yet

- FR9888 FR9886 RT8296A RT8282 Step Down DC DC Converter Buck Ic Nguon Gan Giong Act 4523 PDFDocument11 pagesFR9888 FR9886 RT8296A RT8282 Step Down DC DC Converter Buck Ic Nguon Gan Giong Act 4523 PDFdinh vinh nguyenNo ratings yet

- AOZ2023PIDocument11 pagesAOZ2023PIjuliocunachiNo ratings yet

- uPI Semiconductor Up1735 Synchronous-Rectified Buck Converter DatasheetDocument13 pagesuPI Semiconductor Up1735 Synchronous-Rectified Buck Converter DatasheetSultan SinghNo ratings yet

- Complete DDR3/ DDR4 Memory Power Solution Controller: General Description FeaturesDocument15 pagesComplete DDR3/ DDR4 Memory Power Solution Controller: General Description FeaturesIgor LabutinNo ratings yet

- DATASHEET Up1542rDocument17 pagesDATASHEET Up1542rjoao doisssNo ratings yet

- 3A, 23V, 340Khz Synchronous Step-Down Converter: General Description FeaturesDocument12 pages3A, 23V, 340Khz Synchronous Step-Down Converter: General Description FeaturesAbdul MuhidNo ratings yet

- 3A, 1Mhz, Synchronous Step-Down Converter: General Description FeaturesDocument12 pages3A, 1Mhz, Synchronous Step-Down Converter: General Description FeatureskiryanoffNo ratings yet

- Ic rt9214Document17 pagesIc rt9214Franklin JimenezNo ratings yet

- APL5932A/B/C/D: Features General DescriptionDocument21 pagesAPL5932A/B/C/D: Features General DescriptionAku KudupiknikNo ratings yet

- 2A, 2Mhz, Synchronous Step-Down Regulator: General Description FeaturesDocument15 pages2A, 2Mhz, Synchronous Step-Down Regulator: General Description FeaturesPedrolaura BethencourtNo ratings yet

- FR9886Document12 pagesFR9886abrkNo ratings yet

- 5V/12V Synchronous-Rectified Buck Controller With Reference InputDocument19 pages5V/12V Synchronous-Rectified Buck Controller With Reference InputIgor LabutinNo ratings yet

- 3A Ultra Low Dropout Linear Regulator With Enable: GND FB V EN PG V V 8 7 6 5 1 2 3 4 VDocument14 pages3A Ultra Low Dropout Linear Regulator With Enable: GND FB V EN PG V V 8 7 6 5 1 2 3 4 VNuriyanto 3No ratings yet

- DS 2857FG 02 PDFDocument12 pagesDS 2857FG 02 PDFJohan GuanchezNo ratings yet

- Rt9008ge Apl5611aci-Trg Apl5611 9008ge 9008 La04 La12 La13 La14 La15 La16 La17 La0 La1Document9 pagesRt9008ge Apl5611aci-Trg Apl5611 9008ge 9008 La04 La12 La13 La14 La15 La16 La17 La0 La1laptophaianhNo ratings yet

- 3A, 23V, 340Khz Synchronous Step-Down Converter: General Description FeaturesDocument12 pages3A, 23V, 340Khz Synchronous Step-Down Converter: General Description FeaturesJuan Carlos SrafanNo ratings yet

- Datasheet AP7175Document14 pagesDatasheet AP7175Edwin SorianoNo ratings yet

- Apl5930 PDFDocument20 pagesApl5930 PDFanthony loboNo ratings yet

- 8T Rt5768aDocument12 pages8T Rt5768aVISHALNo ratings yet

- Single 12V Input Supply Dual Regulator - Synchronous-Buck-PWM and Linear-Regulator ControllerDocument15 pagesSingle 12V Input Supply Dual Regulator - Synchronous-Buck-PWM and Linear-Regulator ControllerBabei IlieNo ratings yet

- 5V/12V Synchronous Buck PWM DC-DC and Linear Power ControllerDocument18 pages5V/12V Synchronous Buck PWM DC-DC and Linear Power Controllerraed hasaniaNo ratings yet

- 1Mhz, 2.0A, High-Efficiency Synchronous-Rectified Buck ConverterDocument16 pages1Mhz, 2.0A, High-Efficiency Synchronous-Rectified Buck ConverterFuNn FFNo ratings yet

- LWNMNM : General Description FeaturesDocument16 pagesLWNMNM : General Description FeaturesSergio BarbozaNo ratings yet

- 300ma, Low Dropout, Low Noise Ultra-Fast Without Bypass Capacitor CMOS LDO RegulatorDocument11 pages300ma, Low Dropout, Low Noise Ultra-Fast Without Bypass Capacitor CMOS LDO RegulatordinhdtdNo ratings yet

- General Description Features: EzbuckDocument9 pagesGeneral Description Features: EzbuckCristina NistorNo ratings yet

- RT7296F 0.1Document96 pagesRT7296F 0.1Chiapin LeeNo ratings yet

- Single-Channel Power Distribution Switch: Description FeaturesDocument16 pagesSingle-Channel Power Distribution Switch: Description FeaturessandrolafaieteNo ratings yet

- Tps 65135Document28 pagesTps 65135Arthit SomrangNo ratings yet

- 3A, 23V, 340Khz Synchronous Step-Down Converter: General Description FeaturesDocument12 pages3A, 23V, 340Khz Synchronous Step-Down Converter: General Description FeaturesMarcius RodriguesNo ratings yet

- Features General Description: 3A, Ultra Low Dropout (0.23V Typical) Linear RegulatorDocument24 pagesFeatures General Description: 3A, Ultra Low Dropout (0.23V Typical) Linear RegulatorOdyem SadamNo ratings yet

- 3A, 2Mhz, Synchronous Step-Down Converter: General Description FeaturesDocument13 pages3A, 2Mhz, Synchronous Step-Down Converter: General Description FeaturesKavinda Jayasinghege DonNo ratings yet

- FAN7390 High-Current, High & Low-Side, Gate-Drive IC: Features DescriptionDocument14 pagesFAN7390 High-Current, High & Low-Side, Gate-Drive IC: Features DescriptionjoelpalzaNo ratings yet

- 2A, 23V, 340Khz Synchronous Step-Down Converter: General Description FeaturesDocument14 pages2A, 23V, 340Khz Synchronous Step-Down Converter: General Description FeaturesGioVoTamNo ratings yet

- Up 6201Document23 pagesUp 6201Babei IlieNo ratings yet

- DatasheetDocument12 pagesDatasheetWAN MOZESNo ratings yet

- Advanced Voltage Mode Pulse Width Modulator: Description FeaturesDocument24 pagesAdvanced Voltage Mode Pulse Width Modulator: Description Featuresvanhuong87No ratings yet

- RT8068AZQWDocument13 pagesRT8068AZQWTaller 62No ratings yet

- Ds8204a 05Document19 pagesDs8204a 05marcelo Chiu LeonNo ratings yet

- RT8057Document11 pagesRT8057antonio carlos clementino cruzNo ratings yet

- Datasheet - HK lp6253 8406861Document11 pagesDatasheet - HK lp6253 8406861Boban CvetkovicNo ratings yet

- Synchronous-Rectified Buck MOSFET Drivers: General Description FeaturesDocument11 pagesSynchronous-Rectified Buck MOSFET Drivers: General Description FeaturesDaniel Norberto DemariaNo ratings yet

- LWNMNP : General Description FeaturesDocument16 pagesLWNMNP : General Description FeaturesArturo ArmuellesNo ratings yet

- 500ma, Low Dropout, Low Noise Ultra-Fast Without Bypass Capacitor CMOS LDO RegulatorDocument13 pages500ma, Low Dropout, Low Noise Ultra-Fast Without Bypass Capacitor CMOS LDO RegulatoreugeneNo ratings yet

- A5268 3A, 28V, 340Khz Synchronous Rectified Step-Down ConverterDocument16 pagesA5268 3A, 28V, 340Khz Synchronous Rectified Step-Down ConverterAnderson Galarza CalderonNo ratings yet

- Off-Line Quasi-Resonant Switching Regulators: STR-Y6763, STR-Y6765, and STR-Y6766Document13 pagesOff-Line Quasi-Resonant Switching Regulators: STR-Y6763, STR-Y6765, and STR-Y6766Renato Luther escalanteNo ratings yet

- Slusck3 PDFDocument40 pagesSlusck3 PDFGlauco Borges BrumNo ratings yet

- UP6281 uPISemiconductorDocument10 pagesUP6281 uPISemiconductorВячеслав ЗагвоцкийNo ratings yet

- Tiny Microphone - Preamplifier: Components PlacementDocument1 pageTiny Microphone - Preamplifier: Components Placementedel camachoNo ratings yet

- R6870 Hawk R6870 Hawk: Feature SpecificationDocument1 pageR6870 Hawk R6870 Hawk: Feature SpecificationdejanNo ratings yet

- 775Twins-HDTV multiQIG PDFDocument129 pages775Twins-HDTV multiQIG PDFdejanNo ratings yet

- Guide To SATA Hard Disks Installation and RAID ConfigurationDocument22 pagesGuide To SATA Hard Disks Installation and RAID ConfigurationdejanNo ratings yet

- General Description Product Summery: Bvdss Rdson IDDocument4 pagesGeneral Description Product Summery: Bvdss Rdson IDdejanNo ratings yet

- AMD Radeon™ HD 6850/6870: User GuideDocument38 pagesAMD Radeon™ HD 6850/6870: User GuidedejanNo ratings yet

- Hobart 210 Ironman PDFDocument56 pagesHobart 210 Ironman PDFAlonso IbarraNo ratings yet

- General Industry Safety and Health Standard Part 18. Overhead and Gantry CranesDocument22 pagesGeneral Industry Safety and Health Standard Part 18. Overhead and Gantry CranesRubén Cabrera RojasNo ratings yet

- Surface Modifiers Technology and Benefits Brochure - 18-125570Document7 pagesSurface Modifiers Technology and Benefits Brochure - 18-125570zagNo ratings yet

- Primacs TOC Analyser: Chapter 2: Unpacking and InstallationDocument6 pagesPrimacs TOC Analyser: Chapter 2: Unpacking and InstallationAnonymous 2LYCWDPuiuNo ratings yet

- DiodeDocument22 pagesDiodeengineer.chiranjitNo ratings yet

- Hoppecke Solar Batteries For All ApplicationsDocument4 pagesHoppecke Solar Batteries For All ApplicationsAgitNo ratings yet

- Yeang 2022 Transparent Highcharge Capacity Met - Bi - CuDocument11 pagesYeang 2022 Transparent Highcharge Capacity Met - Bi - CuNikhil BhoumikNo ratings yet

- Applied Physics Polytechnic 2nd Sem Question PeparDocument2 pagesApplied Physics Polytechnic 2nd Sem Question PeparROBOTICS TECHNOLOGYNo ratings yet

- 2205020250-01 DWGDocument1 page2205020250-01 DWGJuan Carlos TolabaNo ratings yet

- Tutorial Sonnet eDocument26 pagesTutorial Sonnet eSomnath DasNo ratings yet

- 30-Jan-2020 2 and 4 Quadrant Choppers Chopper Control DrivesDocument26 pages30-Jan-2020 2 and 4 Quadrant Choppers Chopper Control DrivesATULYA ALOK 17BEE0065No ratings yet

- Inline Check Sieve: High-Quality End ProductsDocument2 pagesInline Check Sieve: High-Quality End ProductsGreere Oana-NicoletaNo ratings yet

- 199043energy Exergy AnalysisDocument157 pages199043energy Exergy AnalysisDuhan SidalNo ratings yet

- Industrial Diesel Generator Set - 50 HZ: KOHLER SDMO Premium QualityDocument7 pagesIndustrial Diesel Generator Set - 50 HZ: KOHLER SDMO Premium QualityJoanCarlesLLopysNo ratings yet

- Us Ss 33 Climates and Houses Around The World Powerpoint Ver 3Document12 pagesUs Ss 33 Climates and Houses Around The World Powerpoint Ver 3Carolina BianchiniNo ratings yet

- DR DRDocument14 pagesDR DRRahmat FNo ratings yet

- Load-Settlement Response of Rectangular and Circular Piles in Multilayered SoilDocument11 pagesLoad-Settlement Response of Rectangular and Circular Piles in Multilayered SoilrkNo ratings yet

- Technician GR - III Model PaperDocument10 pagesTechnician GR - III Model PaperJay patelNo ratings yet

- Thermaguard TIC 400 TDSDocument4 pagesThermaguard TIC 400 TDSJIMMY JAMESNo ratings yet

- Electron Beam WeldingDocument19 pagesElectron Beam WeldingSahil DhimanNo ratings yet

- 5070 s03 QP 4Document16 pages5070 s03 QP 4karan79No ratings yet

- Self Priming SPDocument2 pagesSelf Priming SPasdjhfkadhfNo ratings yet

- 6th Tips Physics SPM Success Tips Answer Paper 2Document7 pages6th Tips Physics SPM Success Tips Answer Paper 2Cikgu FaizalNo ratings yet

- Testo 205 Data SheetDocument2 pagesTesto 205 Data SheetjavierNo ratings yet

- Operating Manual: Electronic Current-Transducer With Analog Output STWA 2 AHDocument4 pagesOperating Manual: Electronic Current-Transducer With Analog Output STWA 2 AHAlbert KristianNo ratings yet