Professional Documents

Culture Documents

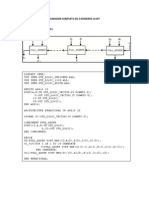

Multiplicador 4 Bits

Uploaded by

romel portugalOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Multiplicador 4 Bits

Uploaded by

romel portugalCopyright:

Available Formats

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity multiplicador4 is

port ( A: in STD_LOGIC_VECTOR (3 downto 0);

B: in STD_LOGIC_VECTOR (3 downto 0);

P: out STD_LOGIC_VECTOR (7 downto 0));

end multiplicador4;

architecture Behavioral of multiplicador4 is

-- Declaración del componente Sumador Completo

component sumcompl

port ( A: in STD_LOGIC;

B: in STD_LOGIC;

Cin: in STD_LOGIC;

Cout: out STD_LOGIC;

S: out STD_LOGIC);

end component;

-- Declaración intermedia

signal AB0,AB1,AB2,AB3: STD_LOGIC_VECTOR (7 downto 0);

signal C1 : STD_LOGIC_VECTOR (1 downto 0);

signal P1: STD_LOGIC_VECTOR (1 downto 0);

begin

-- Multiplier input

AB0(0) <= A(0) and B(0); -- Primera fila del producto

AB0(0) <= A(1) and B(0);

AB1(0) <= A(0) and B(1); -- Segunda fila del producto

AB1(1) <= A(1) and B(1);

AB2(0) <= A(0) and B(0); -- Primera fila del producto

AB2(0) <= A(1) and B(0);

AB3(0) <= A(0) and B(1); -- Segunda fila del producto

AB3(1) <= A(1) and B(1);

-- Port Mapping Full Adder 8 times and Half Adder 4 times

FA1: sumcompl port map(AB0(1), AB1(0), '0', C1(0), P1(0));

FA2: sumcompl port map(AB1(1), '0', C1(0), C1(1), P1(1));

FA3: sumcompl port map(AB2(1), AB3(0), '0', C1(0), P1(0));

FA4: sumcompl port map(AB3(1), '0', C1(0), C1(1), P1(1));

-- Mulitplier output

P(0)<= AB0(0);

P(1)<= P1(0);

P(2)<= P1(1);

P(3)<= C1(1);

end Behavioral;

You might also like

- VHDL CodeDocument34 pagesVHDL CodeHimanshu Thakur100% (1)

- Verilog CodeDocument85 pagesVerilog Codeappuamreddy75% (8)

- VHDL KeypadDocument17 pagesVHDL Keypadtroid426No ratings yet

- VHDL Code For Booth MultiplierDocument4 pagesVHDL Code For Booth MultiplierSwati Sharma100% (1)

- Project 1 Carry Look Ahead AdderDocument8 pagesProject 1 Carry Look Ahead AdderMansi JaisinghNo ratings yet

- Library IEEE Use IEEE - STD - LOGIC - 1164.ALL Use Ieee - STD - Logic - Unsigned - All Use Ieee - STD - Logic - Arith - AllDocument4 pagesLibrary IEEE Use IEEE - STD - LOGIC - 1164.ALL Use Ieee - STD - Logic - Unsigned - All Use Ieee - STD - Logic - Arith - AllLeydycita HemofixNo ratings yet

- Ee529 Lab Asg4Document10 pagesEe529 Lab Asg4dd23015No ratings yet

- VHDL CodesDocument9 pagesVHDL CodesIndunil Ruwan Kumara SeneviratneNo ratings yet

- VhdlfileDocument7 pagesVhdlfileNaveen NegiNo ratings yet

- 4 Bit Ripple Carry Adder VHDL CodeDocument5 pages4 Bit Ripple Carry Adder VHDL CodeSwifty SpotNo ratings yet

- DSD Lab ReportDocument70 pagesDSD Lab ReportJinesh KbNo ratings yet

- Ejemplo Con Procedure: Archivo de TestbenchDocument2 pagesEjemplo Con Procedure: Archivo de TestbenchrolandoNo ratings yet

- Ejemplo Procedure PDFDocument2 pagesEjemplo Procedure PDFrolandoNo ratings yet

- Sumador 16 BitDocument2 pagesSumador 16 BitPercy Julio Chambi PaccoNo ratings yet

- Library IEEE Use IEEE - STD - LOGIC - 1164.ALLDocument4 pagesLibrary IEEE Use IEEE - STD - LOGIC - 1164.ALLJaspreet KaurNo ratings yet

- AIM: - Write A VHDL Code For 4 Bit Ripple Carry Adder Using Loop Statement. CodeDocument4 pagesAIM: - Write A VHDL Code For 4 Bit Ripple Carry Adder Using Loop Statement. CodePrashant PathakNo ratings yet

- Ecad & Vlsi Lab ManualDocument28 pagesEcad & Vlsi Lab ManualSharath Kumar S SNo ratings yet

- EXP4Document9 pagesEXP4Rohan__MakwanaNo ratings yet

- Fdlca 5.1Document4 pagesFdlca 5.1Ankit BhardwajNo ratings yet

- Coding:: VHDL Code For BufferDocument27 pagesCoding:: VHDL Code For BufferAar Kay GautamNo ratings yet

- N Bit Adder: VHDL CodeDocument3 pagesN Bit Adder: VHDL Codeabhay kumarNo ratings yet

- Digital Design Lab (Ec661) Experiment N0.:1: Brief Description of WorkDocument63 pagesDigital Design Lab (Ec661) Experiment N0.:1: Brief Description of WorkBhaskar KNo ratings yet

- Assignment 1: 8 Bit Ring CounterDocument12 pagesAssignment 1: 8 Bit Ring CounterAarohi VoraNo ratings yet

- CAS 8 CodeDocument3 pagesCAS 8 Codebhslegion1498No ratings yet

- Previamente Se Realiza El Codigo VHDL para Un Sumador CompletoDocument18 pagesPreviamente Se Realiza El Codigo VHDL para Un Sumador CompletophoenyxoscuroNo ratings yet

- Multiplicacion Sumas Sucesivas Factores de 4 BitsDocument4 pagesMultiplicacion Sumas Sucesivas Factores de 4 BitsRoberto Carlos QuispeNo ratings yet

- VHDL Prei Nforme 4Document19 pagesVHDL Prei Nforme 4R Patty FloresNo ratings yet

- VHDLDocument6 pagesVHDLsachinpnNo ratings yet

- VHDL Sample PtogramsDocument40 pagesVHDL Sample PtogramsShanmuga PriyaNo ratings yet

- DISEÑODocument1 pageDISEÑOJose Montiel PulidoNo ratings yet

- Sol Ex010 11-Sã©rie2Document6 pagesSol Ex010 11-Sã©rie2cncr87kffkNo ratings yet

- 06 Verilog SynthDocument41 pages06 Verilog SynthAlexandru OleinicNo ratings yet

- Library IEEEDocument4 pagesLibrary IEEEAdeel HanifNo ratings yet

- Register File Using VHDLDocument15 pagesRegister File Using VHDLSumeet SauravNo ratings yet

- DSD LabDocument42 pagesDSD LabArun GoyalNo ratings yet

- Adsd Lab Experiments: NAME: Ankit Mukherjee REG NO: RA1911043040015 Class: Ece B'Document29 pagesAdsd Lab Experiments: NAME: Ankit Mukherjee REG NO: RA1911043040015 Class: Ece B'AnkitShubhoeMukherjeeNo ratings yet

- ENCS 533 Advanced Digital Design: Introduction To VHDLDocument51 pagesENCS 533 Advanced Digital Design: Introduction To VHDLLalush AbujaishNo ratings yet

- Engr2015 Lab2Document13 pagesEngr2015 Lab2SUPER AMAZINGNo ratings yet

- Verilog Behavioral Program For Counters: Up Counter (4 Bit)Document17 pagesVerilog Behavioral Program For Counters: Up Counter (4 Bit)Sainadh YerrapragadaNo ratings yet

- BCD Sumador de 1 Dígito: Library Use All Use All Entity Is Port in Downto in Out Downto Out End Architecture of IsDocument3 pagesBCD Sumador de 1 Dígito: Library Use All Use All Entity Is Port in Downto in Out Downto Out End Architecture of IsCristian Fabian Romero RojasNo ratings yet

- UNIT-3: Design Combinational CKT Using Architecture ModelDocument36 pagesUNIT-3: Design Combinational CKT Using Architecture Modelankit_4382No ratings yet

- VHDL SynthesisDocument91 pagesVHDL SynthesisFennil KinsperNo ratings yet

- LAB 7 Introduction To C ProgrammingDocument29 pagesLAB 7 Introduction To C ProgrammingHamza NasirNo ratings yet

- Structural LabDocument69 pagesStructural LabNABIRASOOLNo ratings yet

- VHDL Lab FileDocument48 pagesVHDL Lab FileAnkit Gupta100% (1)

- 4 Bit Full AdderDocument5 pages4 Bit Full AdderVinay YadavNo ratings yet

- Verilog Programs 5th UnitDocument14 pagesVerilog Programs 5th UnitVenkat ChadalavadaNo ratings yet

- Sumador BCD CodigoDocument1 pageSumador BCD Codigojjimenezmolina00No ratings yet

- Correction VHDL ExercicesDocument10 pagesCorrection VHDL ExercicesHazem HaNo ratings yet

- MohamedSamir AssignmentDocument45 pagesMohamedSamir Assignmentmohamed samierNo ratings yet

- TD 3 VHDL CorrectionDocument4 pagesTD 3 VHDL Correctionbenazizaaya8No ratings yet

- Código VHDL: Entity Port in in In: in Out Out Out EndDocument4 pagesCódigo VHDL: Entity Port in in In: in Out Out Out EndCesar Quintero AnzolaNo ratings yet

- CA PracticalDocument11 pagesCA PracticalBidhan BaraiNo ratings yet

- Verilog Present 2Document25 pagesVerilog Present 2markloopNo ratings yet

- Wa0000.Document35 pagesWa0000.KARTAVYANo ratings yet

- VHDLDocument13 pagesVHDLSrijeeta SenNo ratings yet

- Expt No: 7a Date:19.3.2015 Led Interfacing AimDocument36 pagesExpt No: 7a Date:19.3.2015 Led Interfacing AimbcemailidNo ratings yet

- FPGA Summer ReportDocument18 pagesFPGA Summer ReportAbhishek RajNo ratings yet