Professional Documents

Culture Documents

Paper Code Paper Title Batch (Optional) Calculator Required (Yes/No) Any Other Document To Be Used by Student (Yes / No)

Uploaded by

lalit saini0 ratings0% found this document useful (0 votes)

1 views4 pagesThis document provides a format for an MCQ paper on the topic of computer architecture. It includes:

1. Paper details like code, title, and whether a calculator is required

2. A table with 13 multiple choice questions about computer architecture topics like memory organization, CPU operations, and addressing modes

3. The questions are numbered and include the question text and multiple answer options

Original Description:

Original Title

2020

Copyright

© © All Rights Reserved

Available Formats

XLSX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThis document provides a format for an MCQ paper on the topic of computer architecture. It includes:

1. Paper details like code, title, and whether a calculator is required

2. A table with 13 multiple choice questions about computer architecture topics like memory organization, CPU operations, and addressing modes

3. The questions are numbered and include the question text and multiple answer options

Copyright:

© All Rights Reserved

Available Formats

Download as XLSX, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

1 views4 pagesPaper Code Paper Title Batch (Optional) Calculator Required (Yes/No) Any Other Document To Be Used by Student (Yes / No)

Uploaded by

lalit sainiThis document provides a format for an MCQ paper on the topic of computer architecture. It includes:

1. Paper details like code, title, and whether a calculator is required

2. A table with 13 multiple choice questions about computer architecture topics like memory organization, CPU operations, and addressing modes

3. The questions are numbered and include the question text and multiple answer options

Copyright:

© All Rights Reserved

Available Formats

Download as XLSX, PDF, TXT or read online from Scribd

You are on page 1of 4

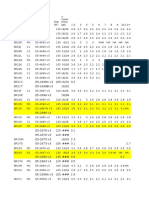

Format for MCQ Paper

1 Paper Code BCA 203

2 Paper Title Computer architecture

3 Batch (optional)

4 Calculator required (Yes/No) No

5 Any other document to be NO

If yes,by

used details of Documents

student (Yes / No)

Question Question Text Answer Answer Option Answer Answer

S.No.

1 .__________ mapping is used in Set Option 1 (A) Direct2 (B) Option 3

Sequential Option 4 (D)

Associative

2 cache

The organisationinwhich

configuration, whichisno the associative

Memory unit Memory- Memory(C) Memory unit

3 quickest

difference

After and

fetching most

between supple

memory and

the instruction from Instruction mapped I/O

program address

Instruction Accumulator

4 organisation.

I/O devices

the

When memory,

an interruptistheseen binary by the

occurs, code CPU,

which of is pointer

Execution of counter register

Execution of Execution Execution of

5 referred

the instruction

one

Which of onetheto following

as

of the ________

is stored takes

following in place?

which

most the current

To perform To the store

current of the

To perform the generate

To current

6 one

Write ofthrough

correctly thedescribes

following?

technique the is used in arithmetic instruction

virtual memory is program

instruction

main memory is current

logic

auxiliary instruction

control

cache is

signals

memory

7 functionality

which

The memory

load of the

instruction control

for updating is mostly unit

the in a completed

used Accumulator aborted

operations instructions

Instruction and its instruction

operations

memory

Program aborted

based onand

Memory

8 CPU?

data

to

An designate

instructiona pipeline transfer can frombe based on

LIFO buffer register

FIFO buffer based

Stack on

counter decoded

address

None of the

9 memory

implemented

A to a processor

combinational by means

logic circuit register

of which Decoder Encoder Multiplexer register

above

Demultiplexer

10 known

sends

In which asaddressing

data coming from mode a single

the Implied Immediate Indirect Direct

11 source

operand toistwo

Stack organised given or more

explicitly

computer separatein

has the Three address Two address One Zero address

12 destination

instruction

A program counter is calledcontains a instruction

850 instruction

824 address

825 instruction

849

13 number

A page fault 825 and Occurs the address part When there is When a instruction

When a When a

14 of the instruction

Virtual memory iscontained the an error in a An

Extremely program

Illusionaccess program

of an A type of program

All of These

15 number

Which of24, thethe effective

following addressis Memory

registers specific page Memory

large a page ofdata

extremely main accesses a

large Instruction

memory Access a page

Program

16 used

A to keep

digital computer track has of address

a common secondary

of address

16,32 memory

register

32,16 page

used

32,32innot

register belonging

Counter

16,16 to

17 the 8memory

bus

An system

bit register location

for 16 register

contains where theofthe32 memory

register

1001110 11001110 supercomp

00111000 00011000

18 next

bits

binary

A instruction

each.value

computer The uses is alocated

bus

10011100. is constructed

memory What unitis 7,16,8 6,6,18 7,8,16 7,6,18

19 with

The multiplexers.

the register

256K words

reverse value

polish of_______Number

after32 bits

notation an each of the. +AB**C+DE+F AB+CDE+*F+* ABDE+ ABCDEF++*+*

20 arithmetic

a binary

A bus organized shift right?

instruction

expression(A+B)*[C*(D+E)+F] CPU code hasis32 storedis 16,32,4X16 32,16,4X16 +C*f+*

16,16,16X4 32,32,16X4

21 in

A one

register word

computer withhas of

16memory.The

bits

32-bit in each,an

instructions 250 24576 500 25000

22 ALU,and

and

A non bitaaddresses.

12pipeline destination

system Iftakes there50 are ns 4 4.76 5 None of these

23 decoder.______

250

to

the two address

process

binary a task.multiplexers

division instructions,

The same task

of 0111000000 how Giving

are 11010 11101 00110 11001

many programming

24 can

by

A beone

10001

computer address

processed

givesemploys ininstructions

quotient aRAMsix segment

chips of 8,16 16,16

versatility to The interrupting 32,8The branch 32,16

25 pipeline

256X8isand

What withROM

the maina clockchips

purpose cycle ofofthe

of 1024 10X Address Large

the user by sourcestorage

supplies Reduce

address theis Provides

26 8.The computer

memory

__________ managementoccur system when needs

unit? an 2k translationData hazards

providing Control

the hazards

branch size

Structural

obtained addressinspace

Hazard

27 bytes

instruction

SIMD of RAM depends

represents andan 4K on bytes

the result

organization of Refers to

facilities asa Represents to from

information hazards

Includes

a pipeline

none of the

28 of a ,previous

that

The processor

amount ofinstruction

time and in

unit required a a way to computer

The timeto

pointers organization

it’s the

The time it of register

processor manytimeinit

The aboveof the

none

29 that

memory

read

How ismany

a exposed

unit.

block of(D)

address bynone

data the from

lines overlapping

of are

the

a disk system

takes

8

memory single

for the through

takes

10 computer

for the

an processing

takes

the

11 for above

12

30 above.

into

In a memory

needed Ans:

vectored C

to addressisinterrupt.

composed each memory of seek capableplatter

counters

The toof

branch for containing a

read-writevector

interrupt head units under

the platter

processor none of the

31 time,

locations

Computers rotational

in use

a 2048 latency, x 4 memory

addressing andmode make loop

address a full

control

is to

Tomove

reduce into

no. to rotate

Specifying above

All the above

32 chip?

techniques for executes only the Complex

1.__________ assigned to a Reduced

of bits in the rules for

Reduced Very long

33 _____________________.

instructions

1._____ is athat are commonly

register that fixed

Memory location

instruction field of Buffer

set Memory

instruction modifying

set Memory

instruction instruction

Instruction

34 used

In theinlate

temporarily programs

storeswe

1970s, and thus,that

theobserved

data makes computer

is Main-frame

the Address instruction

computer

Register,

Supercomputer or

set

Address

Microcomp word (VLIW),

Register,

Processors,

35 the processor

to be written

emerging

Consider in simpler.

the memory

of ___________

the following 2. or the 1-

that

statements (CISC),

Register,

computers,

True, 2- Very (RISC),

Memory

s,

1- Main-frame

False, 2- computer

Register,

uters,

1- True, 2- Reduced

Memory

Microprocesso

1- False, 2-

36 data

with

Consider received

wererespect

high-performance from

thetofollowing the

data hazards: memory.

computers

statements 2.

1. In 1-Instruction

Microcompute

True

True, 2- Address

computers

True

1- False, 2- Memory

Supercomp

False

1- False, 2- Address

rs True, 2-

False

1-

37 for

The scientific

pipelining,

with respect

address the computing.

toofcontrol

a pagehazards

instructions 2. In

table forin rs

True

Stack pointer Page False table base uters

True

Page False

Program counter

38 arise

control

memory

Which whenflow: the

1. In

is pointed

registers sequence

a by

can program

interact of with MAR register

PC register

IR R0

39 control

theasecondary

In type

program using of instruction,

storage? subroutine call Initialise Clear the Reset the Clear the

40 ifinstruction

the main itmemory is necessary is of 8k tobytes program 11bits accumulator

21bits microproce

16bits instruction

20bits

41 and the

when cacheismemory

a CPU executing is aof 2K counter mode System mode ssor

Interrupt Half mode register.

Simplex mode

42 words

program

The it uses

that is

multiplicand associative

part

register of theand mapping the (812)10 (12)10 (-12)10 (-812)10

43 then

Agingeach

operating

multiplier word are

system

register

registers ofof

itcache

isa said memory

hardware to be in Registers Counters which Counters to Counters to

44 circuit implementing

During the executionBooth of a program which MDR keep indicate

IR how keep

PC track keep

MAR track of

45 algorithm

which gets

______ is have 11101

initialized

used to choose and?1100

first track of When long

Conditional ago their of

Multiplexer last unit

Control latest of

None Datathe

46 between

Microprogram incrementing sequencer the PC or the codesprogram

Generate the associated

Generate the accessed

Sequentiall Structure

F13

Enables the

performing ALU operations. address of the control signal to y averages efficient

next micro execute a micro all micro handling of

instruction to instruction instruction microprogram

When a device raises a vectored

interrupt, the CPU does polling to

identify the source of the interrupt.

III. In polling, the CPU periodically

checks the status bits to know if

47 A K device

any bit fieldneedscan specify any oneIV.of (k)2

its attention. (k)3 (2)k (3)k

48 An interface

During DMA,that bothprovide

the CPU input

and- DDA Serial transfer BR DMA

49 output

The 2’s

DMA transfer

complement

controller of

candata directly

beform

bus of the to 111100 110110 110111 1011

50 and

The from

number

masters atthe

1010(

maximum thememory

in

addressing

same unit and

6 bittime.

word )is

capacity

Which 64K 4GB Both a and none of these

51 peripheral

of a

the above is

microprocessor termed

statementsas

Comparing the time T1 taken for16

which uses

is/are a T1<=T2 T1>=T2 b

T1<T2 T1 is T2 plus

52 bit datainstruction

TRUE?

single bus and 32 onBit

a address I and IV only I and II only III only the

I andtime taken

III only

53 bus

Which is of the

pipelined CPU with time

following is T2

used taken

as Accumulator Register Adder for one

Decoder

54 on a non-pipelined

storage

A processor locationshas 40 but

both in the ALU

distinct 24 32 40 instruction

16

55 and

The the

instructions control

following and section

are 24 of

general

some a

events QPTRS PRTSQ QRSTP PSTRQ

56 computer

purpose

that occur ?

registers.

after a A 32-bit

device

______ are used to over come the Speedcontroller Bridge circuits Multiple Buffer registers

57 instruction

issues

difference

The main word

an virtue

interrupt

in datahas an opcode,

while

transfer

for using process

speedsL Fast

single enhancing

data Buses

Cost effective Cost None of These

58 is under

of

Bus

An 24 bitexecution.(P)The

various

structuredevices.

address is_________

generates an circuitory

transfers

1024 connectivity

4096 and effective

2 ^ 48 16,777,216

59 address

If a system space is 64ofbit

______

machine , then 4 bytes speed

8 bytes connectivity

16 bytes 12 bytes

60 locations

the

Physical . of eachisword

lengthmemory will into

divided be Frames Pages and ease of

Blocks Vectors

____of. finite size called as ______

sets

Total

.

per

Correct Answer Option Image Maximum

(A/B/C/D)

D Marks1(Each

B Question)

1

C 1

B 1

D 1

D 1

A 1

B 1

D 1

B 1

D 1

A 1

C 1

D 1

D 1

A 2

B 2

D 2

B 2

B 2

B 2

B 2

A 2

C 2

A 1

A 1

C 1

A 1

C 1

C 1

D 1

B 1

C 1

B 1

B 1

D 1

B 1

A 1

D 1

C 1

B 1

A 2

B 1

C 1

B 1

A 1

C 1

D 1

B 2

B 2

B 1

D 1

B 1

D 2

A 1

D 1

C 1

D 2

B 2

A 1

75

You might also like

- 8051 BasicsDocument22 pages8051 BasicsviswapraveenNo ratings yet

- Rexesas RX MCUs PDFDocument59 pagesRexesas RX MCUs PDFAbdelhadi SdedekeNo ratings yet

- Cyber Crime ClassDocument32 pagesCyber Crime Classlalit sainiNo ratings yet

- English For IT StudentsDocument6 pagesEnglish For IT StudentsAnastasia KovalovaNo ratings yet

- Functional BLK Diagram 8085Document3 pagesFunctional BLK Diagram 8085Clash JNo ratings yet

- Computer Arch. & Organization - I: The Basic Organization of ComputersDocument33 pagesComputer Arch. & Organization - I: The Basic Organization of Computerssaksham0506No ratings yet

- Comp SciiDocument94 pagesComp Sciiumar568No ratings yet

- Diab Computer 3Document41 pagesDiab Computer 3RadNo ratings yet

- Week 2 LabDocument6 pagesWeek 2 LabTitan ThanosNo ratings yet

- CTMT Chap 07.processor Structure and FunctionDocument38 pagesCTMT Chap 07.processor Structure and FunctionTrần Đình Minh KhoaNo ratings yet

- Microprocessor Based Systems: Lecture No 03 Introduction To Von Neumann ArchitectureDocument32 pagesMicroprocessor Based Systems: Lecture No 03 Introduction To Von Neumann ArchitectureMuhammad ZubairNo ratings yet

- Direct Addressing Gives The Address of The Address of The Data in TheDocument5 pagesDirect Addressing Gives The Address of The Address of The Data in TheBryan PabloNo ratings yet

- How Microprocessors Work: Control Unit DCU (Data Cache Unit) Prefetch UnitDocument2 pagesHow Microprocessors Work: Control Unit DCU (Data Cache Unit) Prefetch UnitAhmad FairuzNo ratings yet

- 1.3.2 Computer Architecture and The Fetch-Execute Cycle PDFDocument4 pages1.3.2 Computer Architecture and The Fetch-Execute Cycle PDFAhmed HassanNo ratings yet

- 1.3.2 Computer Architecture and The Fetch-Execute CycleDocument4 pages1.3.2 Computer Architecture and The Fetch-Execute CycleZulkarnainNo ratings yet

- Sec 1.3.2 Computer Architecture & Fetch Execute Cycle: Computer Science 2210 With Majid TahirDocument9 pagesSec 1.3.2 Computer Architecture & Fetch Execute Cycle: Computer Science 2210 With Majid TahirFiyazul HaqueNo ratings yet

- Embedded Lab2Document26 pagesEmbedded Lab2Saddam AbdullahNo ratings yet

- 2.3 Processor and Memory 2.4 Peripherals 2.5 Storage Devices 2.6 Putting Together The Hardware Components 2.7 Improving Computer PerformanceDocument46 pages2.3 Processor and Memory 2.4 Peripherals 2.5 Storage Devices 2.6 Putting Together The Hardware Components 2.7 Improving Computer PerformanceSammy ModecaiNo ratings yet

- S23U14438 - Lecture 19 - Buffer OverflowDocument34 pagesS23U14438 - Lecture 19 - Buffer Overflowsara hashemiNo ratings yet

- CH03-COA10e ComputerFunctionDocument20 pagesCH03-COA10e ComputerFunctionthuan phamNo ratings yet

- CSC 403 Lecture 2Document16 pagesCSC 403 Lecture 2koredekayode2023No ratings yet

- CSC 222: Computer Organization: & Assembly LanguageDocument22 pagesCSC 222: Computer Organization: & Assembly Languageذیشان چودھریNo ratings yet

- C4 - Central Processing UnitDocument22 pagesC4 - Central Processing UnitMuhamad Nurhafiz YusoffNo ratings yet

- Computer Architecture...Document8 pagesComputer Architecture...abdul.mannan.bcs.24No ratings yet

- Sheetocheat Computer Architecture - BWDocument1 pageSheetocheat Computer Architecture - BWAadilNo ratings yet

- Discovering Computers 2008: The Components of The System UnitDocument53 pagesDiscovering Computers 2008: The Components of The System Unitapi-26417140100% (1)

- Ciclo de Búsqueda y Ejecución StallingDocument7 pagesCiclo de Búsqueda y Ejecución StallingMatias BeneitezNo ratings yet

- 2019 2020 CSE206 Week04 Ch3 Computer SystemsDocument46 pages2019 2020 CSE206 Week04 Ch3 Computer Systemstemhem racuNo ratings yet

- Memory Arbitration and Cache Management in Stream-Based SystemsDocument6 pagesMemory Arbitration and Cache Management in Stream-Based SystemsalekhyakushikNo ratings yet

- A B) Von Neumann ArchitectureDocument13 pagesA B) Von Neumann Architecturepira30No ratings yet

- Parallel Processing Chapter 1 2024Document22 pagesParallel Processing Chapter 1 2024Just SomeoneNo ratings yet

- Computer Organization & Computer Organization & Computer Organization & Computer Organization & Assembly Languages Assembly LanguagesDocument119 pagesComputer Organization & Computer Organization & Computer Organization & Computer Organization & Assembly Languages Assembly LanguagesEdel Karlo Sibidal ZarasateNo ratings yet

- Programmer Competency Matrix - Sijin JosephDocument8 pagesProgrammer Competency Matrix - Sijin JosephkikiNo ratings yet

- Different Types of Operating SystemsDocument8 pagesDifferent Types of Operating SystemsMahesh AbnaveNo ratings yet

- Juj 103 - Literasi KomputerDocument8 pagesJuj 103 - Literasi KomputerAdnnyl NnymNo ratings yet

- Chapter 2Document45 pagesChapter 2Phạm Tiến AnhNo ratings yet

- CPU ArchitectureDocument14 pagesCPU ArchitectureTrynosNo ratings yet

- Goodphone Operating-Systems - BWDocument1 pageGoodphone Operating-Systems - BWT.A Souban aadiNo ratings yet

- Chap. 7 Microprogrammed ControlDocument14 pagesChap. 7 Microprogrammed ControlShashank MohanNo ratings yet

- WilliamStallings Chp3 PDFDocument60 pagesWilliamStallings Chp3 PDFAlfonsus devinNo ratings yet

- Unit 1completeDocument82 pagesUnit 1completemayur jagdaleNo ratings yet

- Vision de Alto Nivel Del Computador V5 PDFDocument52 pagesVision de Alto Nivel Del Computador V5 PDFGARY DAVID TRUJILLO MOTATO100% (1)

- Real Time System Lect10 ADocument25 pagesReal Time System Lect10 AAkshay DoshiNo ratings yet

- Goals of This Chapter: COEN-4710 Computer Hardware Processor Part 1: Datapath and Control (Ch.4)Document24 pagesGoals of This Chapter: COEN-4710 Computer Hardware Processor Part 1: Datapath and Control (Ch.4)Đắc Hùng Phú NguyễnNo ratings yet

- FCHN - Module 1 - Fundamentals of Computer SystemDocument14 pagesFCHN - Module 1 - Fundamentals of Computer Systemmirchigamers7No ratings yet

- Computer Science Solved Past Paper For IGCSE EDEXCELDocument4 pagesComputer Science Solved Past Paper For IGCSE EDEXCELaayanshehzad09No ratings yet

- Notes For Basic ProgrammingDocument5 pagesNotes For Basic ProgrammingbamberoNo ratings yet

- ٣محاضرات أساسيات نضام الحاسوبDocument10 pages٣محاضرات أساسيات نضام الحاسوبmuazalamri2006No ratings yet

- Computer HardwareDocument16 pagesComputer HardwareKali GouthamNo ratings yet

- Engineering BooksDocument163 pagesEngineering BooksRaj NikhargeNo ratings yet

- Chapter 4 MemoryDocument14 pagesChapter 4 MemoryNischalcha SexyNo ratings yet

- Processor and MemoryDocument27 pagesProcessor and MemoryAsad HashimNo ratings yet

- Ch6 BachDocument44 pagesCh6 BachSurid AnirbanNo ratings yet

- Lecture 4Document57 pagesLecture 4Nour NourinNo ratings yet

- CSC 222: Computer Organization: & Assembly LanguageDocument22 pagesCSC 222: Computer Organization: & Assembly LanguageAbdul RahmanNo ratings yet

- 1.4.2 The Fetch-Execute CycleDocument4 pages1.4.2 The Fetch-Execute CycleAbbas HaiderNo ratings yet

- CH 2Document86 pagesCH 2Debebe YirgaNo ratings yet

- Von Neumann ArchitectureDocument8 pagesVon Neumann ArchitectureHafeezullah shaikhNo ratings yet

- Verilog Implementation of A Node of Hierarchical Temporal MemoryDocument6 pagesVerilog Implementation of A Node of Hierarchical Temporal MemoryChandreshSinghNo ratings yet

- Sequential Logic Flip-Flop: Structure - The Control UnitDocument8 pagesSequential Logic Flip-Flop: Structure - The Control UnitSC Priyadarshani de SilvaNo ratings yet

- Green Teal Futuristic Technology PresentationDocument29 pagesGreen Teal Futuristic Technology Presentationquoctuanisme0610No ratings yet

- C-Question-Bank-ebook VIPSDocument46 pagesC-Question-Bank-ebook VIPSlalit sainiNo ratings yet

- Computer Network Part01Document80 pagesComputer Network Part01lalit sainiNo ratings yet

- Henri Fayol Principles of ManagementDocument17 pagesHenri Fayol Principles of Managementlalit sainiNo ratings yet

- Instruction Cycle: Universiti Teknologi MARADocument10 pagesInstruction Cycle: Universiti Teknologi MARANUR ZAFIRA AMANI RUSLANNo ratings yet

- Assembly Coding of 8051Document12 pagesAssembly Coding of 8051Faizan RajNo ratings yet

- Organisasi Dan Arsitektur Komputer: CPU Execution Time Amil A. IlhamDocument19 pagesOrganisasi Dan Arsitektur Komputer: CPU Execution Time Amil A. IlhamcharlesNo ratings yet

- The Processor: Computer Organization and DesignDocument162 pagesThe Processor: Computer Organization and Design王皓平No ratings yet

- Intel Xeon E5 v3 SpecificationsDocument6 pagesIntel Xeon E5 v3 SpecificationseuphurNo ratings yet

- MP&I Question BankDocument7 pagesMP&I Question Bankdarshanbhavsar41No ratings yet

- Advanced Microcontrollers Grzegorz Budzyń Lecture 8 - ARM Based MCUs and APs PDFDocument103 pagesAdvanced Microcontrollers Grzegorz Budzyń Lecture 8 - ARM Based MCUs and APs PDFtudor11111No ratings yet

- 68 XXXDocument20 pages68 XXXRyan John de LaraNo ratings yet

- QB ECC402 May 2022 Examination Microcontroller SE EXTC Sem IV 2021-22Document9 pagesQB ECC402 May 2022 Examination Microcontroller SE EXTC Sem IV 2021-22Dj RayNo ratings yet

- Control Unit and Symbolic MicroinstructionDocument1 pageControl Unit and Symbolic MicroinstructionSuresh PantNo ratings yet

- Pentium ArchitectureDocument18 pagesPentium ArchitectureMary HarrisonNo ratings yet

- BoardsDocument10 pagesBoardsAlexis DelgadoNo ratings yet

- Precise InterruptsDocument17 pagesPrecise InterruptsAshish TiwariNo ratings yet

- The Sparc ArchitectureDocument16 pagesThe Sparc ArchitectureAshwini PatilNo ratings yet

- Exploiting ILP, TLP, and DLP With The PDFDocument21 pagesExploiting ILP, TLP, and DLP With The PDFJoel Ortiz SosaNo ratings yet

- Microprocessor - Lab Assignment 1Document30 pagesMicroprocessor - Lab Assignment 1Jay ParmaniNo ratings yet

- Exploring The ARM Cortex-M7Document10 pagesExploring The ARM Cortex-M7raduseicaNo ratings yet

- Instruction CycleDocument19 pagesInstruction CycleA TNo ratings yet

- Acer Aspire A514-52G: Result InformationDocument6 pagesAcer Aspire A514-52G: Result InformationDedi IrwantoNo ratings yet

- Sistem Cerdas Pemberi Pakan Ikan Otomatis Berbasis Arduino UnoDocument12 pagesSistem Cerdas Pemberi Pakan Ikan Otomatis Berbasis Arduino Unokiky zulkifliNo ratings yet

- What Is The Difference Between Microcontrollers and 8051Document6 pagesWhat Is The Difference Between Microcontrollers and 8051Erandi Brito100% (1)

- Leaking Secrets Via Intel AMD Micro OP Caches Isca2021aDocument14 pagesLeaking Secrets Via Intel AMD Micro OP Caches Isca2021aichida_hiroshiNo ratings yet

- MCQMOD5Document3 pagesMCQMOD5maruti800No ratings yet

- Zen ArchitectureDocument24 pagesZen ArchitecturekjeevanNo ratings yet

- Lecture-5 (8086 Hardware Specifications - Pin Specification and Timing Diagrams) NotesDocument42 pagesLecture-5 (8086 Hardware Specifications - Pin Specification and Timing Diagrams) NotesFarhan FarukNo ratings yet

- Instruction Format PDFDocument5 pagesInstruction Format PDFG.SAIDULUNo ratings yet

- ILP - Appendix C PDFDocument52 pagesILP - Appendix C PDFDhananjay JahagirdarNo ratings yet

- WinPic800 - GTP-USB (Plus) Supported DevicesDocument11 pagesWinPic800 - GTP-USB (Plus) Supported DevicesjbrunobNo ratings yet