Professional Documents

Culture Documents

h08 Lecture5

h08 Lecture5

Uploaded by

tqthang7794Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

h08 Lecture5

h08 Lecture5

Uploaded by

tqthang7794Copyright:

Available Formats

Lecture 5

EE214 Technology: fT and Intrinsic Gain

gm/ID Design Methodology

Boris Murmann

Stanford University

murmann@stanford.edu

Copyright © 2004 by Boris Murmann

B. Murmann EE 214 Lecture 5 (HO#8) 1

Overview

• Reference

– F. Silveira et. al. "A gm/ID based methodology for the design

of CMOS analog circuits and its application to the synthesis

of a silicon-on-insulator micropower OTA," IEEE Journal of

Solid-State Circuits, Sept. 1996, pp. 1314-1319.

• Introduction

– Today, we'll continue to characterize the EE214 technology.

The two remaining figures of merit that are of interest to us

as circuit designers are fT and intrinsic device gain. In

conclusion, we find that VOV is not "directly" related to either

performance metric we care about. Hence, we switch

towards a strategy called "gm/ID design methodology", in

which gm/ID, rather than VOV is used directly as a central

design variable.

B. Murmann EE 214 Lecture 5 (HO#8) 2

Performance Metrics of Interest

• Transconductor Efficiency

gm

ID

• Transit Frequency

gm

ωT =

C gs

• Intrinsic Gain

g m ro

B. Murmann EE 214 Lecture 5 (HO#8) 3

fT Simulation

$ ft vs. gate overdrive

$ Boris Murmann, September 2004

.param gs=1

vgs g 0 dc 'gs'

mn1 g g 0 0 nch214 L=0.35um W=10um

.op

10/0.35

.dc gs 0.4V 1.2V 10mV

.probe ov = par('gs-vth(mn1)')

.probe ft = par('1/2/3.142*gmo(mn1)/(-cgsbo(mn1))')

.options post brief dccap

.lib './ee214_hspice.txt' nominal

.end

B. Murmann EE 214 Lecture 5 (HO#8) 4

Result

NMOS W/L=10/0.35

30

EE214 technology

25 Long Channel Fit

20

f T [GHz]

15

10

0

-0.2 -0.1 0 0.1 0.2 0.3 0.4 0.5

VOV [V]

1 3 µVOV

Long Channel: fT =

2π 2 L2

B. Murmann EE 214 Lecture 5 (HO#8) 5

Observations - fT

• Again, a simple long channel model doesn't do a very good job

– Large fT discrepancy in weak inversion and in strong

inversion, at large VOV

• The reasons for these discrepancies are exactly the same as

the ones we came across when looking at gm/ID

– Bipolar action in weak and moderate inversion

– Short channel effects at large VOV

• Less gm, hence lower gm/Cgs

• Same conclusion, we won't be able to make good predictions

with a simple long channel relationship

B. Murmann EE 214 Lecture 5 (HO#8) 6

Another Look at gm/ID·fT

NMOS W/L=10/0.35

160

140 EE214 technology

Long Channel

120

gm/I D*f T [GHz/V]

100

80 Sweet spot (?)

60

40 Short channel

Long channel predicts effects

20 too much gm/ID

0

-0.1 0 0.1 0.2 0.3 0.4 0.5

VOV [V]

gm 1 3µ

Long Channel: ⋅ fT =

ID 2π L2

B. Murmann EE 214 Lecture 5 (HO#8) 7

Intrinsic Gain Simulation

$ gm*ro vs. vds

$ Boris Murmann, September 2004

$ vt measured using .op run

.param vt1=580m

.param vt2=600m

mn1 d g1 0 0 nch214 L=0.35um W=10um

mn2 d g2 0 0 nch214 L=0.40um W=10um

vg1 g1 0 dc 'vt1+0.2'

vg2 g2 0 dc 'vt2+0.2' VGS=Vt +200mV

vd d 0 dc 1

.op

.dc vd 0 3.3V 10mV

.probe av1 = par('gmo(mn1)/gdso(mn1)')

.probe av2 = par('gmo(mn2)/gdso(mn2)')

.options post brief

.lib './ee214_hspice.txt' nominal

.end

B. Murmann EE 214 Lecture 5 (HO#8) 8

Intrinsic Gain Plot (VOV=200mV)

NMOS W=10um NMOS W=10um

120 120

L=0.35um L=0.35um

L=0.4um L=0.4um

100 100

80 80

Long Channel

gmro=const.

gm*ro

gm*ro

60 60

40 40

20 20

0 0

0 1 2 3 0 0.2 0.4 0.6

VDS [V] VDS [V]

B. Murmann EE 214 Lecture 5 (HO#8) 9

Observations – Intrinsic Gain

• The gm·ro product shows a strong dependence on VDS bias

– Mostly due to varying ro, (see lecture 2, slide 20)

• Also, there is a very smooth transition from triode to something

close to forward active behavior

– Long channel model would have predicted an abrupt change

to large intrinsic gain at VDS = VOV

– From the plots, we see that we need VDS > 1.5…3 VOV to get

appreciable gain

• At high VDS, ro and thus gm·ro decrease due to SCBE (substrate

current induced body-effect)

– Highly technology dependent, and usually not present in

PMOS devices

– If you are interested in more details, please refer to EE316

or a similar course

B. Murmann EE 214 Lecture 5 (HO#8) 10

Why care about VOV?

• By now, it should be clear that VOV is not a very useful design

variable

– There is no simple expression that accurately links either

gm/ID, ft or gm·ro to VOV

– VOV does not even clearly define the onset of forward active

operation ("Vdsat")

• The primary variables we care about from a design and

performance perspective are gm/ID, ft and gm·ro

– So why not work exclusively with these?

– In case we need a rough estimate for "Vdsat", we can always

use Vdsat ≅ 2/(gm/ID)

• E.g. gm/ID=10V-1 ⇒ Vdsat ≅ 200mV

• Let's go back to a design example using a simple CS stage

B. Murmann EE 214 Lecture 5 (HO#8) 11

Design Example 1

2V

RL

Vo

CL

vi

VB

• Given specifications

– DC gain=-2, ID ≤ 2mA, f-3dB=100MHz, CL=10pF

– Make transistor as small as possible

B. Murmann EE 214 Lecture 5 (HO#8) 12

Hand Calculations (1)

• We know that in our technology gm·ro ~> 40, even for minimum

channel length. Hence, for a small signal gain of 2, the output

impedance of the amplifier will be dominated by RL

– OK to use L=Lmin=0.35µm

• We can now find RL and gm simply as

1 1 1 1

f −3dB = ⇒ RL = = 159Ω

2π RLC L 2π 100MHz ⋅10 pF

2

ADC = − g m RL = −2 ⇒ gm = = 12.6mS

159Ω

• If we use all the available current, we have

g m 12.6mS 1

= = 6.3

ID 2mA V

B. Murmann EE 214 Lecture 5 (HO#8) 13

Hand Calculations (2)

• How about using less current?

• Recall that for fixed transconductance W ~ 1/VOV ~ gm/ID

– Using less current means larger gm/ID and thus larger device

• But specifications said to minimize device size

• As a last step, we need to determine the actual device width

– For design implementation and verification with Spice

• Using long channel equations will be very inaccurate

• Solution: Sizing chart

– Plot of ID/W as a function of the design variable gm/ID

– Can generate this chart once for several channel lengths

and use it throughout the design process

B. Murmann EE 214 Lecture 5 (HO#8) 14

Current Density Chart

NMOS L=0.35um

90

80

70

60

I D/W [uA/um]

50

40

30

20

10

0

0 5 10 15 20 25

gm/I D [1/V]

B. Murmann EE 214 Lecture 5 (HO#8) 15

A Better Current Density Chart

NMOS L=0.35um

35

30

25

23µA/µm

I D/W [uA/um]

20

15

10

(2/6.3)V=317mV

5

0

100 150 200 250 300 350 400

2/(gm/I D) [mV]

B. Murmann EE 214 Lecture 5 (HO#8) 16

Spice Verification

ID 2000

• So, the device width is W=

ID

= µm = 87 µm

23

W

2V

• How to determine VB?

159Ω

• Adjust VB in Spice until gm/ID=6.3V-1

Vo

• Good initial guess

– VB ≅ Vt+2/(gm/ID) ≅ 600mV+317mV 87/0.35

10pF

• Fortunately, we'll find a way to build vi

circuits without VB VB

– No need to iterate in practice…

B. Murmann EE 214 Lecture 5 (HO#8) 17

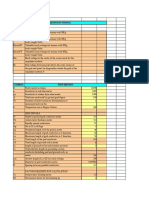

DC Operating Point

**** mosfets

subckt beta 60.5664m

element 0:mn1 gam eff 894.1238m

model 0:nch214 gm 12.7994m

region Saturation

gds 223.6427u

id 2.0147m

gmb 2.7928m

ibs 0.

ibd 0. cdtot 112.7289f

vgs 845.0000m cgtot 154.6957f

vds 1.6797 cstot 294.9323f

vbs 0. cbtot 300.7032f

vth 569.7473m cgs 107.6797f

vdsat 201.1145m cgd 19.7903f

g m 12.8mS 1

= = 6.37

I D 2.01mA V

B. Murmann EE 214 Lecture 5 (HO#8) 18

AC Response

7

5.87dB=1.97

6

5

|vo/vi| [dB]

0 0 1 2

10 10 10

f [MHz]

B. Murmann EE 214 Lecture 5 (HO#8) 19

Observations and Remarks

• The design is essentially "dead on" target!

– No need for any Spice tweaking

• We accomplished this by focusing on a performance related

parameter (gm/ID) in the design process

– Note that strictly speaking, device width is not a design

parameter, since it does not directly relate to any of the

specs that we were given!

Specifications

Design

gm, gm/ID, f T, ...

Determine device sizes

Implementation/

Verification Simulation results

B. Murmann EE 214 Lecture 5 (HO#8) 20

gm/ID Design Methodology

• Determine gm

– Based on circuit and specifications

• Pick L

– Short channel → high fT, long channel → high ro, gm·ro

• Pick gm/ID

– Based on speed, power or other constraints

• Determine bias (VB or ID for current source bias)

– Adjust VB to yield desired gm/ID

– For current source bias, we can directly find ID=gm/(gm/ID)

• Determine W

– Using current density chart or Spice

B. Murmann EE 214 Lecture 5 (HO#8) 21

You might also like

- VLF Radio Engineering: International Series of Monographs in Electromagnetic WavesFrom EverandVLF Radio Engineering: International Series of Monographs in Electromagnetic WavesNo ratings yet

- Iom - 1-250Document250 pagesIom - 1-250Eduardo JoseNo ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsRating: 5 out of 5 stars5/5 (1)

- Excel On Steroids Tips and Tricks Vol1Document31 pagesExcel On Steroids Tips and Tricks Vol1Shane BallantyneNo ratings yet

- Protection and Automation: Life Cycle Testing of Synchrophasor Based Systems Used For Protection, Monitoring and ControlDocument58 pagesProtection and Automation: Life Cycle Testing of Synchrophasor Based Systems Used For Protection, Monitoring and ControlAlberto Medeiros100% (2)

- Iso TS 55010-2019Document48 pagesIso TS 55010-2019usman67% (3)

- LSK389 Dual Monolithic JFETDocument14 pagesLSK389 Dual Monolithic JFETattapapaNo ratings yet

- Lacroix 2008Document4 pagesLacroix 2008Kloga Rajesh WaranNo ratings yet

- h06 Lecture4Document23 pagesh06 Lecture4tqthang7794No ratings yet

- 2011 5 May ISCS Jain PresentationDocument17 pages2011 5 May ISCS Jain PresentationbrunopjacobNo ratings yet

- Microwave Engineering Chapter 2 Example 1Document16 pagesMicrowave Engineering Chapter 2 Example 1John Bofarull GuixNo ratings yet

- EGHTV65B-F-C3-5XR Product SpecificationDocument4 pagesEGHTV65B-F-C3-5XR Product SpecificationCristiana BonifácioNo ratings yet

- Fm/Am Radio Ic: CD2003GP/GBDocument7 pagesFm/Am Radio Ic: CD2003GP/GBМаксим МульгинNo ratings yet

- 130nm A gmID-Based Noise Optimization For CMOS Folded-CascodeDocument6 pages130nm A gmID-Based Noise Optimization For CMOS Folded-Cascodejeevamk423No ratings yet

- Week 06 Assignment 06 SolnDocument6 pagesWeek 06 Assignment 06 SolnsuneethaNo ratings yet

- 36847-CG14154 Damping Scheme EHS 5 - 16-20140718Document5 pages36847-CG14154 Damping Scheme EHS 5 - 16-20140718alanetnNo ratings yet

- Exp 4Document8 pagesExp 4Ali MhadatNo ratings yet

- EXFO FOT-20A Power Meter Data SheetDocument4 pagesEXFO FOT-20A Power Meter Data SheetEmilioNo ratings yet

- JCVV-65A-R4 Product SpecificationsDocument5 pagesJCVV-65A-R4 Product SpecificationsJulián GiménezNo ratings yet

- ET-426L Lab Manual Spring 2020 PDFDocument59 pagesET-426L Lab Manual Spring 2020 PDFMalik Mudasir NazeerNo ratings yet

- Abs Bukl+sfDocument269 pagesAbs Bukl+sfding liuNo ratings yet

- FAE347-A29/E30/J23: Compact, AM/FM Automotive Electronic Tuner For Popular ClassDocument2 pagesFAE347-A29/E30/J23: Compact, AM/FM Automotive Electronic Tuner For Popular ClassComputer World sbyNo ratings yet

- 1) Basic Data: Design of Cantilever Beam As Per IS 456-2000Document4 pages1) Basic Data: Design of Cantilever Beam As Per IS 456-2000khaniskhan03No ratings yet

- Task3 - Common Soure FET AmplifierDocument24 pagesTask3 - Common Soure FET AmplifierAman Kumar TrivediNo ratings yet

- Lecture07 Ee474 GmidDocument23 pagesLecture07 Ee474 Gmiddunglh.bi12-108No ratings yet

- Andmch4015 1-DDocument11 pagesAndmch4015 1-DManoel Camargo SampaioNo ratings yet

- Broadcom IP2 IP3Document7 pagesBroadcom IP2 IP3shengquan_hu1512No ratings yet

- A. Pengamatan Sinyal DSB-SC V2 5mV V2 10mVDocument4 pagesA. Pengamatan Sinyal DSB-SC V2 5mV V2 10mVBluesInsectNo ratings yet

- Expt 3: Voltage Shunt Feedback Amplifier (2020)Document4 pagesExpt 3: Voltage Shunt Feedback Amplifier (2020)samarthNo ratings yet

- Characteristics: EXPERIMENT 08: SPICE Simulation of and Implementation For MOSFETDocument11 pagesCharacteristics: EXPERIMENT 08: SPICE Simulation of and Implementation For MOSFETJohnny NadarNo ratings yet

- Samb Expand End PlateDocument5 pagesSamb Expand End PlateArbiNo ratings yet

- Class F: ©james BuckwalterDocument33 pagesClass F: ©james Buckwalterts bulganNo ratings yet

- ASI4517 R3 V 06Document2 pagesASI4517 R3 V 06Дмитрий СпиридоновNo ratings yet

- EE5320: Analog IC Design Chaitanya Kumar EE19S062 Dept. of Electrical Engg. IIT Madras Chennai 600036Document26 pagesEE5320: Analog IC Design Chaitanya Kumar EE19S062 Dept. of Electrical Engg. IIT Madras Chennai 600036Chaitanya KumarNo ratings yet

- 09 WO - NAST3017 - E01 - 1 UMTS Interference Investigation-48Document48 pages09 WO - NAST3017 - E01 - 1 UMTS Interference Investigation-48Rajesh KumarNo ratings yet

- Ec49222 e Cmos PDFDocument19 pagesEc49222 e Cmos PDFKiinhooNo ratings yet

- Belts Tables PDFDocument30 pagesBelts Tables PDFM Hamdy EladwyNo ratings yet

- CS7204441 - 01 RVV2H-6533D-R5Document5 pagesCS7204441 - 01 RVV2H-6533D-R5YarinaNo ratings yet

- MPT 221Document3 pagesMPT 221marina anastasovaNo ratings yet

- Design of Slab: F5F6G5G6Document2 pagesDesign of Slab: F5F6G5G6AKSHAYNo ratings yet

- 2VV-33C-R4: General SpecificationsDocument5 pages2VV-33C-R4: General SpecificationsCristian GhicaNo ratings yet

- Line Reactance, Zero Sequence Reactance and Mutual Zero Sequence ReactanceDocument39 pagesLine Reactance, Zero Sequence Reactance and Mutual Zero Sequence ReactanceHanh-Trang DangNo ratings yet

- Useful Design Parameters (Simplified)Document2 pagesUseful Design Parameters (Simplified)Pay RentNo ratings yet

- Quick Reference Data: PILKOR ElectronicsDocument8 pagesQuick Reference Data: PILKOR ElectronicsAnonymous CGk2roNo ratings yet

- 18eel66 Lab ManualDocument53 pages18eel66 Lab ManualVasanthNo ratings yet

- W 3 DzzslidesDocument19 pagesW 3 DzzslidesMarceloNo ratings yet

- EM Pro Simulation: Geometr y Port/Feed Simulatio N Setting Post-Processin GDocument9 pagesEM Pro Simulation: Geometr y Port/Feed Simulatio N Setting Post-Processin GHa Tran KhiemNo ratings yet

- COMMSCOPE - RHHTT 65A R4 V2 - TitiDocument4 pagesCOMMSCOPE - RHHTT 65A R4 V2 - TitiWitto PereNo ratings yet

- Manual Voltage Drop Caculate EngDocument11 pagesManual Voltage Drop Caculate EngTeammeaTXoXNo ratings yet

- MGF0917A: L & S Band Gaas FetDocument4 pagesMGF0917A: L & S Band Gaas FetTulio SanchezNo ratings yet

- QuestionsDocument1 pageQuestionsMadhura Bhashitha0% (1)

- Electrical Computation Frmo ExcelDocument1 pageElectrical Computation Frmo Excelwilson coNo ratings yet

- Calculation and Selection ResultDocument18 pagesCalculation and Selection ResultNery TorresNo ratings yet

- 4P-4M-A2 Product SpecificationDocument5 pages4P-4M-A2 Product SpecificationTan Teck jinnNo ratings yet

- The State-of-the-Art of Silicon-on-Sapphire CMOS RF SwitchesDocument4 pagesThe State-of-the-Art of Silicon-on-Sapphire CMOS RF SwitchesAhmed AtefNo ratings yet

- 3 Earth MatDocument9 pages3 Earth MatdesignselvaNo ratings yet

- Cabluri Rg6 20-8320Document1 pageCabluri Rg6 20-8320ionutsmNo ratings yet

- Product Information: Data Cable, U/UTP, Category 6, AWG23Document4 pagesProduct Information: Data Cable, U/UTP, Category 6, AWG23Numan AminNo ratings yet

- (2011 IEDM) Record High RF Performance For Epitaxial Graphene TransistorsDocument3 pages(2011 IEDM) Record High RF Performance For Epitaxial Graphene Transistorsybgwst5wnrNo ratings yet

- Ref10 06259481Document3 pagesRef10 06259481Rajendra ChikkanagoudaNo ratings yet

- HMC 511Document6 pagesHMC 511payam79bNo ratings yet

- Sunlord TWPEP131313B305T DSDocument7 pagesSunlord TWPEP131313B305T DSrathish.aNo ratings yet

- Commscope 6p 2l4m d3Document4 pagesCommscope 6p 2l4m d3hasib_muhammedNo ratings yet

- CalculationReport TimberBeam PDFDocument4 pagesCalculationReport TimberBeam PDFMoz NazNo ratings yet

- Qaim's CVDocument1 pageQaim's CVQaim RazaNo ratings yet

- Parts Breakdown For Remote Mount Dmr-300-15-Xl-200Document1 pageParts Breakdown For Remote Mount Dmr-300-15-Xl-200UB HeavypartsNo ratings yet

- dnx120 Manual 2Document39 pagesdnx120 Manual 2claudio caroNo ratings yet

- LR Mate 200id ARC Mate 50id: Operator'S ManualDocument125 pagesLR Mate 200id ARC Mate 50id: Operator'S ManualbmeshakirNo ratings yet

- ECDIS: Type Specific Checklist Type:: BSM Mtcs Document FormDocument2 pagesECDIS: Type Specific Checklist Type:: BSM Mtcs Document FormГенна ФелексовNo ratings yet

- Mechanical and Plumbing Works General Notes For All Mechanical and Plumbing WorksDocument3 pagesMechanical and Plumbing Works General Notes For All Mechanical and Plumbing WorksMOHAMED ATTIANo ratings yet

- Bendiksen1991 PDFDocument10 pagesBendiksen1991 PDFlhphong021191No ratings yet

- Industrial Training Report: Bachelor of TechnologyDocument4 pagesIndustrial Training Report: Bachelor of Technologysai project100% (1)

- Animal ClassificationDocument9 pagesAnimal ClassificationGayatri RakurthiNo ratings yet

- FALLSEM2022-23 BCSE202L TH VL2022230103384 Reference Material I 22-07-2022 DSA Module1 1Document15 pagesFALLSEM2022-23 BCSE202L TH VL2022230103384 Reference Material I 22-07-2022 DSA Module1 1anisha sharmaNo ratings yet

- ScriptDocument4 pagesScriptMe. GamerNo ratings yet

- Barko Barko Barko Barko Barko Loaders Loaders Loaders Loaders LoadersDocument190 pagesBarko Barko Barko Barko Barko Loaders Loaders Loaders Loaders Loadersalexandre desdoitsNo ratings yet

- Voss CatalogDocument507 pagesVoss CatalogadelinciprianNo ratings yet

- Dsu Microproject (Linked List) Ayush SasaneDocument18 pagesDsu Microproject (Linked List) Ayush SasaneAyush Sasane50% (2)

- Data CleansingDocument6 pagesData Cleansingjohn949No ratings yet

- ExcavatorDocument15 pagesExcavatorfredymademydayNo ratings yet

- Masterbatch - WikipediaDocument15 pagesMasterbatch - WikipediaSudhir PatilNo ratings yet

- TLC 5971Document43 pagesTLC 5971jpserafiniNo ratings yet

- BIM KPI Role of Key Performance Indicators For Evaluating The Usage PDFDocument9 pagesBIM KPI Role of Key Performance Indicators For Evaluating The Usage PDFstuntclashNo ratings yet

- Vol 19 No 9 September 2020Document408 pagesVol 19 No 9 September 2020ijlter.orgNo ratings yet

- Anatomy-Specific Classification of Medical Images Using Deep Convolutional NetsDocument4 pagesAnatomy-Specific Classification of Medical Images Using Deep Convolutional NetsSiva SreeramdasNo ratings yet

- COSC 2307: Sub-QueriesDocument23 pagesCOSC 2307: Sub-QueriesBhavikDaveNo ratings yet

- 15 HSDB Non-Rotating Hydraulic-Set Liner HangerDocument2 pages15 HSDB Non-Rotating Hydraulic-Set Liner HangerGhinet Teodor-ioanNo ratings yet

- Hardware and Software Development and Integration Per SAE ARP4754ADocument5 pagesHardware and Software Development and Integration Per SAE ARP4754ALucas LazaméNo ratings yet

- Scope Database - International Advisory Board - URLDocument7 pagesScope Database - International Advisory Board - URLNagarajan TNo ratings yet

- JUnit TutorialDocument79 pagesJUnit TutorialSaravanan MuruganNo ratings yet