Professional Documents

Culture Documents

PFC Small Signal

Uploaded by

Meral MeralOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

PFC Small Signal

Uploaded by

Meral MeralCopyright:

Available Formats

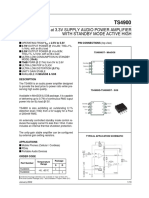

AVERAGE SMALL-SIGNAL ANALYSIS OF THE BOOST POWER FACTOR

CORRECTION CIRCUIT

Dr. Ray Ridley

Ridley Engineering Inc.

www.ridleyengineering.com

Original paper published 1987

Center for Power Electronics

Virginia Tech

ABSTRACT

A thrre-terminal, small-si?,nal model for the boo.rt power factor correction cirmit is

developed. The model is applicable for frequencies below the line frrquency, and i.f

useful for desi?,nin!!, the low-frrquency compensation network for feedback of the

output volta!!,e. Thr model i.5 derived for a control with a reference derived either

from the line or f rom a fzxed sinu.widal reference. The implicatinm nf the new model

are discu.ued for resistive and comtant power loads, and desi!!,11 procedures/or

closin1: the voltage feedback loop are given.

trols the off time. Pixed or variable hysteresis con

I. Introduction trol can be used, but this docs not affect the

small-sign al analysis. The lower circuit of Fig. I

Many users of ac-dc power supplies are becoming

shows the same power stage, but the inductor cur

increasingly conscious of the need to improve the

rent is compared to a fixed sinewave reference. It

power factor of the input current to the conve11cr.

will be seen that this circuit has some small-signal

One of the most common circuits used to achieve advantages which may justify the more complex

unity power factor is the boost converter. The op control needed to generate the fixed reference.

eration of this converter has hcen analyzed in detail

by many previous researchers, hut none of them There are two major concerns of the small-signal

provides an averaged small-sign al model suitable for performance of the circuit. Firstly, the control cir

the design and analysis of the output voltage feed cuit forcing the line current to track the input volt

back loop. age must be stable. This circuit can be analyzed in

a manner very similar to state-space averaging, with

Pig. I shows a boost converter used with two dif the control voltage, l'c• and input voltage assumed

ferent control schemes to achieve unity power fac constant during each switching cycle. The closed

tor. In the upper circuit, the switch is turned on loop eigenvalues of the circuit will vary as the input

until the inductor current equals a scaled multiple voltage increases from zero to its peak value. The

of the input voltage. !\. hysteresis comparator con- second control consideration is the analysis of the

Ridley Engineering Design Center 1

Full-Wave

Rectifier

Full-Wave

Loa

Rectifier

Figure 1. Boost Converter with Unity Power-Factor Control: The upper control circuit uses a line-voltage

reference to control the inductor current. This provides a more sensitive cont.rol than the lower circuit,

which uses an external reference synchronized to the input line frequency.

circuit on a cycle-to-cycle basis. In this case, the Many papers have discussed various implementa

input current is assumed to track the input voltage tions of active power factor correction circuits and

correctly, and the circuit is analyzed on an average dc-ac interfaces. Schlecht ( 11 introduced the con

basis over a full cycle of operation. This analysis is cept of quasi-static analysis for these time-varying

essential for the proper design of the feedback cir systems, and showed the locations of poles and ze

cuit, which regulates the output voltage of the ros of the system as they changed over the

power factor circuit. sinusoidal cycle. Kocher and Steigerwald [21 ana

lyzed a flyback version of the power factor car-

Ridley Engineering Design Center 22

RIDLEYWORKS

®

rection circuit, using a similar modeling technique,

II. Sn1all-Sig11al A 11aly..vis

but the dynamics from control-input-to-output

were not considered. Henze and Mohan f 3] pre

sented a control-output model consisting of a con The small-signal analysis is performed on an aver

trolled current source fceding the load capacitor and age hasis over a complete half-cycle of the input

sincwave voltage, assuming that the input current

resistor. This model is shown to be incomplete

is properly controlled to track the scaled input

later in this paper. For resistive loads, this difference

voltage. This analysis uses similar techniques to

is small, but it can be significant with constant

those of Vorperian (7J, who derived the equivalent

power loads. Mohan, Undeland and Ferraro [41

PWM switch model for de-to-de converters. The

considered the current-programming loop of the waveforms of the converter are shown in Fig. 2.

boost converter, showing it to be stable for all The input voltage is a sinewave, and the current

conditions. Keller and Baker [SJ correctly consid programming loop forces the input current to also

ered both the high-frequency current feedback loop be a sinewave. 1be output voltage is assumed to

and the low frequency output-voltage feedback, be constant over a switching cycle, and the output

providing experimental measurements and SPICE current is chopped at high frequency with a

simulations, which agreed well. Other papers 16,7) sinusoidal envelope equal to that of the input cur

derive interesting topologies for isolating the power rent. Referring to the waveforms of Fig. 2, the

factor circuit or reducing semiconductor stresses. power balance equation for one cycle of operation

ts

The quasi-static analysis (41 of the boost converter

with hysteretic current programming has been

done, and is not considered in detail in this paper. The input quantities v1 and i1 are rms values, v0 is

No instabilities can arise in the current loop, and the de output voltage, and i0 is the average output

the only problem in designing the switching control current over a cycle. For line-referenced control,

circuit is in selecting an hysteresis scheme and find shown in Fig. 1, the control law governing the in

put current is

ing a reliable method for sensing the line current.

The design of the output-voltage compensator,

(2)

however, has not been addressed, largely due to the

lack of a small-signal model for the power converter

Substituting this control law into Eq. I gives

on a cycle-to-cycle hash. This small-sign al model

is developed in this paper. Interesting differences to

(3)

the model derived in [31 are shown, and the impact

on design for resistive and constant-power loads is The steady-state conversion ratio, M, of the system

discussed. Design rules for the control components can then be found:

are given with consideration of widely-varying tine

and loads which can he encountered. The small (4)

signal model and design guidelines are verified with

computer simulation. where

Ridley Engineering Design Center 3

I.

0 0

Input Voltage Input Current

I --

o

Output Voltage Output Current

Figure 2. Waveforms of the Unity Power-Factor Boost Converter: The conlrol circuit forces the input current

to follow the input voltage sinewave. The ilvcrage input and out.put terminal quantities of the power

factor circuit are defined on the waveforms.

(5) (8)

Perturhing Eq. 3 and eliminating small-signal

cross-products and de tenns yields the equation

Ill. Eq11h ale11t Small-Signal

1

(6) Circuit

The small-signal Eqs. (7) and (8) can he represented

which simplifies to

with the simple circuit model shown in Pig. 3. The

component values of this circuit are all given in the

(7)

left column of Tahle I. Similar analysis can he per

formed for the fixed-reference control scheme of

The control Eq. 2 can be similarly perturbed to give

Fig. I, and the component values corresponding to

Ridley Engineering Design Center 4

this circuit are in the right-hand column of Tahlc circuit i� not a simple controlled current source

I. The small-signal equivalent circuit remains the feeding the load. due to the presence of the small

same for both control schemes. Notice that thi� signal resistor r0

ro

Figure 3. Small""C,ignal Circuit Model of the Roost rower Factor Circuit: This circuit models the i.mall-ilignal

Eqs. (7) and(!!). Notice the presence of the �mall-signal output resistor, ,0• which significantly affect�

the characteristics of the circuit when CQnnected to a resistive or a regulator load.

I

:

I

I

ro 'C

I

R

I

I

I

I

I

----------------------------------------�

1

I

Power Factor Switch Model

Figure 4. Small""�ignal Circuit Model with Output Filter Load: The small-signal model of Fig. 4 is connected

to the external load and input source.

From the small-signal circuit of Fig. 4 with the Similarly, the control-output transfer function can

output ftlter capacitor and load connected, the be derived by inspection to give

input-output transfer function can be derived by

inspection to give (IO)

Por a resistive load R1., the small-signal resistance

(9)

r0 is equal to the load resistance, and the control

output transfer function simplifies to

Ridley Engineering Design Center 5

'fRhlc I. Smnll-Siit nal Component \'alurs for the Hnost Power Factor Correction Circuit.

J ,JNR REFERENCE FIXED REFERENCE

M

1¥ 15¥ i

ro

r, 00

M2

V1

gl k

v,

Vo Vo

ro -

lo lo

gf

--

2M

r ro

o

V1 v,

gc kM M

put of the power-factor correction circuit. The

( 11) control-output transfer function of the power-factor

correction circuit when connected to a regulator

load is

Notice that the time constant of this expression is

half that which would be expected without the

small-signal resistance r0 • 1 + .rCr0

// - R, (13)

=gr, I

A constant power load, such as a switching regula .re

tor, has a small-signal input impedance at low fre

In this case, the small-signal resistance is of oppo

quencies given by (8)

site sign to the input resistance of the regulator, and

the parallel combination is an open circuit. This is

( 12) significantly different from the small-signal model

of (JJ, with the controlled current source feeding the

where V0 and 10 are the input voltage and current, load. Fig. 5 shows the control-output plots for the

respectively, of the regulator, provided by the out- model with and without r0

Ridley Engineering Design Center 6

40

Gain

30

20

10

0 -------------

Without r0

·ca -10

C,

-20

-30

-40

-50,---,--�---r------r---,---r---,----;

0.01 0.1 1.0 10.0 100.0

Frequency (Hz)

0

Phase

-90-t------------------==�--

---

�

l?_ Wrthol.t r

O __

a.. -180 ,.. - - - - - - -

-VO

0.01

------.---�-------....----.---........

0.1 1.0 10.0

-- 100.0

Frequency (Hz)

Figure S. Control-Output Transfer Function with Regulator Load: The significance of the small-signal- resist

ance r0 when the circuit supplies a constant power load is demonstrated by the plot with and without

this resistor in the model.

The system model without r0 is open-loop unsta to produce low de error. However, such a com

ble, with a right-half plane pole at s = 1/CRv The pensation would produce a conditionally stable

model with r0 does not have the right-half plane system where the phase exceeds -180° at low fre

pole, and has ·the characteristics of an integrator. quencies, and is less than 180° at crossover, as

The model without r0 has severe implications for shown in Fig. 6. Such a system is undesirable due

the control compensation which must be used. It to reductions in gain which can he encountered

is desirable to use an integrator and lead network during transient or start-up conditions.

Ridley Engineering Design Center 7

100 Gain

80

m

�

60

C: 40

·a;

20

-20

0.01 0.1 1.0 10.0 100.0

Frequency (Hz)

0

Phase

-90 ---

(I)

Cl.I

With r0 /

� /

0.. -180--1------- /

.,,. .,,.

-270 ---

0.01 0.1 1.0 10.0 100.0

Frequency (Hz)

Figure 6. Com(lensated Looi' Gain with Regulator Load: The significance of the small-signal resistance r0 on

the loop gain with a constant-power load is demonstrated.

filter capacitor of 673 11F. Line-referenced control

IV. V erificatio11 of was used for the simulation. From Eq. 9, the line

to-output transfer function is

Sniall-Signal Mode/

I\

Vo RL

I\ =gf 2+ .rCR,.

v,

The small-signal model can be verified by simulat

2M · (14)

ing the exact switching circuit, and comparing the 2+ sCR,.

output-voltage transient with that predicted hy the 2

l + 0.0673.r

small-sign al equivalent circuit. A 50-W circuit was

used as an example, with the parameter values de The time-domain response for the output voltage

fined in Table 2, assuming a resistive load, and a is then given by

Ridley Engineering Design Center 8

Table 2. Numerical Values for the Small-Signal Components of Ocsign Example

LINE REPERENCE FIXED REPERENCE

V; 50 50

Vo 100 100

lo 0.5 0.5

VC I I

k 50 .

v, - 1

M 2 2

r1 50 00

gl I 1

ro 200 200

gf 0.02 0.01

gc 0.5 0.5

- - 14·861] step control change of 0.1 V, the output voltage

vo(t) = V0 + 2l\V1 [ I e

transient from the small-si gnal model is

= 100 + 10( I e- 14'861]

for a 5-V step input change.

Fig. 7 show the exact digital simulation of this ex The results of the exact simulation and the predic

ample superimpo!>ed on the step response predicted tion of the small-signal model are shown in Pig. 8

by Eq. ( 15). It can he seen that the small-signal for a step change in the control voltage. The excel

model predicts the correct result. Similarly, for a lent agreement of the results confirms the validity

of the small-signal modelling.

Ridley Engineering Design Center 9

110 �-----------------------------,

108

106

104

102

Exact digital Simulation

Small-Signal Model Simulation

100

0 0.02 0.04 0.08 0.08 0.1 0.12 0.14

Time (s)

Figure 7. Simulated Circuit Response for a Step-Line Change: The exact simulation of the circuit closely fol

lows the response predicted hy the small-signal model, verifying the time constant and amplitude of

the first-order system response.

V. Feedback Loop a>z =

2

(17)

CRL

Compensation This location of the compensation zero ensures a

90° phase margin at all frequencies for a resistive

Feedback compensation is required to regulate the

load.

output voltage over the full input voltage and out

put load range. An integral-and-lead network pro

The transfer function from control-output with a

vides the optimum compensation for both resistive

constant power load (Fig. 6) is simply an integrator.

and constant power loads. Two parameters must

'Jbe zero for this case must be placed at or below

be selected for the compensation network: the lo

the minimum crossover frequency of the loop gain

cation of the zero, and the high-frequency gain.

to provide a phase margin of 45° or greater. The

These parameters are defined on the compensation

control-output transfer function is

gain asymptotes shown in Fig. 9. For a resistive

load, the zero should be placed at the same fre

to_ _I__ _!_i_ _t_ (18)

quency as the pole in the transfer function from t - Kc sC - kM sC

C

control to output, given by

for line-referenced control, and

Ridley Engineering Design Center 10

110 --.-------------------------------,

Exact digital Simulation

108

Small-Signal Model Simulation

106

�

(I)

Cl

�

�

>O 104

102

100

98 4--..---,-------,-----,---r--.--,-----,---,---.--,----,-----,----1

0.02 0.04 0.08 0.08 0.1 0.12 0.14

Time (s)

Figure 8. Simulated Circuit Re!iponse for a Step-Control Change: The exact simulation of the circuit closely

follows the response predicted by the small-signal model, verifying the time constant and amplitude

of the first-order system response.

Oo _ _l__ V, _l_ (21)

(19)

0 - gc .rC - M .rC

C

for fixed reference control. In both cases, the maxi

for a constant-reference control. Both of these

mum crossover frequency of loop gain will be given

transfer functions change with line conditions, but

by

not with load variations, and have a maximum

value at high line. A suitable crossover frequency

(22)

at high line is 1/4 the frequency of the rectified line,

or 1/2 the frequency of the input line. The high The minimum crossover frequency, occurring at

frequency asymptote can then he selected for the low line, is given by

compensation:

min

We =

[-V_l_

mi_n

vmax

]2 w2/

(23)

l

(20) for line-referenced control and

(24)

for line-referenced control and

Ridley Engineering Design Center 11

40

30

20

10

- 0

·ca -10

Cl

-20

-30

-40

-50

0.01 0.1 1.0 10.0 100.0

Frequency (Hz)

Figure 9. Compensation Gain Asymptotes: An integral and lead network is used to provide 1,ero de error and

good phase margin at the cros11over frequency. The zero of the compemu1tion network is placed be•

fore the crossover frequency.

for fixed-reference control. The flat gain of the The 7..ero of the compensation network should be

compensation network at higher frequencies will placed at wr1n for a 45" phase margin, OT, more

transmit considerable ripple back to the control conservatively, at ] <Dcmtn for a 60° phase mar

voltage, Ve, which can distort the input waveforms.

gin. The recommenied zero locations and gains of

However, this ripple can easily be removed with the

addition of a notch filter at twice the line frequency. compensators for the different control schemes with

The design of such a compensation scheme is not resistive and constant-power loads are summarized

considered in this paper. in Table 3.

Tahle 3. Recommended Compensation Circuit Parameter Values

LINE REFERENCE FIXED REFERENCE

Resistive Regulator Resistive Regulator

2

CRL

Ridley Engineering Design Center 12

Waveforms", Power Electronics Specialists'

VI. Collclusiolls Conference Record, I 982, pp. 6J-75.

An average small-signal circuit model has heen de

3. C. P. Henze, N. Mohan, "A Digitally

veloped to predict the response of the hoost

Controlled AC to DC Power Conditioner

power-factor correction circuit. Simulated results

that Draws Sinusoidal Input Current",

for step-line and step-control transients have con

Power Electronics Specialists' Conference

firmed the results of the small-sign al modeling. The

Record, 1986, pp. SJ I -540.

circuit model contains a small-signal resistance, r0 ,

which significantly affects the performance of the

4. N. Mohan, T. M. lJndcland, R. .J. Perraro,

circuit, simplifying the compensation design when

"Sinusoidal I .inc Current Rectification with a

a regulator is preceded hy the power factor cor

100 kHz 8-SIT Step-Up Converter", Power

rection circuit.

Electronics Specialists' Conference Record,

Control-loop compensation design procedures have 1984, pp. 92-98.

been developed for two different power-factor con

trol schemes, with either resistive or constant power 5. R. Keller, G. Baker, "Unity Power Factor Off

loads. The design guidelines provide a simple, non I ,ine Switching Power Supplies", International

iterative procedure for the selection of control pa Telecommunications Energy Conference Re

rameters, which can easily be automated by a cord, 1984, pp. JJ2-339.

computer program. The next phase of this work

will use these results to close the loop on simulated 6. M.P. Schlecht, "Novel Topological Alterna

and hardware converters, t.o verify the small-sign al tives to the Design of a Harmonic-Pree,

model and design procedures. Utility-DC Interface", Power Electronics Spe

cialists' Conference Record, 198J, pp. 206-216.

7. V. Vorperian, "Simplify Your PWM Con

verter Analysis Using the Model of the PWM

References Switch", VPEC Current, a puhlication of the

Virginia Power Electronics Center, December,

1. M. P. Schlecht, "A I ,ine Interfaced Inverter

1988.

with Active Control of The Output Current

Waveform", Power Electronics Specialists'

Conference Record, 1980, pp. 234-241.

8. R. D. Middlebrook, "Input Filter Consider

2. M. .J. Kocher, R. L. Steigerwald, "An AC to ations in Design and Application of Switching

DC Converter with High Quality Input Regulators", IEEE Industry Applications So

ciety Meeting Record, 1976, pp.366-382.

Ridley Engineering Design Center 13

You might also like

- Nonlinear Carrier Control Boosts Power FactorDocument7 pagesNonlinear Carrier Control Boosts Power FactorSv SandeepNo ratings yet

- analysis-of-predictive-control-for-active-power-factor-correctioDocument6 pagesanalysis-of-predictive-control-for-active-power-factor-correctioezloy80No ratings yet

- A Unity Power Factor Converter Using The Synchronous Reference Frame Based Hysteresis Current ControlDocument7 pagesA Unity Power Factor Converter Using The Synchronous Reference Frame Based Hysteresis Current ControlGabriel VilknNo ratings yet

- Synthetic-Ripple Modulator For Synchronous Buck ConverterDocument4 pagesSynthetic-Ripple Modulator For Synchronous Buck ConverterBishoo ShenoudaNo ratings yet

- Cascade Controller For DCDC Buck ConvertorDocument6 pagesCascade Controller For DCDC Buck ConvertorCristóbal Eduardo Carreño MosqueiraNo ratings yet

- 7 Control of Circulating Current in Parallel Three-PhaseDocument7 pages7 Control of Circulating Current in Parallel Three-PhaseRizwan UllahNo ratings yet

- Implementation and Performance Evaluation of A Fast Dynamic Control Scheme For Capacitor-Supported Interline DVRDocument14 pagesImplementation and Performance Evaluation of A Fast Dynamic Control Scheme For Capacitor-Supported Interline DVRRamphani NunnaNo ratings yet

- Angle Controlled Current Regulated Rectifiers For AC/AC ConvertersDocument7 pagesAngle Controlled Current Regulated Rectifiers For AC/AC ConvertersKanomba JavaNo ratings yet

- Performance Analysis of Compensator: A PWM Inverter VARDocument12 pagesPerformance Analysis of Compensator: A PWM Inverter VARRohit Joshi100% (1)

- Iccicct - 122 PDFDocument6 pagesIccicct - 122 PDFGlan DevadhasNo ratings yet

- Self-Oscillating Resonant AC/DC Converter Topology For Input Power-Factor CorrectionDocument11 pagesSelf-Oscillating Resonant AC/DC Converter Topology For Input Power-Factor CorrectionJie99No ratings yet

- 10 1109@pesc 1997 616727 PDFDocument7 pages10 1109@pesc 1997 616727 PDFjeos20132013No ratings yet

- Maintaining DC Voltage with Feedback ControlDocument8 pagesMaintaining DC Voltage with Feedback ControlFatih BurakNo ratings yet

- Ridley 1991Document10 pagesRidley 1991mounicapaluru_351524No ratings yet

- Steady-State Analysis of An Interleaved Boost Converter With Coupled InductorsDocument9 pagesSteady-State Analysis of An Interleaved Boost Converter With Coupled InductorsSasanga HewagamaNo ratings yet

- Generalized Discontinuous DC-link Balancing Modulation Strategy For Three-Level InvertersDocument8 pagesGeneralized Discontinuous DC-link Balancing Modulation Strategy For Three-Level Invertersmeistehaft270No ratings yet

- A Novel High-Efficiency Inverter For Stand-Alone and Grid-Connected SystemsDocument6 pagesA Novel High-Efficiency Inverter For Stand-Alone and Grid-Connected Systemsvinsen letsoinNo ratings yet

- A New, Continuous-Time Model For Current-Mode ControlDocument10 pagesA New, Continuous-Time Model For Current-Mode ControlChuang BiNo ratings yet

- Elimination of Harmonics Using Active Power Filter Based On DQ Reference Frame TheoryDocument5 pagesElimination of Harmonics Using Active Power Filter Based On DQ Reference Frame TheoryseventhsensegroupNo ratings yet

- Sabata Et Al Switching AmpDocument7 pagesSabata Et Al Switching AmpWill ForfangNo ratings yet

- 5 106-6 PDFDocument6 pages5 106-6 PDFCeh DjamelNo ratings yet

- Simulation of Wireless EV Charging with Power Factor CorrectionDocument6 pagesSimulation of Wireless EV Charging with Power Factor Correctionwalidghoneim1970No ratings yet

- Steady-State Analysis of An Interleaved Boost Converter With Coupled InductorsDocument9 pagesSteady-State Analysis of An Interleaved Boost Converter With Coupled InductorsNanda AzizahNo ratings yet

- Neural Network Controllers For Power Factor Correction of AC/DC Switching ConvertersDocument8 pagesNeural Network Controllers For Power Factor Correction of AC/DC Switching ConvertersHuri PalacioNo ratings yet

- Hybrid NPC CHBDocument10 pagesHybrid NPC CHBvahid barahoueiNo ratings yet

- Design of Single-Phase Active Power Filter Using Analogue Cascade ControllerDocument7 pagesDesign of Single-Phase Active Power Filter Using Analogue Cascade Controllerapi-3826450No ratings yet

- Analysis and Design of Three-Phase AC-to-DC Converters With High Power Factor and Near-Optimum FeedforwardDocument10 pagesAnalysis and Design of Three-Phase AC-to-DC Converters With High Power Factor and Near-Optimum FeedforwardTalha SadiqNo ratings yet

- A Novel Switch Mode DC-AC Inverter With Nonlinear Robust Control (IEEE-TIE)Document7 pagesA Novel Switch Mode DC-AC Inverter With Nonlinear Robust Control (IEEE-TIE)Al Bajad MamadNo ratings yet

- Pulsewidth Modulation For Electronic Power Conversion: J. Holtz, Fellow, IEEE Wuppertal University - GermanyDocument18 pagesPulsewidth Modulation For Electronic Power Conversion: J. Holtz, Fellow, IEEE Wuppertal University - GermanyRangesh Babu100% (1)

- Simulations and Experimental Verification of An All-Active Hybrid Converter Arrangement For Filtering Power System Harmonics andDocument6 pagesSimulations and Experimental Verification of An All-Active Hybrid Converter Arrangement For Filtering Power System Harmonics andshiks16No ratings yet

- Performance of Difference PFC Converter For Improved Converter Efficiency: A ReviewDocument6 pagesPerformance of Difference PFC Converter For Improved Converter Efficiency: A ReviewJohn PetersNo ratings yet

- DSP-Based Implementation of An LQR With Integral Action For A Three-Phase Three-Wire Shunt Active Power FilterDocument8 pagesDSP-Based Implementation of An LQR With Integral Action For A Three-Phase Three-Wire Shunt Active Power FilterkhanNo ratings yet

- analysis-and-application-of-a-new-control-method-for-continuousmDocument7 pagesanalysis-and-application-of-a-new-control-method-for-continuousmezloy80No ratings yet

- Single Phase AC To AC Conversion Without Frequency RestrictionsDocument4 pagesSingle Phase AC To AC Conversion Without Frequency RestrictionsTaniyaNo ratings yet

- Ieee Iemdc PaperDocument6 pagesIeee Iemdc Paperheligolwala1No ratings yet

- Unified Constant-Frequency Integration Control of Active Power Filters-Steady-State and DynamicsDocument9 pagesUnified Constant-Frequency Integration Control of Active Power Filters-Steady-State and Dynamics2020EEP006 DEBANJAN DHARANo ratings yet

- InvertersDocument8 pagesInvertersJeffrey A PobladorNo ratings yet

- Strong - 1Document11 pagesStrong - 1PT Orangiro Makmur JayaNo ratings yet

- Voltage-Source Active Power Filter Based On Multilevel Converter and Ultracapacitor DC LinkDocument9 pagesVoltage-Source Active Power Filter Based On Multilevel Converter and Ultracapacitor DC LinkhdinhhienNo ratings yet

- Applications of Artificial Neural Networks in Power ElectronicsDocument5 pagesApplications of Artificial Neural Networks in Power ElectronicsnarakribNo ratings yet

- Direct Power Control of PWM Converter Without Power Source VoltaDocument6 pagesDirect Power Control of PWM Converter Without Power Source Voltabalaji mendiNo ratings yet

- AC-AC (DC Link) - B.H.KWon PDFDocument10 pagesAC-AC (DC Link) - B.H.KWon PDFBui DaiNo ratings yet

- A Novel Soft-Switching Single-Phase AC-DC-AC Converter Using New ZVS-PWM StrategyDocument2 pagesA Novel Soft-Switching Single-Phase AC-DC-AC Converter Using New ZVS-PWM Strategyskumar_61719No ratings yet

- Maximum Power Point Tracking of Coupled Interleaved Boost Converter Supplied SystemDocument10 pagesMaximum Power Point Tracking of Coupled Interleaved Boost Converter Supplied SystemRaveendhra IitrNo ratings yet

- Cascaded Theory - FullDocument14 pagesCascaded Theory - FullTJPRC PublicationsNo ratings yet

- One-Cycle-Controlled Bidirectional AC-to-DC Converter With Constant Power FactorDocument12 pagesOne-Cycle-Controlled Bidirectional AC-to-DC Converter With Constant Power FactorKrishna ReddyNo ratings yet

- Carrier Based Sinusodial PWM Scheme For The Nine Switch ConverterDocument6 pagesCarrier Based Sinusodial PWM Scheme For The Nine Switch ConverterShankar MukalNo ratings yet

- PI ShuntDocument8 pagesPI Shuntdrestaari arkanNo ratings yet

- E3sconf Posei2021 02021Document4 pagesE3sconf Posei2021 02021WilliamNo ratings yet

- Current Mode Control of A Solar Inverter With MPPT ADOPTIVE AlgorithmDocument7 pagesCurrent Mode Control of A Solar Inverter With MPPT ADOPTIVE AlgorithmAnonymous afzpkOo3No ratings yet

- Operation of the LCC-Type Parallel Resonant Converter as a Low Harmonic RectifierDocument12 pagesOperation of the LCC-Type Parallel Resonant Converter as a Low Harmonic RectifierJie99No ratings yet

- Power Factor Correction With Flyback Converter EmpDocument7 pagesPower Factor Correction With Flyback Converter EmpVinícius Vasconcelos Do RêgoNo ratings yet

- Ijaret: International Journal of Advanced Research in Engineering and Technology (Ijaret)Document8 pagesIjaret: International Journal of Advanced Research in Engineering and Technology (Ijaret)IAEME PublicationNo ratings yet

- A Novel Single-Stage Full-Bridge Buck-Boost InverterDocument10 pagesA Novel Single-Stage Full-Bridge Buck-Boost InverteriiscgovindraiNo ratings yet

- Applying PWM to Control Overcurrents at Unbalanced Faults of Forced-Commutated VSCsDocument6 pagesApplying PWM to Control Overcurrents at Unbalanced Faults of Forced-Commutated VSCsJULFANRI SIRAITNo ratings yet

- Current-Source Resonant Converter in Power Factor CorrectionDocument7 pagesCurrent-Source Resonant Converter in Power Factor CorrectionJie99No ratings yet

- ConverterDocument7 pagesConverterjoanelias45No ratings yet

- Comparison of Conventional New Multilevel Inverter Topology PDFDocument5 pagesComparison of Conventional New Multilevel Inverter Topology PDFchristopherNo ratings yet

- OhnumaDocument7 pagesOhnumaHiển TrầnNo ratings yet

- 7._Power_SuppliesDocument29 pages7._Power_SuppliesMeral MeralNo ratings yet

- 3-Phase Pulse Width Modulated (PWM) Inverter: DR - Arkan A.Hussein Power Electronics Fourth ClassDocument10 pages3-Phase Pulse Width Modulated (PWM) Inverter: DR - Arkan A.Hussein Power Electronics Fourth Classmohammed aliNo ratings yet

- Average_model_of_a_three_phase_controlled_rectifier_valid_for_continuous_and_discontinuous_conduction_modesDocument7 pagesAverage_model_of_a_three_phase_controlled_rectifier_valid_for_continuous_and_discontinuous_conduction_modesMeral MeralNo ratings yet

- Solved Problems To Chapter 02 (Singh)Document7 pagesSolved Problems To Chapter 02 (Singh)Julie Hurley100% (1)

- RectifiersDocument27 pagesRectifiersMeral MeralNo ratings yet

- Thyristor Fundamental Characteristics of Thyristors Application Note PDFDocument6 pagesThyristor Fundamental Characteristics of Thyristors Application Note PDFsksarang30% (1)

- Fractional Order Systems-MDPI AG (2019)Document116 pagesFractional Order Systems-MDPI AG (2019)Meral MeralNo ratings yet

- Grid-Forming Power Inverters - Control and Applications-CRC Press (2023) Hassan Haes Alhelou, Nabil Mohammed, Behrooz BahraniDocument307 pagesGrid-Forming Power Inverters - Control and Applications-CRC Press (2023) Hassan Haes Alhelou, Nabil Mohammed, Behrooz BahraniAdinath 02No ratings yet

- EEE302-LAB9Document18 pagesEEE302-LAB9Meral MeralNo ratings yet

- MagneticsTables Con Datos de Núcleos e HilosDocument6 pagesMagneticsTables Con Datos de Núcleos e HilosJavierNo ratings yet

- Presure MeasurementDocument31 pagesPresure MeasurementMalik MuchamadNo ratings yet

- Implementation of High Step-Up Solar Power Optimizer For DC Micro Grid ApplicationDocument5 pagesImplementation of High Step-Up Solar Power Optimizer For DC Micro Grid ApplicationMeral MeralNo ratings yet

- (IEEE Press Series On Power and Energy Systems) Paul C. Krause - Reference Frame Theory - Development and Applications-Wiley-IEEE Press (2020)Document177 pages(IEEE Press Series On Power and Energy Systems) Paul C. Krause - Reference Frame Theory - Development and Applications-Wiley-IEEE Press (2020)Meral MeralNo ratings yet

- Lecture 9-Fluid Pressure MeasurementDocument43 pagesLecture 9-Fluid Pressure MeasurementMeral MeralNo ratings yet

- 10 17694-Bajece 1096188-2343685Document6 pages10 17694-Bajece 1096188-2343685Meral MeralNo ratings yet

- APpNotes - Temperature Coefficient of Resistance For Current SensingDocument5 pagesAPpNotes - Temperature Coefficient of Resistance For Current SensingMeral MeralNo ratings yet

- Dynamic Analysis of The Switched-Inductor Buck-BoostDocument10 pagesDynamic Analysis of The Switched-Inductor Buck-BoostMeral MeralNo ratings yet

- 10 17694-Bajece 1096188-2343685Document6 pages10 17694-Bajece 1096188-2343685Meral MeralNo ratings yet

- Experiment No 1speed Control of DC Motor Single Phase Half Wave Controlled RectifierDocument4 pagesExperiment No 1speed Control of DC Motor Single Phase Half Wave Controlled RectifierMohammed Dyhia Ali100% (2)

- Fundamentals of Backstepping ControlDocument10 pagesFundamentals of Backstepping ControlEstácio LimaNo ratings yet

- Sim U Link SlidesDocument23 pagesSim U Link SlidesMeral MeralNo ratings yet

- Control of Chaotic Behaviour in Parallel-Connected DC-DCDocument5 pagesControl of Chaotic Behaviour in Parallel-Connected DC-DCMeral MeralNo ratings yet

- Dynamic Analysis of The Switched-Inductor Buck-BoostDocument10 pagesDynamic Analysis of The Switched-Inductor Buck-BoostMeral MeralNo ratings yet

- Mariusz - Cichowlas PWM Rectifier Active FilterDocument154 pagesMariusz - Cichowlas PWM Rectifier Active FilterJandfor Tansfg ErrottNo ratings yet

- Converter System Modeling Via MATLAB/SimulinkDocument18 pagesConverter System Modeling Via MATLAB/SimulinkjacarmiNo ratings yet

- Control of Chaotic Behaviour in Parallel-Connected DC-DCDocument5 pagesControl of Chaotic Behaviour in Parallel-Connected DC-DCMeral MeralNo ratings yet

- Euler's Formula and Trigonometry: 1 The Sine and Cosine As Coordinates of The Unit CircleDocument11 pagesEuler's Formula and Trigonometry: 1 The Sine and Cosine As Coordinates of The Unit CircleMeral MeralNo ratings yet

- Control Design of PWM Converters: The User Friendly ApproachDocument145 pagesControl Design of PWM Converters: The User Friendly ApproachMeral MeralNo ratings yet

- 300Mw at 3.3V Supply Audio Power Amplifier With Standby Mode Active HighDocument19 pages300Mw at 3.3V Supply Audio Power Amplifier With Standby Mode Active HighPanagiotis PanagosNo ratings yet

- OTA DesignDocument18 pagesOTA DesignAnandNo ratings yet

- MonteCarlo Simulations Using ADE XLDocument7 pagesMonteCarlo Simulations Using ADE XLDuc DucNo ratings yet

- DC-DC Converters Feedback and ControlDocument220 pagesDC-DC Converters Feedback and ControlNguyên NghĩaNo ratings yet

- Power Supply Design 1 PDFDocument12 pagesPower Supply Design 1 PDFsenkum812002No ratings yet

- Transient Response Counts When Choosing Phase MarginDocument4 pagesTransient Response Counts When Choosing Phase Marginharis13harisNo ratings yet

- 负反馈音频功率放大器电路的稳定性和仿真Document65 pages负反馈音频功率放大器电路的稳定性和仿真4671 WenNo ratings yet

- A New Mathematical Model and Control of A Three-Phase AC-DC Voltage Source ConverterDocument8 pagesA New Mathematical Model and Control of A Three-Phase AC-DC Voltage Source ConverterVenktesh MishraNo ratings yet

- Nonlinear Modeling and Stability Analysis of Resonant DC-DC ConvertersDocument17 pagesNonlinear Modeling and Stability Analysis of Resonant DC-DC Convertersseyed mohsen SalehiNo ratings yet

- 110 TOP CONTROL SYSTEMS questionsDocument24 pages110 TOP CONTROL SYSTEMS questionsEj ParañalNo ratings yet

- Compensator For Control SystemDocument56 pagesCompensator For Control SystembhaskarNo ratings yet

- AD630Document20 pagesAD630saurabhNo ratings yet

- Control Loop CookbookDocument41 pagesControl Loop CookbookLixo4618No ratings yet

- H Robust Control Design For The Nasa Airstar Flight Test VehicleDocument14 pagesH Robust Control Design For The Nasa Airstar Flight Test VehicleAlfa BetaNo ratings yet

- Opamp ProjectDocument10 pagesOpamp Projectbirla_sNo ratings yet

- LMC6462 Dual/LMC6464 Quad Micropower, Rail-to-Rail Input and Output CMOS Operational AmplifierDocument31 pagesLMC6462 Dual/LMC6464 Quad Micropower, Rail-to-Rail Input and Output CMOS Operational Amplifierkevin smithNo ratings yet

- IES EE Topic wise 2001-2008 Control System MCQsDocument101 pagesIES EE Topic wise 2001-2008 Control System MCQsJeetu Raj50% (2)

- An038 en PDFDocument31 pagesAn038 en PDFAshok KumarNo ratings yet

- Improve transient response and noise attenuation with MicroRAMDocument8 pagesImprove transient response and noise attenuation with MicroRAMalexanderNo ratings yet

- An 76Document16 pagesAn 76Şahin BozkurtNo ratings yet

- Dual op amps with no frequency compensationDocument3 pagesDual op amps with no frequency compensationGalang Super'Henecia JuniorNo ratings yet

- Ad8541 8542 8544 PDFDocument20 pagesAd8541 8542 8544 PDFAbel GaunaNo ratings yet

- Laboratory 4 - Feedback and CompensationDocument6 pagesLaboratory 4 - Feedback and CompensationbaymanNo ratings yet

- C and I Lab Manual - 1Document95 pagesC and I Lab Manual - 1iniyavan3119No ratings yet

- Op Amps Driving Capacitive Loads - Analog DevicesDocument11 pagesOp Amps Driving Capacitive Loads - Analog DevicesPreeti MishraNo ratings yet

- Stability and Frequency Compensation: When Amplifiers Go BadDocument12 pagesStability and Frequency Compensation: When Amplifiers Go BadabmatazNo ratings yet

- Nr-220206 Control SystemsDocument8 pagesNr-220206 Control SystemsSrinivasa Rao G100% (1)

- Unit-Iii Frequency Response Analysis Part-A (Two Marks)Document38 pagesUnit-Iii Frequency Response Analysis Part-A (Two Marks)Santhosh Kumar0% (1)

- TIPD128 CapacitiveLoadDrive CapacitiveLoadDriveSolutionUsingAnIsolationResistor Tidu032cDocument28 pagesTIPD128 CapacitiveLoadDrive CapacitiveLoadDriveSolutionUsingAnIsolationResistor Tidu032cLudovico SilvinoNo ratings yet

- TLC271Document70 pagesTLC271poetaenatorNo ratings yet