Professional Documents

Culture Documents

Eee F215 1079 20230808175634

Eee F215 1079 20230808175634

Uploaded by

f20211509Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Eee F215 1079 20230808175634

Eee F215 1079 20230808175634

Uploaded by

f20211509Copyright:

Available Formats

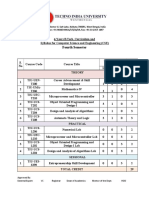

BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, Pilani

Pilani Campus

AUGS/ AGSR Division

Date: 2 August 2023

FIRST SEMESTER 2023-2024

In addition to Part-I (General Handout for all courses appended to the timetable), this portion

gives further specific details regarding the course.

Course Handout

Course No : CS F215/ ECE F215/ EEE F215 / INSTR F215

Course Title : Digital Design

Instructor-in-charge : Dr. Pawan K. Ajmera (pawan.ajmera@pilani.bits-pilani.ac.in)

Instructors for Lecture : Prof. Sudeept Mohan, Dr. Pawan K. Ajmera.

Tutorial Instructors : Dr. GSS Chalapathi, Jyoti Pande, Dr. Pawan K. Ajmera, Dr. Arnab Hazra,

Anubhav Elhence, Nihit Bhatnagar, Buddhi Prakash Sharma, Dr. Y. Sujan,

Dr. Bijoy Krishna Mukherjee, Qaiser Razi.

Practical Instructors : Nihit Bhatnagar, Jyoti Pande, K M Pooja Maurya, Somesh Thanvi,

Balamurugan P, Sumitra, Jeevan Kittur, Divyanshu, Qaiser Razi.

Scope and Objective: The objective of the course is to impart knowledge of the basic

tools for the design of digital circuits and to provide methods and procedures suitable

for a variety of digital design applications.

Textbooks:

T1: M. Moris Mano and Michael D. Ciletti “Digital Design,” PHI, 5th Edition, 2013.

T2: G. Raghurama, S. Gurunarayanan, S. Mohan, Karthik, “Laboratory Manual”, EDD

notes 2007.

Reference Books:

R1: Donald D. Givonne, “Digital Principles and Design” TMH, 2003

R2: W. Stallings, “Computer Organization and Architecture” PHE, 10th Edition, 2015

Please Do Not Print Unless Necessary

BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, Pilani

Pilani Campus

AUGS/ AGSR Division

Course Plan

Lecture

Main Topic Contents Reference

No.

01 Introduction Introduction to Digital systems and characteristics

Number systems Digital, Binary, Octal and Hexadecimal, Number-Base T1:1.1-1.9

02

and codes Conversions, Complements, Signed Binary Numbers.

Logic Gates and Digital Logic Gates, Truth Table, Boolean Algebra, Theorems T1:2.1-2.8

03

Boolean Algebra and Properties, Boolean Functions, Canonical and Std. forms.

Minimization Gate-Level Minimization, The Karnaugh Map Method, T1:3.1-3.8

04-06

Techniques Quine-McCluskey Method

Introduction, Analysis and Design Procedure, Binary Adder- T1:4.1-4.7

Combinational

07-11 Subtractor, Decimal Adder, Binary Multiplier, HDL Models of T1:4.12

Logic Circuits

Combinational Circuits.

Sequential Logic Introduction, Storage Elements: Latches and Flip-Flops. T1:5.1-5.4

12-14

Circuits

Digital Integrated TTL, MOS Logic families and characteristics. T1:10.1-

15-18

Circuits 10.9

Magnitude Comparator, Decoders, Encoders, Multiplexers, T1:4.8-

19-23 MSI Logic Circuits

HDL Models of Combinational Circuits. 4.12

Analysis of Clocked Sequential Circuits, State Reduction, and T1:5.5-5.8

Synchronous

24-28 Assignment, Design Procedure, HDL Models of Sequential

Sequential circuits

Circuits

Introduction, Random-Access Memory, Memory Decoding, T1:7.1-7.8

29-30 Memory and PLDs Error Detection and Correction, Read-Only Memory,

Programmable Logic Array, Programmable Array Logic

Registers and Registers, Shift Registers, Ripple Counters, Synchronous T1:6.1-6.5

31-34

Counters Counters, HDL for Registers and Counters

Design of Digital Register Transfer Level (RTL) Notation, Algorithmic State T1:8.1-8.8

35-37

Systems Machines (ASMs), HDL description.

Memory Memory Hierarchy R2

38-40

Organization

Evaluation Scheme:

EC No. Evaluation Component Duration Marks Date and Time Nature of Component

Quizzes (Best 9 out of

1 10 Min 45 Continuous Close Book

N conducted)

Laboratory

2 180 Min 10 + 35 Continuous Close Book

(Attendance + Lab exam)

3 Mid-Semester Exam 90 Min 90 13/10/23 AN1 Close Book

4 Comprehensive Exam 180 Min 120 18/12/23 FN Open/Close Book

Total 300

Please Do Not Print Unless Necessary

BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, Pilani

Pilani Campus

AUGS/ AGSR Division

Practical

S. No. Name of experiment

1. Familiarization with bench equipment

2. Boolean functions implementation

3. Design of arithmetic circuits (Adder and Subtractors)

4. Implementation of BCD adder

5. Decoders, multiplexers, and de-multiplexers

6. Latches and Flip-Flops

7. Counter design

8. Operation of a 4-bit counter

9. Shift registers

10. Design of sequence detector

11. Comparators and arithmetic logic unit

12. Memories and FPGAs

Assignments: There will be simulation-based assignments, which will be take-home assignments.

Chamber Consultation Hours: To be announced in the class.

Notices: Notices regarding the course will be displayed only on the EEE (FD II) notice

board/NALANDA.

Makeup Policy: Makeup will be granted to extremely genuine cases only, provided the IC has been

informed.

Instructor-in-charge

CS F215/ ECE F215/ EEE F215 / INSTR F215

Please Do Not Print Unless Necessary

You might also like

- DC Motor Speed Controller 1 PDFDocument1 pageDC Motor Speed Controller 1 PDFRyn YahuFNo ratings yet

- Digital Signal Processing: A Practical Guide for Engineers and ScientistsFrom EverandDigital Signal Processing: A Practical Guide for Engineers and ScientistsRating: 4.5 out of 5 stars4.5/5 (7)

- Digital Electronics Lab ManualDocument93 pagesDigital Electronics Lab ManualAnoop MathewNo ratings yet

- Birla Institute of Technology and Science, Pilani Pilani Campus Instruction DivisionDocument4 pagesBirla Institute of Technology and Science, Pilani Pilani Campus Instruction DivisionTrideeb BhattacharyaNo ratings yet

- DDDocument3 pagesDDJAY JANAK MANEKNo ratings yet

- CS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24Document3 pagesCS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24Deepti MishraNo ratings yet

- Bits PilaniDocument3 pagesBits PilaniasdmddamcNo ratings yet

- CS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24Document4 pagesCS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24f20220264No ratings yet

- Ece F215 Digital Design - HandoutDocument3 pagesEce F215 Digital Design - HandoutRishiNo ratings yet

- Page 1 of 2: W.E.F. AY 2018-19Document2 pagesPage 1 of 2: W.E.F. AY 2018-19Jenny BhadouriyaNo ratings yet

- 2.digital Electronics TheoryDocument15 pages2.digital Electronics TheoryYash KuncolienkerNo ratings yet

- Course Handout: Birla Institute of Technology and Science, Pilani Pilani Campus Instruction DivisionDocument3 pagesCourse Handout: Birla Institute of Technology and Science, Pilani Pilani Campus Instruction Divisionsaurjyesh nayakNo ratings yet

- Handout 2016 PDFDocument4 pagesHandout 2016 PDFShubham RohilaNo ratings yet

- Uttarakhand Technical University Dehradun: Study and Evaluation Scheme (B.Tech. Iii Year)Document7 pagesUttarakhand Technical University Dehradun: Study and Evaluation Scheme (B.Tech. Iii Year)Ankit SharmaNo ratings yet

- 15ec751 DSP AlogorithmsDocument40 pages15ec751 DSP AlogorithmsSudheer BabuNo ratings yet

- Department of Electronics and Communication Engineering: Mr.K.Aanandhasaravanan AanandhasaravananDocument4 pagesDepartment of Electronics and Communication Engineering: Mr.K.Aanandhasaravanan AanandhasaravanansarvanmeNo ratings yet

- Digital Electronics and Computer OrganizationDocument3 pagesDigital Electronics and Computer OrganizationSai Prajwal SavanamNo ratings yet

- Handout DSP Ece Eee f434Document2 pagesHandout DSP Ece Eee f434Nitesh JainNo ratings yet

- IT3L3 Digital System Design Lab Credits: 2 Internal Assessment: 25 Marks Lab: 3 Periods/week Semester End Examination: 50 Marks ObjectivesDocument2 pagesIT3L3 Digital System Design Lab Credits: 2 Internal Assessment: 25 Marks Lab: 3 Periods/week Semester End Examination: 50 Marks ObjectivesVyshnavi ThottempudiNo ratings yet

- Diploma IT 3rd Sem SylDocument20 pagesDiploma IT 3rd Sem Sylshriram1082883No ratings yet

- Digital Design: Cs/Eee/Ece /instr F215Document34 pagesDigital Design: Cs/Eee/Ece /instr F215SIDDHANT RAVINDRA KULKARNINo ratings yet

- M.Tech ECE SyllabusDocument4 pagesM.Tech ECE Syllabuspaku deyNo ratings yet

- Academic Course DescriptionDocument8 pagesAcademic Course DescriptionRajalearn2 Ramlearn2No ratings yet

- Number System and CodesDocument300 pagesNumber System and Codes011S6Amit PandeyNo ratings yet

- Course Information Sheet: Sir Syed University of Engineering & Technology Electronic Engineering DepartmentDocument6 pagesCourse Information Sheet: Sir Syed University of Engineering & Technology Electronic Engineering DepartmentAbdullah SohailNo ratings yet

- SY Btech E&TC Syllabus - 2!03!2021Document40 pagesSY Btech E&TC Syllabus - 2!03!2021legad40026No ratings yet

- Course Description Form (CDF) Digital Signal Processing EEE324 - Updated 4Document10 pagesCourse Description Form (CDF) Digital Signal Processing EEE324 - Updated 4Huzaifa YasirNo ratings yet

- Fourth Semester: S. No Course Code Course Title Contact Hrs. / Week Credit L T PDocument10 pagesFourth Semester: S. No Course Code Course Title Contact Hrs. / Week Credit L T Pjiman84235No ratings yet

- Updated Course Outline EE 221 - Digital - Logic - Design - Spring - 2023Document9 pagesUpdated Course Outline EE 221 - Digital - Logic - Design - Spring - 2023Laiqa AliNo ratings yet

- Aei-5th & 6TH Sem23062008Document44 pagesAei-5th & 6TH Sem23062008War MachineNo ratings yet

- Attachment Circular 2023081115025923 Ic 001Document9 pagesAttachment Circular 2023081115025923 Ic 001shivam.cs667No ratings yet

- Birla Institute of Technology & Science, Pilani Hyderabad Campus Second Semester 2018-2019 Course Handout (Part-II) 07-01-2019Document3 pagesBirla Institute of Technology & Science, Pilani Hyderabad Campus Second Semester 2018-2019 Course Handout (Part-II) 07-01-2019PriNo ratings yet

- Gujarat Technological University: Semester - III Subject Name: Digital ElectronicsDocument3 pagesGujarat Technological University: Semester - III Subject Name: Digital ElectronicsBhargavsinh ParmarNo ratings yet

- CS ECE EEE INSTR F241 - Microprocessor Programming Interfacing - Handout 2018 (2 Files Merged)Document5 pagesCS ECE EEE INSTR F241 - Microprocessor Programming Interfacing - Handout 2018 (2 Files Merged)Parth SoodanNo ratings yet

- DDE 1313 Digital Electronics 1 LODocument6 pagesDDE 1313 Digital Electronics 1 LOAhmad FadzlyNo ratings yet

- 05 Unit V DTEDocument217 pages05 Unit V DTEKrunal WaniNo ratings yet

- 311001-Fundamentals of Ict SyllabusDocument10 pages311001-Fundamentals of Ict SyllabusSuriRawatNo ratings yet

- Chhattisgarh Swami Vivekanand Technical University, BhilaiDocument22 pagesChhattisgarh Swami Vivekanand Technical University, Bhilaibheshram janghelNo ratings yet

- Dtev 180916171027Document217 pagesDtev 180916171027vaishnavi biradarNo ratings yet

- Birla Institute of Technology & Science, Pilani Instruction Division FIRST SEMESTER 2017 - 2018 Course Handout (Part Ii)Document2 pagesBirla Institute of Technology & Science, Pilani Instruction Division FIRST SEMESTER 2017 - 2018 Course Handout (Part Ii)prabhatNo ratings yet

- ECE-VII-DSP ALGORITHMS & ARCHITECTURE Part ADocument111 pagesECE-VII-DSP ALGORITHMS & ARCHITECTURE Part AmanjumathgowdaNo ratings yet

- Deca ChoDocument9 pagesDeca ChoTARANGITNo ratings yet

- ECE 6th Sem SyllabusDocument7 pagesECE 6th Sem SyllabusHarsh KumarNo ratings yet

- Digital Communication SystemsDocument4 pagesDigital Communication SystemsMarina KhanNo ratings yet

- EE407 Digital Signal ProcessingDocument2 pagesEE407 Digital Signal ProcessingbibuthomasNo ratings yet

- Ece VII DSP Algorithms Architecture 10ec751 Notes PDFDocument181 pagesEce VII DSP Algorithms Architecture 10ec751 Notes PDFManojNo ratings yet

- ME F320 Engineering OptimizationDocument5 pagesME F320 Engineering OptimizationARYAAN PARIDANo ratings yet

- RTS SyllabusDocument3 pagesRTS SyllabusthejasNo ratings yet

- Syallbus B. Tech CSE First YearDocument12 pagesSyallbus B. Tech CSE First YearRishav RajNo ratings yet

- Digital ElectronicsDocument2 pagesDigital ElectronicsretheeshvkmNo ratings yet

- CS C363Document3 pagesCS C363Aravind KondamudiNo ratings yet

- CP16036Document6 pagesCP16036Sankar TerliNo ratings yet

- B Tech CIVIL Engineering CurriculumDocument36 pagesB Tech CIVIL Engineering CurriculumG Ravi Kiran HSCNo ratings yet

- Digital Design EEE F215 HandoutDocument3 pagesDigital Design EEE F215 HandoutHarshilGargNo ratings yet

- Bits g553 Real Time SystemsDocument2 pagesBits g553 Real Time SystemsUriti Venkata Naga KishoreNo ratings yet

- Don Bosco Institute of Technology: Course Syllabi With CO'sDocument2 pagesDon Bosco Institute of Technology: Course Syllabi With CO'sprashantgeminiNo ratings yet

- CP Je Tele PH1Document2 pagesCP Je Tele PH1Sagnik ChakrabortyNo ratings yet

- UT Dallas Syllabus For Ee4361.501.08f Taught by Issa Panahi (Imp015000)Document2 pagesUT Dallas Syllabus For Ee4361.501.08f Taught by Issa Panahi (Imp015000)UT Dallas Provost's Technology GroupNo ratings yet

- DPSD CS8351 U1 PDFDocument182 pagesDPSD CS8351 U1 PDFPragna SidhireddyNo ratings yet

- Scope and Objective of The CourseDocument3 pagesScope and Objective of The CourseNitu SharmaNo ratings yet

- 3 - Optimizing PLD Counter Designs Using K-Maps (DLP-2021-22)Document16 pages3 - Optimizing PLD Counter Designs Using K-Maps (DLP-2021-22)K BalajiNo ratings yet

- Ee 2254 Linear Integrated Circuits and Applications Anna University Previous Year Question PaperDocument2 pagesEe 2254 Linear Integrated Circuits and Applications Anna University Previous Year Question Paperkibrom atsbhaNo ratings yet

- DatasheetDocument24 pagesDatasheetLuis CordeiroNo ratings yet

- Programmable Unijunction TransistorDocument2 pagesProgrammable Unijunction TransistorBaquiran John Paul Baquiran100% (1)

- Design of Millimeter Wavw Radio - RazaviDocument13 pagesDesign of Millimeter Wavw Radio - Razaviदीपक जोशीNo ratings yet

- C1r17ele102ttpDocument2 pagesC1r17ele102ttpYavar AhadNo ratings yet

- Chapter Three Part IIDocument48 pagesChapter Three Part IIMelese AschalewNo ratings yet

- Gdi PDFDocument4 pagesGdi PDFshoaib nadeemNo ratings yet

- krc110s krc114sDocument4 pageskrc110s krc114szaraidejesusrojasguaiquirimaNo ratings yet

- Logic Gates: IGCSE ® Computer Science © Hodder & Stoughton 2015Document26 pagesLogic Gates: IGCSE ® Computer Science © Hodder & Stoughton 2015Muhammad WaleedNo ratings yet

- FENDER SR 6520-8520PD-11x17Document12 pagesFENDER SR 6520-8520PD-11x17Vital Juan LuisNo ratings yet

- Tutorial Sheet - 8 (Sinusoidal Oscillators)Document3 pagesTutorial Sheet - 8 (Sinusoidal Oscillators)Sulabh KumarNo ratings yet

- Tda 8505Document27 pagesTda 8505Miszcsi MiszcsiNo ratings yet

- 5 Assignment-1Document3 pages5 Assignment-1chandan choudharyNo ratings yet

- Waveform Shaping Circuit: - RC Circuit (High Pass CKT)Document33 pagesWaveform Shaping Circuit: - RC Circuit (High Pass CKT)Samuel PakianathanNo ratings yet

- Clean Boost For Guitar2Document7 pagesClean Boost For Guitar2大石 真義No ratings yet

- MultisimDocument9 pagesMultisim09es80No ratings yet

- MAE307 Applied Electronics (Spring 2013) Mid-Term Exam Class: A B Student ID: Name: Problem 1Document4 pagesMAE307 Applied Electronics (Spring 2013) Mid-Term Exam Class: A B Student ID: Name: Problem 1limjunbeomNo ratings yet

- Module 13 - ADC and DAC ProgrammingDocument29 pagesModule 13 - ADC and DAC Programmingnik ariffNo ratings yet

- Zero-Voltage Switch With Adjustable Ramp: DescriptionDocument11 pagesZero-Voltage Switch With Adjustable Ramp: DescriptionTorzsok JozsefNo ratings yet

- Current Sensing Using OpampDocument2 pagesCurrent Sensing Using Opamplibrian_30005821No ratings yet

- CSE 250 Assignment 01Document8 pagesCSE 250 Assignment 01Ziana BhuiyanNo ratings yet

- GHHGGHDocument54 pagesGHHGGHPro AaishNo ratings yet

- Fm/Am Radio Ic: CD2003GP/GBDocument7 pagesFm/Am Radio Ic: CD2003GP/GBМаксим МульгинNo ratings yet

- TM 610Document112 pagesTM 610sorin2002No ratings yet

- Glossary: - Device That Converts An Information Signal Into A Form Suitable For Propagation Along A ChannelDocument4 pagesGlossary: - Device That Converts An Information Signal Into A Form Suitable For Propagation Along A ChannelReivenNo ratings yet

- RC Circuit and Its ApplicationTerm PaperDocument13 pagesRC Circuit and Its ApplicationTerm PapersummitzNo ratings yet

- Tps 51120Document44 pagesTps 51120peloton10No ratings yet