Professional Documents

Culture Documents

10 Exp

Uploaded by

BT21EE017 Gulshan RajOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

10 Exp

Uploaded by

BT21EE017 Gulshan RajCopyright:

Available Formats

Differential Pulse Code

Modulation Trainer

ST2113

Learning Material

Ver 1.2

An ISO 9001:2008 company

Scientech Technologies Pvt. Ltd.

94, Electronic Complex, Pardesipura, Indore - 452 010 India,

+ 91-731 4211100, : info@scientech.bz , : www.ScientechWorld.com

ST2113

Scientech Technologies Pvt. Ltd. 2

ST2113

Differential Pulse Code Modulation Trainer

ST2113

Table of Contents

1. Safety Instructions 4

2. Introduction 5

3. Features 7

4. Technical Specifications 8

5. Theory 9

6. Differential Pulse Code Modulation 33

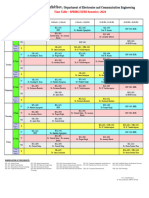

7. ST2113 DPCM Trainer- Brief Description 38

8. Experiments

• Experiment 1 43

Study of Differential Pulse Code Modulation and Demodulation

Technique

• Experiment 2 46

To verify experimentally that DPCM is a Differentiation Process

• Experiment 3 49

To establish voice link using DPCM Technique

9. Frequently Asked Questions 51

10. Warranty 57

11. List of Contents 57

Scientech Technologies Pvt. Ltd. 3

ST2113

Safety Instructions

Read the following safety instructions carefully before operating the instrument. To

avoid any personal injury or damage to the instrument or any product connected to it.

Do not operate the instrument if suspect any damage to it.

The instrument should be serviced by qualified personnel only.

For your safety:

Use proper Mains cord : Use only the mains cord designed for this instrument.

Ensure that the mains cord is suitable for your

country.

Ground the Instrument : This instrument is grounded through the protective

earth conductor of the mains cord. To avoid electric

shock the grounding conductor must be connected to

the earth ground. Before making connections to the

input terminals, ensure that the instrument is properly

grounded.

Observe Terminal Ratings : To avoid fire or shock hazards, observe all ratings and

marks on the instrument.

Use only the proper Fuse : Use the fuse type and rating specified for this

instrument.

Use in proper Atmosphere : Please refer to operating conditions given in the

manual.

1. Do not operate in wet / damp conditions.

2. Do not operate in an explosive atmosphere.

3. Keep the product dust free, clean and dry.

Scientech Technologies Pvt. Ltd. 4

ST2113

Introduction

ST2113, Differential Pulse Code Modulation Trainer is a manifestation of our

increasing efforts to present the modern technology in a best way to the people who

want to unfold the mysteries behind ever increasing communication super highway.

To present it in a best way the trainer incorporates the practical operating frequencies

for sampling, audio processing and data processing that are commonly used in our

public telephone networks.

ST2113, DPCM trainer comprises of following major blocks :

• Audio Signal generator (with sine and square wave output).

• Modulator block which consists of :

a. Difference amplifier with sign manipulation circuit

b. ADC

c. Parallel to serial converter

d. Sample Predictor

• Demodulator block which consists of :

a. Serial to parallel converter

b. Adder and subtractor units

c. Bus latches

d. DAC

e. Output Low pass filter

• Audio input processing circuit.

• Audio output processing circuit.

• Clock and entire control Signal section.

Scientech Technologies Pvt. Ltd. 5

ST2113

Scientech Technologies Pvt. Ltd. 6

ST2113

Features

• Onboard DPCM Transmitter and receiver

• Onboard Signal generator block

• Onboard Audio input & output processing circuits

• Clock and entire control Signal section

• Detailed signal processing circuit with complete data and control signal

flow

Scientech Technologies Pvt. Ltd. 7

ST2113

Technical Specifications

Signal generator block

Functions : Sine and Square

O/P frequency range : 300Hz to 3.4 KHz

Audio blocks : Audio I/P and O/P processing circuits

Control signals : R/W for ADC, reset. Latch enables, OEs.

Sampling frequency : 8 KHz

Total Bits per sample : 5 bits including sign bit

Bandwidth improvement

Compared to 8 bit PCM : 3 bits per sample

Interconnections : 2mm socket

Power Supply : ± 5V, ± 12V DC, 200mA

Dimensions (mm) : W325, H90, D255

Weight : 1 Kg. (approximately)

Scientech Technologies Pvt. Ltd. 8

ST2113

Theory

Pulse Code Modulation (PCM) is an extension of PAM wherein each analogue

sample value is quantized into a discrete value for representation as a digital code

word.

Thus, as shown below, a PAM system can be converted into a PCM system by adding

a suitable analogue-to-digital (A/D) converter at the source and a digital-to-analogue

(D/A) converter at the destination.

PCM is a true digital process as compared to PAM. In PCM the speech signal is

converted from analogue to digital form.

PCM is standardized for telephony by the ITU-T (International Telecommunications

Union - Telecoms, a branch of the UN), in a series of recommendations called the G

series. For example the ITU-T recommendations for out-of-band signal rejection in

PCM voice coders require that 14 dB of attenuation is provided at 4 kHz. Also, the

ITU-T transmission quality specification for telephony terminals requires that the

frequency response of the handset microphone has a sharp roll-off from 3.4 kHz.

In quantization the levels are assigned a binary codeword. All sample values falling

between two quantization levels are considered to be located at the centre of the

quantization interval. In this manner the quantization process introduces a certain

amount of error or distortion into the signal samples. This error known as quantization

noise is minimized by establishing a large number of small quantization intervals. Of

course, as the number of quantization intervals increase, so must the number or bits

increase to uniquely identify the quantization intervals. For example, if an analogue

voltage level is to be converted to a digital system with 8 discrete levels or

quantization steps three bits are required. In the ITU-T version there are 256

quantization steps, 128 positive and 128 negative, requiring 8 bits. A positive level is

represented by having bit 8 (MSB) at 0, and for a negative level the MSB is 1.

Pulse code modulation, more popularly known as PCM is the most widely used digital

modulation system. It is a widely known fact that the analog modulation systems are

most prone to the noise present in the channel and receiver. As we will see further that

the digital modulation systems are far less sensitive to noise as compared to analog

modulation. The basis of digital modulation systems lies on pulse modulation i.e. a

particular characteristic of the pulse is varied in accordance with the information

signal.

In Pulse Modulation, analog message is transmitted in discrete time. First of all,

sampling of the message signal should be performed. Considering the sampling

process, the sampled signal appears as a train of samples which is a form of PAM

(Pulse Amplitude Modulation) signal. When M levels are used to quantize this signal,

this modulation is called M-PAM. If those pulses were converted to digital numbers,

then the train of numbers so generated would be called as Pulse Code Modulated –

PCM signal. In PCM, modulation process is executed in three steps:

1. Sampling

2. Quantizing

3. Coding

These steps are shown in Figure 1 with a block diagram:

Scientech Technologies Pvt. Ltd. 9

ST2113

Figure 1

PCM block Diagram

Figure 2

In PCM, the information signal x(t) is first sampled with the appropriate

sampling frequency (sampling frequency fs ≥ 2×highest frequency of the

information signal (fx) ), then the sampled levels are quantized to appropriate

quantization levels. In the last step, each quanta level is demonstrated by a

two-code word, that is by a finite number of {0,1} sequence. After this step,

the signal is called as PCM wave.

Scientech Technologies Pvt. Ltd. 10

ST2113

Pulse Code Modulation

Steps in Pulse Code Modulation:

Sampling:

The signals which are required to be transmitted as information is known as

information signal and in the case of voice communication this will be a continuously

changing signal containing speech information. The aim of the kit is to transmit the

signals in digital form and is to reproduce this information signal in analog form at the

receiving end of the communication system with the help of sampling and

reconstruction trainer.

In the exercises to follow, you will simulate audio signal by a 1 kHz test signal

provided On-board. The repetitive, non-changing waveform does not contain

information. Provided the frequency of the test-signal lies within the frequency range

which an information signal will occupy, a test signal of this type can be extremely

helpful in system analysis and testing.

The voice signals are limited to the range 300 Hz to 3.4 kHz, a 1 kHz frequency fits

conveniently in this range and can be used to demonstrate and test many techniques

used in communication system.

Theory of sampling:

The signals we use in the real world, such as our voice, are called "analog" signals.

To process these signals for digital communication, we need to convert analog signals

to "digital" form. While an analog signal is continuous in both time and amplitude, a

digital signal is discrete in both time and amplitude. To convert continuous time

signal to discrete time signal, a process is used called as sampling. The value of the

signal is measured at certain intervals in time. Each measurement is referred to as a

sample.

Principle of sampling:

Consider an analogue signal x(t) that can be viewed as a continuous function of time,

as shown in figure 3. We can represent this signal as a discrete time signal by using

values of x(t) at intervals of nTs to form x(nTs) as shown in figure 3. We are

"grabbing" points from the function x(t) at regular intervals of time, Ts, called the

sampling period.

Scientech Technologies Pvt. Ltd. 11

ST2113

Basic Sampling Process

Figure 3

Sampling of signal at sampling interval (period) Ts

Figure 4

Figure 4 depicts the sampling of a signal at regular interval (period) t=nTs where n is

an integer. The sampling signal is a regular sequence of narrow pulses δ (t) of

amplitude 1.Figure 5 shows the sampled output of narrow pulses δ (t) at regular

interval of time.

Scientech Technologies Pvt. Ltd. 12

ST2113

Sampled Output of narrow pulses δ (t)

Figure 5

The time distance Ts is called sampling interval or sampling period, fs=1/Ts is called

as sampling frequency (Hz or samples/sec), also called sampling rate.

The Sampling Theorem:

The Sampling Theorem states that a signal can be exactly reproduced if it is sampled

at a frequency Fs, where Fs is greater than twice the maximum frequency Fmax in the

signal.

Fs > 2· Fmax

The frequency 2· Fmax is called the Nyquist sampling rate. Half of this value, Fmax, is

sometimes called the Nyquist frequency.

The sampling theorem is considered to have been articulated by Nyquist in 1928 and

mathematically proven by Shannon in 1949. Some books use the term "Nyquist

Sampling Theorem", and others use "Shannon Sampling Theorem". They are in fact

the same sampling theorem.

The sampling theorem clearly states what the sampling rate should be for a given

range of frequencies. In practice, however, the range of frequencies needed to

faithfully record an analog signal is not always known beforehand. Nevertheless,

engineers often can define the frequency range of interest. As a result, analog filters

are sometimes used to remove frequency components outside the frequency range of

interest before the signal is sampled.

For example, the human ear can detect sound across the frequency range of 20 Hz to

20 kHz. According to the sampling theorem, one should sample sound signals at least

at 40 kHz in order for the reconstructed sound signal to be acceptable to the human

ear. Components higher than 20 kHz cannot be detected, but they can still pollute the

sampled signal through aliasing. Therefore, frequency components above 20 kHz are

removed from the sound signal before sampling by a band-pass or low-pass analog

filter.

Scientech Technologies Pvt. Ltd. 13

ST2113

Nyquist Criterion

As shown-in the figure 6 the lowest sampling frequency that can be used without the

sidebands overlapping is twice the highest frequency component present in the

information signal. If we reduce this sampling frequency even further, the sidebands

and the information signal will overlap and we cannot recover the information signal

simply by low pass filtering. This phenomenon is known as fold-over distortion or

aliasing.

Nyquist Criterion (Sampling Theorem)

Figure 6

The Nyquist criteria states that a continuous signal band limited to Fm Hz can be

completely represented by and reconstructed from the samples taken at a rate greater

than or equal to 2Fm samples/second.

This minimum sampling frequency is called as Nyquist Rate i.e. for faithful

reproduction of information signal fs > 2 fm.

For audio signals the highest frequency component is 3.4 KHz.

So, Sampling Frequency ≥ 2 fm

≥ 2 x 3.4 KHz

≥ 6.8 KHz

Practically, the sampling frequency is kept slightly more than the required rate. In

telephony the standard sampling rate is 8 KHz. Sample quantifies the instantaneous

value of the analog signal point at sampling point to obtain pulse amplitude output.

Scientech Technologies Pvt. Ltd. 14

ST2113

Nyquist’s Uniform Sampling Theorem for Low pass Signal:

Part - I If a signal x(t) does not contain any frequency component beyond W Hz, then

the signal is completely described by its instantaneous uniform samples with sampling

interval (or period ) of Ts < 1/(2W) sec.

Part – II The signal x(t) can be accurately reconstructed (recovered) from the set of

uniform instantaneous samples by passing the samples sequentially through an ideal

(brick-wall) low pass filter with bandwidth B, where W ≤ B < fs – W and fs = 1/(Ts).

As the samples are generated at equal (same) interval (Ts) of time, the process of

sampling is called uniform sampling. Uniform sampling, as compared to any non-

uniform sampling, is more extensively used in time-invariant systems as the theory of

uniform sampling (either instantaneous or otherwise) is well developed and the

techniques are easier to implement in practical systems.

Sampling Techniques:

There are three types of sampling techniques as under:

1. Ideal sampling or Instantaneous sampling or Impulse sampling

2. Natural sampling

3. Flat top sampling

1. Ideal sampling or Instantaneous sampling or Impulse sampling:

For the proof of sampling theorem we use ideal or impulse sampling.

The concept of ‘instantaneous’ sampling is more of a mathematical abstraction as no

practical sampling device can actually generate truly instantaneous samples (a

sampling pulse should have non-zero energy). However, this is not a deterrent in

using the theory of instantaneous sampling, as a fairly close approximation of

instantaneous sampling is sufficient for most practical systems. To contain our

discussion on Nyquist’s theorems, we will introduce some mathematical expressions.

If x(t) represents a continuous-time signal, the equivalent set of instantaneous uniform

samples {x(nTs)} may be represented as:

{x(nTs)} = Σ x(t).δ(t- nTs)

where x(nTs) = x(t) =nTs , δ(t) is a unit pulse singularity function and ‘n’ is an

integer

Scientech Technologies Pvt. Ltd. 15

ST2113

Ideal sampling process

Figure 7(a)

Figure 7(b)

Scientech Technologies Pvt. Ltd. 16

ST2113

2. Natural sampling:

In the analogue-to-digital conversion process an analogue waveform is sampled to

form a series of pulses whose amplitude is the amplitude of the sampled waveform at

the time the sample was taken. In natural sampling the pulse amplitude takes the

shape of the analogue waveform for the period of the sampling pulse as shown in

figure 8.

Figure 8

3. Flat Top sampling:

After an analogue waveform is sampled in the analogue-to-digital conversion process,

the continuous analogue waveform is converted into a series of pulses whose

amplitude is equal to the amplitude of the analogue signal at the start of the sampling

process. Since the sampled pulses have uniform amplitude, the process is called flat

top sampling as shown in figure 9.

Figure 9

Scientech Technologies Pvt. Ltd. 17

ST2113

Note that due to the flat-top pulses, the spectrum of the sampled signal is distorted.

The narrower the pulse width lesser the distortion.

The original signal may be obtained by using a low-pass filter with a characteristic

which inverts the distortion.

Another important process in the PCM process is known as Quantization.

Sample & Hold circuit:

In electronics, a sample and hold circuit is used to interface real-world signals, by

changing analogue signals to a subsequent system. The purpose of this circuit is to

hold the analogue value steady for a short time while the converter or other following

system performs some operation that takes a little time.

Sampling mode:

In this mode, the switch is in the closed position and the capacitor charges to the

instantaneous input voltage.

Hold mode:

In this mode, the switch is in the open position. The capacitor is now disconnected

from the input. As there is no path for the capacitor to discharge, it will hold the

voltage on it just before opening the switch. The capacitor will hold this voltage till

the next sampling instant.

Sample and Hold Waveform

Figure 10

Now, from figure 10 the area under the curve (which is equivalent to the signal

power) is greater and so the filter output amplitude and quality of reproduced signal is

improved.

In most circuits, a capacitor is used to store the analogue voltage and an electronic

switch or gate is used to alternately connect and disconnect the capacitor from the

analogue input. The rate at which this switch is operated is the sampling rate of the

system.

In a sample and hold circuit the switch opens for a very short duration. The sample

and hold circuit integrates for a short duration charge into a capacitor.

Scientech Technologies Pvt. Ltd. 18

ST2113

The 'hold' facility can be provided by a capacitor, when the switch connects the

capacitor to PAM output it charges to the instantaneous value.

A buffered sample and hold circuit consists of unit gain buffer preceding and

succeeding the charging capacitor. The high input impedance of the preceding buffer

prevents the loading of the message source and also ensures that the capacitor charges

by a constant rate irrespective of the source impedance see figure 11(a).

Sample Hold Circuit

Figure 11(a)

The high input impedance of the succeeding buffer prevents the charging from the

capacitor due to loading and hence the capacitor can hold the charge for infinite time,

at least theoretically. However, small leakage current through the capacitor dielectric

into '+'ve input of second buffer is always present which causes gradual charge loss.

The rate of change of voltage with respect to time dv / dt is called as droop rate and is

important parameter in sample and Hold circuit design. The sample and hold

waveform is shown in figure 11(b).

Sample and hold wave form

Figure 11(b)

Scientech Technologies Pvt. Ltd. 19

ST2113

Important Parameters of Sample & Hold Circuit

1. Aperture time:

The aperture time is defined as the delay time between the beginnings of the hold

command to the time the capacitor voltage ceases to follow the information signal.

Hence the hold value is different from the true sample value. The aperture time cannot

be reducing to zero because on application of finite time taken by a switch to close &

open on application of the hold signal. Therefore a small value of aperture time is

sought after.

Timing Diagram for Sample and Hold Circuit

Figure 12

2. Acquisition Time:

In sample mode, it takes finite time for the capacitor to charge to the information

signal value depending on the RC time constant. This is called as the acquisition time.

The acquisition time is dependent on the current flowing from the input buffer

through switch and hence on RC time constant. The maximum acquisition time occurs

when the capacitor voltage has to change by the full amplitude of the information

signal.

3. Droop Rate:

As it has been discussed earlier, the presence of leakage current through capacitor

dielectric to +ve input of succeeding buffer causes charge loss of capacitor. Hence the

voltage level at the output falls with in time. This rate of change of voltage with

respect to time dv/dt is known as droop rate. Over value of droop rate is desirable as

the circuit should be able to maintain the sample at a relatively constant level until the

next sample.

Scientech Technologies Pvt. Ltd. 20

ST2113

4. Feed Through:

At high frequencies, the stray capacitance within the switch causes some of the input

signal to appear at the output during the hold state (switch open). The fraction of input

signal appearing at the output of sample and hold circuit is called feed through.

The sample and hold feature provides both problem and benefit will be seen

afterwards.

Quantization:

In quantization the levels are assigned a binary codeword. All sample values falling

between two quantization levels are considered to be located at the centre of the

quantization interval. In this manner the quantization process introduces a certain

amount of error or distortion into the signal samples. This error known as quantization

noise is minimized by establishing a large number of small quantization intervals. Of

course, as the number of quantization intervals increase, so must the number or bits

increase to uniquely identify the quantization intervals. For example, if an analogue

voltage level is to be converted to a digital system with 8 discrete levels or

quantization steps three bits are required. In the ITU-T version there are 256

quantization steps, 128 positive and 128 negative, requiring 8 bits. A positive level is

represented by having bit 8 (MSB) at 0 and for a negative level the MSB is 1.

This is the process of setting the sample amplitude, which can be continuously

variable to a discrete value. Look at Uniform Quantization first, where the discrete

values are evenly spaced.

The operation of quantization is represented in figure 13. Here we contemplate a

signal m (t) whose excursion is confined to the range from VL to VH. We have divided

this total range into M equal intervals each of size S. Accordingly S, called the step

size, is S = (VH - VL)/M. In figure 13 we show the specific example in which M = 8. In

the center of each of these steps we locate quantization levels m0, m1,..., m7. The

quantized signal mq(t) is generated in the following way: Whenever m(t) is in the

range Δ0, the signal mq(t) maintains the constant level m0; whenever m(t) is in the

range Δ1, mq(t) maintains the constant level m1; and so on. Thus the signal mq(t) will

at all times be found at one of the levels mo, ml, ..., m7. The transition in mq (t) from

mq(t) = m0 to mq(t) = m1 is made abruptly when m(t) passes the transition level L01

which is midway between m0 and m1 and so on. To state the matter in an alternative

fashion, we say that, at every instant of time, mq(t) has the value of the quantization

level to which m(t) is closest. Thus the signal mq(t) does not change at all with time or

it makes a "quantum" jump of step size S. Note the disposition of the quantization

levels in the range from VL to VH. These levels are each separated by an amount S, but

the separation of the extremes VL and VH each from its nearest quantization level is

only S/2. Also, at every instant of time, the quantization error m (t) - mq(t) has a

magnitude which is equal to or less than S/2.

Scientech Technologies Pvt. Ltd. 21

ST2113

Process of Quantization of an Analog Signal

Figure 13

We see, therefore, that the quantized signal is an approximation to the original signal.

The quality of the approximation may be improved by reducing the size of the steps,

thereby increasing the number of allowable levels. Eventually, with small enough

steps, the human ear or the eye will not be able to distinguish the original from the

quantized signal. To give the reader an idea of the number of quantization levels

required in a practical system, we note that 256 levels can be used to obtain the

quality of commercial color TV, while 64 levels gives only fairly good color TV

performance. These results are also found to be valid when quantizing voice.

Uniform Quantization

We assume that the amplitude of the signal m(t) is confined to the range (-mp, +mp ).

This range (2mp) is divided into L levels, each of step size δ, given by

δ = 2 mp / L

A sample amplitude value is approximated by the midpoint of the interval in which it

lies. The input/output characteristic of a uniform quantizer is shown figure 14.

Scientech Technologies Pvt. Ltd. 22

ST2113

Figure 14

The conventional, practical digital-to-analog converter (DAC) does not output a

sequence of impulses (such that, if ideally low-pass filtered, result in the original

signal before sampling) but instead output a sequence of piecewise constant values or

rectangular pulses. This means that there is an inherent effect of the zero-order hold

on the effective frequency response of the DAC resulting in a mild roll-off of gain at

the higher frequencies (a 3.9224 dB loss at the Nyquist frequency). This zero-order

hold effect is a consequence of the hold action of the DAC and is not due to the

sample and hold that might precede a conventional ADC as is often misunderstood.

The DAC can also suffer errors from jitter, noise, slewing, and non-linear mapping of

input value to output voltage.

Each binary word defines a particular narrow range of amplitude level. The sampled

value is then approximated to the nearest amplitude level. The sample is then assigned

a code corresponding to the amplitude level, which is then transmitted.

This process is called as Quantization & it is generally carried out by the A/D

converter.

Scientech Technologies Pvt. Ltd. 23

ST2113

Quantization & Encoding of a sampled signal

Figure 15

The PCM code generated after Quantization process:

010 101 111 111 110 010 001 010 010

Scientech Technologies Pvt. Ltd. 24

ST2113

There are two important problems associated with quantization.

a. Quantization noise :

As we have seen the signal is approximated to the nearest level (step). Since the levels

are discrete where as the signal is continuous, the discrepancy creeps in.

The difference between the analog signal value & its approximated one (quantized

one) is random & unpredictable. This is a sort of unwanted, unpredictable, random

signal which accompanies the information signal and is termed as 'Quantization

noise'.

The difference between m (t) - mq(t) can be regarded as noise and is called

quantization noise. Hence, the received signal is not a perfect replica of the trans-

mitted signal m (t). The difference between them is due to errors caused by additive

noise and quantization noise.

Quantization Noise

Figure 16

Quantization noise can be reduced by increasing the number of levels, hence reducing

the approximation. But it can never be eliminated. Increasing the number of levels to

reduce quantization noise has the effect of increasing the number of bits. But nothing

comes without price. Increasing the number of bits to represent a sample increases the

system's bandwidth requirement.

b. Finite sampling time of A/D converter :

Another problem associated with quantization is that the A/D Converter requires

finite time to convert the analog information to digital data. The A/D Converter

requires that the value at its input, remain unchanged till the conversion is complete.

But in practice, the duration of sampled pulse is much smaller than the A/D

converter's sampling time.

Scientech Technologies Pvt. Ltd. 25

ST2113

Bit step Analog to digital converter

Figure 17

This problem can be overcome by using a sample & hold circuit prior to A/D

converter output. The sample & hold circuitry holds the sample value till the next

sample. The encoding method described above is called as uniform encoding i.e. the

quantization levels are uniform for all the amplitude range. But this method of

encoding has disadvantages of its own. The quantization noise plays havoc with the

low level signals because the % approximation compared to the signal amplitude is

very high. This causes a great amount of distortion at the receiver for low level

signals. Also the quieter part of music or speech could become severely distorted &

would make them unpleasant to listen.

To overcome this problem, a non-uniform encoding scheme is used. Here the

quantization levels are clear together for low level than they are for the high levels.

This has an effect of compression on the extreme ends of the signal. The input/output

characteristics for compression signal passed through a comparator network 'prior to

compression (See figure 18). This process is called compression.

Scientech Technologies Pvt. Ltd. 26

ST2113

An input output characteristic providing compression

Figure 18

The opposite effect is utilized at the receiver to undo the effect of compression, is

termed as expanding. The two processes are combined are known as compounding

this feature is not provided on trainer but you should be aware of its existence. Some

error correcting codes & synchronization can also be transmitted along with the

information signal.

At receiver, the data is decoded by the D/A converter; the recovered samples are

filtered & reconstructed to provide the original waveform.

Various channels can be multiplexed in time domain i.e. the information data from

various sources are sequentially transmitted over the same transmission medium e.g.

Let us assume a 3 channel PCM system. The system samples 0-2 samples sequentially

providing 3 samples to be converted to 3 "n" bit words. These three n bit words forms

the basis of a frame. The frame contains these three n bit words also contains some

synchronization & reference positioning information.

On more complex multi-channel systems, control & routing information have to be

included. This information is termed as signaling information. If all these information

can not be fitted in a single frame, a separate channel is used for signaling &

synchronization information.

In Europe, a 30 channel PCM System is followed which is specified by CCITT

(International Radio Consultative Committee). Besides these channels, two separate

channels are used for signaling & synchronization information. Here the multi frame

consists of 16 frames.

Multi Frame:

When the number of bits in allocated channels is insufficient to cope with the

synchronization & signaling information then it is spread on defined channels over a

number of frames. This sequence of frames is known as a Multi Frames.

Scientech Technologies Pvt. Ltd. 27

ST2113

Pulse Code Modulation:

A signal, which is to be quantized prior to transmission, is usually sampled first. The

quantization is used to reduce the effects of noise, and the sampling allows us to time-

division multiplex a number of messages if we choose to do so. The combined

operations of sampling and quantizing generate a quantized PAM waveform, that is, a

train of pulses whose amplitudes are restricted to a number of discrete magnitudes.

We may, if we choose, transmit these quantized sample values directly. Alternatively

we may represent each quantized level by a code number and transmit the code

number rather than the sample value itself. The merit of so doing will be developed in

the subsequent discussion. Most frequently the code number is converted, before

transmission, into its representation in binary arithmetic, i.e., base-2 arithmetic. The

digits of the binary representation of the code number are transmitted as pulses.

Hence the system of transmission is called (binary) pulse code modulation (PCM).

We review briefly some elementary points about binary arithmetic. The binary system

uses only two digits, 0 and 1. An arbitrary number N is represented by the sequence...

k2 k1I k0, in which the k's are determined from the equation

N =. + k222 + k121 + k020

with the added constraint that each k has the value 0 or 1. The binary representations

of the decimal numbers 0 to 15 are given in table 1. Observe that to represent the four

Binary Codes for 16 Level Quantization

Table 1

(Decimal) numbers 0 to 3; we need only two binary digits k1 and k0. For the eight

(decimal) numbers from 0 to 7 we require only three binary places, and so on. In

general, if M numbers 0, 1, M - 1 are to be represented, then an N binary digit

sequence kN-1 ... k0 is required, where M = 2N.

Scientech Technologies Pvt. Ltd. 28

ST2113

Sampling and Binary Coding of an Analog Signal (PCM)

Figure 19

The essential features of binary PCM are shown in figure 19. We assume that the

analog message signal m (t) is limited in its excursions to the range from - 4 to +4

volts. We have set the step size between quantization levels at 1 volt. Eight

quantization levels are employed, and these are located at - 3.5, - 2.5, +3.5volts. We

assign the code number 0 to the level at - 3.5volts, the code number 1 to the level at -

2.5volts, etc., until the level at + 3.5volts, which is assigned the code number 7. Each

code number has its representation in binary arithmetic ranging from 000 for code

number 0 to 111 for code number 7.

In figure 19, in correspondence with each sample, we specify the sample value, the

nearest quantization level, and the code number and its binary representation. If we

were transmitting the analog signal, we would transmit the sample values 1.3, 3.6,

2.3, etc. If we were transmitting the quantized signal, we would transmit the

quantized sample values 1.5, 3.5, 2.5, etc. In binary PCM we transmit the binary

representations 101, Ill, 110, etc.

Scientech Technologies Pvt. Ltd. 29

ST2113

Electrical pulses for Binary Codes in PCM

Figure 20

We may represent the binary digits by electrical pulses in order to transmit the code

representations of each quantized level over a communication channel. Such a

representation is shown in figure 20. Pulse time slots are indicated at the top of the

figure, and, as shown in figure 20 a, a pulse represents the binary digit 1, while the

binary digit 0 is represented by the absence of a pulse. The row of three-digit binary

numbers given in figure 20 is the binary representation of the sequence of quantized

samples in figure 19. Hence the pulse pattern in figure 20a is the (binary) PCM

waveform that would be transmitted to convey to the receiver the sequence of

quantized samples of the message signal m (t) in figure 19. Each three-digit binary

number that specifies a quantized sample value is called a word. The spaces between

words allow for the multiplexing of other messages.

At the receiver, in order to reconstruct the quantized signal, all that is required is that

a determination be made, within each pulse time slot, about whether a pulse is present

or absent. The exact amplitude of the pulse is not important. There is an advantage in

making the pulse width as wide as possible since the pulse energy is thereby

increased and it becomes easier to recognize a pulse against the background noise.

Suppose then that we eliminate the guard time τg between pulses. We would then

have the waveform shown in figure 20 b.

We would be rather hard put to describe this waveform as either a sequence of

positive pulses or of negative pulses. The waveform consists now of a sequence of

transitions between two levels. When the waveform occupies the lower level in a

particular time slot, a binary 0 is represented, while the upper voltage level represents

a binary 1.Suppose that the voltage difference of 2 V volts between the levels of the

waveform of figure 20 b is adequate to allow reliable determination at the receiver of

which digit is being transmitted. We might then arrange, say, that the waveform make

excursions between 0 and 2 V volts or between - V volts and + V volts. The former

waveform will have a dc component, the latter waveform will not. Since the dc

component wastes power and contributes nothing to the reliability of transmission,

the latter alternative is preferred and is indicated in figure 20 b.

Scientech Technologies Pvt. Ltd. 30

ST2113

The PCM System:

The Encoder:

A PCM communication system is represented in figure 21. The analog signal m (t) is

sampled, and these samples are subjected to the operation of quantization. The

quantized samples are applied to an encoder. The encoder responds to each such

sample by the generation of a unique and identifiable binary pulse (or binary level)

pattern. In the example of figures 19 and 20, the pulse pattern happens to have a

numerical significance that is same as the order assigned to the quantized levels.

However, this feature is not essential. We could have assigned any pulse pattern to

any level. At the receiver, however, we must be able to identify the level from the

pulse pattern. Hence it is clear that not only does the encoder number the level, it also

assigns to it an identification code.

A PCM Communication System

Figure 21

The combination of the quantizer and encoder in the gray outlined box of figure 21 is

called an analog-to-digital converter, usually abbreviated A/D converter. In

commercially available A/D converters there is normally no sharp distinction

between that portion of the electronic circuitry used to do the quantizing and that

portion used to accomplish the encoding. In summary, then, the A/D converter

accepts an analog signal and replaces it with a succession of code symbols, each

symbol consisting of a train of pulses in which each pulse may be interpreted as the

representation of a digit in an arithmetic system. Thus the signal transmitted over the

communications channel in a PCM system is referred to as a digitally encoded signal.

The Decoder:

When the digitally encoded signal arrives at the receiver (or repeater), the first

operation to be performed is the separation of the signal from the noise, which has

been added during the transmission along the channel. As noted previously,

separation of the signal from the noise is possible because of the quantization of the

signal. Such an operation is again an operation of requantization; hence the first

block in the receiver in figure 21 is termed a quantizer. A feature which eases the

Scientech Technologies Pvt. Ltd. 31

ST2113

burden on this quantizer is that for each pulse interval it has only to make the

relatively simple decision of whether a pulse has or has not been received or which of

two voltage levels has occurred. Suppose the quantized sample pulses had been

transmitted instead, rather than the binary-encoded codes for such samples. Then this

quantizer would have had to yield, in each pulse interval, not a simple yes or no

decision, but rather a more complicated determination about which of the many

possible levels had been received. In the example of figure 21, if a quantized PAM

signal had been transmitted, the receiver quantizer would have to decide which of the

levels 0 to 7 was transmitted, while with a binary PCM signal the quantizer need only

distinguish between two possible levels. The relative reliability of the yes or no

decision in PCM over the multi valued decision required for quantized PAM

constitutes an important advantage for PCM.

The receiver quantizer then, in each pulse slot, makes an educated and sophisticated

estimate and then decides whether a positive pulse or a negative pulse was received

and transmits its decisions, in the form of a reconstituted or regenerated pulse train, to

the decoder. (If repeater operation is intended, the regenerated pulse train is simply

raised in level and sent along the next section of the transmission channel.) The

decoder, also called a digital-to-analog (D/A) converter, performs the inverse

operation of the encoder. The decoder output is the sequence of quantized multilevel

sample pulses. The quantized PAM signal is now reconstituted. It is then filtered to

reject any frequency components lying outside of the base band. The final output

signal m'(t) is identical with the input m (t) except for quantization noise and the

occasional error in yes-no decision making at the receiver due to the presence of

channel noise.

In telephony, a standard audio signal for a single phone call is encoded as 8000

analog samples per second, of 8 bits each, giving a 64k bit/s digital signal known as

DS0. The default signal compression encoding on a DS0 is either μ-law (mu-law)

PCM (North America and Japan) or a-law PCM (Europe and most of the rest of the

world). These are logarithmic compression systems where a 12 or 13 bit linear PCM

sample number is mapped into an 8-bit value. This system is described by

international standard G.711.

Differential (or Delta) pulse-code modulation (DPCM) encodes the PCM values as

differences between the current and the previous value. For audio this type of

encoding reduces the number of bits required per sample by about 25% compared to

PCM. Adaptive DPCM (ADPCM) is a variant of DPCM that varies the size of the

quantization step, to allow further reduction of the required bandwidth for a given

signal-to-noise ratio. Where circuit costs are high and loss of voice quality is

acceptable, it sometimes makes sense to compress the voice signal even further. An

ADPCM algorithm is used to map a series of 8 bit PCM samples into a series of 4 bit

ADPCM samples. In this way, the capacity of the line is doubled. The technique is

detailed in the G.726 standard. Later it was found that even further compression was

possible and additional standards were published. Some of these international

standards describe systems and ideas that are covered by privately owned patents and

thus use of these standards requires payments to the patent holders. Some ADPCM

techniques are used in Voice over IP communications.

Scientech Technologies Pvt. Ltd. 32

ST2113

Differential Pulse-Code Modulation

In Practical system bandwidth requirement for transformation of information is very

important aspect, since if bandwidth requirement is less, more number of channels can

be multiplexed on a single line and full utility of transmitting media is extracted out.

In a system in which a base band signal m (t) is transmitted by sampling, there is

available a scheme of transmission which is an alternative to transmitting the sample

values (quantized or not) at each sampling time. We can instead, at each sampling

time, say the kth sampling time, transmit the difference between the sample value m(k)

at sampling time k and the sample value m(k - 1) at time k - 1. If such changes are

transmitted, then simply by adding up (accumulating) these changes we shall generate

at the receiver a waveform identical in form to m (t). There can be a difference in dc

components between transmitted and received signals but, almost invariably; such dc

components are of no interest.

Such a differential scheme has special merit when these differences are to be

transmitted by pulse code modulation. For we may well anticipate that the differences

m(k) - m(k - 1) will be smaller than the sample values themselves. Hence fewer levels

will be required to quantize the difference than are required to quantize m (k) and

correspondingly, fewer bits will be needed to encode the levels. For example,

suppose that m (k) extends over a range VH - VL, and using PCM, m (k) is encoded

using 28 = 256 levels. Then the step size is S = (VH - VL)/28, that is VH- VL = 256S. If,

however, the difference signal m (k) - m (k - 1) extends only over the range ± 2S then

the quantized levels needed are at ± O.5S and at ± l.5S. There are now only four

levels and two bits per sample difference are adequate.

In an analog system, where we are able, at least in principle, to transmit the

differences exactly, the differential system described above would operate in

accordance with our description. In a digital (quantized) system we encounter the

complication that the differences are not generally transmitted exactly because of the

quantization. Further, we have the problem that the difference may be larger than the

maximum that can be accommodated because of the restricted number of encoding

bits we have provided. Hence it might well be that at some time there might be a

large discrepancy between the original signal m(t) and the signal m(t) generated at the

receiver by accumulation. Suppose that over a number of samplings, while m (t) is

increasing, the transmitted differences were too small so that m (k) had fallen

substantially short of keeping up with m (t). Suppose, further, that in the interval

sampling times k and k + 1, m (t) should decrease slightly. Clearly if we transmitted

the negative change of m (t) we would be giving the wrong signal.

In a digital differential system we circumvent the difficulty we have just described by

making available at the transmitter a duplicate of the receiver accumulator so that at

the transmitter we have available the same signal m (t). Then we arrange that the

transmitted signal should not convey the most recent change in m (t) but conveys

instead the difference between m (t) and m’ (t).

Scientech Technologies Pvt. Ltd. 33

ST2113

DPCM Transmitter / Receiver

Figure 22

In an analog system, this difference m (t) – m’ (t) is precisely the last change in m (t).

In a quantized system, as we have noted, such is not the case. In short, in a quantized

system we add or subtract from m (t) a value which is appropriate to bring m (t)

closer to m (t). The waveform m’ (t) is generally referred to as the approximation to

m (t).

Altogether, then, the quantized differential transmission scheme is as shown in 22

(we ignore initially the "predictors" that appear in the figure 22). The receiver

consists of an accumulator which adds up the received quantized differences ΔQ (k)

and a filter which smooths out the quantization noise. The output of the accumulator

is the signal approximation m’ (k) which becomes m (t) at the filter output. At the

transmitter we need to know whether m (t) is larger or smaller than m (t), and by how

much. We may then determine whether the next difference ΔQ (k) needs to be positive

or negative and of what amplitude in order to bring m’ (t) as close as possible to m

(t). For this reason we have a duplicate accumulator at the transmitter. At each

sampling time, the transmitter difference amplifier compares m’ (t) and m (t) and the

Scientech Technologies Pvt. Ltd. 34

ST2113

sample and hold circuitry holds the result of that comparison Δ (t) for the duration of

the interval between sampling times. The quantized generates the signal So (t) = ΔQ

(k) both for transmission to the receiver and to provide input to the receiver

accumulator in the transmitter. In a practical system the quantized differences would

first be encoded into a binary bit stream before transmission and decoded at the

receiver. For simplicity the encoder and decoder are not included in the above figure

22.

It needs to be emphasized that the basic limitation of the scheme we have just

described is that the transmitted differences are quantized and are of limited

maximum value. The quantization means that almost never will the increment ΔQ (k)

added to m (k) make m’ (t) precisely equal to m (t). The limitation on the maximum

value of (k) means that when m (t) changes monotonically at a rapid rate, m’ (t) may

simply not be able to keep up.

Need for a Predictor:

The DPCM scheme we have described in this section turns out, as a matter of

practice, not to be effective. When the sampling rate is set at the Nyquist rate it

generates unacceptably excessive quantization noise in comparison to PCM. The

quantization noise can be reduced by significantly increasing the sampling rate. With

increased rate the differences from sample to sample are smaller and the rate of

producing large quantization errors is reduced. Suppose, then, that in DPCM we

increase the sampling rate, above the Nyquist rate, to the point where we get a quality

of sound transmission, which is comparable to that, available from PCM operating at

the Nyquist rate. Then again it turns out that DPCM is at a disadvantage because it

has been demonstrated that the bit rate of DPCM (bits per sample x sample rate)

exceeds that required for PCM.

The situation in DPCM can be improved by recognizing that there is a correlation

between successive samples of the signal m (t) and of Δ (t) if the signal is sampled at

a rate exceeding the Nyquist rate. Hence a knowledge of past sample values or

differences allows us to predict, with some probability of being correct, the range of

the next required increment. To take advantage of this correlation, a predictor is

included in the DPCM system shown in figure 22 the predictor will generally be a

moderately sophisticated system; it will need to incorporate the facility for storing

past differences and for carrying out some algorithm to predict the next required

increment.

Altogether, the quality of voice or video transmission using DPCM can be made

comparable to that of PCM by increasing the sampling rate (which reduces the

differences and increases the correlation between samples) and by using a predictor.

Most importantly, by these expedients, DPCM can operate at approximately one-half

of the bit rate of PCM with a consequent saving of spectrum space.

Scientech Technologies Pvt. Ltd. 35

ST2113

Practical Considerations:

In PCM system we use 8 bits per samples, so if 8 KHz is the sampling frequency then

64K bits/s is the bandwidth requirement. If we can reduce number of bite per sample

and keep sampling frequency same, it will effectively reduce bit rate of the system

and hence the bandwidth required for the transmission. In DPCM we transmit the

difference between previous sample and current sample instead of transmitting exact

sample value every time. Naturally the difference between the two consecutive

samples is less than the sample value itself. So it requires less numbers of bits to

quantize the difference signal.

In ST2113 we used 4 bits for quantizing the difference and 1 bit for positive or

negative difference indication. So, overall 5 bits per sample are transmitted.

Sampling frequency is fixed and is 8 KHz. Both transmitter and receiver are designed

on the same board. In actual practical system we have to duplicate receiver at

transmitting end itself. This receiver consists of an accumulator and a predictor with

associated computing circuitry. The output of this receiver is the predicted output

computed with the help of the accumulator. Now this predicted output and the original

modulating signals are fed into the input terminals of the difference amplifiers. At the

O/P of subtractor (or difference amplifier) we get the difference between the previous

sample and current value of the signal at the sampling instance. This can be positive

or negative depending upon their relative amplitudes. A sign bit is generated

accordingly using a comparator. If difference is positive i.e. current value is more than

the predicted value a ‘0’ (or low signal) is generated, and if the difference is negative

a high signal (or logic‘1’) is generated. This sign signal is also send together with the

quantized difference signal.

In either case input to A/D should be positive. For this purpose two channels of A/D

are used & giving the sign bit to the control input of multiplexer of ADC makes

selection of particular channel. The negative difference signal is first inverted to

positive and then applied to the second channel of the multiplexer. The first channel is

being fed with positive polarity difference signal directly. Now as per the nature of

difference signal i.e. positive or negative the input to the ADC is positive always but

the sign bit later on as to differentiate between the positive and negative sampled

values controls the rest of the processing.

Only four least significant bit values of the ADC are used for the conversion purpose

since the value of difference signal between present and previous sampled signal is

always less than the individual sampled value and hence only few numbers of bits are

suffice to quantize the difference. Rest of the MSBs are used to limit the output by

generating a control signal which will either keep on adding or subtracting the

samples difference until the difference between predicated and present samples comes

within the specified limits.

The outputs of ADC together with the sign bit are then passed to the parallel to serial

converter. After the serial conversion we are ready to transmit it through the

communication channel and to the input of duplicated receiver at the transmitting end

as well.

Scientech Technologies Pvt. Ltd. 36

ST2113

At the receiver end all the received serial bits are fed to the serial to parallel converter.

After getting the parallel bits these are fed simultaneously to the adder and subtractor

block, which are the part of signal processing circuit. Activation of particular block is

decided by the nature of the sign bit. If the present sample value is less than the

previously stored sample the difference would be positive and thus resulting in a high

sign bit value. This high sign bit will activate the adder unit and the difference value

will get added to the previous sampled value and the process keep going like this until

the present sample value exceed the previous sample value. In that case the difference

would be negative and hence the subtractor unit gets activated thus causing the

present value to get subtracted from the previously stored sample value. The whole

process is such that it keeps tracking the input signal and thus the stored values

replicate the input signal in discrete fashion. The stored samples are then converted

into analog form through D to A converter. The output of this converter is then fed to

an output low pass filter and to the “predicted O/P” input of the DPCM transmitter.

Scientech Technologies Pvt. Ltd. 37

ST2113

Brief Description of ST2113

ST2113, Differential pulse code modulation / Demodulation Trainer has been

designed to clearly demonstrate the complete processes involved in Differential Pulse

Code Modulation and demodulation technique. The detailed mimic is shown in the

figure 23, given below. ST2113, Differential Pulse Code Modulation / Demodulation

Trainer board consists of following major blocks:

(a) Audio signal generator: The audio signal generator block generates sine wave

and square wave output in the frequency range of 300Hz to 3.4 KHz i.e. in the

audio frequency range. The frequency of the output signal can be adjusted with

the help of pot provided therein. This audio signal generator serves the purpose

of test signal source for the modulator / demodulator.

(b) Clock and control signal block: This block consists of various control and

clock signal test points. These clock and control signals guide the various

processes in the system and provide a smooth and errorless flow of the data and

signals in the system. A timing diagram of all these control and clock signals is

given in the figure 24. This timing diagram should be taken as a reference while

performing the experiments.

(c) Differential pulse code modulator (or transmitter) : The modulator

comprises of :

i. Difference Amplifier

ii. Sign bit generator

iii. ADC

iv. Parallel to serial converter

v. Predictor

Scientech Technologies Pvt. Ltd. 38

ST2113

ST2113 Differential Pulse Code Modulation / Demodulation Trainer Mimic

Figure 23

Scientech Technologies Pvt. Ltd. 39

ST2113

(i) Difference amplifier: The difference amplifier subtracts the predicted

estimate of the input signal from the original input signal and then gives this

difference signal to the ADC for A/D conversion.

(ii) Sign Bit Generator: The sign bit generator generates the sign bit based on

the sign of difference signal sample. If the magnitude of the incoming signal

is larger than the predicted signal, the sign bit generator will generate a high

signal (logic ‘1’) or else it will generate low signal (logic ‘0’). This sign bit

controls the mathematical manipulation of data in the predictor accumulator.

(iii)ADC: The ADC converts the analog difference signal sample into digital

data bits. Note that the bits required to encode the difference signal would

obviously be fewer than had it been the encoding of complete input signal

sample (refer to the theory of DPCM technique given in the previous

section). In the present system only four bits are being used to encode the

difference signal. The main control signals associated with this A/D

conversion are R/W signal and output LE (latch enable) signal of the ADC.

The frequency of R/W control signal is 8 KHz, which can be termed as the

sampling frequency of the system.

(iv) Serial to Parallel converter: The serial to parallel converter converts

parallel data (four bits) coming from A/D converter and an extra sign bit into

the serial form. The main control and clock signals for S/P conversion are

EN signal and Clock of shift register (refer o the timing diagram given in

figure 24). Note that during the time period when enable signal is high,

exactly five clock pulses drives the S/P converter in order to convert five

parallel bits into serial form. The digital signal (or data) coming out of this

converter is the final differentially coded PCM signal available for

transmission.

(v) Predictor: The Predictor is nothing but a receiver used at the modulator end

itself. In fact the similar circuit, used here for predictor, is used at the

receiver end as a receiver with an added output filter. In actual practical

system two receiver configurations are used; one at the transmitting end as a

predictor accumulator and the other at receiving end as a receiver. The

filtered output of the predictor accumulator in the present system can serve

here the purpose of received signal and so there is no need of providing a

redundant section as far as the conceptual study of the DPCM technique is

concerned.

(d) Differential pulse code demodulator (or Receiver) : The Receiver consists of

the following sections :

i. Serial to Parallel converter

ii. Adder and Subtractor section

iii. Data Latches

iv. DAC

v. Output LPF

Scientech Technologies Pvt. Ltd. 40

ST2113

(i) Serial to Parallel converter: The serial to parallel converter at the receiver

end converts the received data bits into parallel form. The clock signal used

here is same as used in P/S conversion at the transmitter. After S/P

conversion, out of five received bits, sign bit is sent to control circuitry and

rest four bits are sent to the signal processing section.

(ii) Adder and Subtractor section: This section does the main computational

task. The circuitry adds or subtracts the incoming coded difference signal

from the difference signal, which in this case is the output of sign bit

generator that has been extracted out through S/P conversion. Actually this

sign bit enables or disables the adder or subtractor block based on whether it

is ‘0’ or ‘1’ at that particular instant.

(iii)Data Latches: These latches act in dynamism to store and forward he

processed data to next sections.

(iv) DAC: DAC converts the digitally processed data back into analog form..

The data available at the output of the latches after addition or subtraction of

the differentially encoded data from the previously stored data goes to the

input of DAC.

(v) Output LPF: The output LPF filter the output obtained from the ADC and

thus reduces the quantization noise and smoothened the signal.

(e) Audio Input circuit: This is basically an audio amplifier which amplifies the

output of an audio input transducer (e.g. mic). The electrical form the audio then

can be used as a test signal to check the capability of the system for faithful

transmission of the voice signal through DPCM process.

(f) Audio output circuit: The audio output amplifier amplifies the output of LPF

and then this output can be fed to an audio transducer such as headphone to get

the audio output back.

Scientech Technologies Pvt. Ltd. 41

ST2113

Timing Diagram of various Controls and Clock Signals

Figure 24

Scientech Technologies Pvt. Ltd. 42

ST2113

Experiment 1

Objective: Study of Differential pulse code modulation and Demodulation

Technique

Equipments Required:

1. ST2113 DPCM Trainer with power supply cord

2. CRO with connecting cable

3. Connecting Cords

Connection Diagram:

Setup for study of DPCM Process

Figure 1.1

Scientech Technologies Pvt. Ltd. 43

ST2113

Procedure:

1. Connect the sine wave output of the audio signal generator to one of the inputs

of the difference amplifier as shown in the figure 1.1.

2. Connect the output of the difference amplifier to the input of the ADC.

3. Connect the output of parallel to serial converter to the input of serial to

parallel converter of the receiver accumulator.

4. Connect the output of the DAC to the other input of the difference amplifier as

shown in the above figure 1.1.

5. Now switch ‘On’ the power supply. Observe the sine wave output of the sine

wave generator on the CRO. Adjust the frequency of sine wave at 1 KHz.

6. Observe the signal at the output of DAC. You will see the stair case

approximation of the input signal at the output of DAC. Also observe the

output of low pass filter and see that it is nearly same as the input signal.

7. Now observe various controls and clock signal shown in the control and clock

section and try to relate these signals with the timing diagram of figure 1.2.

8. Note that the sampling starts with the R/W signal pulse that has a frequency of

8 KHz. For a small duration when pulse is high, ADC reads the input port and

for the rest of the low period it provides this data at the output of the ADC.

9. Now observe the clock and reset signal of the parallel to serial converter.

Observe that for the time period when reset is low, exactly five clock pulses

shift the content of the shit register.

10. Observe the LE2 and OE 2of previous data latch and relate them with timing

diagram of figure 1.2.

11. You may find it difficult to appreciate the entire control signals

simultaneously with a normal two channels CRO but nevertheless an intuitive

sense of relative time based occurrences of all these signals can make the task

easier. You can see all these signals simultaneously on the screen with the help

of logic analyzer too.

12. Also it is to be taken into consideration that the data flow through the entire

system is fast enough random as well so it is not feasible to observe the data

exactly at any point. But still you can have an overview of the data statistics at

any test point of the data bus.

Scientech Technologies Pvt. Ltd. 44

ST2113

Figure 1.2

Observations:

Conclusion:

Questions:

1. Define DPCM?

2. What are the limitations of PCM system?

3. What is the function of Predictor?

4. What is the function of differential amplifier?

5. Differentiate between PCM and DPCM?

Scientech Technologies Pvt. Ltd. 45

ST2113

Experiment 2

Objective: To verify experimentally that DPCM is a differentiation process.

Equipments Required:

1. ST2113 DPCM Trainer with power supply cord

2. CRO with connecting cable

3. connecting Cords

Connection Diagram:

Setup for DPCM modulation /Demodulation for a square wave input

Figure 2.1

Scientech Technologies Pvt. Ltd. 46

ST2113

Procedure:

1. Connect square wave output of the signal generator to one of the input of the

difference amplifier.

2. Make rest of the connections as per the procedure given in the previous

experiment. You can refer to the figure 2.1 while making connections.

3. Switch ‘On’ the power supply and Set the frequency of square wave around 1

KHz.

4. Connect the square wave output and the filtered output (after DAC) to the

CRO channels and see the waveform in dual trace mode.

5. Observe that corresponding to rising and falling edges of the square wave we

get positive and negative impulses in the demodulated waveform as shown in

the figure 2.2 given below.

Square wave input with demodulated output

Figure 2.2

6. The above figure 2.2 suggests that the DPCM process is nothing but a

differentiation process.

The above result is obvious from point of view of the process since at the

rising or falling edges, the difference between the original samples and

predicted samples would be very large but subsequently the at the constant

amplitudes of the input signal the circuit try to minimize the difference as to

track the input signal and correspondingly we get ramp shape for a certain

time period during this constant amplitude of the input signal. The slop of this

ramp will depend upon the system frequency (sampling frequency of the

system) i.e. higher the sampling rate; steeper will be the slop of ramp.

Observations:

Conclusion:

Scientech Technologies Pvt. Ltd. 47

ST2113

Questions:

1. What is the bandwidth requirement for DPCM?

2. Draw the block diagram of DPCM?

3. What are the draw backs of DPCM?

4. What is slope overload?

5. How slope over loading can be reduced?

Scientech Technologies Pvt. Ltd. 48

ST2113

Experiment 3

Objective: To establish voice link using DPCM Technique

Equipments Required:

1. ST2113 DPCM Trainer with power supply cord

2. CRO with connecting cable

3. Connecting Cords

Connection Diagram:

Setup for establishing voice link through DPCM technique

Figure 3.1

Scientech Technologies Pvt. Ltd. 49

ST2113

Procedure:

1. Connect microphone jack to the input socket of the Audio I/P circuit.

2. Connect the O/P of the Audio I/P Circuit to one of the input of the difference

amplifier as shown in the figure 3.1.

3. Connect the output of difference amplifier to the ADC input.

4. Connect the output of parallel to serial converter to the serial parallel converter.

5. Connect the output of DAC to the other input of difference amplifier.

6. Connect the output of low pass filter to the input of Audio O/P circuit.

7. Connect the output socket of the Audio O/P circuit to the headphone/speaker.

8. Now switch ‘On’ the power supply.

9. Verify that voice link has been established. Also verify that the main

articulations of voice (or intelligibility of voice) are being properly carried out

through the system.

10. Use the microphone and the headphone supplied with the instrument only.

11. You can also test signals at various test point with a CRO prob.

12. The data, which has to be transmitted to the communication channel, is the

serial data present at the output of parallel to serial converter.

Observations:

Conclusion:

Questions:

1. Define the frequency band for voice?

2. What is the function of microphone?

3. Explain the voice communication process using DPCM technique?

4. Why low pass filter is used for reconstruction of signals?

5. What is the function of quantizer?

Scientech Technologies Pvt. Ltd. 50

ST2113

Frequently Asked Questions

1. How PAM signal is converted into PCM signal?

Ans: A PAM system can be converted into a PCM system by adding a suitable

analogue-to-digital (A/D) converter at the source and a digital-to-analogue (D/A)

converter at the destination.

2. List the steps to get the PCM signals?

Ans: In PCM, modulation process is executed in three steps:

1. Sampling

2. Quantizing

3. Coding

3. What is Quantization?

Ans: In quantization the levels are assigned a binary codeword. All sample values

falling between two quantization levels are considered to be located at the centre of

the quantization interval. In this manner the quantization process introduces a certain

amount of error or distortion into the signal samples.

4. What is Quantization noise?

Ans: During the quantization process introduces a certain amount of error or

distortion into the signal samples. This error known as quantization noise

5. How Quantization noise can be minimized?

Ans: Quantization noise can be minimized by establishing a large number of small

quantization intervals. Of course, as the number of quantization intervals increase, so

must the number or bits increase to uniquely identify the quantization intervals.

6. Draw the block diagram of Bit step Analog to digital converter?

Ans: The block diagram of Bit step Analog to digital converter is as follows:

Scientech Technologies Pvt. Ltd. 51

ST2113

7. List the pulse modulation techniques and explain them in short?

1. Pulse Amplitude Modulation (PAM) :

In pulse amplitude modulation system the amplitude of the pulse is varied in

accordance with the instantaneous level of the modulating signal. Now days, the

PAM system is not generally used, but it forms the first stage of the other types

of pulse modulation.

2. Pulse Width Modulation (PWM) :

In PWM system the width of the pulse is varied in accordance with the

instantaneous level of the modulating signal.

3. Pulse Position Modulation (PPM) :

In PPM System, the position of the pulse relative to the zero reference level is

varied in accordance with the instantaneous level of the modulating signal.

4. Pulse Code Modulation (PCM) :

In PCM System the amplitude of the sampled waveform at definite time

intervals is represented as a binary code. The first three techniques of the above

described systems are not truly digital but in fact are analog in nature. The very

fact that the variation of a particular pulse parameter is continuous rather than

being in the discrete steps makes the system analog in nature.

8. What are the benefits of using TDM?

Ans: Benefits of TDM are as follows:

1. TDM is all about cost: fewer wires and simpler receivers are used to transmit

data from multiple sources to multiple destinations.

2. TDM also uses less bandwidth than Frequency-Division Multiplexing (FDM)

signals, unless the bit rate is increased, which will subsequently increase the

necessary bandwidth of the transmission.

3. An asset of TDM is its flexibility. The scheme allows for variation in the

number of signals being sent along the line, and constantly adjusts the time

intervals to make optimum use of the available bandwidth. The Internet is a

classic example of a communications network in which the volume of traffic

can change drastically from hour to hour.

9. What is Pseudo-random Noise (PN) sequence?

Ans: A Pseudo-random Noise (PN) sequence is a sequence of binary numbers, e.g.

±1, which appears to be random; but is in fact perfectly deterministic. The sequence

Scientech Technologies Pvt. Ltd. 52

ST2113

appears to be random in the sense that the binary values and groups or runs of the

same binary value occur in the sequence in the same proportion they would if the

sequence were being generated based on a fair "coin tossing" experiment.

10. What are the uses of Pseudo-random Noise (PN) sequence?

Ans: They can be used to logically isolate users on the same frequency channel. They

can also be used to perform scrambling as well as spreading and dispreading

functions.

11. Draw the block diagram and explain how PN sequence can be generated?

Ans: A PN generator is typically made of N cascaded flip-flop circuits and a specially

selected feedback arrangement as shown below.

Figure

The flip-flop circuits when used in the cascaded manner is called a shift register, since

each clock pulse applied to the flip-flops causes the contents of each flip-flop to be

shifted to the right. The feedback connections provide the input to the left-most flip-

flop. With N binary stages, the largest number of different patterns the shift register

can have is 2N. However, the all-binary-zero state is not allowed because it would

cause all remaining states of the shift register and its outputs to be binary zero. The

all-binary-ones state does not cause a similar problem of repeated binary ones

provided the number of flip-flops input to the module 2 adder is even. The period of

the PN sequence is therefore 2N-1, but IS-95 introduces an extra binary zero to

achieve a period of 2N, where N equals 15.

12. Write the advantages and disadvantages of Digital modulation system?

Ans: Advantages of digital modulation system:

a. Noise & Distortion :

a. Pulse which becomes distorted by the addition of noise can be reshaped at

the regenerators installed at pre-determined intervals along the link. Thus

within certain threshold the error will not creep in.

b. Multiplexing :

a. The information once sampled & coded can be multiplexed in time

domain, i.e. the coded information from different sources can be sent, one

after another, if it can be re-routed to the corresponding channels at the