Professional Documents

Culture Documents

Exerice N1 Examen Code VHDL PartieB

Uploaded by

Mariem Tlili0 ratings0% found this document useful (0 votes)

20 views1 pageThis document defines an entity called FSM_VentB that contains a finite state machine with 6 states (E0, E1, E2, E3, E4, E5) to control two outputs (V1, V2) based on three inputs (S0, S1, H). The state transitions and output logic are defined in three processes - Combinatoire defines the next state logic, Memoire contains the state register logic, and Sortie assigns the output values based on the current state.

Original Description:

Original Title

Exerice-N1-Examen-Code-VHDL-PartieB

Copyright

© © All Rights Reserved

Available Formats

TXT, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThis document defines an entity called FSM_VentB that contains a finite state machine with 6 states (E0, E1, E2, E3, E4, E5) to control two outputs (V1, V2) based on three inputs (S0, S1, H). The state transitions and output logic are defined in three processes - Combinatoire defines the next state logic, Memoire contains the state register logic, and Sortie assigns the output values based on the current state.

Copyright:

© All Rights Reserved

Available Formats

Download as TXT, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

20 views1 pageExerice N1 Examen Code VHDL PartieB

Uploaded by

Mariem TliliThis document defines an entity called FSM_VentB that contains a finite state machine with 6 states (E0, E1, E2, E3, E4, E5) to control two outputs (V1, V2) based on three inputs (S0, S1, H). The state transitions and output logic are defined in three processes - Combinatoire defines the next state logic, Memoire contains the state register logic, and Sortie assigns the output values based on the current state.

Copyright:

© All Rights Reserved

Available Formats

Download as TXT, PDF, TXT or read online from Scribd

You are on page 1of 1

Library IEEE;

Use IEEE.STD_LOGIC_1164.ALL;

Use IEEE.STD_LOGIC_arith.ALL;

entity FSM_VentB is

Port (S0, S1,H ,Reset :IN std_logic;

V1,V2:OUT std_logic);

end FSM_VentB;

ARCHITECTURE Arch_VentB of FSM_VentB is

Type Etats_FSM is (E0,E1,E2,E3,E4,E5);

Signal Ep,Ef: Etats_FSM;

begin

Combinatoire:process(S0,S1,Ep)

begin

Case Ep is

when E0 => if S0='1' and S1='0' then Ef <= E1;

else Ef <= E0;

end if;

when E1 => if S0='0' and S1='0' then Ef <= E2;

else Ef <= E1;

end if;

when E2 => if S0='1' and S1='0' then Ef <= E3;

else Ef <= E2;

end if;

when E3 => if S0='1' and S1='1' then Ef <= E4;

else Ef <= E3;

end if;

when E4 => if S0='1' and S1='0' then Ef <= E5;

else Ef <= E4;

end if;

when E5 => if S0='0' and S1='0' then Ef <= E0;

else Ef <= E5;

end if;

end case;

end process;

Memoire: Process(H,Reset)

begin

if (Reset = '1') then EP <= E0;

elsif (H = '1' and H'event) then Ep <= Ef;

end if;

end process;

Sortie: process(Ep)

begin

case Ep is

when E0 => V1<='0';V2<='0';

when E1 => V1<='1';V2<='0';

when E2 => V1<='0';V2<='0';

when E3 => V1<='0';V2<='1';

when E4 => V1<='1';V2<='1';

when E5 => V1<='1';V2<='0';

end case;

end process;

end Arch_VentB;

You might also like

- Exerice N1 Examen Code VHDL PartieADocument1 pageExerice N1 Examen Code VHDL PartieAMariem TliliNo ratings yet

- FeuxDocument1 pageFeuxFarhat RahmaNo ratings yet

- Exerice N2 Examen Coca ColaDocument1 pageExerice N2 Examen Coca ColaMariem TliliNo ratings yet

- Exemple - Code VHDLDocument4 pagesExemple - Code VHDLSaid EL AissaouyNo ratings yet

- SemaforoDocument2 pagesSemaforoVictor yurivilca lazoNo ratings yet

- 7th DocumentDocument2 pages7th DocumentRatish Kumar JamiNo ratings yet

- Chapter 04 ISMDocument34 pagesChapter 04 ISMMekuannint DemekeNo ratings yet

- Analysis of RC CircuitsDocument11 pagesAnalysis of RC Circuitsغريب أعجميNo ratings yet

- CHP 4-STAT 245 Summer 2021Document36 pagesCHP 4-STAT 245 Summer 2021Jaheda SultanaNo ratings yet

- VHDL Project: Title: "Stop Watch"Document13 pagesVHDL Project: Title: "Stop Watch"Soriya HiteshNo ratings yet

- Primer ProgramaDocument2 pagesPrimer ProgramaPOWUQNo ratings yet

- MatlabDocument2 pagesMatlabVanesa Castanedo GonzálezNo ratings yet

- Logic Design Lab - Lab 09Document3 pagesLogic Design Lab - Lab 09Aditya NambiarNo ratings yet

- Worked Examples 1Document13 pagesWorked Examples 1Anonymous WyTCUDyW0% (1)

- Aim: To Write An C++ Program To Evaluate A Postfix Expression. AlgorithmDocument6 pagesAim: To Write An C++ Program To Evaluate A Postfix Expression. AlgorithmSuganya SelvarajNo ratings yet

- Universal College of Engineering & Research, Pune: Class Time Table - Te E&Tc (Sem-V)Document24 pagesUniversal College of Engineering & Research, Pune: Class Time Table - Te E&Tc (Sem-V)poo235No ratings yet

- 2 - Alternating - Currents (Autosaved)Document33 pages2 - Alternating - Currents (Autosaved)kdNo ratings yet

- Btech 10214 21 Shreyansh Singh Exp-07Document3 pagesBtech 10214 21 Shreyansh Singh Exp-07Vivek kumarNo ratings yet

- MUX - 8to1 (BHVR) - CodeDocument1 pageMUX - 8to1 (BHVR) - Codebhslegion1498No ratings yet

- Sengoku Basara 2 NTSC-J .Pnach (SFILEDocument1 pageSengoku Basara 2 NTSC-J .Pnach (SFILEpaijembuangkartadinayaNo ratings yet

- Báo Cáo Lab3 FPGA - Nhóm 8Document22 pagesBáo Cáo Lab3 FPGA - Nhóm 8Tân GiangNo ratings yet

- VHDL of The Moore Machine With A Synchronous Reset and MEALY SEQ DETECTORDocument5 pagesVHDL of The Moore Machine With A Synchronous Reset and MEALY SEQ DETECTORdhr893No ratings yet

- Hydrogen and Quantum BoxDocument1 pageHydrogen and Quantum Boxxben88-emailNo ratings yet

- Screenshot 2023-11-25 at 1.21.57 PMDocument21 pagesScreenshot 2023-11-25 at 1.21.57 PMVK GNo ratings yet

- Impri MirDocument16 pagesImpri MirDeliana DelianaNo ratings yet

- Created by C. Mani, Principal, K V No.1, AFS, Jalahalli West, BangaloreDocument22 pagesCreated by C. Mani, Principal, K V No.1, AFS, Jalahalli West, Bangaloreayush paswanNo ratings yet

- 2 Alternating CurrentsDocument22 pages2 Alternating Currentsmpravin kumarNo ratings yet

- Eve of PostfixDocument2 pagesEve of PostfixbadonoNo ratings yet

- Trabajo de Diseño02Document10 pagesTrabajo de Diseño02Alvaro SegoviaNo ratings yet

- Trabajo de Diseño02Document10 pagesTrabajo de Diseño02Victor yurivilca lazoNo ratings yet

- Alternating Current 48Document25 pagesAlternating Current 48saransh geraNo ratings yet

- Nama: Bambang Budiarto NIM: 061401025Document3 pagesNama: Bambang Budiarto NIM: 061401025FriendlyFaucet PurbaNo ratings yet

- Alternating CurrentDocument38 pagesAlternating CurrentMP12No ratings yet

- DigiELECS 2 Lab Act 2Document6 pagesDigiELECS 2 Lab Act 22021308464No ratings yet

- Dis06 Assembly PDFDocument12 pagesDis06 Assembly PDFnew2trackNo ratings yet

- лр 5 архDocument2 pagesлр 5 архspam trachNo ratings yet

- T3 Ge I FF,: Gi Eei:Fiee:IDocument1 pageT3 Ge I FF,: Gi Eei:Fiee:IpanindalineNo ratings yet

- Mutually Exclusive EventsDocument9 pagesMutually Exclusive EventsReygie FabrigaNo ratings yet

- % Tebakan Awal: FunctionDocument2 pages% Tebakan Awal: FunctionAkademik Saluak LakaNo ratings yet

- Simplified DES 1: 2.1 Key GenerationDocument3 pagesSimplified DES 1: 2.1 Key GenerationRimbun Ferianto SrNo ratings yet

- Impletar en VHDL La Siguiente Maquina de EstadosDocument10 pagesImpletar en VHDL La Siguiente Maquina de EstadosGian SusanaNo ratings yet

- MAlik Abdulllah DsaDocument6 pagesMAlik Abdulllah DsaAhmed AlyNo ratings yet

- Unit 4 Bayes' Theorem: StructureDocument13 pagesUnit 4 Bayes' Theorem: StructureSumundra RathNo ratings yet

- Unpacking Asprotect 2.Xx SKE - Part 2 IAT RebuildingDocument30 pagesUnpacking Asprotect 2.Xx SKE - Part 2 IAT RebuildingthemmmNo ratings yet

- Tugas KNT Listing BoyDocument10 pagesTugas KNT Listing Boyali fikriNo ratings yet

- Corrigé TD2Document9 pagesCorrigé TD2All AhmeDciaNo ratings yet

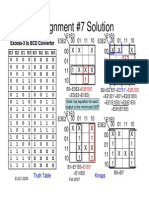

- Assignment #7 Solution: X X X 00 01 11 10 1 1 1 X X X 1 X X X 00 01 11 10Document6 pagesAssignment #7 Solution: X X X 00 01 11 10 1 1 1 X X X 1 X X X 00 01 11 10jisteeleNo ratings yet

- %steel Input%Document25 pages%steel Input%Saurabh Bansal BansalNo ratings yet

- Cs9251 CD Unit III NotesDocument20 pagesCs9251 CD Unit III Noteskarthi_gopalNo ratings yet

- Json Deep EqualDocument1 pageJson Deep EqualAna GonçalvesNo ratings yet

- Code Generation: - Intermediate Code Generation: - Code Optimization: - Final Code GenerationDocument8 pagesCode Generation: - Intermediate Code Generation: - Code Optimization: - Final Code Generationsuhaskurup2446No ratings yet

- Int Fo A0 Int Fos 0 Float Mjerenje 0Document4 pagesInt Fo A0 Int Fos 0 Float Mjerenje 0PewDiePie aqtNo ratings yet

- P OlverDocument7 pagesP OlverAscanio BarbosaNo ratings yet

- Sckeylog 1 N 2Document35 pagesSckeylog 1 N 2Mozart HikaruNo ratings yet

- Lecture8 - Infinite Coin TossDocument4 pagesLecture8 - Infinite Coin TossAnonymous uuSF7AN4No ratings yet

- Guass PDFDocument1 pageGuass PDFMahmoud GaballaNo ratings yet

- CCP Quiz QuestionsDocument3 pagesCCP Quiz QuestionsKarthik KamathNo ratings yet

- Img 0008Document1 pageImg 0008Ionel RotaruNo ratings yet

- EEPROM - To Write Some Initial Value To The Memory and Read Back (Test Bed For Testing Nonvolatile RAM of 8583)Document7 pagesEEPROM - To Write Some Initial Value To The Memory and Read Back (Test Bed For Testing Nonvolatile RAM of 8583)axerayNo ratings yet