Professional Documents

Culture Documents

Solution

Solution

Uploaded by

erbk191Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Solution

Solution

Uploaded by

erbk191Copyright:

Available Formats

1 KNREDDY

COMPUTER ORGANIZATION AND ARCHITECTURE

ASSIGNMENT –3

1. Perform the arithmetic operations below with binary numbers and with negative numbers

in signed 2’s complement representation. Use seven bits to accommodate each number

together with its sign. In each case, determine if there is an overflow by checking the

carries into and out of the sign bit position.

a. (+35) + (+40)

b. (-35) + (-40)

c. (-35) - (+40)

When two numbers of n digits each are added and the sum occupies n + 1 digits, we say that

an overflow occurred.

A result that contains n + 1 bits cannot be accommodated in a register with a standard length

of n bits.

The detection of an overflow after the addition of two binary numbers depends on whether

the numbers are considered to be signed or unsigned. When two unsigned numbers are added,

an overflow is detected from the end carry out of the most significant position.

In the case of signed numbers, the leftmost bit always represents the sign, and negative

numbers are in 2' s complement form. When two signed numbers are added, the sign bit is

treated as part of the number and the end carry does not indicate an overflow.

An overflow cannot occur after an addition if one number is positive and the other is

negative, since adding a positive number to a negative number produces a result that is

smaller than the larger of the two original numbers. An overflow may occur if the two

numbers added are both positive or both negative.

An overflow condition can be detected by observing the carry into the sign bit position and

the carry out of the sign bit position. If these two carries are not equal, an overflow condition

is produced. If the two carries are applied to an exclusive-OR gate, an overflow will be

detected when the output of the gate is equal to 1 .

a) +35 0 100011

+40 0 101000

+75 1 001011

Last two carries are F=0 and E=1. F XOR E= 1.Hence overflow had occurred.

b) -35 1 011101

-40 1 011000

-75 1 110101

Last two carries are F=1 and E=0. F XOR E= 1.Hence overflow had occurred.

c) –(35 )-(+40) . Add 2’s complement of 40 to 2’ complement of 35. Same as above

COMPUTER ORGANIZATION AND ARCHITECTURE

2 KNREDDY

2. Show the contents of registers E, A, Q, and SC during the process of multiplication of

two binary numbers, 11111 (multiplicand) and 10101 (multiplier). The signs are not

included.

3. Show the step-by-step multiplication process using Booth algorithm when the following

binary numbers are multiplied. Assume 5-bit registers that hold signed numbers. The

multiplicand in both cases is + 15.

a. (+ 15) * (+ 13) b. (+ 15) * (- 13)

COMPUTER ORGANIZATION AND ARCHITECTURE

3 KNREDDY

4. Show the contents of registers E, A, Q, and SC during the process of division of

(a) 10100011 by 1011; (b) 00001111 by 0011. (Use a dividend of eight bits.)

a)

COMPUTER ORGANIZATION AND ARCHITECTURE

4 KNREDDY

b)

COMPUTER ORGANIZATION AND ARCHITECTURE

You might also like

- Booth AlgorithmDocument25 pagesBooth AlgorithmSanvi Singh ChauhanNo ratings yet

- Static and Dynamic Analysis For A Turbo Propeller Engine and Its OptimizationDocument47 pagesStatic and Dynamic Analysis For A Turbo Propeller Engine and Its OptimizationNationalinstituteDsnr100% (1)

- Exp PR Di010 en r0 - 1 DiagramsDocument67 pagesExp PR Di010 en r0 - 1 Diagramsbali100% (3)

- Declare OpenSTAADDocument34 pagesDeclare OpenSTAADAnonymous JZFSB3DNo ratings yet

- Design of Adders, Subtractors, BCD Adders Week6 and 7 - Lecture 2Document60 pagesDesign of Adders, Subtractors, BCD Adders Week6 and 7 - Lecture 2Gursheel SinghNo ratings yet

- Chemistry Review PacketDocument29 pagesChemistry Review Packetamanderple100% (1)

- Introdution To The Raptors of Southeast AsiaDocument36 pagesIntrodution To The Raptors of Southeast AsiaReby NirupuNo ratings yet

- Manual TV TRCDocument14 pagesManual TV TRCPedro MoraNo ratings yet

- Respiratory Physiology: Ventilation Perfusion DiffusionDocument6 pagesRespiratory Physiology: Ventilation Perfusion DiffusionShiara Ruth EdrosoloNo ratings yet

- Energy Consumption in Yarn ProductionDocument15 pagesEnergy Consumption in Yarn ProductionPushpendra Jain100% (1)

- Basic Calculus Cot 1 f2fDocument9 pagesBasic Calculus Cot 1 f2fRowie Dizon VlogsNo ratings yet

- Finite Word Length EffectsDocument31 pagesFinite Word Length EffectsSugumar Sar DuraiNo ratings yet

- Basic Concepts of Technical Statistics-1Document68 pagesBasic Concepts of Technical Statistics-1anirudh bNo ratings yet

- CO 18CS34 MOD4 IncompleteDocument11 pagesCO 18CS34 MOD4 IncompleteAashik J KrishnanNo ratings yet

- Digital Arithmetic: Operations and Circuits: Chapter-6Document44 pagesDigital Arithmetic: Operations and Circuits: Chapter-6Samina TohfaNo ratings yet

- Unit IvDocument62 pagesUnit Ivsnkarthik35No ratings yet

- Chapter 6 Digital Arithmetic: Operations and CircuitsDocument63 pagesChapter 6 Digital Arithmetic: Operations and CircuitsHugo Arriagada AlbarranNo ratings yet

- Number SystemDocument18 pagesNumber SystemJanarthanan SubramanianNo ratings yet

- Publication 6 431 6508Document19 pagesPublication 6 431 6508Damilola OniNo ratings yet

- 198:211 Computer Architecture: TopicsDocument35 pages198:211 Computer Architecture: TopicsJaswant SinghNo ratings yet

- Unit 3 - Computer Organization and Architecture - WWW - Rgpvnotes.inDocument17 pagesUnit 3 - Computer Organization and Architecture - WWW - Rgpvnotes.inAreeba RizviNo ratings yet

- Lecture #3Document13 pagesLecture #3Abdii MakNo ratings yet

- Addition and Subtraction With Signed 2s ComplementDocument3 pagesAddition and Subtraction With Signed 2s ComplementMoses DianNo ratings yet

- Convolutional (Viterbi) Encoding: Input A Input B OutputDocument14 pagesConvolutional (Viterbi) Encoding: Input A Input B Outputeliezer lopezNo ratings yet

- Computer Organisation Midterm - Ii Solution 12.30 PM To 2.30 PM Time: 2 HrsDocument4 pagesComputer Organisation Midterm - Ii Solution 12.30 PM To 2.30 PM Time: 2 HrsVIKRAM KUMARNo ratings yet

- Digital Electronics Registers Transfer Logic and Micro-Operation (1) .PPSXDocument18 pagesDigital Electronics Registers Transfer Logic and Micro-Operation (1) .PPSXNGUYỄN HOÀNG LINHNo ratings yet

- Digital Electronics Registers Transfer Logic and Micro-Operation (1) .PPSXDocument18 pagesDigital Electronics Registers Transfer Logic and Micro-Operation (1) .PPSXNGUYỄN HOÀNG LINHNo ratings yet

- GS01 Digital Systems and Binary NumbersDocument4 pagesGS01 Digital Systems and Binary NumbersMark Renzkie Casanova CulambotNo ratings yet

- ConvolutionalcodesDocument30 pagesConvolutionalcodesprakash_oxfordNo ratings yet

- Complete-Unit-01-Soft Copy of Notes - Computer Data Representations - CAODocument15 pagesComplete-Unit-01-Soft Copy of Notes - Computer Data Representations - CAOaayushgithala101No ratings yet

- Computer Arithmetic (5 Hours)Document27 pagesComputer Arithmetic (5 Hours)Rahithya AmbarapuNo ratings yet

- Machine Instructions and ProgramsDocument7 pagesMachine Instructions and ProgramsComputer NotesNo ratings yet

- LabWeek4 - M CyrulikDocument4 pagesLabWeek4 - M CyrulikMark CyrulikNo ratings yet

- Unit - II: Computer ArithmeticDocument41 pagesUnit - II: Computer ArithmeticRiajiminNo ratings yet

- Midterm 2 SolDocument8 pagesMidterm 2 SolACDNo ratings yet

- Homework 10 Computer Architecture: Name Student Code Section NoDocument1 pageHomework 10 Computer Architecture: Name Student Code Section NoHarshit RastogiNo ratings yet

- Numbers, Representations, and Ranges Ivor PageDocument9 pagesNumbers, Representations, and Ranges Ivor PageXiaomi MIX 3No ratings yet

- COA Unit 2Document25 pagesCOA Unit 2Shivam KumarNo ratings yet

- Short Exam 1Document2 pagesShort Exam 1espfb1807No ratings yet

- Assingnment# 1Document8 pagesAssingnment# 1Tayyab AbbasNo ratings yet

- Mod 1 2Document20 pagesMod 1 2Naseef RahmanNo ratings yet

- Digital ElectronicDocument17 pagesDigital Electronicfaiyaz pardiwalaNo ratings yet

- Description of The Algorithms (Part 1)Document6 pagesDescription of The Algorithms (Part 1)Darshan Yeshwant MohekarNo ratings yet

- Co 2 Marks All Units Q & A Final PrintDocument10 pagesCo 2 Marks All Units Q & A Final PrintArun VijayNo ratings yet

- AE 242 Aerospace Measurements LaboratoryDocument60 pagesAE 242 Aerospace Measurements LaboratoryAnubhavNo ratings yet

- Dl5 ArithmeticDocument23 pagesDl5 Arithmeticomgcharlie12No ratings yet

- Comparators and Code ConvertersvDocument36 pagesComparators and Code ConvertersvReena JacobNo ratings yet

- Computer Architecture CS 45101 CS 55101: Arithmetic For ComputersDocument63 pagesComputer Architecture CS 45101 CS 55101: Arithmetic For ComputersArchana AnilNo ratings yet

- Ade (Unit 1)Document80 pagesAde (Unit 1)SHUBHAMKAR JOSHINo ratings yet

- Lect 3Document58 pagesLect 3gupta.pagNo ratings yet

- Practice Problems 12Document32 pagesPractice Problems 12suduku007No ratings yet

- Mod 1Document29 pagesMod 1Abin KurianNo ratings yet

- TS-1-Number Systems PDFDocument2 pagesTS-1-Number Systems PDFUdai Kumar33% (3)

- OpenbookDocument1 pageOpenbookpardhu509No ratings yet

- My ProjectDocument31 pagesMy Projectesam eisaNo ratings yet

- Unit - 3Document53 pagesUnit - 3Bhuvan Susheel MekaNo ratings yet

- Combinational Logic Design&AnalysisDocument34 pagesCombinational Logic Design&AnalysisBasheer V.PNo ratings yet

- Coa Chapter 1Document62 pagesCoa Chapter 1mulugetahiluf995No ratings yet

- Compuer Organization (Ce-313) Assignment #2Document2 pagesCompuer Organization (Ce-313) Assignment #2RawabiNo ratings yet

- Integer RepresentationDocument7 pagesInteger Representationmanishbhardwaj8131No ratings yet

- HW1 4Document4 pagesHW1 4yarasultan201No ratings yet

- 2.1 Addtion&subtractionDocument42 pages2.1 Addtion&subtractionGireesh DgNo ratings yet

- CS151B/EE116C - Solutions To Homework #2: ProblemDocument6 pagesCS151B/EE116C - Solutions To Homework #2: ProblemtinhtrilacNo ratings yet

- Module 4Document19 pagesModule 4Amruta KhangaonkarNo ratings yet

- Microprocessor Programming and Interfacing: Number SystemsDocument34 pagesMicroprocessor Programming and Interfacing: Number SystemsKaushikperikaNo ratings yet

- DLD - Question - Final 2022Document2 pagesDLD - Question - Final 2022Md Israfil HossainNo ratings yet

- COA Question Bank-2Document2 pagesCOA Question Bank-2itzzsandeshNo ratings yet

- Full Shape Diamond PatternDocument6 pagesFull Shape Diamond Patternerbk191No ratings yet

- Floyd TriangleDocument3 pagesFloyd Triangleerbk191No ratings yet

- C Coding Question AnswerDocument4 pagesC Coding Question Answererbk191No ratings yet

- Half Pyramid CDocument2 pagesHalf Pyramid Cerbk191No ratings yet

- 6234 5 EN-Maximizing-performance PDFDocument12 pages6234 5 EN-Maximizing-performance PDFSridhar TholasingamNo ratings yet

- BE-201 Practical ExperimentsDocument39 pagesBE-201 Practical ExperimentsKunal DasNo ratings yet

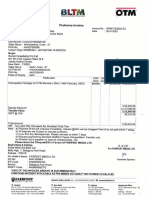

- Sorrel Otm FebDocument1 pageSorrel Otm FebGagandeep SinghNo ratings yet

- Combinational Logic Design With VerilogDocument13 pagesCombinational Logic Design With VerilogWong JulianNo ratings yet

- Geomorphology and Its Different Parameters in The Flood Prone Lower Gandak PainDocument12 pagesGeomorphology and Its Different Parameters in The Flood Prone Lower Gandak PainIJAR JOURNALNo ratings yet

- Layers of The AtmosphereDocument19 pagesLayers of The AtmosphereRalph Andrew AgustinNo ratings yet

- Analysis Shows Magnitude of Z-Factor Error - Oil & Gas JournalDocument8 pagesAnalysis Shows Magnitude of Z-Factor Error - Oil & Gas JournalLdtc ZerrotNo ratings yet

- List of Parameters Programmable by CostomerDocument11 pagesList of Parameters Programmable by Costomerasif mahmoodNo ratings yet

- Biped AnimationDocument18 pagesBiped AnimationHatsuneMikuNo ratings yet

- Mix Design Manual PDFDocument98 pagesMix Design Manual PDFB R Paul FortinNo ratings yet

- ACI Multi-Site Architecture and Deployment: Max Ardica Principal Engineer - INSBUDocument31 pagesACI Multi-Site Architecture and Deployment: Max Ardica Principal Engineer - INSBUDavIdFernsNo ratings yet

- Adv Chem Lab Report - 3Document3 pagesAdv Chem Lab Report - 3Braden ShugarmanNo ratings yet

- Guia TapconDocument24 pagesGuia TapconCristian AndresNo ratings yet

- Start Download - View PDF: 110 Top Most Control SYSTEMS Objective Questions and Answers PDFDocument24 pagesStart Download - View PDF: 110 Top Most Control SYSTEMS Objective Questions and Answers PDFEj ParañalNo ratings yet

- wph12 01 Que 20240119Document36 pageswph12 01 Que 20240119Nethsari DiwyangaNo ratings yet

- BD235 235 237 238Document6 pagesBD235 235 237 238NunzioRossiNo ratings yet

- Mitesh N Doshi, Dept of Instrumentation Technology, RvceDocument22 pagesMitesh N Doshi, Dept of Instrumentation Technology, RvceMitesh DoshiNo ratings yet

- Quiz - RAC Part Two Sp19c (Logan Malone 2018)Document10 pagesQuiz - RAC Part Two Sp19c (Logan Malone 2018)Martha Treviño100% (1)

- A New Extension of The EAP-TLS Protocol Based On Quantum CryptographyDocument8 pagesA New Extension of The EAP-TLS Protocol Based On Quantum CryptographyJournal of ComputingNo ratings yet