Professional Documents

Culture Documents

Mid-Term Analoge

Uploaded by

jfx8j568zj0 ratings0% found this document useful (0 votes)

2 views1 pageOriginal Title

Mid-term+analoge

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

2 views1 pageMid-Term Analoge

Uploaded by

jfx8j568zjCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 1

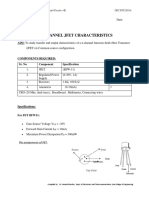

Almughtaribeen University

College of Engineering

MID-TERM EXAM FOR ACADEMIC YEAR 2022

Subject: Analogue electronic circuits ② Level: 3th year

Time: 1.5 Hours Date: 21/sep/2022

ANSWER ALL QUESTIONS AS POSSIBLE YOU CAN

QUESTION ONE: Increased, then width of conducting channel..

1- How many diodes a Junction Field Effect A- Decrease

[Type a quote from the document or

Transistors Contain? B- Increase.

the summary of an interesting point.

2- What is FET biasing? Explain!, and C- RemainsYouthe

cansame.

position the text box

What are the FET biasing circuits? D- None ofanywhere

the above.in the document. Use the

3- Why are FET transistors called unipolar Drawing Tools tab to change the

QUESTION THREE:

formatting of the pull quote text box.]

transistors?

4- Why the channel of a JFET is never 1- Given IDSS=3mA,VGS(OFF)=-6V,

Completely closed at the drain end? gm(max)=5000µS, Determine the

5- What is IDSS is stands for? transconductance for VGS=-4V, and find the

drain current ID at this point.

QUESTION TWO: 2- A JFET in fig. below has values of VGS(off)=-

8V and IDSS=16mA. Determine the values of

1- IDSS can be defined as:

VGS , ID and VDS for the circuit.

A- The minimum possible current.

B- The maximum possible current Then try to sketch transfer characteristic curve

With VGS held at -4 V. of this model

C- The maximum possible current

With VGS held at 0 V.

D- The maximum drain current

With the source shorted

2- When VGS = 0 V, a JFET is:

A- Saturated.

B- An analog device.

C- An open switch.

D- Cut-off.

3- If reverse bias on the gate of JFET is

GOOD LUCK

You might also like

- Lecture Notes For Semiconductor Devices and Circuits: JFET and MOSFETDocument25 pagesLecture Notes For Semiconductor Devices and Circuits: JFET and MOSFETdevashri gaurkedeNo ratings yet

- ECE 027 - Module 5 Field Effect TransistorDocument102 pagesECE 027 - Module 5 Field Effect TransistorMiyuki NakiriNo ratings yet

- EE386 FET - Field Effect TransistorsDocument7 pagesEE386 FET - Field Effect TransistorsKeshara WeerasingheNo ratings yet

- Questions On MOS Field Effect Transistors (MOSFETs)Document59 pagesQuestions On MOS Field Effect Transistors (MOSFETs)kibrom atsbhaNo ratings yet

- Lecture 3 Field Effect TransistorDocument11 pagesLecture 3 Field Effect TransistoralexNo ratings yet

- Module 4 FET MOSFETDocument23 pagesModule 4 FET MOSFETsenthilnathanNo ratings yet

- Exam 2012 Eng20121211Document21 pagesExam 2012 Eng20121211enekoNo ratings yet

- Chapter 4 - JFET PDFDocument13 pagesChapter 4 - JFET PDFnelsonjnelsonjNo ratings yet

- Medical Science: Review of Contemporary Research in Finfet TechnologyDocument3 pagesMedical Science: Review of Contemporary Research in Finfet TechnologyParichay PapnoiNo ratings yet

- Jfet MosfetDocument25 pagesJfet Mosfethrishabhraj710No ratings yet

- VLSI DesignDocument18 pagesVLSI Designkishorereddy416No ratings yet

- Electronic Devices Lab - Exp - 9 - Student - Manual (Summer 18-19)Document3 pagesElectronic Devices Lab - Exp - 9 - Student - Manual (Summer 18-19)MD MONIM ISLAMNo ratings yet

- Self Bias 3Document17 pagesSelf Bias 3Chen Chee JungNo ratings yet

- Design and Simulation of A Two Stage OPAMPDocument4 pagesDesign and Simulation of A Two Stage OPAMPAbd TashNo ratings yet

- Mosfet PDFDocument16 pagesMosfet PDFTejinder SinghNo ratings yet

- General Digital 1. General Digital Design Questions Design QuestionsDocument44 pagesGeneral Digital 1. General Digital Design Questions Design QuestionsAbdul KhaliqNo ratings yet

- Bangladesh University of Engineering and Technology Department of Computer Science and EngineeringDocument7 pagesBangladesh University of Engineering and Technology Department of Computer Science and EngineeringSIAM AL MUJADDEDNo ratings yet

- Electronic Device Suvrodeep Debnath ECE 20-ECE-006 Third Second 8Document7 pagesElectronic Device Suvrodeep Debnath ECE 20-ECE-006 Third Second 8Suvrodeep DebnathNo ratings yet

- 1 s2.0 S2589208821000132 MainDocument8 pages1 s2.0 S2589208821000132 MainEvent DecemberNo ratings yet

- Notes Module2 (FET Part) Basic Electronics 22BBEE203Document12 pagesNotes Module2 (FET Part) Basic Electronics 22BBEE203Hani MNo ratings yet

- Charge Transport Model of Double Gate Tunnel FETDocument7 pagesCharge Transport Model of Double Gate Tunnel FETFahad NibirNo ratings yet

- (NAAC Accredited "A++" Grade University) : Koneru Lakshmaiah Education FoundationDocument13 pages(NAAC Accredited "A++" Grade University) : Koneru Lakshmaiah Education FoundationLakshmi JagupillaNo ratings yet

- ED - Final Lecture-3Document17 pagesED - Final Lecture-3Arindam DeyNo ratings yet

- Fet MosfetDocument20 pagesFet MosfetnupurnehaNo ratings yet

- Expt - 11: JFET CharacteristicsDocument8 pagesExpt - 11: JFET CharacteristicssamarthNo ratings yet

- 1 Self-BiasDocument6 pages1 Self-BiasSaurav ChourasiaNo ratings yet

- 1 Self-BiasDocument6 pages1 Self-BiasSaurav ChourasiaNo ratings yet

- LP 4Document5 pagesLP 4etasureshNo ratings yet

- 1T Capacitor-Less DRAM Cell Based OnDocument6 pages1T Capacitor-Less DRAM Cell Based OnmaheshNo ratings yet

- Chapter 4Document15 pagesChapter 4Gizachew BalchaNo ratings yet

- Ec8095 Vlsi QBDocument17 pagesEc8095 Vlsi QBManimegalaiNo ratings yet

- Electronic Devices and Circuit LabDocument30 pagesElectronic Devices and Circuit LabANo ratings yet

- Lab 4 Directional CouplerDocument10 pagesLab 4 Directional Couplernurin runNo ratings yet

- DEE20023 Chapter 4 JUNCTION FIELD EFFECT TRANSISTOR SESI II 20222023Document51 pagesDEE20023 Chapter 4 JUNCTION FIELD EFFECT TRANSISTOR SESI II 20222023Muhd ZarifNo ratings yet

- Koneru Lakshmaiah Education Foundation: Department of Electronics and Communication EngineeringDocument11 pagesKoneru Lakshmaiah Education Foundation: Department of Electronics and Communication EngineeringLakshmi JagupillaNo ratings yet

- JFET AmplifierDocument4 pagesJFET AmplifierSakshi GosaviNo ratings yet

- Module 2Document51 pagesModule 2eswarsenthil2004No ratings yet

- MOS Integrated Circuit DesignFrom EverandMOS Integrated Circuit DesignE. WolfendaleNo ratings yet

- Exam5 SolutionsV3 S15Document7 pagesExam5 SolutionsV3 S15s22bxyggzsNo ratings yet

- Ee141 HW5 2Document3 pagesEe141 HW5 2Vidhya DsNo ratings yet

- Fet (2014) PDFDocument87 pagesFet (2014) PDFJoanne Mendoza IlaoNo ratings yet

- Comparison of Cable Models For Time Domain SimulationsDocument5 pagesComparison of Cable Models For Time Domain SimulationsGokul VenugopalNo ratings yet

- 5.0 Field Effect Transistor (FET)Document50 pages5.0 Field Effect Transistor (FET)F1038 IFFAH SYAZANA BINTI MD HASNIN HADINo ratings yet

- Section 3A Transmission Lines PackageDocument10 pagesSection 3A Transmission Lines PackagealfredomatiasrojoNo ratings yet

- EDC-II Unit-3 Field Effect Transistor & MOSFET TheoryDocument34 pagesEDC-II Unit-3 Field Effect Transistor & MOSFET TheorysamarthNo ratings yet

- Updated Handout Bandgap PDFDocument11 pagesUpdated Handout Bandgap PDFvishal kumarNo ratings yet

- Topic FET - 16 CompleteDocument33 pagesTopic FET - 16 CompleteShelbyNo ratings yet

- EI5007W1D2Document8 pagesEI5007W1D2PyiAungNo ratings yet

- Investigation of Dielectric Modulated DG-MOSFET With Different Configuration For Biosensor ApplicationsDocument25 pagesInvestigation of Dielectric Modulated DG-MOSFET With Different Configuration For Biosensor ApplicationsAnand KumarNo ratings yet

- Dančak2018 Chapter TheFinFETATutorialDocument33 pagesDančak2018 Chapter TheFinFETATutorialAhmed KamalNo ratings yet

- Vlsi Design - Ec - 701 - Unit - 2Document18 pagesVlsi Design - Ec - 701 - Unit - 2angelcrystl4774No ratings yet

- Ec 301 2Document4 pagesEc 301 2Samaira Shahnoor ParvinNo ratings yet

- Expt 13 - JFET-CharaceristicsDocument8 pagesExpt 13 - JFET-CharaceristicssamarthNo ratings yet

- EC8353 EDC by WWW - Learnengineering.inDocument92 pagesEC8353 EDC by WWW - Learnengineering.inAnush KannanNo ratings yet

- Tutorial 5 MosDocument3 pagesTutorial 5 MosomerNo ratings yet

- Questions On DiodesDocument40 pagesQuestions On Diodeskibrom atsbha100% (1)

- Hospital Management Using Circular Queue Linked ListDocument22 pagesHospital Management Using Circular Queue Linked ListRam Kiran Devireddy0% (2)

- Mos Transistor Review: 3D Band Diagram of A Long Channel Enhancement Mode NMOS TransistorDocument14 pagesMos Transistor Review: 3D Band Diagram of A Long Channel Enhancement Mode NMOS TransistorKumar Amit VermaNo ratings yet

- It Is Quite Another Electricity: Transmitting by One Wire and Without GroundingFrom EverandIt Is Quite Another Electricity: Transmitting by One Wire and Without GroundingNo ratings yet

- Elec Eng 2ei5 Microelectronic Devices and Circuits I Winter 2013 Final Exam - 4/22/13Document7 pagesElec Eng 2ei5 Microelectronic Devices and Circuits I Winter 2013 Final Exam - 4/22/13SonDinhQuangNo ratings yet

- 5 CMOS Amplifiers - AC AnalysisDocument11 pages5 CMOS Amplifiers - AC AnalysisRamo ZNo ratings yet

- Hoja Caracteristica Trasistor 2N6059Document5 pagesHoja Caracteristica Trasistor 2N6059Alejandro G SantosNo ratings yet

- Chapter 11 Part 3 Differential Amplifier With Active LoadDocument8 pagesChapter 11 Part 3 Differential Amplifier With Active Loadbhala rraadjNo ratings yet

- Bipolar Junction TransistorsDocument55 pagesBipolar Junction Transistorshuy PhamNo ratings yet

- SMD N-CH MOSFET Transistor PDFDocument1 pageSMD N-CH MOSFET Transistor PDFkhawar mukhtarNo ratings yet

- GTODocument29 pagesGTOAjay TalajiyaNo ratings yet

- Fault Modelling and Accelerated Simulation of Integrated Circuits Manufacturing Defects Under Process Varia 1Document200 pagesFault Modelling and Accelerated Simulation of Integrated Circuits Manufacturing Defects Under Process Varia 1Alessandro BerciouxNo ratings yet

- Lab 9 TransistorDocument8 pagesLab 9 TransistorChing Wai YongNo ratings yet

- 2 Sa 1141Document3 pages2 Sa 1141Jesus GCNo ratings yet

- Test 5 ThyristorsDocument14 pagesTest 5 ThyristorsViktor RudanNo ratings yet

- 2 SD 1877Document2 pages2 SD 1877GoTripGPS VelocidadNo ratings yet

- DiodesDocument2 pagesDiodesRO-AM-BDNo ratings yet

- Unit - 5Document66 pagesUnit - 5Lavanya MNo ratings yet

- Power Electronics Ned Mohan Slides Ch21Document27 pagesPower Electronics Ned Mohan Slides Ch21Anoop MathewNo ratings yet

- Comparison of Sic Mosfet and Si IgbtDocument10 pagesComparison of Sic Mosfet and Si IgbtYassir ButtNo ratings yet

- CH 1Document15 pagesCH 1demos2011No ratings yet

- Wafer Level Package and Technology (Amkor)Document17 pagesWafer Level Package and Technology (Amkor)David GiulianoNo ratings yet

- 2N 6107Document5 pages2N 6107Alok Pokharel100% (1)

- Spice Mosfet Model IntroDocument58 pagesSpice Mosfet Model IntrodeancjenningsNo ratings yet

- Electronic Devices & Circuits SyllabusDocument4 pagesElectronic Devices & Circuits SyllabusShareef KhanNo ratings yet

- MC14070B, MC14077B Cmos Ssi: Quad Exclusive "OR" and "NOR" GatesDocument8 pagesMC14070B, MC14077B Cmos Ssi: Quad Exclusive "OR" and "NOR" Gateskarácsonyi krampuszNo ratings yet

- SMD Darlington Transistor (NPN)Document3 pagesSMD Darlington Transistor (NPN)Majk StoneNo ratings yet

- Exercises Problems Answers Chapter 5Document5 pagesExercises Problems Answers Chapter 5A Sibiescu100% (1)

- Group 2Document21 pagesGroup 2AkiNo ratings yet

- Evolution of MicroprocessorDocument11 pagesEvolution of MicroprocessorJeswanth JeshuNo ratings yet

- A-Si TFT LCDDocument20 pagesA-Si TFT LCDngoccuong832003No ratings yet

- Semiconductor 2N7000: Technical DataDocument4 pagesSemiconductor 2N7000: Technical DataFrancisco RodriguesNo ratings yet

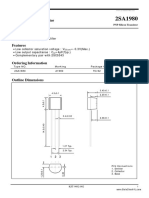

- 2SA1980 DatasheetDocument3 pages2SA1980 DatasheetDOMINGOSERPA4148No ratings yet

- Edt 224L Lab ManualDocument34 pagesEdt 224L Lab ManualAnilaSaghirNo ratings yet