Professional Documents

Culture Documents

Ldco MCQ

Uploaded by

TEIT38 prasad Pansare0 ratings0% found this document useful (0 votes)

4 views50 pagesOriginal Title

LDCO-MCQ

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

4 views50 pagesLdco MCQ

Uploaded by

TEIT38 prasad PansareCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 50

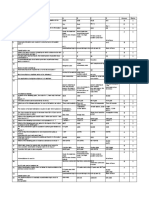

This sheet is for 2 Mark questions

S.r NoTest_ID Question Figure A B C D Answer Marks

1 Boolean expression

Simplify the expression F = C(Bpostulates

using Boolean + C)(A + BY+=C).

(A + B)( Ā A A+B+C A.B C D 1

2 + C)(B + C) A.B.C AC + B Ā AB+ĀC BĀ B 1

3 An inverter

The performs

output of an operation

gate is HIGH when atknown as of its inputs is

least one Complementation

assertion Inversion both answers (a)D and (c) 1

4 LOW. It is true for AND OR NAND NOR C 1

0 1 equal to the

the inverse of D

5 The complement of a variable is always variable the 1

ComplementOriginal 0 1

B

6 Inversion law states that double inversion of a variable results in variable 1

7 Boolean Algebra is used to analyze and simplify the_______ ckts Analog Digital Both are included

Both are not included

B 1

8 The OR operator represents ________ of variables Addition SubtractionMultiplication

Division A 1

9 The AND operator represents ________ of variables Addition SubtractionMultiplication

Division C 1

10 Which gate is known as Universal gate NAND OR AND NAND and NORD 1

11 If we have to perform logical Addition we will use ______ gate AND OR NOT None of the above

B 1

12 If we have to perform logical Multiplication we will use ______ gate AND OR NOT None of the above

A 1

Boolean Canonical Algebric Expression

None of them

A

13 Relation between inputs and outputs can be represented by Expressio Expressio 1

14 A.B expression will use _____ gate A NAND B A OR B A not B A AND B D 1

15 IC used for Ex-OR is 7486 7404 7408 7432 A 1

16 A digital system consists

signal having of ______

_____ disticntno. of values

values is called as Finite Infinite Large but Finite

Finite but smallA 1

17 hexadecimal signal Two Ten Eight sixteen D 1

18 Digital signals are __________ time signals Continous Random Discerte Fluctuate C 1

Counter Code Amplifier Microprocessor

C

19 Which of the following is not digital Converte 1

20 The High Level signal as Outcome In binary logic represents Logic 0 Logic 1 Null Constant B 1

Digital Digital Digital Digital

signals signals signals signals

C

are light are easy are less create

21 Advantage of Digital signal over analog signal is weight to use noisy more 1

22 A binary digit 0 or 1 is referred as Bit nibble Byte Double word A 1

23 Nibble is represented by _______ bits 8 16 32 4 D 1

24 Double word is represented by _______ bits 8 16 32 4 C 1

25 Sinewave or Triangular wave is example of _________ signal Analog Digital Discere Random A 1

26 In Negative Logic, a LOW voltage level represents Logic 0 Logic 1 Null Constant B 1

27 In Negative Logic, a High voltage level represents Logic 0 Logic 1 Null Constant A 1

28 When used with an IC, what does the term "QUAD" indicate 2 circuits 8 circuits 6 circuits 4 circuits D 1

29 Which of the following logical operations is represented by the inversion AND OR complementation C 1

all inputs are

anyHIGH

input any input isallLOW

inputs are LOW

D

30 The output of a NOR gate is HIGH if ________ is HIGH 1

31 The Boolean expression for a 3-input AND gate is ________ X = AB X = ABC X = A + B +XC= AB + C B 1

32 The _____ Law states that A·B = B·A Commutative Associativ DistributiveDuality A 1

33 The _____ Law states that (A·B)·C = A·(B·C) Commutative Associativ DistributiveDuality B 1

Duality Theorm states that ______ are allowed in a Boolean ConversionManipula Multiplication

Division

A

34 expression tion 1

35 In AND laws A.0=0 represents that one variable in AND High Null Constant Low D 1

36 In AND laws A.1= A represents that one variable in AND High Null Constant Low A 1

37 In AND laws A.Ā= 0 represents that one variable in AND High Null Constant Low D 1

OR gate NOR gate NOR gate NAND

and and and gate and B

38 De-Morgans second theorm shows the equivalance between exclusive NAND Bubbled NOR gate 1

39 A+ĀB = __________ 0 Ā A+B Ā+B C 1

Bubbled AND Bubbled Bubbled OR

NAND

C

40 According to De-Morgans theorm NOR = ______________ NAND 1

41 Solve A+ĀB+AB= ________________ A+1 A+B A+Ā A B 1

The output of a logic gate is 1 when all its inputs are at logic 0. a NAND or an OR EX-OR

or an AND or aanNOR

EX-OR

or an EX-NOR

D

42 the gate is either an EX- 1

OR gate NOR gate NOR gate NAND gate and NOT gate

and and and B

43 DeMorgan’s first theorem shows the equivalence of Exclusive Bubbled NAND 1

44 How many AND gates are required to realize Y = CD+EF+G 4 5 3 2 D 1

positive voltage

higher zero voltage

lower

levelvoltage level

voltage B

45 In a positive logic system, logic state 1 corresponds to level 1

46 How many two-input AND and OR gates are required to realize 2,2 2,3 3,3 none of these. A 1

47 A universal logic gate is one, which can be used to generate OR AND XOR NAND D 1

parity gateequality gate inverted OR parity

gate or

B

the

48 The Ex-NOR is sometimes called the ________. equality 1

49 IC 7432 is used for OR NOR AND EX-OR A 1

50 IC 7404 is also known as inverter hexinvertercomplement None of them B 1

51 For 3 input And gate we use____ IC 7404 7432 7411 7400 C 1

52 Any number with an exponent of zero is equal to: Zero One that number Ten B 1

53 In the decimal numbering system, what is the MSD? The middleThe digitdigit

of ato

stream

The

thelast

right

ofdigit

numbers

of

Thethe

ondigit

the

decimal

with D most weight1

rightthe

point

54 What are the symbols used to represent digits in the binary number system? 0,1 0,1,2 0 through 81,2 A 1

55 A full subtractor circuit has ________. two inputs twoand inputs

two outputs

three

and three

inputsthree

outputs

andinputs andD two outputs 1

one output

56 The output of an AND gate is LOW ________. all the timewhen any input whenisany LOW input

when isallHIGH

inputs Bare HIGH 1

57 The output of a NOT gate is HIGH when ________. the input istheLOWinput isthe

HIGHinput changes

voltage is from

removed

LOW

A to from

HIGH 1

the gate

58 The output of an OR gate is LOW when ________. all inputs areanyLOW

input isany

LOWinput isallHIGH

inputs are HIGHA 1

59 In positive logic, ________. a HIGH = 1,aaLOW LOW==1,0only

a HIGH

HIGHs= 0only

are LOWs

present are present

A 1

–1 0.5 0.25 0.05 0.1

60 What is the decimal value of 2 ? A 1

61 A type of digital circuit technology that uses bipolar junction transistors isTTL

________.CMOS LSI NMOS A 1

62 How many unique symbols are used in the decimal number system? One Nine Ten Unlimited C 1

63 A classification of ICs with complexities of 12 to 100 equivalent gates onSSI MSI as ________.

a chip is known LSI VLSI B 1

64 A classification of ICs with complexities of 100 to 10,000 equivalent gatesSSIper chip isMSIknown as LSI________.VLSI C 1

65 The output of an AND gate with three inputs, A, B, and C, is HIGH when ________. A = 1, B = 1,AC==0,0B = 0,A C= =1,0B = 1,AC = 1,

= 1B = 0, C =C1 1

66 If a 3-input NOR gate has eight input possibilities, how many of those possibilities

1 will2 result in a7HIGH output? 8 A 1

67 If a signal passing through a gate is inhibited by sending a LOW into one of the ANDinputs, NAND

and the output

NOR is HIGH, ORthe gate is B 1

68 The output of an OR gate with three inputs, A, B, and C, is LOW when ________ A = 0, B = 0,AC==0,0B = 0,A C= =0,1B = 1,allCof= the

1 aboveA 1

69 Which of the following logical operations is represented by the + sign in Booleaninversion AND

algebra? OR Complementation C 1

70 Output will be a LOW for any case when one or more inputs are zero for OR gate NOT gate AND gate NOR gate C 1

71 If a 3-input AND gate has eight input possibilities, how many of those possibilities

1 will2result in a7HIGH output? 8 A 1

72 What are the pin numbers of the outputs of the gates in a 7432 IC? 3, 6, 10, and 1,13

4, 10, and3, 13

6, 8, and1,11 4, 8, and 11 C 1

73 If the input to a NOT gate is A and the output is X, then ________ X=A X=0 none of the above B 1

74 How many truth table entries are necessary for a four-input circuit? 4 8 12 16 D 1

75 for AND gate : X.X'=____ 1 0 X X' B 1

76 what is 2's compliment 1's compliment

2's compliment

& add1 only add1

& subtract

none 1 A 1

77 which of the number is not representative of hexadecimal sysytem 1234 ABCD 1001 DEFH D 1

78 If all inputs to a TTL NAND gate are low, what is the ON, OFF condition of each

Q1-ON,

transistor

Q2-OFF,

Q1-ON,

in the

Q3-ON,

Q2-ON,

circuit?

Q1-OFF,

Q4-OFF

Q3-OFF,

Q2-OFF,

Q1-OFF,

Q4-OFF

Q3-ON,

Q2-ON,Q4-ON

AQ3-OFF, Q4-ON

1

79 Solving –11 + (–2) will yield which two's-complement answer? 1110 1101 1111 10011111 00111110 1001 C 1

80 The BCD number for decimal 347 is ________. 1100 1011 0011

1000 0100 00110111 0100110000011011 0110B 1

81 while obtaining 2' s compliment __ is not change MSB LSB Both NONE A 1

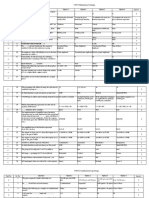

82 The value of A+ĀB+AB is equal to A+B A Ā AB A 2

83 The value of ABCD+ A CD is equal to 0 1 ACD ABCD C 2

84 Simplify the expression and find the result A +Ā B + AB + Ā 0 1 AC AB B 2

85 Simplify the expression and find the result A C+ĀBC +ABC AC+ B C(A+B) AC C 2

86 Simplify the expression and find the result A+ĀB +AB A+B AB A A 2

87 Simplify the expression and find the result Y= (AB + C) (AB + D) A+B A+C AB+CD A+CD C 2

88 Simplify the expression and find the result Y= AB+ABC+A B A ABC AB+C B 2

89 Simplify the following expression Y= (A+B)(A+C) A+BC AB AC A+C A 2

90 Give the decimal value of binary 10010. 6 9 18 20 C 2

91 In a certain digital waveform, the period is four times the pulse width. The duty

0% cycle is25% 50% 100% B 2

92 A pulse has a period of 15 ms. Its frequency is ________. 6.66 Hz 66.66 Hz 666.66 Hz 15 Hz B 2

93 Give the decimal value of binary 10000110. 134 144 110 126 A 2

–1 0.5 0.25 0.05 0.1

94 What is the decimal value of 2 ? A 2

95 The output of an AND gate with three inputs, A, B, and C, is HIGH when ________.

A = 1, B = 1,AC==0,0B = 0,A C= =1,0B = 1,

AC = 1,

= 1B = 0, C =C1 2

96 If a 3-input NOR gate has eight input possibilities, how many of those possibilities

1 will

2 result in7a HIGH output?8 A 2

97 When used with an IC, what does the term "QUAD" indicate? 2 circuits 4 circuits 6 circuits 8 circuits B 2

98 The output of an OR gate with three inputs, A, B, and C, is LOW when ________.

A = 0, B = 0,AC==0,0B = 0,A C= =0,1B = 1,

allCof= the

1 aboveA 2

99 What are the pin numbers of the outputs of the gates in a 7432 IC? 3, 6, 10, and1,134, 10, and3, 13

6, 8, and1,114, 8, and 11 C 2

NAND OR gate AND gate NOR gate

gate immediat immediat immediat

B

immediat ely ely ely

100 Logically, the output of a NOR gate would have the same Boolean expression elyas: followed followed followed 2

7400 has 7400 has 7400 has 7400 has

two four- four two- two four- four two-

input input input input AND

NAND NAND AND gates; B

gates; gates; gates; 7410 has

7410 has 7410 has 7410 has two three-

101 What is the difference between a 7400 and a 7410 IC? three three four input 2

A clock signal with a period of 1 microsec.is applied to the Enable

input of an enable gate. The output must contain six pulses. must be c

102 How long must the enable pulse be active? Enable must Enable

be active

must Enable

for

be0active active

microsec.

must for for

be3active

microsec

for 6 microsec 2

103 If a 3-input OR gate has eight input possibilities, how many of those possibilities

1 will result

2 in a HIGH

7 output? 8 C 2

104 How many input combinations would a truth table have for a six-input AND 32gate? 48 64 128 C 2

an

inverter

B

that has a

105 The term "hex inverter" refers to: an invertersix that

inverters

has sixa inputs

six-input

in a single history

symbolic

packageof logic device 2

106 How many AND gates are found in a 7408 IC? 1 2 3 4 D 2

107 Which of the following equations would accurately describe a 1 + 1 + 0 + 01 =+ 01

1 + 0 + 10 += 1 + 0 + 10 += 10 + 0 + 0 = 00 B 2

108 What is the Boolean expression for a four-input OR gate? Y = A + B +YC =+ A D · B · CY ·=DA – B Y– C= A– D$ B $ C $AD 2

109 How many truth table entries are necessary for a four-input circuit? 4 8 12 16 D 2

110 How many entries would a truth table for a four-input NAND gate have? 2 8 16 32 C 2

111 From the truth table for a three-input NOR gate, what is the A = 1, B = 1, A C= 1,

= 1B = A 0, =C 0,= 0B = A0, =C 0,= B1 = 0, C D=0 2

112 Convert the following SOP expression to an equivalent POS expression. B 2

113 Determine the values of A, B, C, and D that make the sum term A = 1, B =equal

0,AC==1,

to0,Bzero.

D= =0,A0C= =0,1,B D= =1,

A0C= 1,

= 0,

BD = 0,

= 0C =B1, D = 1 2

114 Which of the following expressions is in the sum-of-products (SOP) form? (A + B )(C +(AD)B ) (CD ) AB (CD ) AB + CD D 2

a NOR a NAND an AND a NOR

and an and an and a and a

One of De Morgan's theorems states that Simply AND gate OR gate NOR gate NAND A

stated, this means that logically there is no difference with with with gate with

115 between: inverted inverted inverted inverted 2

116 The commutative law of Boolean addition states that A + B = A × B . TRUE FALSE Both (a) and None

(b) of these B 2

117 Applying DeMorgan's theorem to the expression , we get ________. A 2

118 Which output expression might indicate a product-of-sums circuit construction? D 2

119 An AND gate with schematic "bubbles" on its inputs performs the same function

NOT as a(n)________

OR NORgate. NAND C 2

120 For the SOP expression , how many 1s are in the truth1 table's output

2 column? 3 5 C 2

121 A truth table for the SOP expression has how many input

1 combinations?

2 4 8 D 2

122 How many gates would be required to implement the 1 2 4 5 D 2

123 Determine the values of A, B, C, and D that make the product term A = equal

0, B = to

1,AC

1.

==0,0,BD= =0,A1C= =1,0,B D= =1,

A1C= 0,

= 1,

BD= 0,

= 1C =A1, D = 0 2

124 AC + ABC = AC TRUE FALSE Both (a) and None

(b) of these A 2

125 A 4-variable AND-OR-Invert circuit produces a 0 at its Y output. Which combination of inputs is correct? none of the above C 2

126 In a graphical representation of voltage versus time, ________ time, y , voltage,

voltage,x y ,Bothtime,(a)x and None

(b) of these B 2

127 Solving –11 + (–2) will yield which two's-complement answer? 1110 1101 1111 10011111 00111110 1001 C 2

128 The 2's-complement system is to be used to add the signed –113 and –114,

–14 and–227–13,–11–27 and –16, –27–27

and –13, –40 B 2

129 The decimal value for E16 is: 12 13 14 15 C 2

130 The binary subtraction 0 – 0 = difference =difference

0 borrow=difference

=10borrowdifference

==10borrow==11borrow

A =1 2

131 Convert each of the decimal numbers to 8-bit two's- 0001 001 0000 111 0010 11101110 0000 B 2

132 Adding in binary, a decimal 26 + 27 will produce a sum of: 111010 110110 110101 101011 C 2

133 Convert each of the following signed binary numbers (two's- –5 +4 +8+5 –4 –8–5 +252 +5+248 –252 –248 B 2

134 Convert hexadecimal value 16 to decimal. 22 16 10 20 A 2

135 Convert decimal number 187 to 8-bit binary. 10111011 1.1E+07 1E+07 10111100 A 2

136 Convert binary 111111110010 to hexadecimal. EE2 FF2 2FE FD2 B 2

137 Convert binary number 01011 to decimal. 11 35 15 10 A 2

138 Convert the binary number 1001.0010 to decimal. 90.125 9.125 125 12.5 B 2

139 Convert decimal 59 to BCD 111011 1011001 1110.11 1.01E+14 B 2

140 Convert 8B3F Hexadecimal to binary. 35647 11010 ####### 1E+15 D 2

141 Convert 17 octal number to decimal. 51 82 57 15 D 2

142 Convert decimal 64 to binary. 1010010 1000000 110110 1001000 B 2

143 Convert 010111100 binary number to octal. 172 272 174 274 D 2

144 The BCD number for decimal 347 is ________. 1100 1011 0011

1000 0100 0011 0111 01001100 00011011 0110B 2

145 The binary number for octal 45 is ________. 100010 100101 110101 100100 B 2

146 The sum of 11101 + 10111 equals ________. 110011 100001 110100 100100 C 2

147 Convert 10011010 binary number to decimal. 154 155 153 157 A 2

148 The decimal number 188 is equal to the binary number ________. 10111100 111000 1100011 1111000 A 2

149 Convert 001101011 binary number to octal. 153 351 253 352 A 2

150 A binary number's value changes most drastically when the ________ is changed.

MSB frequency LSB duty cycle A 2

151 Convert decimal 213 to binary. 11001101 1.1E+07 1.1E+07 10010111 B 2

152 Give the decimal value of binary 10000110. 134 144 110 126 A 2

153 Convert 527 Octal to binary. 11100111 1E+08 343 1.11E+08 B 2

154 The BCD number for decimal 96 is ________. 10010110 10000 10010 11100000 A 2

155 Convert B5 hexadecimal number to decimal. 212 197 165 181 D 2

156 What is the decimal value of the hexadecimal number 777? 191 1911 19 19111 B 2

157 Convert 731 Hexadecimal to decimal. 216.4 985 3D9 1841 D 2

158 Convert 74 decimal number to hexadecimal. A4 B4 4A 4B C 2

159 Convert the binary number 1011010 to hexadecimal. 5B 3F 5A 5C C 2

160 Convert 1CF hexadecimal number to decimal. 463 4033 479 4049 A 2

161 The octal number for binary 1101110101110110 is ________. 654521 556561 156656 156566 D 2

162 What is the result when a decimal 5238 is converted to base 16? 327.375 12.166 1388 1476 D 2

163 Convert the BCD number to decimal100000000011bcd 8003 803 1003 103 B 2

164 The binary number 11001110 is equal to the decimal number ________. 12 206 127 66 B 2

165 Convert 457 decimal to hexadecimal. 711 811 2C7 1C9 D 2

166 Determine the decimal equivalent of the signed binary number 11110100 in116

1's complement.

–12 –11 128 C 2

167 Convert the Gray code 1011 to binary. 1011 1010 100 1101 D 2

168 What decimal number does hexadecimal 25 represent? 10 31 25 37 D 2

169 Which of the following is an invalid BCD code? 11 1101 101 1001 B 2

170 The difference of 111 – 001 equals ________. 100 111 1 110 D 2

171 What is the resultant binary of the decimal problem 49 + 01 = ? 1010101 110101 110010 110001 C 2

172 A decimal 11 in BCD is ________. 1011 1100 10001 10010 C 2

173 Convert 125 decimal number to hexadecimal. 7D D7 7C C7 A 2

174 Add the following hex numbers: 011016 + 1001016 10120 10020 11120 120 A 2

175 Adding in binary, a decimal 26 + 27 will produce a sum of: 111010 110110 110101 101011 C 2

176 How many basic binary subtraction operations are possible? 4 3 2 1 A 2

the the C

the minuend minuend

minuend is is left in the

and the changed its minuend

subtrahe to 2's- original and

nd are complem form and subtrahen

both ent and the d are both

changed the subtrahe left in

to the 2's- subtrahe nd is their

complem nd is left changed original

177 When performing subtraction by addition in the 2's-complement system: ent. in its to its 2's- form. 2

178 When 1100010 is divided by 0101, what is the decimal remainder? 2 3 5 6 B 2

inverting C

179 One way to make a four-bit adder perform subtraction is by: theoutput.

inverting the carry- inverting the

grounding

B inputsthe B inputs. 2

180 What is the most important operation in binary-coded decimal (BCD) arithmetic?

addition subtractionmultiplication division A 2

181 The range of positive numbers when using an eight-bit two's-complement system

0 to 64 is: 0 to 100 0 to 127 0 to 256 C 2

182 What are the two types of basic adder circuits? sum and carry

half-adder asynchronous

and full-adder

one-and

andsynchronous

two's-complement

B 2

183 Determine the two's-complement of each binary number.00110 0001111001 11101

11100

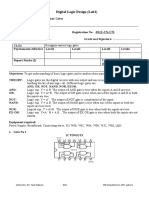

0011100010 00010

001100001000011

11010 11101

11101 D 00011 2

184 Solve this binary problem: 01110010 – 01001000 = 11010 101010 1110010 111100 B 2

It is It is It is It requires C

slower easier to faster advance

than the impleme than a knowledg

ripple- nt ripple- e of the

185 What distinguishes the look-ahead-carry adder? carry logically carry final 2

186 Perform the following hex subtraction: ACE16 – 99916 = 235 135 35 335 B 2

187 Convert the signed decimal numbers to an 8-bit signed binary number (two's-complement).

11111101 1.1E+07–3 1E+07 10101101 A 2

188 Solve this binary problem: 01000110 ÷ 00001010 = 111 10011 1001 11 A 2

189 Convert the decimal numbers 275 and 965 to binary-coded 1101 1110 1110

1010 1010 0001

1110 00100010

01000011

00000100C0000 2

190 When multiplying 13 × 11 in binary, what is the third partial product? 1011 0 100000 100001 B 2

191 An 8-bit register may provide storage for two's-complement codes within which

+128 to

decimal

–128

–128

range?

to +127

+128 to –127

+127 to –127 B 2

groups simplifies D

binary tasks and

numbers saves saves

192 The octal numbering system: in groups

simplifies tasks time time 2

193 The binary number 1110 is equal to the decimal number ________. 3 1 7 14 D 2

194 Convert the following decimal number to octal 281 134 431 331 133 B 2

195 Convert the following octal number to decimal 358 71 17 92 29 D 2

196 Convert binary 11001111 to hexadecimal. 8F CE DF CF D 2

197 1’s complement representation of decimal number of -17 by using 8 bit representation

1110 1110 1101

is 11011100 11000001 0001 A 2

198 The excess 3 code of decimal number 26 is 0100 1001 1011001 1000 10011001101 B 2

199 When an input signal A=011001 is applied to a NOT gate serially, its output 100111

signal is 100110 10101 10101 B 2

200 How many gates would be required to implement

What is the Gray equivalent of (25 )base 10 . the 110111 1100 111100 111111 A 2

201 following Boolean expression

The two's-complement system after

is to simplification?

be used to add theXY + 1 –113 and 4

2 5 B 2

signed numbers 11110010 and 11110011. Determine, in –14 and –114, –27 and –11 and A

202 decimal, the sign and value of each number and their sum. –13, –27 227 –13, 40 –16, –27 2

203 Solve this

Which binary

of the problem:

following 01110010

equations – 01001000

would accurately= 11010 101010 1110010 111100 B 2

204 describe a four-input OR gate when A = 1, B = 1, C = 0, 1 + 1 + 0 +1 0+ =1 01

+ 0 +1 +0 1=+10 + 10 += 10 + 0 + 0 = 00 B 2

205 CMOS

PhysicalIClogic

packages are available

gates take finite time in to

________

respond to changes DIP configuration

SOIC configuration

DIP and SOIC neither

configurations

DIP norCSOIC configurations 2

206 in their input signal .what name is given to this time hold time setup time propogation rise timetime C

delay 2

207 ten TTL loads per TTL driver is know as____ noise immunity

fan -out power dissipation propogation delay B 2

208 write does

Why sign magnitude of -36use

the TTL family in a8totem-pole

bit numbercircuit

systemon the 10100110 11011100 1011110 none B 2

209 output? It provides It

active

provides

pull-up.

Itactive

provides

pull-down

none

activeofpull-up

the above

and

C active pull-down 2

210 Normal

The two's-complement NPN bipolar

operation of an system transistor

is to be used torequires

add the the positive, negative

positive, positive

negative, positive

negative, negative A 2

211 signedthe

Using numbers 11110010

schematic diagramandof11110011.

a TTL NAND Determine,

gate, in –14 and –13,–113

–27and –114,

–27 and227–13,–1140and –16, –27 A 2

212 determine

Convert the of

each state

theof each transistor

following signed (ON or numbers

binary OFF) when Q1-ON, Q2-OFF,

Q1-ON,Q3-ON,

Q2-ON,

Q1-OFF,Q4-OFF

Q3-OFF,

Q2-OFF,

Q1-OFF,Q4-OFFQ3-ON,

Q2-ON,D Q4-ON

Q3-OFF, Q4-ON 2

213 (two's-complement) to a signed decimal number. –5 +4 +8 +5 –4 –8 –5 +252 +5+248 –252 –248 B 2

214 Why is the fan-out of CMOS gates frequency dependent? Each CMOS When

inputthe

gate

frequency

Thehashigher

a specific

reaches

The

the input

number

propagation

thegates

critical

of Dgates

oftime

the

value,

attached

FETs

andthe

thisto2limits

are

gate predominantly

the

willoutput,

the

only number

be

thecapable

capacitiv

more

of diff

fro

215 what is the difference between 54XX & 74XX Series 54xx is faster

54xx is slower

54XX has 54XX a widerhas power

a narrower

supply

C power

& expanded 2 tempature

supply & cotracted range

tempat

216 What must be done to interface TTL to CMOS? A droppingAs resistor

long asmust

A

the5beCMOS

V used

ZenerAsupply

onpull-up

diode

the CMOS

voltage

must

resistor

beD

12

isplaced

must

5VV,supply

they

be

across

used

can 2the

to reduce

between

be inputs

interfaced;

it to

the

of5 the

TTL

V however

for

TTL

outpu

thegaT

217 What74F-Fast

The is uniqueTTLabout TTL devices such

integrated-circuit as the 74S00?

fabrication technique The S denotes

The gate transistors are

The the

siliconfact

S denotes

(S),that

The and aslow

single

adevices

the gate

gates

version

use is

ofpresent

DSchottky

therefore in2lower

the device, thewhich

transistors

have ICand

rather

values than

isdiodes tothe

a consequenc

of leakageus

prev

218 uses reduced interdevice ________ to achieve reduced noise resistance capacitanceinductance C 2

219 ________ is about twice as fast as P-MOS CMOS DMOS MOD NMOS D 2

A multiplexer is a logic circuit that accepts accepts accepts accepts

one input many many one input

C

and gives inputs inputs and gives

220 several and gives and gives one output 1

Which of the given expressions is in the sum-of-products output

(A + B)(C many

(A)B(CD one

AB(CD) AB + CD

D

221 (SOP) form? + D) ) 1

For a 4-bit parallel adder, if the carry-in is connected to a the same that carry- a one the carry-

logical HIGH, the result is: as if the out will will be out is

carry-in is always be added to ignored.

tied LOW HIGH. the final

since the result. C

least

significan

222 t carry-in 1

223 How many 3-line-to-8-line decoders are required for a 1-of-32 is

1 2 4 8 C 1

224 decoder?

How many select lines are required for selecting eight inputs? 1 2 3 4 C 1

Each "1" entry in a K-map square represents: a HIGH a HIGH a LOW a DON'T

for each output on output CARE

input the truth for all condition

truth table table for possible for all

condition all LOW HIGH possible A

that input input input truth

produces combinati condition table

225 a HIGH ons. s. combinati 1

226 How many outputs are on a BCD decoder? output.

4 16 8 ons.

10 D 1

What is the function of an enable input on a multiplexer chip? to apply to to active to active

Vcc connect the entire one half C

227 ground chip of the 1

A principle regarding IC74138 decoder is that when the active- to a high to an chip

active-

D

228 correct input is present, the related output will switch: HIGH impedanc open LOW 1

e

One multiplexer can take the place of: several combinati several several

SSI logic onal logic Ex-NOR SSI logic

gates circuits gates gates or D

combinati

229 onal logic 1

Most demultiplexers facilitate which type of conversion? decimal- single ac to dc circuits

odd parity

to- input, to even B

230 hexadeci multiple parity 1

The primary use for Gray code is: mal

coded outputs

turning to to convert

representa on/off represent the

tion of a software the angular

shaft's switches correct position

mechanic ASCII of a shaft A

al code to on

position indicate rotating

the machinery

231 angular into 1

Why is a demultiplexer called a data distributor? The input One of position

The hexadeci

One of the

will be the inputs output The

distribute will be will be output

d to one selected distribute will be A

of the for the d to one distribute

232 outputs. output. of the d to one 1

Why is the Gray code more practical to use when coding the All digits Two inputs.

Only one of the

3 digit

position of a rotating shaft?(e.g.4bit) change digits digit change

C

between change changes between

233 counts. between between count 1

If two inputs are active on a priority encoder, which will be the higher counts.

the lower counts.

neither of both of

A

234 coded on the output? value value the the inputs 1

235 How many select lines would be required for an 8-line-to-1-line 2 3 4inputs 8 B 1

236 multiplexer?

The inverter can be produced with how many NAND gates? 1 2 3 4 A 1

237 The inverter can be produced with how many NOR gates? 1 2 3 4 A 1

238 The AND gate can be produced with how many NAND gates? 1 2 3 4 B 1

239 The OR gate can be produced with how many NOR gates? 1 2 3 4 B 1

A 4-variable AND-OR circuit produces a 0 at its Y output. A = 0, B A = 1, B A = 1, B A = 1, B =

D

240 Which combination of inputs is correct? = 0, C = = 1, C = = 1, C = 0, C = 1, 1

241 In a which code, each number is 3 greater than the binary 1, D=

gray 1

code 0,

ex-3D= 0

code 1,

BCDD=1 D =0

binary B 1

representation

A of thatprinciple

basic multiplexer number.can be demonstrated through the single- DPDT code

rotary code

linear

C

242 use of a: pole relay switch switch stepper 1

One application of a digital multiplexer is to facilitate: data serial-to- parity data

generatio parallel checking selector D

243 n conversio 1

When two or more inputs are active simultaneously, the first-in, npriority ripple first-in,

process is called: first-out encoding blanking first-out

processin processin B

g g or

244 priority 1

Which of the following is not a weighted value positional hexadeci binary- binary encoding

octal

B

245 numbering system: mal coded 1

A truth table with output columns numbered 0-15 may be for decimal

4-of-16 dual octal

binary-to- hexadeci

A

246 which type of decoder IC? outputshexadeci mal-to- 1

How can the active condition (HIGH or LOW) or the decoder A bubble A bubble mal

A binary

square A square

output be determined from the logic symbol? indicates indicates

indicates indicates

B

active- active-active- active-

247 HIGH. LOW. HIGH. LOW. 1

If two inputs are active on a priority encoder, which will be the higher the lower

neither of both of

A

248 coded on the output? value value the the inputs 1

249 How many select lines would be required for an 16-line-to-1- 2 3 4inputs 8 C 1

line multiplexer?

A half-adder does not have ________. carry in carry out two all of the

A

250 inputs above 1

A circuit that can convert one of ten numerical keys pressed on priority decoder multiplex demultipl

A

251 a keyboard to BCD is a ________. encoder er exer 1

The AND-OR-INVERT gates are designed to simplify POS logic DeMorga NAND SOP logic

A

252 implementation of ________. n's logic 1

theorem

A Karnaugh map will ________. eliminateallow any produce give an

the need circuit to the overall

for be simplest picture of

tedious implemen sum-of- how the A

Boolean ted with products signals

simplifica

just AND expressio flow

253 tions and OR n through 1

254 When Karnaugh mapping, we must be sure to use the maximum gates

minimum median the logic

Karnaugh B 1

255 ________

The number

final output ofof loops.circuit is generated by ________.

a POS an AND an OR a NOR a NAND A 1

256 The final output of a SOP circuit is generated by ________. an AND an OR a NOR a NAND B 1

257 When grouping cells within a K-map, the cells must be 2's 1, 2, 4, 8, 4's 3's B 1

combined in groupscircuit

_______________ of ________.

does not need memory? etc.

Combinat Sequentia Digital None of

A

258 ional l the above 1

Which of the following are examples of Combinational Adders Comparat Multiple All of the

D

259 circuits? ors xer above 1

If Y=AB+BC is given expression,then A,B,C are called as Minterm Maxterm Literals None of

C

260 the above 1

The expression Y=A'B'+BC+A'C is in _________ form SOP POS Mixed All of the

A

261 above 1

The expression Y=(A'+B')+(B+C)+(A+'C) is in _________ SOP POS Mixed All of the

B

262 form above 1

_________ form means each term used in a switching equation Standard Non- Canonica All of the

C

263 must contain all the available input variables Standard l above 1

The expression Y=(A+B)(A'+B') is in _________ form Standard Non- Canonica All of the

A

264 Standard l above 1

Which of the following is in Non-standard SOP form Y=A+BC Y=A'B+ Both A None of

A

265 +AC AB' &B the above 1

The standard SOP form of Y=AB+AC' Y=ABC+ Y=ABC+ Y=ABC+ None of

B

266 A'B'C'+A ABC'+A A'BC'+A the above 1

Maxterm corresponding to 011 is B'C'

(A'+B+C) B'C'

(A+B'+C' B'C'

(A'+B'+C None of

B

267 ) ) the above 1

268 The minterm A'B'C' is represented as mo Mo M7 m7 A 1

The relationship between the expressions expressed using Additive Complem Dual All of the

B

269 minterms and Maxterms is of entary above 1

270 3 variable K-Map consists of _________ cells 7 8 15 4 B 1

271 In K-map,input values are ordered in ________ code sequence Binary Gray XS-3 BCD B 1

The logical expression in std SOP form can be represented on 0's 1's Don’t None of

B

272 K-map by entering ___ in the cells corresponding to each Care the above 1

273 minterm present in thegrouping

In k-map,_________ equationof 1's is not allowed Horizonta Vertical Diagonal Corner C 1

274 In k-map, grouping of 2 adjacent cells gets rid of ---- variables 1l 2 3 4 A 1

275 In k-map, grouping of 4 adjacent cells gets rid of ---- variables 1 2 4 8 B 1

276 In k-map, grouping of 8 adjacent cells gets rid of ---- variables 1 2 3 4 C 1

___________ consists of 1's which are already considered once Pair Octet Redunda All of the

C

277 in other groups nt above 1

The Maxterm designator of the term A'+B'+C+D' is 4 2 13 None of

C

278 the above 1

279 Logical expression in POS form is most suitable for designing XNOR XOR NAND NOR D 1

280 logic circuits

Logical using in

expression only

SOP form is most suitable for designing XNOR XOR NAND NOR C 1

logicterm

The circuits using

in SOP onlyin a logic function that must be present

form Literal Prime Essential minterm

in the minimum expression is called Implicant Prime C

281 Implicant 1

The result of binary addition 1+1 is Carry Carry Carry Carry 1

C

282 0,Sum 0 0,Sum 1 1,Sum 0 Sum 1 1

Half adder circuit is half of an half of a to add 2 None of

C

283 AND gate NAND bits the above 1

284 The addition of 3 bits is performed by using a _________ adder Full gate

Half together

Both A Parallel A 1

285 Which of the following is not a combinational logic circuit? 4:1 MUX 3:8 &B

DFF Adder C 1

286 IC 74153 is a __________ MUX decoder

DEMUX Encoder Decoder A 1

IC 74138 is a __________ 2:4 3:8 8:1 MUX None of

B

287 decoder decoder the above 1

Demultiplexer has Single Single Multiple Multiple

input input inputs inputs

B

Single multiple Single Multiple

288 output outputs output outputs 1

289 Which digital system translates coded characters into a more encoder display counter decoder D 1

useful form?

290 How many possible outputs would a decoder have with a 6-bit 16 32 64 128 C 1

binary

A input?

combinational circuit is one in which the output depends on input input input present

the combinati combinati combinat output and

on at the on at that ion and the

time time and the previous A

the previous output

previous output

291 input 1

Which of the following circuit can be used as parallel to serial Multiplex combinati

Demultipl Decoder Digital

A

292 converter ? er exer counter 1

In which of the following adder circuits, the carry look ripple Half Full Parallel Carry-

C

293 delay is eliminated ? Adder adder adder look- 1

294 How many inputs are required for a decoder with 16 outputs? 2 4 8 ahead

16 B 1

One can safely state that the output lines for a demultiplexer input data the the Input data

A

295 are under the direct control of the: select internal internal line. 1

296 How many 3-line-to-8-line decoders are required for a 1-of-32 1lines 2AND 4OR gate 8 C 1

297 decoder?

The implementation of simplified sum-of-products expressions AND/OR NAND NOT NOR B 1

may be easily

A decoder canimplemented into actual logic

be used as a demultiplexer bycircuits using all

________. tying all tying all tying all using the

enable data- data- input lines

pins select select for data

LOW lines lines selection D

LOW HIGH and an

enable

298 line for 1

Which statement below best describes a Karnaugh map? A The Variable data input

Karnaugh

Karnaugh Karnaugh complem maps

map can map ents can provide a

be used to eliminate be visual

replace s the need eliminate approach D

Boolean for using d by to

rules. NAND using simplifyin

299 and NOR Karnaug g Boolean 1

A full-adder has a Cin = 0. What are the sum () and the carry ∑=0,Cout gates.

∑=1,C h∑=1,C

maps. expressio

none

300 out out D 1

(Cout) when A = 1 and B = 1? =0 =0 =1

301 The inverter can be produced with how many NAND gates? 1 2 3 4 A 1

Which is the decimal number for the BCD number, 10110110? 182 36 116 Not a

D

302 valid 1

What is the major difference between half-adders and full- Nothing Full Full BCD

Half no

adders? basically; adders adders adders can

full- can have a handle

adders are handle carry only C

made up double- input single-

303 of two digit capabilit digit 1

What distinguishes the look-ahead-carry adder? half-

It is numbers.

It is y.

It is numbers.

It requires

slower easier to faster advance

than the implemen than a knowledg C

ripple- t logically ripple- e of the

304 carry than a carry final 1

The binary adder circuit is designed to add ________ binary adder.

3 full

4 adder adder.

8 answer.

None of

D

305 numbers at the same time these 1

Why is a fast-look-ahead carry circuit used in the 7483 ? to to make it to slow to speed

D

306 decrease smaller down the up the 1

307 _____________ is an input signal to a digital circuit that can the cost Strobe

Logic circuit

Digital circuit

Analog B 1

308 enable

The /disable

4-bit binarythe circuit

adder IC is gate

7483 74151 74153 74138 A 1

309 Quite often,______ code is used to represent decimal numbers Binary Gray Xs-3 BCD D 1

in a calculator

Adders can perform___________________________________ Only Only Both All of the

addition subtractio Addition above C

310 n and 1

_______ can also be used as binary-to-decimal decoder. MUX DEMUX Half subtracti Carry

B

311 adder look- 1

Active low means_______ Performs Does not Performs Does aheadnot

operation perform operation perform

when it is operation when it is when it is A

LOW when it is HIGH not HIGH

312 LOW 1

Active high means_______ Performs Does not Performs Does not

operation perform operation perform

when it is operation when it is when it is C

LOW when it is HIGH not HIGH

313 LOW 1

Strobe is an _________ signal active active indefinite None of

B

314 high low these 1

315 The min. no of selection inputs required for selecting one out 4 5 6 32 B 1

316 of 32 inputs

______ is

complementation is used for performing BCD 1's 2's 9's 10's C 1

subtraction

A std SOP logic expression of 4 variables contains each term 4 8 16 None of

A

317 with __ literals these 1

A std SOP logic expression of 3 variables contains each term 2 3 4 None of

B

318 with __ literals these 1

A std SOP logic expression of 2 variables contains each term 2 3 4 None of

A

319 with __ literals these 1

320 A NOR-NOR realization is a __________ level realization 2 3 4 16 A 1

321 Subtractors are designed using _____ Ics Adder Subtracto 7447 7404 A 1

How is an encoder different from a decoder? The r

The

output of output of

an a decoder A

encoder is is a

322 a binary binary 1

Any SOP expression can be directly implemented using only code for 1- code

an XOR for an AND three 2-

an XNOR

C

323 ________. gate gate OR INV input 1

A 2:1 multiplexer has ______ number of circuit NAND

B

324 select lines. three

combinati one five two 1

A demultiplexer can be used to realize a onal

A

325 _________ circuit

BCD shift-register

counter display system 1

326 Which of the following is a combinational circuit? adder shift-register

4counter

bit ring counter A 1

binary

C

327 The IC 7483 is a __________ multiplexercomparator

dual 4:1 adder demultiplexer 1

328 The IC 74153 is a __________ mux 16:1 MUX4:1 Mux 8:1 MUX A 1

329 The __________ is a 4:1 dual multiplexer IC 74153 IC 74151 IC 7485 IC 74138 A 1

Two 16:1 and one 2:1 multiplexers can be

A

330 connected

A _________to form a _________

is digital circuit which selects one of the n data 32:1 MUX16:1 MUX64:1 MUX8:1 MUX 1

inputs and routes it to the

A

331 output. multiplexerdemultiplexer

decoder counter 1

If multiplexer has x select lines, it has ____

A

332 output(s). one

coded two

non three four 1

informati coded

on into informati

non- on into A

coded coded

333 A decoder converts ___________ form form HIGHs to LOWs to HIGHs 1

334 It is possible to convert a 1:4 DEMUX into a_______ decoder. 3:8 2:4 1:4 1:8 B 1

335 in binary subtractor 0-1=_______. 0with borrow

1with

1 borrow1 with

0 borrow

0 with

1 borrow 0C 1

336 _______addition technique eliminates problem due to interstage carrydelay.Look aheadFull

carry

adder

adder

Half adderBCD adder A 1

337 Truth table is step of ______ method to design combinational circuit. MSI TraditionalSSI LSI B 1

338 In priority encoder priorities are given to_______lines. Select

two output Input All of

three these C 1

inputs inputs and

and two two D

339 A full subtractor circuit requires ________. outputs

one data two inputs three

and three outputs

inputs

outputs

and one output 1

input and

a number

of

selection several

A

inputs, inputs

and they one input and several

have and one several inputs and

340 A demultiplexer has ________. several output outputs one output 1

moving moving

data data

between internally

memory within a

moving and moving microproc

data storage data over essor or C

internally registers long between

within a in a distance memory

microproc micropro transmiss and

341 Multiplexing of digital signals is usually required when: essor. cessor. ion lines.

Actual storage 1

circuit Boolean

Karnaugh trial and algebra

Boolean mapping error and actual

algebra and evaluatio circuit A

and circuit n and trial and

Which of the following statements accurately represents Karnaugh waveform wavefor error

342 the two BEST methods of logic circuit simplification? mapping analysis m evaluation 1

343 How many inputs will a decimal-to-BCD encoder have? 4 8 10 16 C 1

344 A BCD decoder will have how many rows in its truth table? 10

coded 9

non 8 3 A 1

informati coded

on into informati

non- on into B

coded coded HIGHs to LOWs to

345 decoder converts

A 4-variable ___________

logic expression can be realized by using only one form

16:1 form LOWs HIGHs 1

346 __________ MUX NAND gateNOR gate demultiplexer A 1

347 Which of the following is not a combinational circuit? decoder bcd adder counter code converter C 1

348 The number of inputs and outputs in a half adder are ________ 3 and 2 2 and 2 3 and 3 2 and 1 B 1

Which device changes the parallel data to

A

349 serial data? multiplexerdecoder flip-flop demultiplexer

parity 1

generator

multiplex and B

350 The IC 74153 is a __________ comparatorer checker

demultiplexer

3:8 1

351 The IC 74138 is a __________ 2:4 decoderdecoder none of these C

8:1 multiplexer 1

sum bit carry bit difference

output of output of bit output

A

a half a half of a full

352 The difference bit output of a half subtractor is same as: adder

decimal- adder

sum bit output

single substrator.

of a full-adder 1

to- input, odd parity

hexadeci multiple to even B

353 Most demultiplexers facilitate which type of conversion? mal outputs ac to dc parity 1

If multiplexer has x select lines, it has ____

A

354 output(s). one two three four 1

A truth table with output columns numbered 0-15 may be for hexadeci dual octalbinary-to- hexadeci

A

355 which type of decoder IC? mal 1-of- outputs hexadeci mal-to- 1

A half-adder does not have ________. 16

carry in carry out mal

two binary

all of the

A

356 inputs above 1

For a three variable Combinational Circuit ∑m(1,4,7)= ∑M(0,2,3 ∑m(0,2,3 ∏M(0,2, ∏m(0,2,3,

C

357 ,5,6) ,5,6) 3,5,6) 5,6) 1

non

weighted BCD weightte ASCII C

358 Gray code comes under the ________ code code d code code 1

359 binarycode

The Ex-3 number

10000011 is equivantintoBCD

is represented graynumber

is ________

is 0011 0010 0100 0001 B 1

360 The standered SOP expression Y=∑m(0,3,5,8,11) can be

________ 0100 0101 0110 11 B 1

361 realized using a single____MUX and few logic gates. 4:1 8:1 2:1 (a)(b)&(c) B 1

362 the 9's

The complement

gray code 0111of is 0101 is ________

represented in binary form like 0101 0100 0110 1001 B 1

363 ________

If all the cell consist of 1's then the value of that Kmap is 0101 0100 0011 0110 B 1

364 ________

If all the cell consist of 0's then the value of that Kmap is 3 2 1 0 C 1

365 ________

In the SOP equation If there is no any adjacent 1 with any 3 2 1 0 D 1

366 Don’t'cares(X) in thecomplete Kmap then all Don’t'cares(X) 1 0 2 3 B 1

367 thepriority

In 1's complement of 0101 isif two

encoder priorities ________

or more input lines are one 0101 1010 1100 0011 of

none B 1

368 at same time there input line with ______ pripority will be highest lowest arbitatory

(16 X these A 1

369 If n=16 and propagation delay of each Full Addder. is 20 ns then total (16/20)ns

time required

(16+20)ns 20)ns None

for performing the addition is_________

C 1

370 principle of subtractor

The ___________can using

act like IC7483controlled

digitally is basedsingal

on ______

pole 1’s complement

2’s complement10’s complement

9’s complementB 1

371 multiple way switch DEMUX Independ

Dependen MUX Encoder Decoder B 1

372 Look ahead carry adder is ______ of numbers of bits d ant None B 1

Propogati

Time on Both A

C

373 Ripple carry propogation results in_______in addition process dealy Delaey &B none 1

374 How many full adder are required to construct an m-bit parallel adder m/2 m-1 m m+1 B 1

375 Identify the Boolean expression that is in standard POS form (A + B)(C + D)C 1

376 The sum of the two BCD numbers, 0011 + 0011, is ________. 0110 1011 1101 1100 A 1

377 One that is not outcome of magnitude comparator is a>b

0001 a-b

0001 a<b a=b B 1

0001 0010 0111

D

378 What is binary value of BCD number: 0001 0001 1000 (118)? 0110 0011 0111 0111 0110 1

379 In order to implement a 4 variable switching function, a MUX 4 inputs 8 inputs 16 inputs 2 inputs C 2

380 must have

In order to implement a 3 variable switching function, a MUX 4 inputs 8 inputs 16 inputs 2 inputs B 2

must

A have

combinational logic circuit which sends data coming from a Decoder Encoder Multiple Demultipl

D

381 single source to two or more separate destinations is xer exer 2

Looping on a K-map always results in the elimination of: variables variables variables variables

within the that within within the

loop that remain the loop loop that

appear unchange that appear

only in d within appear in only in C

their the loop. both their

complem complem uncomple

ented ented and mented

382 form. uncompl form. 2

emented3

383 How many 2-input NOR gates does it take to produce a 2-input 1 2 4 D 2

384 NAND

How gate?

many 2-input NAND gates does it take to produce a 2- 1 2 3 4 D 2

385 input NOR

What is the gate?

status of the inputs S0, S1, and S2 of the 74153 eight-line multiplexer

S0 = 0,using

S1 =

S0cascading

1,=S2

0, =

S10S0

=in0,=

order

S2

1, S1

=for

1S0

= the

1,= S2

1,output

S1

= 0= Y

0, to

S2be

D 2

= 1a copy of input I5?

386 What is the status of the inputs S0, S1, and S2 of the 74153 eight-line multiplexer

S0 = 0,using

S1 =

S0cascading

1,=S2

0, =

S10S0

=in0,=

order

S2

1, S1

=for

1S0

= the

1,= S2

1,output

S1

= 0= Y

0, to

S2be

A 2

= 1a copy of input I2?

387 What is the status of the inputs S0, S1, and S2 of the 74153 eight-line multiplexer

S0 = 0,using

S1 =

S0cascading

1,=S2

0, =

S10S0

=in0,=

order

S2

1, S1

=for

1S0

= the

1,= S2

1,output

S1

= 0= Y

0, to

S2be

B 2

= 1a copy of input I4?

388 A binary code that progresses such that only one bit changes between two successive

nine's-complement

codes

8421is:code

code

excess-3 code Gray code D 2

389 The largest truth table that can be implemented directly with an 8-line-to-1-line

3 rows

MUX has4 rows

________.8 rows 16 rows C 2

390 The addition of two signed numbers in the 2's complement system can causebe overflow.

positivebe

Fornegativehave

overflow to the

occur

same

have

bothsign

opposite

numberssigns

must

C ________. 2

391 The ________ circuit produces a HIGH output whenever the two inputs are exclusive-AND

equal. exclusive-NAND

exclusive-NOR exclusive-OR C 2

392 A 4-bit adder has the following inputs: C0 = 0, A1 = 0, A2 = 1, A3 = 0, A4 = 1, B1 1100

= 0, B210101

= 1, B3 = 11000

1, B4 = 1. The 11 output will 2

C be ________.(A4 is MSB)

393 For a three variable Combinational Circuit ∑m(1,4,7)= ∑M(0,2,3,5,6)

∑m(0,2,3,5,6)∏M(0,2,3,5,6) ∏m(0,2,3,5,6) C 2

394 K-Map is _____ method of simplifying ______ equation Graphical,Boolean

Analytical,Boolean

Tabular,Arithmetic

All of the aboveA 2

395 By pairing two adjacent 1's on K map,we can eliminate ______variable(s) one two three None of the above A 2

396 A switching function f(A,B,C,D)=A'B'CD+A'BC'D+A'BCD+AB'C'D+AB'CD ∑(1,3,5,7,9)

can also ∑

be(3,5,7,9,11)

∑(3,5,9,11,13)

written as ∑(5,7,9,11,13) B 2

397 Minimization of logical expressions while designing digital systems helps inCost

reducing Space requirements

Power requirements

All of the aboveD 2

398 Half adder circuit contains_________ XOR gate(s) 2 1 4 3 B 2

399 Which of the following combinations cannot be combined into K-map groups? Corners in the

Corners

sameinrowDiagonal

the same column

corners

Overlapping combinations

C 2

400 Looping on a K-map always results in the elimination of: variables within

variables

the loop

that

variables

remain

that appear

within

variables

unchanged

only

the in

within

loop

within

their

that

Cthe

complemented

the

appear

loop

loop.

that 2 form

in both

appear

complemented

only in their and

uncomun

401 Implementation of the following expression ABC+AB+AC' would require three AND three gates,AND

one three

OR

gates,

gate

AND

onethree

NOT

gates,AND

gate,

one gates,

NOT

oneBOR gate,

three

gate

three OR2 gates

OR gates

402 What logic function is the sum output of a half-adder? AND XOR XNOR NAND B 2

An adder circuit for two n-bit binary numbers consists of ____ full adder circuits

n n+1 n-1 n

403 2 A 2

404 A 4-variable logic expression can be realized using single ____ MUX Eight:one Sixteen:oneFour:one None of these B 2

405 How many 2:1 multiplexers are required to implement 4:1 multiplexers? 3 4 5 6 A 2

406 How many 4:1 multiplexers are required to implement 16:1 multiplexers? 5 4 8 2 A 2

407 How many 2:1 multiplexers are required to implement 8:1 multiplexers? 2 7 8 16 B 2

408 AND-OR realization is equivalent to __________ realization NOR-NORNAND-NAND OR-AND All of the aboveB 2

409 Self Complementing code means___________ 1's complement

1's complement

of the 1's

coded

complement

ofnumber

the1's

coded

complement

yield

ofnumber

the9'scoded

complement

yield

Aof number

the2's

coded 2 10's

complement

of

yield

number

the number

complement

yield

of the

itself

7's

number

complem

of itse

the

410 Gray code for decimal 5 is ____________ 101 00010000

00010111 111 1011 1111 B 2

411 Solve this BCD problem: 0100 + 0110 = BCD BCD 00001011BCD 00010011BCD B 2

412 The number of inputs and outputs in a full adder are ________ 3 and 2 2 and 2 3 and 3 2 and 1 A 2

Which of these expressions are correct for

half adder:

1.SUM=A.B+ #A.B

A

2.SUM=A. #B+ #A.B

3.CARRY =A.B

413 4.CARRY=A+B 2 and 3 1 and 2 3 and 4 1 and 4 2

sum bit carry bit difference

output of output of bit output

A

a half a half of a full

414 The difference bit output of a half subtractor is same as: adder adder

sum bit output substrator.

of a full-adder 2

When two 16-input multiplexers drive 2-input MUX,what is 32-input

A

415 the result?the decimal numbers 275 and 965 to binary-coded

Convert MUX

1101 2-input MUX

1110 4-input MUX

0001 16-input MUX 2

decimal (BCD) and add. Select the BCD code groups that 1110 1010 0010 0010 0011

C

416 reflect

How the final

many 4-bit answer.

parallel adders would be required to add two 1010 1110 0100 0100 0000 2

417 binary numbers each representing decimal numbers up through 1 2 3 4 C 2

418 Number of data input in MUX is ______and in Demux is_______. n,1 1,n

subtract m,n

Subtract n,m

subtract A 2

1' that 9 from that

complem number that number D

419 the 9's complement of any number means ________ ent plus 1 from 9 number from 9 2

Multiple Demultipl

B

420 A device

The whichBoolean

following convertsfunction

BCD toisSeven

to be Segment is called

implemented using a Encoder Decoder xer exer 2

Decoder: m (2, 4, 5, 6, 7). The minimum configuration of the 2 – to – 4 3 – to – 8 4 – to – 5 – to –

B

421 decoder should be line.

0100 line. 16 line 32 line.

1000 2

422 The excess 3 code of decimal number 26 is 1001 1011001 1001 1001101 B 2

423 How many select lines will a 16 to 1 multiplexer will have 4 3 5 1 A 2

424 The excess-3 code of decimal 7 is represented by 1100 1001 1011 1010 D 2

425 The BCD

For BCD subtractor

addition ofto1001+0101

get proper is

answer the number of IC7483 10100 10101 10110 10011 A 2

426 required are 2 3 4 5 C 2

427 For 2 digit BCD adder the number of IC7483 required are 2 3 Ex-3, 4 5 C 2

To represent Kmap ________code is used because it has a Gray,unit BCD,wei non Binary,

A

428 property

In ________

look ahead carry generator gate levels are reduced from distance ghted weighted weighted 2

429 ________to ________ 6 to 2

0100 8 to 2 4 to 2

1000 10 to 2 B 2

430 The excess 3 code of decimal number 96 is 1001 11001001 1001 1001101 B 2

431 How4 many

For select

variable Kmaplines

thewill a 32 to

number of1cell

multiplexer

availablewill

are have 4 5 6 3 B 2

432 ________ 16 32 64 8 A 2

433 for BCD to Ex-3 conversion, in BCD number add ________ 3 4 2 1 A 2

The 2 input ________gate is used to implement ODD exclusive- exclusive- exclusive- exclusive-

D

434 function AND NAND NOR OR 2

The 2 input ________gate is used to implement EVEN exclusive- exclusive- exclusive- exclusive-

C

435 function

An encoder that responds to the the highest input is called as AND NAND NOR a & OR

Both 2

436 priority encoder TRUE FALSE b None A 2

437 ______ complementation is used for performing BCD 1's 2's 9's 7's C 2

subtraction active active high

B

438 Bubble at the output of a decoder indicates ________output high

implemen low tristate impedanc

implement 2

t implemen impleme more e then

onfunctio t one nt one one D

439 The advantage of decoder is ________ n

multiplex function function demultipl

function 2

440 we can implement only one function by using________ er decoder encoder exer A 2

carry carry

propagate propagate carry in,

A

In the look ahead carry genrator Pi indicate ________and Gi , carry , carry carry carry in,

441 indicates________

for BCD to Ex-3 code convertor we have ________valid generate out generate carry out 2

442 inputs in truth table for remaining ________combination we 10,6,0

0001 10,6,1

0001 10,6,X

1000 10,6,+ C 2

443 BCDself

The addition of 1001+1001

complementary =________ and unit distance

of ________code 1000

BCD, 0010

Ex- 0001

Ex- 0001 0011

Ex-3, A 2

444 codecomparison

The property of of

________code

two numbersare used

is an for different

operation that determines Gray

comparat 3,Gray 3,Binary BCD

multiplex B 2

445 if One number is greater than, less than, or equal to the other or decoder encoder er A 2

Write the expression for Boolean function F (A, B, C) = ∑m ∑M(0,2,3 ΠM(0,2,3 ΠM(1,4, ∑m

B

446 (1,4,5,6,7) in standard POS form. ) ) 5,6,7) (1,4,5,6,7) 2

th th

447 The full adder adds the K bits of two number to the Difference Sum

of theofprevious

Carrybits

all previous frombit

Sum(k-1)

of bit C

previous bit 2

448 Two 4-bit binary numbers (1011 and 1111) are applied to a 4-bit ∑4∑3parallel

∑2∑1=0111,carry=0

∑4∑3adder.

∑2∑1=1111,carry=1

∑4 ∑ 3∑2∑1=1011,carry=1

The ∑4∑3input

carry ∑2∑1=1100,carry=1

is C1. What are 2the values for the s

449 Which of these expression are correct for half subtractor :- D= A-B D= AB+A’B D=A’B+AB’

,Borrow =A’B’

,Borrow=AB’ D=AB+A’B’

D=A’B+AB’ ,Borrow=A’B ,Borrow=AB’2

C

450 Determine the values of A, B, C, and D that make the sum term equal to zero. A = 1, B = A0, =C 1,

=B 0, =DA0,

= =C

0 0,= B

1, =DA1,==C

01,=B0,=D0,=C0B= 1, D = 1 2

451 Occasionally, a particular logic expression will be of no consequence in the don't

operation

care,of

1s,

spurious,

a 0s,

circuit,

simplify

ANDs,

duplicate,

such as ORs,

a BCD-to-decimal

1s,

spurious,

eliminate

0s, verify

1s, 0s,Aconverter. 2 result in ________ter

simplify These

A<B is 0, A<B is 0, A<B is 1,

What are the outputs of a 7485 four-bit magnitude comparator A=B is 1, A=B is 1, A=B is 0, C

452 when the inputs are A = 0001 and B=0100 A>B is 1 A>B is 0 A>B is 0 A<B is 0 2

negative-

453 7474 requires

IC 7476 contains minimum------V

two independentand---------triggered

maximum -----V D FF.

power edge positive-level negative-level positive-edge A 2

454 supply 4.5, 5 4.75, 5.25 4, 5 5.5, 5.5 B 2

clear input of IC 7473 will reset the outputs redgardless of the high logic

455 levels of the other outputs at----. level low logic levelboth A andNone B of these B 2

negative-

edge

translatio

456 In IC and

clear 7476preset

master JK FF

inputs activited

of IC when----.

7474 are use for------ and ------ n of clock clock is lowclock is high postive transaonDof clock 2

457 purpose. set, reset high, low reset, set low, high C 2

458 To implement 2-bit counter, ------ 7474

preset is 7473 7472 7476 D 2

active

high and

clear is

459 output Q of IC 7476 goes to high when --- active preset is active

Both lowA and and

None

Bclearof is

these

activeB high 2

The 74LS74,74LS76 are characterised for operation from------

460 to-----. 0° to and

high 70° 0°to 60° (-55°) to 70°None of these A 2

461 preset and clear of IC 7476 are active…….. low low high None of these B 2

asynchron

462 Preset

For IC and

7474clear of IC 7476 are and

,VOH(min)=2.4V --------active----inputs

VIH(min)=2V then find out os, high synchronous, asynchronous,

low low,low

high C 2

463 Noise

In margin

IC 7473, (VNH) .

VOL(max)=0.4V and VIL(max)=0.8V then 4.4V 4.8V 0.4V 0.2V C 2

464 calculate Noise Margin(VNL). 0.4V 1.2V 0.8V 0.32V A 2

Which of the following is correct in case of JK flip-flop when Q='0', Q='1', Q='1', Q='0',

465 B 2

it's active low inputs preset and clear are connected to ground Q#='1'

preset and Q#='1' Q#='0' Q#='0'

clear

while while

operation both B

presetting clearing

For a flip-flop with provisions of preset and clear--- are and C are D

clear is preset is

performe true

disabled disabled

d

466 2

In positive level triggering method , flip-flop is triggered when-- simultane

Preset is clock is clock is preset is

467 C 2

- synchronous digital system ,the exact instance at which one

In high

clock low

preset high

clear lowand

set

468 A 2

or more outputs can change the states is determined by the signal signal

synchron Asynchro signal reset

The flip-flop which opeartes in synchronism with external either of none of

ous flip- nous flip- A

469 clock puses are known as the above the above 2

Gated SR flip-flops are called asynchronous because the output flop flop

470 TRUE FALSE B 2

responds

The Q outputimmediately to input

of a flip-flop changes high when the device is

is normally

471 TRUE FALSE B 2

in the 'clear' or 'reset' state

If 'clear' is active high input of the SR flip-flop the 'clear=0' None of

0 1 Z D

472 results in Output Q=? the above 2

If 'preset' is active high input of the JK flip-flop then 'preset=1' None of

0 1 Z B

473 results in output Q=? the above 2

Which of the following is correct in case of JK flip-flop when Q='0', Q='1', Q='1', Q='0',

474 B 2

it'snegative

In active high inputs

level presetmethod

triggering and clear are connected

, flip-flop to Vcc

is triggered when- Q#='1' is clock

Preset Q#='1'is clock

Q#='0'is preset

Q#='0'is

475 B 2

-- high low high

START, low

The asynchronous inputs are normally labelled --- and --- and PRE,CLR ON,OFF, SET,RES

STOP A

476 are normally active ---- inputs ,LOW HIGH ET,HIGH 2

The Q output of a flip-flop is normally high when the device is ,LOW

477 TRUE FALSE A 2

in theQ'Preset'

The output state

of a flip-flop is normally low when the device is

478 In a negative edge triggered J -K flip-flop, in order to have the TRUE

10, 00 FALSE B 2

in the 'Preset' state

479 output Q state

Consider 0, 0 and 1statements

the following in the next: three successive

1. Race clock

around condition and 10 00, 11 and 01,

10 00 and 01,

11 10 and 11 C 2

occurs in a J-K flip-flop when both the

inputs are one. 2. A flip-flop is used to store one bit of

480 information 3. A transparent latch consists of a D type flip- 1, 2 and 3 1, 3 and 4 1, 2 and 4 2, 3 and 4 A 2

Two J-K flip-flops with their J-K inputs tied HIGH are

481 cascaded to be used as counters. After four input clock pulses, 0 1 10 11 A 2

482 To implement mod 249 counter, how many ,IC 7490 is required 249 3 4 5 B 2

If 'Prest' & 'clear' is active low input of the SR flip-flop and PRE='0' , PRE='0' , PRE='1' , PRE='1' ,

C

483 S=R=X then when Q=0? CLR='0' CLR='1' CLR='0' CLR='1' 2

If 'Prest' & 'clear' is active low input of the SR flip-flop and PRE='0' , PRE='0' , PRE='1' , PRE='1' ,

B

484 S=R=X

The then

initial when

state Q=1?

of MOD-16 down counter is 0110.After 37 CLR='0' CLR='1' CLR='0' CLR='1' 2

485 clock pulses,the

Determine state of

the output the counter

frequency for awill be

frequency division circuit 1011

10.24 110 101 1 D 2

486 that contains 12 flip-flops with an input clock frequency of kHz 5 kHz 30.24 kHz15 kHz B 2

edge-

The circuit that is primarily responsible for certain flip-flops to detection

487 be

Twodesignated as edge-triggered

J-K flip-flops with their J-Kis inputs

the: tied HIGH are circuit. NOR latch.NAND latch. pulse-steering circuit.

A 2

488 cascaded

Four J-K to be used are

flip-flops as counters.

cascadedAfter four input

with their clocktied

J-K inputs pulses, 0 11 1 10 A 2

489 HIGH.

In case If

ofthe

SRinput frequency

flip flop (fin)input

following to thecondition

first flip-flop is 32

is prohibited 1 kHz

S = 0, R = 2 kHz 4 kHz 16 kHz B 2

490 (not

In SRallowed)

flip flop the output condition Q = 1, Q# = 0 results with 1S = 0, R = S = 1, R = 1S = 0, R = S0 = 1, R = 0 B 2

491 the following

Race input condition

around condition in JK flip flop results with following J1 = 0, K = S = 1, R = 1S = 1, R = None

0 of these C 2

492 input many

How combination

distinct states are there in the operation of mod n 1 J = 1, K = 1J = 0, K = J0 = 1, K = 0 B 2

493 counter n+1 n n-1 n+2 B 2

494 What is maximum count of mod n counter ? n+1 n n-1 n+2 C 2

495 IC 7490 is mod __ counter. 74

Both 90 10 9 C 2

active

496 The two set inputs of IC 7490 are low Both activeOne

highactiveNone

low &ofother

theseactive

B high 2

Only up

497 An up/down counter can count in direction Both up & Only

downdown

directions

First

direction

up & then Bdown always 2

498 Number of 7490 ICs required to build mod 1000 counter are 100 2 3 10 C 2

499 Number of flip flops in IC 7490 are 4 10 2 5 A 2

Bounce

eliminatio

500 Which one of the following is an application of a S R flip flop n switch Adder MuliplexerCode converterA 2

Bounce

eliminatio

501 Which

In 4 bit one of the

ripple following

counter is not

each flip anhas

flop application of adelay

propagation flip flop

of n switch Adder Register Counter B 2

502 50 nS.

The The timenumber

minimum requiredof to

flipchange the output

flops required to from 1111divide

construct to 50 nS 150 nS 100 nS 200 nS D 2

503 by 13 counter is 4 13 9 8 A 2

504 .The terminal

When count ofare

two counters a mod-11 up the

cascaded, counter is MOD number is

overall 1010 1011 1001 1100 A 2

505 equal to the ________ of their individual MOD numbers. Product

clearing Sum Log Reciprocal A 2

one flip-

flop and

presetting

506 To operate correctly, starting a ring counter requires: all the

a ring clearing allpresetting

the flip-flops

one

presetting

flip-flop

all and clearing all the2 others

theC flip-flops

counter

has an

inverted

A comparison between ring and johnson counters indicates feedback

507 that: many flip-flop are needed to divide the input frequency

How path a ring counter

a johnson

has fewer

counter

a johnson

flip-flops

hascounter

anbut

inverted

Crequires

has more

feedback

more 2decoding

flip-flops

path butcircuitry

less decoding

508 by 64

For ? 1 tranisition at the output of JK flip flop, What must be

0 to 5 6 2 8 B 2

509 applied

For 1 toon its J & K input

0 tranisition at the output of JK flip flop, What must be 0, 1 1, 0 1, X X, 0 C 2

510 applied

For 1 toon its J & K input

1 tranisition at the output of JK flip flop, What must be 0, 1 1, 0 0, X X, 1 D 2

511 applied

For 0 toon its J & K input

0 tranisition at the output of JK flip flop, What must be 1, X X, 1 0, X X, 0 D 2

512 applied

For 0 toon its J & K input

1 tranisition at the output of SR flip flop, What must 0, 1 1, 0 0, X X, 0 C 2

513 be applied

For on its S & at

1 to 0 tranisition R the

input

output of SR flip flop, What must 0, 1 1, 0 0, X X, 0 B 2

514 be applied on its S & R input

For 0 to 0 tranisition at the output of SR flip flop, What must 0, 1 1, 0 0, X X, 0 A 2

515 be applied

For on itsS & R

1 to 1 tranisition at input

the output of SR flip flop, What must 0, 1 1, 0 0, X X, 0 C 2

516 be applied

For on its S & at

0 to 1 tranisition R the

input

output of D flip flop, What must be 0, 1 1, 0 0, X X, 0 of

none D 2

517 applied

For1 to 0ontranisition

its D inputat the output of D flip flop, What must be 0 1 X these of

none B 2

518 applied

For 0 toon its D inputat the output of D flip flop, What must be

0 tranisition 0 1 X these of

none A 2

519 applied

For 1 toon its D inputat the output of D flip flop, What must be

1 tranisition 0 1 X these of

none A 2

520 applied

For 0 toon its D inputat the output of T flip flop, What must be

1 tranisition 0 1 X these of

none B 2

521 applied

For 1 toon its T inputat the output of T flip flop, What must be

0 tranisition 0 1 X these of

none B 2

522 applied

For 0 toon its T inputat the output of T flip flop, What must be

0 tranisition 0 1 X these of

none B 2

523 applied

For 1 toon its T inputat the output of T flip flop, What must be

1 tranisition 0 1 X these of

none A 2

524 applied on its T input 0clk period 1 X these A 2

is <=

Propagati

on delay

For a level triggered JK flip flop, race around condition can be of a JK none of

525 avoided, if flip flop clk period isclk= period these

Propagation

is > Propagation

delay of aAJK

delay a JK 2flip flop

flipofflop

none of

526 In IC 7490 What is output when set inputs are active 0000 1111 1001 these C 2

527 Hw

In SR many

flip flip

flopflops are present

the output in ICQ74191

condition = 1, Q# = 0 results with 1S = 0, R = 2 3 4 D 2

528 the following input condition 1 S = 1, R = 1S = 1, R = None

0 of these C 2

529 IC 7490

The is mod

counter ? counter

in which the decimal equivalent of output 74

Up 90 10 9 C 2

530 increases is known as counter Down counter SynchronousAsynchronous

Counter Counter

A 2

531 Number of flip flops in IC 7490 are 4 10 2 5 A 2

532 Number of flip flops required to construct mod 8 counter are 4

1111 to 8 2 3 D 2

533 The output of mod 16 down counter varies as 0000 0000 to 11111111 to 1010

1010 to 1111 A 2

534 Number of 7490 ICs required to build mod 100 counter are 100 2 3 10 B 2

535 Number

In 3 bit ripple of flipcounter

flops ineach

IC 7476 are has propagation delay of

flip flop 2 7 4 6 A 2

536 50 4nS.

In bitThe time required

synchronous to change

counter theflop

each flip output

hasfrom 111 to 000

propagation 50 nS 150 nS 100 nS 200 nS B 2

537 .delay of 20 nS. The

The maximum maximum

possible number possible time

of states in required to change

a asynchronous 40 nS 10 nS 20 nS 80 nS C 2

538 counter

The consisting

minimum numberof 4 of