Professional Documents

Culture Documents

DELD Unit I & Unit II MCQ

Uploaded by

Aryan PintoOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

DELD Unit I & Unit II MCQ

Uploaded by

Aryan PintoCopyright:

Available Formats

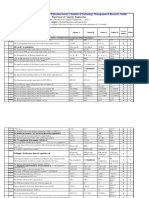

Sr No

Question OptionA OptionB OptionC OptionD Answer

accepts many inputs

accepts one input and gives several and gives many accepts many inputs and accepts one input and gives one

1 A multiplexer is a logic circuit that output output gives one output output C

In order to implement a n variable switching function,

2 a MUX must have 2n inputs 2n+1 inputs 2n-1 inputs 2n-1 inputs A

A combinational logic circuit which sends data coming

from a single source to two or more separate

3 destinations is called Decoder Encoder Multiplexer Demultiplexer D

4 EPROM contents can be erased by exposing it to Ultraviolet rays Infrared rays Burst of microwaves Intense heat radiations A

The output of a logic gate is 1 when all its inputs are at

5 logic 0. the gate is either A NAND or an XOR An OR or an XNOR An AND or XOR A NOR or an XNOR D

A three input NOR gate gives logic high output only

6 when One input is high One input is low Two input are low All input are high D

Which of the following logic families is well suited for

7 high-speed operations ? TTL ECL MOS CMOS B

8 The absorption law in Boolean algebra says that X+X=X X.X=X x+x.y=x None of the above C

The digital logic family which has minimum power

9 dissipation is TTL RTL DTL CMOS D

10 Negative numbers cannot be represented in Signed magnitude form 1’s complement form 2’s complement form None of the above D

11 8-bit 1’s complement form of –77.25 is 1001101.01 1001101.001 10110010.1011 10110010.1101 C

12 In computers, subtraction is generally carried out by 9’s complement 10’s complement 1’s complement 2’s complement D

13 X – = Y + 1 means X=X–Y+1 X = –X – Y – 1 X = –X + Y + 1 X= X – Y – 1 A

Shifting a register content to left by one bit position is

14 equivalent to Division by two Addition by two Multiplication by two Subtraction by two A

The 2s compliment form (Use 6 bit word) of the

15 number 1010 is 111100 110110 110111 1011 B

The answer of the operation (10111) 2*(1110)2 in hex

16 equivalence is 150 241 142 101011110 C

17 The gray code equivalent of (1011)2 is 1101 1010 1110 1111 D

18 12-bit 2’s complement of –73.75 is 1001001.11 11001001.11 10110110.01 10110110.11 C

The negative numbers in the binary system can be

19 represented by Sign magnitude 1s complement 2s complement All of the above C

20 The 2’s complement of the number 1101101 is 101110 111110 110010 10011 D

The number of 1’s present in the binary representation

21 of 10 × 256 + 5 × 16 + 5 is 5 6 7 8B

22 The hexadecimal number equivalent to (1762.46) 8 is 3F2.89 3F2.98 2F3.89 2F3.98 B

How many 1’s are present in the binary representation

23 of 3 × 512 + 7 × 64 + 5 × 8 + 3 8 9 10 11 B

24 What is decimal equivalent of BCD 11011.1100 ? 22 22.2 20.2 21.2 B

What is the binary equivalent of the decimal number

25 368 101110000 110110000 111010000 111100000 A

26 The ASCII code for letter A is 1100011 1111111 1000001 10011 C

27 Floating point representation is used to store Boolean values Whole numbers Real no with fraction Integers C

28 The Gray code for decimal number 6 is equivalent to 1100 1001 101 110 C

29 The decimal equivalent of hex number 1A53 is 6793 6739 6973 6379 B

(001011111010 0000

30 (2FAOC)16 is equivalent to 195 084)10 1100)2 Both (A) and (B) None of these B

31 The octal equivalent of hexadecimal (A.B) 16 is 47.21 12.74 12.71 17.21 B

32 Logic X-OR operation of (4ACO)H & (B53F)H results AACB 0000 FFFF ABCD C

Page Shift Keying (PSK) Method is used to modulate

digital signal at 9600 bps using 16 level. (Find the line

33 signals and speed (i.e. modulation rate). ) 2400 bauds 1200 bauds 4800 bauds 9600 bauds A

The simplified form of the Boolean expression

34 (X+Y+XY)(X+Z) is X + Y + ZX + Y XY – YZ X + YZ XZ + Y C

What is the transitive voltage for the voltage input of a

35 CMOS operating from 10V supply ? 1V 5V 10V 20V B

36 The highest noise margin is offered by BICMOS TTL ECL CMOS B

The branch logic that provides making capabilities in

37 the control unit is known as Controlled transfer Conditional transfer Unconditional transfer None of the above A

The digital logic family which has the lowest

38 propagation delay time is ECL TTL CMOS PMOS A

39 In a positive logic system, logic state 1 corresponds to Positive voltage Higher voltage level Zero voltage level Lower voltage level B

40 AB+(A+B)’ is equivalent to A*B A+B (A+B)A (A+B)B A

41 The NAND gate output will be low if the two inputs are 00 01 10 11 D

42 The Boolean expression x’y’z+yz+xz is equivalent to x y z x+y+z C

Which one of the following expressions does NOT

43 represent exclusive NOR of x and y? xy + x ' y ' x ex-or y ' x 'ex-or y x 'ex-or y ' D

ease of avoiding

Advantage of synchronous sequential circuits over problems due to lower hardware

44 asynchronous ones is faster operation hazard requirement better noise immunity A

A reduced state table has 18 rows. The minimum

number of flip flops needed to implement the

45 sequential machine is 18 9 5 4C

Which of the following is the fastest logic TTL ECL CMOS LSI B 1 (High speeds are possible in ECL because the transistors are

46 used in difference amplifier configuration, in which they are

never driven into saturation and thereby the storage time is

As in CMOS one device is ON & one is Always OFF so

eliminated.

47 CMOS circuits consume power Equal to TTL Less than TTL Twice of TTL Thrice of TTL B 1 power consumption is low

The commercially available 8-input multiplexer integrated

48 circuit in the TTL family is 7495 74153 74154 74151 B 1 MUX integrated circuit in TTL is 74153.

CMOS circuits are extensively used for ON-chip computers

49 mainly because of their extremely low power dissipation. high noise immunity. large packing density. low cost. C 1 Because CMOS circuits have large packing density.

The time difference between the instant of application of

input & the instant at which output responds to it, is called

50 as_________ propagation delay delay time rise time fall time A 1

Reduced power dissipation may lead to ___ in propagation

51 delay Increase Decrease constant None of these A 1

52 Noise immunity of TTL is _____ CMOS More than Less than Equal to Extremely less than B 1

53 TTL tristate inverter consists of ______ 2 transistors & 2 diodes 4 transistors & 2 diodes 4 transistors & 4 diodes 2 transistor & 4 diodes B 1

54 ___ digital Ics have highest packing density PMOS NMOS CMOS TTL B 1

only p channel Mos

55 CMOS consist of______ only n channel Mos devices devices MOS devices p channel & n channel Mos devices D 1

56 Recommended Fan out for TTL gate is_____ 10 4 20 50 A 1

57 ___ is operated in ohamic or cut-off regions CMOS ECL TTL PMOS A 1

58 _____ is operated in saturation or cut-off regions. CMOS ECL TTL PMOS C 1

Dual edge triggered D Dual edge triggered D flip-

59 The MSI chip 7474 is Dual edge triggered JK flip-flop (TTL). flip-flop (CMOS). flop (TTL). Dual edge triggered JK flip-flop (CMOS). C 2 MSI chip 7474 dual edge triggered D Flip-Flop

60 The logic 0 level of a CMOS logic device is approximately 1.2 volts 0.4 volts 5 volts 0 volts D 2 CMOS logic low level is 0 volts approx

In the bipolar saturated ligic families,the bipolar

_________ transistors are used as a switch & operated in transistors are used as the main device. It is used as a

61 saturation region unipolar bipolar ECL Both A & B D 2 switch & operated in the saturation or cutoff regions.

The product of power dissipation and propagation time is

62 always___________ High Low One Constant D 2

Practically,the value of figure of merit should be as low

as possible. Figure of merit is always a compromise

beteen speed & power dissipation. That means if we try

Partially the value of figure of merit should be as_________ to reduce the propagation delay then the power

63 as possible Low High Medium Extremely low A 2 dissipation will increase & vice-versa.

______ is always a compromise between speed & power

64 dissipation Figure of merit Fan-In Fan-Out Noise Margin A 2

The speed power product is used as a common means

_____is used as a common means for measuring & for measuring & comparing the overall performance of

65 comparing the overall performance of different IC family. Speed power product Propagation dealy Noise margin Figure of merit A 2 different IC family.

The TTL Ics known as _________ TTL are not available now TTL Ics were first developed in 1965 & they were known

66 a days. Fast Standard Basic None of these B 2 as standard TTL.

Totem pole output have a very low output impedance

67 typically______ 10ohm 20ohm 40ohm 50ohm A 2

open or floating input acts extly same as if a logical 1 is

68 For a TTL IC any floating input is equivalent to a______ Logic 0 Logic 1 undefiened logic value Defined logic value B 2 applied to that input.

69 Typically the Fan out of a CMOS device is ____ below 1 MHz 10 25 50 100 C 2

70 Input capacitance of each CMOS device gate is ______ 50pF 50nF 50µF 50mF A 2

decreases with

increases with increased reverse-bise increased forword-bise increases with increased

71 The storage time of a trnasistor___ voltage of BC junction of BC junction forward bias of BC junction None of these C 2

72 for fastest switching operation it is preferred to use______ normal p-n junction diodes schottky diodes vacuum diodes rectifier diodes B 2

The average supply current,Icc is determined based on____

73 duty cycle 100% 75% 50% 25% C 2

______ diodes are used in all TTL gates to suppress the

74 ringing caused from the fast voltage transitions Zener Free wheeling Clamping None of these C 2

which one of the following logic families can be operated

75 using a supply voltage from 3V to 15V? 74TTL 74LS 74AS CMOS D 2

can drive maximum of 10

76 If a logic circuit has a fan-out of 10 then the circuit _____ has 10 inputs has 10 outputs inputs can drive maximum of 10 outputs C 3

the temprature range for the series in 7400 is from 0 to

77 The temprature range for devices in 74XX series is from 0 to 70° 55 to 125° 0 to 125° 0 to 55° A 3 70°C, over a supply voltage range of 4.75 to 5.25V

78 Voltage range of CMOS Ics are from_____ 3 to 5V 4 to 6V 2 to 6V 4 to 8V C 3

79 Noise margin is calculated as VOH(min)-VIH(min) VOH(max)- VIH(max) VIL(max)- VOL(max) VOH(min)-VIH(max) A 3

80 Low level noise margin for CMOS is____ & TTL is ___ 0.5V,1.5V 0.4V,1.45V 0.45V,1.5V 0.45V,2.5V A 3

81 Propagation delay of CMOS & TTL is _________ respectively 10ns,105ns 105ns,70ns 105ns,10ns 10ns,70ns C 3

82 VNL is equals to VIL(max)—VOL(max) VOH(max) — VIH(max) VIL(max) — VOL(max) VOH(min)— VIH(max) A 3

It is possible to use an incandesnt lamp of rating 10V, 40mA TTL gate with passive normal open-collector TTL

83 as load in a____ TTL gate with totem-pole output pull-up gate open-collector buffer/driver TTL gate D 3

For standard TTL, voltage levels for VOL(max) and VOH(min)

84 are _____ & _ respectively 0.4V,2.4V 0.4,0.8V 2.0,2.4V 0.2V,0.4V A 3

the current drawn from the output transistor of a

If the output of a TTL gate with active pull-up gets a large current will be drawn from the the supply voltage will TTL gate will not be

85 connected to positive 5V accidently supply causing damage to the gate not be affected at all damaged nothing will happen to the gate A 3

a standard TTL gate has A low power schottky TTL

lower fan out while gate has higher fan out

a standard TTL gate has higher fan out driving low power while driving standard TTL

while driving low power Schottky TTL Schottky TTL gates than gates than while driving A low power schokkty gate has same fan

gates than while driving standard TTL while driving standard low power schottky TTL out while driving standard TTL gates &

86 Which of the following statement is true? gates. TTL gates. gates low power schottky TTL gates. A 3

for TTL 74LS series, IOL= 8MA, IOH=-400µA,IIH=20µA & IIL=

87 -.36mA. Its fan out is 1 10 20 30 C 3

The thrshold voltage of an n channel enhancement mode

MOSFET is 2v. The gate voltage required for conduction is

88 ________ 0.7V 1V 2V more than 2V D 3

(FA) 16 is the ________ one’s complement representation of

89 -5 4-bit 8-bit 16-bit 2-bit B 2

If sign bit (MSB) of The ‘1’ in the MSB position

When adding two positive numbers result and sign bit of indicates a negative

Which of the following condition is true for determining gives a negative result or when two two operands are of number after adding two

90 overflow condition in 2’s complement? negatives give a positive result different signs. positive numbers. All of the above D 1

How -5 is represented in hex format in 2’s complement in

91 8-bits? (FB)16 (7F) 16 (FF)16 (FA)16 A 4

two possible encodings of

92 value of B in 2’s complement binary? the decimal 0.

93 How will you represent −42 in hexadecimal? D6 26 D4 24 A 2

If adding two negative If the magnitude of the result is smaller

If there is a carry out of the least If there is a carry out of numbers results in a than the magnitude of the smaller add

94 Which one of these will cause overflow in signed addition? significant bit. the most significant bit. positive result. end. C 2

How many decimal nos are represented by an 8-bit string,

95 assuming 2’s complement binary? 255 256 8 128 B 2

What is the representation of the sign binary string 0111

96 0101 1011 in hexadecimal and decimal? 0x75B, -1883 in base 10 0x8A4, -1883 in base 10 0x8A4, 1883 in base 10 0x75B, 1883 in base 10 D 2

The 4-variable Karnaugh Map (K-Map) has ______rows and

97 ____colums 2,2 4,2 4,4 2,4 C 1

Eliminate one variable Eliminate both variables in Add both variables in resulting resulting

98 By pairing two adjucent 1's in K-map we can__________ Add one variable in resulting term in original term resulting resulting term term D 1

99 The maxterm corresponding to the combination 011 is_____ Ā + Ē + Ō A+Ē+O A+Ē+Ō Ā+E+O C 1

100 An Octet in K-map eliminates_______________ variable One Two Three Eight C 1

101 In K-map groups may be________________ Horizontal Vertical Diagonal Both horizontal and vertical D 1

Simplification of Y = Σm(1,3,7,11,15) + d(0,2,5) using K-map

102 results into_______.(Consider A,E,I and O as literals) Y = IO+ĀĒ Y = IO+AE Y=ĀŌ + ĒI Y = IŌ + AĒ A 4

What will be the result of minimising the logical expression

103 Y = ĀĒĪ + ĀEĪ + ĀEI + AĒI using K-map. ĀE + ĀI + AĒI AE + ĀĪ + AĒI AE + AĪ + AĒI ĀE + ĀĪ + AĒI D 2

104 Identify the slowest of the logic families listed below LSTTL TTL ECL LOW POWER TTL D 1

In case of CMOS and TTL devices operating at same power

supply voltage of +5 volts, no additional interface IC is either CMOS to TTL or TTL

105 required for________ TTL to CMOS interface CMOS to TTL interface to CMOS interface none of these A 1

two N-channel and two

106 The basic CMOS 2-input NAND gate requires____________. two N-channel MOSFETS P-channel MOSFETS two P-channel MOSFETS one N-channel and one P-channel MOSFET B 1

It is recommended that unused inputs of AND and NAND either logic HIGH or logic

107 gates of TTL family are not left open and are tied to logic High logic LOW LOW ground A 1

_______________ if the circuit which connects or isolates

108 it's input from it's output. Tristate buffer Wired AND open collector TTL TTL inverter A 1

109 In TTL _______________ is lower than CMOS. Propogation delay Fan-out Power dissipation Fan-in B 1

CMOS IC can operate on higher power supply voltages,

110 when ______ noise margin is required. Lower Moderate Higher Extremely Low C 1

The ___________ devices are preferred for battery

111 operated systems. CMOS ECL TTL RTL A 1

We have to use a _____________ network to protect the

112 CMOS IC against electrostatic discharge. Resistive Resistor Diode Capacitive Inductive B 1

Higher Operating

113 Due to __________ CMOS may get damaged permanently. Latch ups frequency High input capacitance Lower operating frequency. A 1

114 __________ are used as buffer/driver. Open collector TTL Open drain output CMOS Tristate buffer C 1

The _______ operator represents complementary

115 function. NOT NOR NAND EXNOR A 1 1 NOT represents inversion or complementary

From the truth table below, determine the standard

116 SOP expression. D 1 1 Outputs which are 1 are taken for SOP.

An OR gate with "bubbles" on its inputs performs the

117 same functions as ________ gate. NAND NOR NOT OR A 1 1 Draw the truth table and then verify it.

The expression Y=AB+(A+B)(ĀB+BB) is simplified

118 as Y= _____ A+B ĀB B AB C 2 1 Use Rules : AB+AB=AB , BB=B, AĀ=0 ,A+1=1

Given function contains minterms and hence answer

119 Find the equivalent of ∑m(2,4,7). ∑M(0,1,3,5,-6) ∏m(0,1,3,5,6) ∑m(0,1,3,5,6) ∏m(0,1,3,5,-6) B 1 1 should have remainig as maxterms

The expression Y=∑m(0,1) can also be represented as

120 Y=______ A B+A B AB+AB A B+A B A B+A B A 1 1 First two combinations are to be considered for this

The output of an OR gate with three inputs, A, B, and As OR gate is having its ouput 1 even if any of the

121 C, is LOW when ________. A = 0, B = 0, C = 0 A = 0, B = 0, C = 1 A = 0, B = 1, C = 1 A=1 , B=1 ,C=1 A 1 1 input is 1 therefore 1st option.

Which of the examples below express the commutative As cumulative law of multiplication therefore second

122 law of multiplication? A + B = B + A AB = BA AB = B + A AB = A * B B 1 1 option

Which is the correct logic function for this PAL X sign indicates valid input considred for this

123 diagram? C 4 4 example.

Derive the Boolean expression for the logic circuit

124 shown below: A 1 1 Trace the diagram according to gates.

The Boolean expression is logically

125 equivalent to which single gate? NAND NOR AND OR A 1 1 As given expression is equivalent to ABC

Which of the following gates is described by the Observing the expression , it is product and then

126 expression X=ABCD ? OR AND NOR NAND B 1 1 inversion

How many truth table entries are necessary for a four-

127 input circuit? 4 16 8 12 B 1 1 As 2^4=16

128 EX-OR gate is ______ gate. Derived Basic Universal Complementary A 1 1 As it is formed from other basic gates.

How many AND gates are required to implement

129 Y=AB+CDE 1 2 3 4C 1 1 One for AB and two for CDE.

130 The expression Y=ABC+ABC is in which form? Standard SOP Standard POS SOP and POS POS A 1 1 As both terms contains all variables.

131 0110 represnts which minterm? ABCD ABCD ABCD ABCD C 1 1 As it is represented in Minterms.

ABC=011 amd minterm is ABCand therefore

132 The maxterm A+B+C is represented as ____. M4 m4 M3 m3 C 1 1 maxterm is A+B+C

How many gates would be required to implement the

following Boolean expression after simplification? XY

133 + X(X + Z) + Y(X + Z) 1 2 4 5B 2 2 Use Rule 1+A=1.

Find out from table and as its maxterm answer will

The Standard POS expression Y=(A+B+C)(A+B+C) have for example A+B+C as 0,0,0 and which is 0th

134 (A+B+C) is also expressed as Y=______. ∑M(0,6,2) ∏m(0,6,2) ∑m(7,1,5) ∏M(7,1,5) A 2 2 term.

135 The logic expression for a NOR gate is ________. D 1 1 From truth table we will have the answer D

Find the most simplified SOP expression

136 for F = ABD + CD +ACD + ABC + ABCD. F = ABD + ABC + CD F = CD + AD F = BC + AB F = AC + AD A 2 2 Use rule 1+A=1 for simplification.

can be found in

The NAND or NOR gates are referred to as "universal" can be used to build all the other almost all digital can be used in all types NAND and NOR are used for buliding all other types

137 gates because either: types of gates circuits of Combinational gates were the first gates to be integrated A 1 1 of gates.

The basic types of programmable arrays are made up of Programmable arrays are combination of both AND

138 ________. AND gates OR gates NAND and NOR gates AND gates and OR gates D 2 2 and OR gates

139 How many AND gates are used in a 7408 IC? 1 2 3 4D 1 1 As according to structure only 4 gates are their.

Converting the Boolean expression LM + M(NO + PQ)

140 to SOP form, answer is ________. LM + MNOPQ L + MNO + MPQ LM + M + NO + MPQ LM + MNO + MPQ D 1 1 Only SOP so solve brackets.

141 ASCII code is 4 bit code 6 bit code 8 bit code 7 bit code D 1 EASY

encoder converts decimal information from n input

Decoder Encoder Mux Demux B 1 EASY

142 Decimal digits can be converted to binary format using lines to n ouput lines

The output of gate is LOW when at least one of its for AND operation if any of the input is LOW the

AND OR NOR OR A 1 EASY

143 inputs is HIGH. It is true for OUPUT is Low else it is High

144 The BCD number for decimal 473 is 11101101 111011110101001 010001110011 010011110011 C 1 EASY 4= 0100, 7= 0111, 3= 0011 => 010001110011

Which of the following rules states that if one input of if A=0 then, 0.0=0 ie A itself and if A=1 then, 1.1=1

an AND gate is always 1 , the output is equal to the A+1=1 A+A=A A.1=A A.A=A D 1 EASY

ie again A itself

145 other input ?

the minimum number of NOR gates required to realize 2 3 4 5 D 1 EASY

146 X-NOR gate is

In a combinational circuit the ouputs at any instant only on the inputs

only on past input only on past output past as well as present inputs C 1 EASY

147 depend present at that instant

The format used to present the logic output for the Boolean constant Boolean variable truth table input logic function C 2 medium

148 various combinations of logic inputs to a gate is called

if a 3-input OR gate has eight input possibilities, how

many of those possibilities will result in a HIGH 1 2 7 8 C medium because for input ABC when 000 then 0+0+0=0

149 output?

0 1 A B+A B ( A*B) * ( A*B) A 2 medium

150 the output of the circuit shown is equal to:

Gate No.1 Gate No.2 Gate No.3 Gate No.4 B 2 medium

151 In the above gate network which gate is redundant

signed 16 bit integer

floating point multiplication arithmetic left shift none of these A

152 Sign extension is a step in addition

making the group of 3 bits from LSB towards MSB

81 72 71 none of these B 1 easy

153 the Octal equivalent of 111010 is 111=7 010=2=> 72

154 Which code is a weigthed code Gray Excess-3 BCD 5111 C

155 The digital systems usually operate on ........system binary decimal octal hexadecimal A

156 The binary system uses powers of ........for positional va 2 10 8 16 A

157 After counting 0, 1, 10, 11, the next binary number is 12 100 101 110 B

158 The number 10002 is equivalent to decimal number one thousand eight four sixteen B

159 In binary numbers, shifting the binary point one place to multiplies by 2 divides by 2 decreases by 10 increases by 10 A

160 The binary addition 1 + 1 + 1 gives 111 10 110 11 D

161 The cumulative addition of the four binary bits ( 1 + 1 + 1111 111 100 1001 B

162 The result of binary subtraction (100 − 011) is −111 111 11 1D

163 The chief reason why digital computers use complemental simplifies their circuitry is a very simple procescan handle negative numbeavoids direct subtraction A

164 The result of binary multiplication 1111 × 102 is 1101 110 1001 1110 A

165 The binary division 110002 ÷ 1002 gives 110 1100 11 101 D

166 Hexadecimal number system is used as a shorthand langua decimal binary octal large D

167 Octal coding involves grouping the bits in 5's 7's 4's 3's D

168 In Excess-3 code each coded number is .......than in BC four larger three smaller three larger much larger C

169 Base 10 refers to which number system? binary coded decimal decimal octal hexadecimal B

170 Which numbering system uses numbers and letters as sydecimal binary octal hexadecimal D

171 The number of bits used to store a BCD digit is 8 4 1 2B

172 Sample-and-hold circuits in ADCs are designed to: sample and hold the output of the binarystabilize the ADCs thresh stabilize the input analog s sample and hold the ADC staircase wavefor C

You might also like

- Digital Electronics Exercises With AnswersDocument157 pagesDigital Electronics Exercises With Answersdineshdkj83% (6)

- EXPENSE TRACKER REPORT (GRP 32)Document46 pagesEXPENSE TRACKER REPORT (GRP 32)Aryan Pinto100% (1)

- 18csl37-Ade Lab ManualDocument41 pages18csl37-Ade Lab ManualEragon ShadeSlayerNo ratings yet

- Intro To Logic Gates and K-MapsDocument13 pagesIntro To Logic Gates and K-MapsSergio Phan LungNo ratings yet

- CSE 231 Final - Summer 2021Document2 pagesCSE 231 Final - Summer 2021Sifat AnwarNo ratings yet

- DELD Unit I & Unit II MCQDocument39 pagesDELD Unit I & Unit II MCQGauri TupeNo ratings yet

- DLD 2018Document53 pagesDLD 2018ZuhabNo ratings yet

- Pune Vidyarthi Griha's COE Digital Electronics and Logic Design NotesDocument74 pagesPune Vidyarthi Griha's COE Digital Electronics and Logic Design NotesDino JamesNo ratings yet

- Matoshri College of Engineering and Research Center Nasik Department of Computer EngineeringDocument11 pagesMatoshri College of Engineering and Research Center Nasik Department of Computer EngineeringAditya DarekarNo ratings yet

- Wireless Networks: Error Detecting and Correcting TechniquesDocument22 pagesWireless Networks: Error Detecting and Correcting TechniquesAsif MehmoodNo ratings yet

- Deld 1MDocument26 pagesDeld 1MAryan PintoNo ratings yet

- AE 242 Aerospace Measurements Lab Digital Signals and Binary ArithmeticDocument60 pagesAE 242 Aerospace Measurements Lab Digital Signals and Binary ArithmeticAnubhavNo ratings yet

- Data Communications and Networking 5th Edition Forouzan Solutions Manual DownloadDocument12 pagesData Communications and Networking 5th Edition Forouzan Solutions Manual DownloadJoseph Hays100% (18)

- Publication 6 431 6508Document19 pagesPublication 6 431 6508Damilola OniNo ratings yet

- Problem Set 4Document3 pagesProblem Set 4Akshit SharmaNo ratings yet

- 5 Datalink Layer enDocument87 pages5 Datalink Layer enEdimarf SatumboNo ratings yet

- 01-02_number systDocument41 pages01-02_number systEray GülerNo ratings yet

- Lecture Slides Week 02Document22 pagesLecture Slides Week 02Farrukh AbbasNo ratings yet

- Chpter VDocument9 pagesChpter VYsha FernNo ratings yet

- Unit Iii: Design With Msi DevicesDocument16 pagesUnit Iii: Design With Msi DevicesArjun SeshadhryNo ratings yet

- Digital Electronics Notes PDFDocument43 pagesDigital Electronics Notes PDFneelam sanjeev kumar0% (1)

- Lecture 03 PDFDocument20 pagesLecture 03 PDFEsmaeil AlkhazmiNo ratings yet

- 9 Error Detection Schemes 08112022 011057pmDocument17 pages9 Error Detection Schemes 08112022 011057pmGohanNo ratings yet

- 05_Codes & Displays- 2022-23Document20 pages05_Codes & Displays- 2022-23Eray GülerNo ratings yet

- Typical Questions and AnswersDocument158 pagesTypical Questions and Answersiragire viateurNo ratings yet

- Ch3-4-5-Linear Block Codes-Galois Fields-Cyclic, Convolutional, Max Length Shift RegisterDocument50 pagesCh3-4-5-Linear Block Codes-Galois Fields-Cyclic, Convolutional, Max Length Shift RegisterRubel HalderNo ratings yet

- Co 2 Marks All Units Q & A Final PrintDocument10 pagesCo 2 Marks All Units Q & A Final PrintArun VijayNo ratings yet

- ASCII and Digital CodesDocument79 pagesASCII and Digital CodesZELE MIHERETNo ratings yet

- Digital Electronics Multiple Choice QuestionsDocument154 pagesDigital Electronics Multiple Choice QuestionsDan DizonNo ratings yet

- LDPC Tutorial Mod1Document55 pagesLDPC Tutorial Mod1JerryNo ratings yet

- DigitalLogic LogicGatesCombinationalCircuitsDocument56 pagesDigitalLogic LogicGatesCombinationalCircuitsLawk othmanNo ratings yet

- Arithmetic Operations in Binary: Addition / Subtraction 01011 + 111 ? "Method" Exatly The Same As DecimalDocument49 pagesArithmetic Operations in Binary: Addition / Subtraction 01011 + 111 ? "Method" Exatly The Same As DecimalAmit UpadhyayNo ratings yet

- Digital ElectronicsDocument19 pagesDigital ElectronicsNitysNo ratings yet

- CSE369 Wi22 Quiz3 SolnDocument4 pagesCSE369 Wi22 Quiz3 SolnDeniz Melek TürkNo ratings yet

- w4 One PDFDocument40 pagesw4 One PDFjudith riefdNo ratings yet

- Error Control Coding: Basic Concepts Classes of CodesDocument17 pagesError Control Coding: Basic Concepts Classes of CodesramumceNo ratings yet

- Number Systems: Prof. Jagannadha Naidu K Assistant Professor (SR.) SENSE, VIT UniversityDocument18 pagesNumber Systems: Prof. Jagannadha Naidu K Assistant Professor (SR.) SENSE, VIT UniversityArvind Kumar PrajapatiNo ratings yet

- Convolutional CodesDocument21 pagesConvolutional CodesSalem AlsalemNo ratings yet

- w5skr3200 ADocument33 pagesw5skr3200 ALaili JamlusNo ratings yet

- DigitalDocument182 pagesDigitalYeshoda MallikarjunaNo ratings yet

- ELEC2141 Combinational Circuit Building BlocksDocument36 pagesELEC2141 Combinational Circuit Building Blocks刘浩灵No ratings yet

- Chapter 1-1Document25 pagesChapter 1-1AynalemNo ratings yet

- Boolean Logic and Digital Circuits Multiple Choice QuestionsDocument6 pagesBoolean Logic and Digital Circuits Multiple Choice Questionsprakash chandNo ratings yet

- ECE213 Solved QuestionsDocument89 pagesECE213 Solved QuestionsJundeep SharmaNo ratings yet

- Lect03-1 4-1 5-1 6Document19 pagesLect03-1 4-1 5-1 6القادم أجملNo ratings yet

- Lecture #3Document13 pagesLecture #3Abdii MakNo ratings yet

- DELD MCQ's - 2Document14 pagesDELD MCQ's - 2Aryan PintoNo ratings yet

- Digtial CircuitDocument25 pagesDigtial CircuitChetan DahalNo ratings yet

- Deld MCQ 3MDocument9 pagesDeld MCQ 3MAryan PintoNo ratings yet

- Chapter 3 - Combinational Logic DesignDocument36 pagesChapter 3 - Combinational Logic Designmahbub mitulNo ratings yet

- High Performance Computing: Matthew Jacob Indian Institute of ScienceDocument14 pagesHigh Performance Computing: Matthew Jacob Indian Institute of ScienceHritik JaiswalNo ratings yet

- DCN Error Detection and CorrectionDocument37 pagesDCN Error Detection and CorrectionRaheel MahmoodNo ratings yet

- FormulasDocument13 pagesFormulassuvarnalatha devarakondaNo ratings yet

- Week 2 - LecturesDocument64 pagesWeek 2 - Lecturespraveen alwisNo ratings yet

- EEE530 Advanced Digital Communications: Source and Channel CodingDocument79 pagesEEE530 Advanced Digital Communications: Source and Channel CodingHussein KteishNo ratings yet

- Principles of Communications: Convolutional CodesDocument37 pagesPrinciples of Communications: Convolutional CodesBui Trung HieuNo ratings yet

- Digital Electronics - Till Boolean TheoremsDocument70 pagesDigital Electronics - Till Boolean TheoremsManjunathVGudurNo ratings yet

- Unit IvDocument62 pagesUnit Ivsnkarthik35No ratings yet

- DD Assignment-2 SolutionDocument10 pagesDD Assignment-2 Solutionsarim rizviNo ratings yet

- Error Detection and CorrectionDocument20 pagesError Detection and CorrectionRekha V RNo ratings yet

- Data Communication Errors: Networking 2Document24 pagesData Communication Errors: Networking 2Leonelyn Hermosa Gasco - CosidoNo ratings yet

- Electronics 3 Checkbook: The Checkbooks SeriesFrom EverandElectronics 3 Checkbook: The Checkbooks SeriesRating: 5 out of 5 stars5/5 (1)

- DELD MCQ's - 2Document14 pagesDELD MCQ's - 2Aryan PintoNo ratings yet

- Deld MCQ 3MDocument9 pagesDeld MCQ 3MAryan PintoNo ratings yet

- Deld 1MDocument26 pagesDeld 1MAryan PintoNo ratings yet

- BFS and DFS Adjacency Matrix and List GraphsDocument8 pagesBFS and DFS Adjacency Matrix and List GraphsAryan PintoNo ratings yet

- Adcs Spi Communications Timing PresentationDocument56 pagesAdcs Spi Communications Timing PresentationKhưu Minh TấnNo ratings yet

- Introduction To LTspice IVDocument38 pagesIntroduction To LTspice IV29377No ratings yet

- MYP Year III Mathematics Unit 2 GRASPS TaskDocument4 pagesMYP Year III Mathematics Unit 2 GRASPS TaskHamdan mohammedNo ratings yet

- Ec5554 Microcontroller Module: Product InformationDocument7 pagesEc5554 Microcontroller Module: Product InformationABDUL QADIRNo ratings yet

- Solution: Mid-Term ExamDocument3 pagesSolution: Mid-Term ExamMai Anh ThưNo ratings yet

- Stick DiagramDocument55 pagesStick Diagramsamiularefin2000No ratings yet

- STB26NM60N, STF26NM60, Sti26nm60n, STP26NM60N, STW26NM60NDocument23 pagesSTB26NM60N, STF26NM60, Sti26nm60n, STP26NM60N, STW26NM60NjjoaquimmartinsNo ratings yet

- CD40174BC - CD40175BC Hex D-Type Flip-Flop - Quad D-Type Flip-FlopDocument7 pagesCD40174BC - CD40175BC Hex D-Type Flip-Flop - Quad D-Type Flip-FlopJose MariaNo ratings yet

- Reconfigurable Computing Hardware Device ArchitectureDocument10 pagesReconfigurable Computing Hardware Device Architectureksb9790No ratings yet

- ATmega164P 324P 644P Complete (Doc8011)Document439 pagesATmega164P 324P 644P Complete (Doc8011)Anil ChaurasiaNo ratings yet

- ST 62Document75 pagesST 62Fam. Esteves MuñoxNo ratings yet

- Lesson 1 - Components of ComputerDocument17 pagesLesson 1 - Components of Computerkimchen edenelleNo ratings yet

- The 8051 MicrocontrollersDocument17 pagesThe 8051 MicrocontrollersBenhadi PratamaNo ratings yet

- Syllabus - Electrical Sem 4Document81 pagesSyllabus - Electrical Sem 4vcb.polykondagaonNo ratings yet

- Unit-III: Memory: TopicsDocument54 pagesUnit-III: Memory: TopicsZain Shoaib MohammadNo ratings yet

- Ite Lec 01 Introduction v01Document22 pagesIte Lec 01 Introduction v01omar salahNo ratings yet

- Vlsi 2020 21 TitlesDocument8 pagesVlsi 2020 21 TitlesDevi Reddy Maheswara ReddyNo ratings yet

- ISA Definition and MIPS ExamplesDocument3 pagesISA Definition and MIPS ExamplesMANAS AGARWALNo ratings yet

- Discussion Lab 9Document1 pageDiscussion Lab 9thevand11100% (1)

- ENGI 3861 - Digital Logic: Introduction - 1Document8 pagesENGI 3861 - Digital Logic: Introduction - 1vigneshwar RNo ratings yet

- Introduction To Cmos Vlsi Design: Design For Low PowerDocument24 pagesIntroduction To Cmos Vlsi Design: Design For Low PowerGopi ChannagiriNo ratings yet

- General Description: Dual Retriggerable Precision Monostable MultivibratorDocument17 pagesGeneral Description: Dual Retriggerable Precision Monostable Multivibratorsajad hejaziNo ratings yet

- Digital Electronics Flip-Flops: Edge vs Level TriggeringDocument20 pagesDigital Electronics Flip-Flops: Edge vs Level Triggeringmfh273No ratings yet

- Coprocessor Configurations Closely Coupled Losely CoupledDocument9 pagesCoprocessor Configurations Closely Coupled Losely Coupledlauro eugin brittoNo ratings yet

- DS3658 Quad High Current Peripheral Driver: General DescriptionDocument4 pagesDS3658 Quad High Current Peripheral Driver: General DescriptionCarlos Luis ColmenaresNo ratings yet

- Design and Analysis of Approximate Compressors For MultiplicationDocument11 pagesDesign and Analysis of Approximate Compressors For MultiplicationAnju BalaNo ratings yet

- Single Bit Full Adder Design Using 8 Transistors With Novel 3 Transistors XNOR GateDocument13 pagesSingle Bit Full Adder Design Using 8 Transistors With Novel 3 Transistors XNOR GateAnonymous e4UpOQEPNo ratings yet