Professional Documents

Culture Documents

Java Practices 12345678

Java Practices 12345678

Uploaded by

erenyeager1320050 ratings0% found this document useful (0 votes)

2 views2 pagesOriginal Title

Java_practices_12345678

Copyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

2 views2 pagesJava Practices 12345678

Java Practices 12345678

Uploaded by

erenyeager132005Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

You are on page 1of 2

AMRITA VISHWA VIDYAPEETHAM

(University Established U/S 3 of the UGC Act 1956)

CONTENTS:

AMRITA SCHOOL OF ENGINEERING, BENGALURU

Sl. EXPERIMENT Date Marks Sign

No.

1. Verification of Kirchoff’s laws in DC

circuits(Hardware & Simulation)

2.

3.

4.

5.

Lab Report

Academic Year 2024 - Jan -May

Department of Electrical and Electronics Engineering

Name :

Register No :

Semester : 2nd Sem AIE D/E Section

Course Title : Introduction to Electrical and Electronics Engineering

Course Code: 22AIE 114

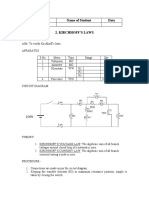

Experiment No. 1 Date

VERIFICATION OF KIRCHOFF’S LAWS FOR D.C CIRCUITS USING MATLB

SIMULINK Platform

AIM:

To verify Kirchhoff’s laws for D.C circuits

Statement:

a) Kirchoff’s current law (KCL): The sum of currents at any node is zero.

OR

At any node, the sum of the incoming currents is equal to the sum of the outgoing

currents

b) Kirchoff’s Voltage law (KVL): The Algebraic sum of applied voltage and the voltage

drops is zero in any closed circuit

OR

In any closed circuit, the sum of the applied voltages is equal to sum of the voltage

drops.

APPARATUS REQUIRED:

PROCEDURE:

Write the Procedure

CIRCUIT DIAGRAM:

Model Calculations:

Simulation Diagram

Graphs

Result & Inference

You might also like

- Instrumentation and Measurement in Electrical EngineeringFrom EverandInstrumentation and Measurement in Electrical EngineeringRating: 3.5 out of 5 stars3.5/5 (5)

- Suruhanjaya Tenaga - Guidelines For Wiring ResidentialDocument55 pagesSuruhanjaya Tenaga - Guidelines For Wiring Residentialkingcloud7100% (24)

- Marine Electrical Practice: Marine Engineering SeriesFrom EverandMarine Electrical Practice: Marine Engineering SeriesRating: 4 out of 5 stars4/5 (8)

- Lab M.S.T Verification of KVLDocument4 pagesLab M.S.T Verification of KVLShreyank PushkarNo ratings yet

- 15Ee103L Electric Circuits Lab: Register No: Name of The Student: Semester: DepartmentDocument66 pages15Ee103L Electric Circuits Lab: Register No: Name of The Student: Semester: DepartmentArvind N LakshmananNo ratings yet

- Lab Manual (CSE133)Document18 pagesLab Manual (CSE133)Shreya Das 203-15-14489No ratings yet

- Eeelab 44Document6 pagesEeelab 44nurshakiblimon2018No ratings yet

- EP LAB ManualDocument70 pagesEP LAB Manual2087 NIRMAL SNo ratings yet

- (ALCANTARA - BSEE-2D) - Activity 2 Electronic Circuits 1Document5 pages(ALCANTARA - BSEE-2D) - Activity 2 Electronic Circuits 1Lawrence Abram AlcantaraNo ratings yet

- New BEE Lab 21elel27Document42 pagesNew BEE Lab 21elel27Ashesh Krishna AdhikariNo ratings yet

- Jaipur National University, Jaipur: School of Engineering & TechnologyDocument26 pagesJaipur National University, Jaipur: School of Engineering & TechnologyRACHANA YADAVNo ratings yet

- EE8261-Electric Circuits Lab Manual PDFDocument91 pagesEE8261-Electric Circuits Lab Manual PDFPraveen Kumar50% (2)

- Physics Project - PDocument23 pagesPhysics Project - PJennis JoelNo ratings yet

- Physics Project - MDocument22 pagesPhysics Project - Mudhayadeepak60No ratings yet

- BH Khan Introduction To Sustainable EnergyDocument40 pagesBH Khan Introduction To Sustainable EnergyTushar GuptaNo ratings yet

- Lesson Plan: PreparationDocument2 pagesLesson Plan: Preparationsurajit biswasNo ratings yet

- Beee Experiment 1.1 - (Akshay Sharma)Document5 pagesBeee Experiment 1.1 - (Akshay Sharma)Akshay SharmaNo ratings yet

- Explaining The Kirchhoffs Law KCL and KVLDocument8 pagesExplaining The Kirchhoffs Law KCL and KVLsinghayushkumar2423No ratings yet

- Experiment I: Verification of Kirchoff'S LawDocument4 pagesExperiment I: Verification of Kirchoff'S LawRennel MallariNo ratings yet

- Physics Project - M EditedDocument23 pagesPhysics Project - M EditedJennis JoelNo ratings yet

- 52224-mt - High Voltage Testing TechniquesDocument2 pages52224-mt - High Voltage Testing TechniquesSRINIVASA RAO GANTANo ratings yet

- Bee Lab MannualDocument45 pagesBee Lab MannualanUGLYcatNo ratings yet

- Institute Engineering Department Academic Unit-1: Discover - . EmpowerDocument34 pagesInstitute Engineering Department Academic Unit-1: Discover - . EmpowerAYUSHNo ratings yet

- Yog Patil - Expt. No. 1Document8 pagesYog Patil - Expt. No. 1Yog PatilNo ratings yet

- 22bce3311 VL2022230105311 Ast01Document10 pages22bce3311 VL2022230105311 Ast01Venkat BalajiNo ratings yet

- 74276-Study On EseDocument109 pages74276-Study On Esestanjack99No ratings yet

- Guru Gobind Singh College of Engineering & Research Centre, NashikDocument5 pagesGuru Gobind Singh College of Engineering & Research Centre, NashikShrey JhaNo ratings yet

- Electric Circuits Lab 15EE103L PDFDocument61 pagesElectric Circuits Lab 15EE103L PDFMadhavanInduNo ratings yet

- Beee Lab Manual-2020Document99 pagesBeee Lab Manual-2020venkata karthikNo ratings yet

- TDPDocument3 pagesTDPHarshad JoshiNo ratings yet

- Task 1Document6 pagesTask 1Harsh ChaudharyNo ratings yet

- 19EEE181 ManualDocument39 pages19EEE181 ManualabcdNo ratings yet

- Eddy Current Testing-1Document8 pagesEddy Current Testing-1hyder_khan74No ratings yet

- Blackbook Sem VIDocument47 pagesBlackbook Sem VIAvanish ShuklaNo ratings yet

- BEEE Manual - 11 - 9 - 23Document57 pagesBEEE Manual - 11 - 9 - 23vermaaarushi1912No ratings yet

- DC Exp 3 Student ManualDocument4 pagesDC Exp 3 Student ManualMuhammad ZayedNo ratings yet

- ELE001 - Basic Electricity and ElectronicsDocument4 pagesELE001 - Basic Electricity and ElectronicsHarold LuceroNo ratings yet

- Roll No Name of Student DateDocument3 pagesRoll No Name of Student Dateleelarani1976No ratings yet

- Electrical Instalation Dee21m 7 CoppiesDocument2 pagesElectrical Instalation Dee21m 7 Coppiesudaku mtaaniNo ratings yet

- Applying Low Voltage CB To Limit Arc FlashDocument6 pagesApplying Low Voltage CB To Limit Arc FlashtechtricNo ratings yet

- Electronic Devices and Circuits Lab: Department of Electrical and Electronics EngineeringDocument14 pagesElectronic Devices and Circuits Lab: Department of Electrical and Electronics EngineeringJeyachandranNo ratings yet

- Beee Worksheet 1Document9 pagesBeee Worksheet 120BCS7140No ratings yet

- Ece IndexDocument1 pageEce IndexMd. Rafiul KabirNo ratings yet

- DC Circuit: Laboratory ManualDocument4 pagesDC Circuit: Laboratory ManualJigar SoniNo ratings yet

- Ieee Schavenmaker 2000aDocument5 pagesIeee Schavenmaker 2000avallala venkateshNo ratings yet

- EE6211-Electric Circuits Laboratory MANUALDocument78 pagesEE6211-Electric Circuits Laboratory MANUALsakilakumaresanNo ratings yet

- 5039B Applied Electronics Laboratory (S5ELCT)Document72 pages5039B Applied Electronics Laboratory (S5ELCT)razahrazNo ratings yet

- Static Electromagnetic Frequency Changers: International Series of Monographs on Electronics and InstrumentationFrom EverandStatic Electromagnetic Frequency Changers: International Series of Monographs on Electronics and InstrumentationNo ratings yet

- Basic Electric Circuits: Pergamon International Library of Science, Technology, Engineering and Social StudiesFrom EverandBasic Electric Circuits: Pergamon International Library of Science, Technology, Engineering and Social StudiesRating: 3 out of 5 stars3/5 (1)

- Design and Implementation of Portable Impedance AnalyzersFrom EverandDesign and Implementation of Portable Impedance AnalyzersNo ratings yet

- It Is Quite Another Electricity: Transmitting by One Wire and Without GroundingFrom EverandIt Is Quite Another Electricity: Transmitting by One Wire and Without GroundingNo ratings yet

- Electromagnetic Compatibility in Underground Mining: Selected ProblemsFrom EverandElectromagnetic Compatibility in Underground Mining: Selected ProblemsNo ratings yet

- High Sensitivity Counting Techniques: International Series of Monographs on Electronics and InstrumentationFrom EverandHigh Sensitivity Counting Techniques: International Series of Monographs on Electronics and InstrumentationNo ratings yet

- Microwave Power Engineering: Generation, Transmission, RectificationFrom EverandMicrowave Power Engineering: Generation, Transmission, RectificationErnest C. OkressNo ratings yet

- Kalarippayattu The Ancient Martial-17112023-1Document4 pagesKalarippayattu The Ancient Martial-17112023-1erenyeager132005No ratings yet

- Final ReportDocument10 pagesFinal Reporterenyeager132005No ratings yet

- OnePlus 5 User ManualDocument39 pagesOnePlus 5 User Manualerenyeager132005No ratings yet

- 21mat105 Mis-1 Lab Practicesheet-6 (Spanset Rs Cs NS)Document3 pages21mat105 Mis-1 Lab Practicesheet-6 (Spanset Rs Cs NS)Dinesh SomisettyNo ratings yet