100% found this document useful (1 vote)

2K views20 pagesBasic Scan

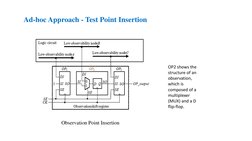

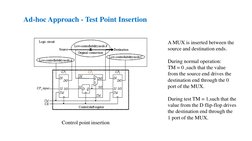

The document discusses design for testability (DFT) and basic scan design concepts. It introduces DFT and why it is needed to address increasing test complexity. It then describes testability, different scan cell designs, scan architectures like full scan and partial scan, and the basic scan design flow. The goal of DFT and scan design is to improve the controllability and observability of a circuit to simplify testing.

Uploaded by

saikumar bhavanaCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PPTX, PDF, TXT or read online on Scribd

100% found this document useful (1 vote)

2K views20 pagesBasic Scan

The document discusses design for testability (DFT) and basic scan design concepts. It introduces DFT and why it is needed to address increasing test complexity. It then describes testability, different scan cell designs, scan architectures like full scan and partial scan, and the basic scan design flow. The goal of DFT and scan design is to improve the controllability and observability of a circuit to simplify testing.

Uploaded by

saikumar bhavanaCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PPTX, PDF, TXT or read online on Scribd