Professional Documents

Culture Documents

SYEN 3330 Digital Systems: Chapters 4 - Part3: Verilog - Part 1

Uploaded by

anjanappa0 ratings0% found this document useful (0 votes)

28 views17 pagesThis document provides an overview of Verilog, a hardware description language. It describes Verilog basics like notation, keywords, constructs and operators. It also describes different types of Verilog descriptions including structural, dataflow, behavioral, hierarchical and procedural. Specific examples are given to illustrate structural, dataflow and behavioral descriptions. The objectives of learning Verilog and how it can be used to specify digital designs are also outlined.

Original Description:

Original Title

Lecture_4-3

Copyright

© © All Rights Reserved

Available Formats

PPT, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThis document provides an overview of Verilog, a hardware description language. It describes Verilog basics like notation, keywords, constructs and operators. It also describes different types of Verilog descriptions including structural, dataflow, behavioral, hierarchical and procedural. Specific examples are given to illustrate structural, dataflow and behavioral descriptions. The objectives of learning Verilog and how it can be used to specify digital designs are also outlined.

Copyright:

© All Rights Reserved

Available Formats

Download as PPT, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

28 views17 pagesSYEN 3330 Digital Systems: Chapters 4 - Part3: Verilog - Part 1

Uploaded by

anjanappaThis document provides an overview of Verilog, a hardware description language. It describes Verilog basics like notation, keywords, constructs and operators. It also describes different types of Verilog descriptions including structural, dataflow, behavioral, hierarchical and procedural. Specific examples are given to illustrate structural, dataflow and behavioral descriptions. The objectives of learning Verilog and how it can be used to specify digital designs are also outlined.

Copyright:

© All Rights Reserved

Available Formats

Download as PPT, PDF, TXT or read online from Scribd

You are on page 1of 17

SYEN 3330

Digital Systems

Chapters 4 – Part3:

Verilog – Part 1

SYEN 3330 Digital Systems Jung H. Kim Chapter 4-3 1

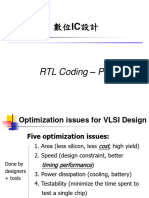

Overview of Verilog – Part 1

• Objectives

• Verilog Basics

Notation

Keywords & Constructs

Operators

• Types of Descriptions

Structural

Dataflow

• Boolean Equations

• Conditions using Binary Combinations

• Conditions using Binary Decisions

Behavioral & Hierarchical

Process (Procedural)

SYEN 3330 Digital Systems Chapter 4-3 Page 2

Objectives

• To become familiar with the hardware

description language (HDL) approach to

specifying designs

Be able to read a simple Verilog HDL

description

Be able to write a simple Verilog HDL

description using a limited set of syntax and

semantics

Understanding the need for a “hardware

view” when reading and writing an HDL

SYEN 3330 Digital Systems Chapter 4-3 Page 3

Verilog Notation - 1

• Verilog is:

Case sensitive

Based on the programming language C

• Comments

Single Line

// [end of line]

Multiple Line

/*

*/

• List element separator: ,

• Statement terminator: ;

SYEN 3330 Digital Systems Chapter 4-3 Page 4

Verilog Notation - 2

• Binary Values for Constants and Variables

0

1

X,x - Unknown

Z,z – High impedance state (open circuit)

• Constants

n’b[integer]: 1’b1 = 1, 8’b1 = 000000001, 4’b0101=

0101, 8’bxxxxxxxx, 8’bxxxx = 0000xxxx

n’h[integer]: 8’hA9 = 10101001, 16’hf1=

0000000011110001

• Identifier Examples

Scalar: A,C,RUN,stop,m,n

Vector: sel[0:2], f[0:5], ACC[31:0], SUM[15:0],

sum[15:0]

SYEN 3330 Digital Systems Chapter 4-3 Page 5

Verilog Keywords & Constructs - 1

• Keywords are lower case

• module – fundamental building block for Verilog

designs

Used to construct design hierarchy

Cannot be nested

• endmodule – ends a module – not a statement

=> no “;”

• Module Declaration

module module_name (module_port, module_port, …);

Example: module full_adder (A, B, c_in,

c_out, S);

SYEN 3330 Digital Systems Chapter 4-3 Page 6

Verilog Keywords & Constructs - 2

• Input Declaration

Scalar

• input list of input identifiers;

• Example: input A, B, c_in;

Vector

• input[range] list of input identifiers;

• Example: input[15:0] A, B, data;

• Output Declaration

Scalar Example: output c_out, OV, MINUS;

Vector Example: output[7:0] ACC, REG_IN,

data_out;

SYEN 3330 Digital Systems Chapter 4-3 Page 7

Verilog Keywords & Constructs - 3

• Primitive Gates

buf, not, and, or, nand, nor, xor, xnor

Syntax: gate_operator instance_identifier

(output, input_1, input_2, …)

Examples:

and A1 (F, A, B); //F = A B

or O1 (w, a, b, c)

O2 (x, b, c, d, e); //w=a+b+c,x=b+c+d+e

SYEN 3330 Digital Systems Chapter 4-3 Page 8

Verilog Operators - 1

• Bitwise Operators

~ NOT

& AND

| OR

^ XOR

^~ or ~^ XNOR

• Example: input[3:0] A, B;

output[3:0] Z ;

assign Z = A | ~B;

SYEN 3330 Digital Systems Chapter 4-3 Page 9

Verilog Operators - 2

• Arithmetic Operators

+, -, (plus others)

• Logical & Relational Operators

!, &&, | |, = =, !=, >=, <=, >, < (plus others)

• Concatenation & Replication Operators

{identifier_1, identifier_2, …}

{n{identifier}}

Examples: {REG_IN[6:0],Serial_in},

{8 {1’b0}}

SYEN 3330 Digital Systems Chapter 4-3 Page 10

SYEN 3330 Digital Systems Chapter 4-3 Page 11

Structural Verilog

• Circuits can be described by a netlist as a text alternative to

a diagram - Example (See Figure 5-19 in text):

module fig519s (A0, B0, C0, C1, S0);

input A0, B0, C0;

output C1, S0;

//Seven internal wires needed

wire[1:7] N;

//Ports on primitive gates listed output port first

not G1 (N[3],C0), G2 (N[5],N[2]), G3 (N[6],N[3]);

nand G4 (N[1],A0,B0);

nor G5 (N[2],A0,B0), G6 (C1,N[2],N[4]);

and G7 (N[4],N[1],N[3]), G8 (N[7],N[1],N[5]);

xor G9 (S0,N[6],N[7]);

endmodule

SYEN 3330 Digital Systems Chapter 4-3 Page 12

Dataflow Verilog - 1

• Circuit function can be described by assign statements

using Boolean equations (See Figure 5-19 in text):

module fig519d (A0, B0, C0, C1, S0);

input A0, B0, C0;

output C1, S0;

wire[1:2] N;

assign N[1] = ~(A0 & B0); /*Note: Cannot write ~& for

NAND */

assign N[2] = ~(A0 | B0);

assign C1 = ~((N[1] & ~C0) | N[2]);

assign S0 = (~N[2] & N[1])^(~(~C0));

endmodule

SYEN 3330 Digital Systems Chapter 4-3 Page 13

Dataflow Verilog - 2

• Circuit function can be described by assign statements using the conditional

operator with binary combinations as in a truth table (See Figure 4-10 in

text):

module fig410dm (A, E_n, D_n);

input[1:0] A;

input E_n;

output[3:0] D_n;

//Conditional: (X) ? Y: Z - if X is true, then Y,else Z

assign D_n = {4{E_n}}&(

(A == 2'b00) ? 4'b1110:

(A == 2'b01) ? 4'b1101:

(A == 2'b10) ? 4'b1011:

(A == 2'b11) ? 4'b0111:

4'bxxxx);

endmodule

SYEN 3330 Digital Systems Chapter 4-3 Page 14

Dataflow Verilog - 3

• Circuit function can be described by assign statements using

the conditional operator for binary decisions on inputs(See

Figure 4-10 in text):

module fig410dc (A, E_n, D_n);

input[1:0] A;

input E_n;

output[3:0] D_n;

/* Conditional: (X) ? Y: Z - if X is true, then Y,else Z */

assign D_n = {4{E_n}} & (A[1] ? (A[0] ? 4'h7 : 4'hB): (A[0] ?

4'hD : 4'hE));

endmodule

SYEN 3330 Digital Systems Chapter 4-3 Page 15

Behavioral & Hierarchical Verilog

• Circuit function can be described by assign statements at

higher than the logic level (See Figure 5-8 in text):

module addsub (A, B, R, sub) ;

input [3:0] A, B ;

output [3:0] R ;//See Fig. 5-18 for carry out

input sub ;

wire [3:0] data_out;

add A1 (A, data_out, sub, R);

M1comp C1 (B, data_out, sub);

endmodule

SYEN 3330 Digital Systems Chapter 4-3 Page 16

Behavioral & Hierarchical Verilog

module add (X, Y, C_in, S);

input [3:0] X, Y;

input C_in;

output [3:0] S;

assign S = X + Y + {3'b0, C_in};

endmodule

module M1comp (data_in, data_out, comp);

input[3:0] data_in;

input comp;

output [3:0] data_out;

assign data_out = {4{comp}} ^ data_in;

endmodule

SYEN 3330 Digital Systems Chapter 4-3 Page 17

You might also like

- Verilog: Logic and Computer Design FundamentalsDocument10 pagesVerilog: Logic and Computer Design FundamentalsEmre ErensoyNo ratings yet

- Verilog SlidesDocument24 pagesVerilog SlidesDeepikaa PoobalarajaNo ratings yet

- Im Tech Ver I Log IntroductionDocument85 pagesIm Tech Ver I Log Introductionramkushal090No ratings yet

- Verilog Dataflow Modeling: Expt. No. 3 (Fourth Week Lab1 and Lab2)Document5 pagesVerilog Dataflow Modeling: Expt. No. 3 (Fourth Week Lab1 and Lab2)R INI BHANDARINo ratings yet

- Verilog HDL Introduction: ECE 554 Digital Engineering LaboratoryDocument79 pagesVerilog HDL Introduction: ECE 554 Digital Engineering LaboratoryBbsn EmbeddedNo ratings yet

- Introduction To Verilog HDL: Presented by K.SwathiDocument35 pagesIntroduction To Verilog HDL: Presented by K.SwathiswathikomatiNo ratings yet

- Verilog Lec s03Document126 pagesVerilog Lec s03Bruno SilvaNo ratings yet

- Chapter 4Document58 pagesChapter 4Agha Salman HaiderNo ratings yet

- Verilog GATE AND DATA FLOWDocument64 pagesVerilog GATE AND DATA FLOWPRIYA MISHRANo ratings yet

- Hardware Description Language: - Tool For Specifying Hardware Circuits Types of HDL: - VHDL - VerilogDocument17 pagesHardware Description Language: - Tool For Specifying Hardware Circuits Types of HDL: - VHDL - Verilogاسامه صلاح الدينNo ratings yet

- DDCArv Ch3Document36 pagesDDCArv Ch3rabiatul adawiyahNo ratings yet

- DDCAarm Ch4Document40 pagesDDCAarm Ch4SebaNo ratings yet

- Verilog: Advantages of HDL Based Design TechniqueDocument9 pagesVerilog: Advantages of HDL Based Design TechniqueRafiqul IslamNo ratings yet

- Verilog TutorialDocument92 pagesVerilog TutorialAmmar AjmalNo ratings yet

- VerilogDocument115 pagesVeriloganurag kumarNo ratings yet

- Intro To VerilogDocument68 pagesIntro To VerilogNicolas AmezquitaNo ratings yet

- DDCArv Ch4Document71 pagesDDCArv Ch4Islamic & Science AcademyNo ratings yet

- Computer System Architectures: Based OnDocument52 pagesComputer System Architectures: Based OnIvan ZamoraNo ratings yet

- Lec13 X86asmDocument71 pagesLec13 X86asmmeowmeow88No ratings yet

- HDL Model of Combinational CircuitsDocument6 pagesHDL Model of Combinational CircuitsMunwar Ali Sd100% (1)

- 2011verilog Lec v1 PDFDocument82 pages2011verilog Lec v1 PDFpeter26194100% (1)

- Lab 6 Verilog Data FlowDocument13 pagesLab 6 Verilog Data FlowUsama Javid MughalNo ratings yet

- Verilog BasicDocument48 pagesVerilog BasicDaksh BothraNo ratings yet

- SystemC Data Types 2pagesDocument12 pagesSystemC Data Types 2pagesrk123456No ratings yet

- Verilog PresentationDocument43 pagesVerilog PresentationRüstem EleçNo ratings yet

- DSDV M1Document21 pagesDSDV M1Shamitha HiremathNo ratings yet

- Ds First LatestDocument31 pagesDs First LatestZohaib KhanNo ratings yet

- Unit-V Verilog Hardware Description LanguageDocument73 pagesUnit-V Verilog Hardware Description LanguageThariq Azeez MNo ratings yet

- VLSI Lab Manual Exercise ProblemsDocument38 pagesVLSI Lab Manual Exercise ProblemsPrakhar Kumar100% (1)

- Verilog HDLDocument62 pagesVerilog HDLc406400100% (1)

- Chapter 3Document105 pagesChapter 3s9222647No ratings yet

- Mtds 1 VHDL Quick LookDocument6 pagesMtds 1 VHDL Quick Looknithinsp92No ratings yet

- Introduction To Verilog HDL - SRSDocument50 pagesIntroduction To Verilog HDL - SRSSusheela Patgar 2GI19EC164No ratings yet

- Design Domain and Levels of AbstractionDocument68 pagesDesign Domain and Levels of Abstractionsirisha1983No ratings yet

- Lab 07Document10 pagesLab 07api-241454978No ratings yet

- Basic Logic Design With Verilog HDL: Combinational CircuitsDocument67 pagesBasic Logic Design With Verilog HDL: Combinational CircuitsAfshan KaleemNo ratings yet

- VerilogDocument18 pagesVerilogReggie Fresco AguilarNo ratings yet

- VerilogDocument61 pagesVerilogSathish Kumar100% (1)

- Verilog HDLDocument204 pagesVerilog HDLNhu Ngoc Phan Tran100% (1)

- Bitwise OperationsDocument12 pagesBitwise OperationsAnuruddha Bhattacharjee JohnNo ratings yet

- Classroom 3Document43 pagesClassroom 3nitcvisheshNo ratings yet

- CO Lab Manual-MinDocument40 pagesCO Lab Manual-MinMatheen TabidNo ratings yet

- LOVELY ProjectDocument30 pagesLOVELY ProjectPrathap SujayveraNo ratings yet

- Unit Ii Program Design and Analysis: - Software Components. - Representations of Programs. - Assembly and LinkingDocument60 pagesUnit Ii Program Design and Analysis: - Software Components. - Representations of Programs. - Assembly and LinkingRahul SharmaNo ratings yet

- Digital Logic Design (EL-227) : Laboratory Manual Spring-2020Document5 pagesDigital Logic Design (EL-227) : Laboratory Manual Spring-2020Demin revisNo ratings yet

- Lab 6 Verilog Data FlowDocument13 pagesLab 6 Verilog Data Flowsafdarmunir070No ratings yet

- Verilog 1 - Fundamentals: 6.375 Complex Digital Systems ArvindDocument36 pagesVerilog 1 - Fundamentals: 6.375 Complex Digital Systems ArvindVIJAYPUTRANo ratings yet

- Verilog Present 2Document25 pagesVerilog Present 2markloopNo ratings yet

- S1 Introduction To VerilogDocument41 pagesS1 Introduction To Verilog유홍승No ratings yet

- Assign in VerilogDocument4 pagesAssign in VerilogafmohfwhlNo ratings yet

- Digital Circuit Verification Hardware Descriptive Language VerilogDocument17 pagesDigital Circuit Verification Hardware Descriptive Language VerilogFreyja SigurgisladottirNo ratings yet

- Verilog Tutorial For Beginner'sDocument65 pagesVerilog Tutorial For Beginner'sSachin SreelalNo ratings yet

- Introduction To VHDLDocument153 pagesIntroduction To VHDLKirankumar LadNo ratings yet

- Intro To HDL MidtermDocument112 pagesIntro To HDL MidtermchienikolaoNo ratings yet

- Lab 5Document13 pagesLab 5SHAHZAIB AHMAD QURESHINo ratings yet

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (2)

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- PH537/PI515: Astrostructure and Evolution: Answer With Examples and ReferencesDocument4 pagesPH537/PI515: Astrostructure and Evolution: Answer With Examples and ReferencesSDasNo ratings yet

- Programming Manual II Fx1s2Document224 pagesProgramming Manual II Fx1s2chaubinhkhang110686No ratings yet

- Logical Reasoning - Venn Diagrams - English - 1600422066Document9 pagesLogical Reasoning - Venn Diagrams - English - 1600422066saiNo ratings yet

- Arima JmultiDocument11 pagesArima Jmultijota de copasNo ratings yet

- MATHS FORM TWO QNS Teacher - Co - KeDocument10 pagesMATHS FORM TWO QNS Teacher - Co - Kekasumbaashraf3No ratings yet

- Unit 2 Introduction To CDocument30 pagesUnit 2 Introduction To CSujit KhandareNo ratings yet

- STAT 151A SyllabusDocument2 pagesSTAT 151A SyllabusWilliamHuangNo ratings yet

- Geometry: Quarter 1 - Module 6: Perimeter and Area of PolygonsDocument23 pagesGeometry: Quarter 1 - Module 6: Perimeter and Area of Polygonskyeopta jullieNo ratings yet

- Reading Graphs and ChartsDocument2 pagesReading Graphs and ChartsSebastián García MeyerNo ratings yet

- All About Personality Number in NumerologyDocument1 pageAll About Personality Number in Numerology7t556hxntqNo ratings yet

- Guitar Pickup Sensitivity and Amplitude Malcolm MooreDocument3 pagesGuitar Pickup Sensitivity and Amplitude Malcolm Mooremarkrichardmurad100% (1)

- SQnA Structure and Quality Adherence GuidelineDocument19 pagesSQnA Structure and Quality Adherence GuidelinerajalakshmiNo ratings yet

- IDEA - Collaborative Filtering Techniques in Recommendation SystemsDocument11 pagesIDEA - Collaborative Filtering Techniques in Recommendation SystemsSandeep RaghuwanshiNo ratings yet

- Garvin Melles and Saharon Shelah - Aut (M) Has A Large Dense Free Subgroup For Saturated MDocument10 pagesGarvin Melles and Saharon Shelah - Aut (M) Has A Large Dense Free Subgroup For Saturated MJtyhmfNo ratings yet

- Sequences of Real NumbersDocument55 pagesSequences of Real NumbersVijay ChhipaNo ratings yet

- Scilab Manual For Simulation Lab by DR Santosh Desai Instrumentation Engineering BMS College of Engineering, BangaloreDocument20 pagesScilab Manual For Simulation Lab by DR Santosh Desai Instrumentation Engineering BMS College of Engineering, BangaloreWalterCastellNo ratings yet

- Kenneth ArrowDocument11 pagesKenneth Arrowthomas555No ratings yet

- Chapter16 Econometrics Measurement Error ModelsDocument21 pagesChapter16 Econometrics Measurement Error ModelsAmaanNo ratings yet

- Chapter 6: Thermodynamics: $ 1: TemperatureDocument25 pagesChapter 6: Thermodynamics: $ 1: TemperatureMuhammad RehanNo ratings yet

- Blog PostDocument23 pagesBlog PostsunilNo ratings yet

- Upes Research Entrance Test (Ret) Syllabus For PHD ProgramsDocument70 pagesUpes Research Entrance Test (Ret) Syllabus For PHD ProgramsAnkit TiwariNo ratings yet

- Elasticity BoardworksDocument27 pagesElasticity BoardworksMurugan.SubramaniNo ratings yet

- Pipelines 2015 Recent Advances in Underground Pipe... - (Assessment and Rehabilitation II)Document271 pagesPipelines 2015 Recent Advances in Underground Pipe... - (Assessment and Rehabilitation II)Irina ElinaNo ratings yet

- PC - Section 1.3 - Worksheet PDFDocument2 pagesPC - Section 1.3 - Worksheet PDFAnabbNo ratings yet

- Tutorial SantuBabaTricksDocument64 pagesTutorial SantuBabaTricksArvsrv100% (14)

- Aspen Plus ReformerDocument134 pagesAspen Plus ReformerIbrahim RagabNo ratings yet

- Mini DictionaryDocument2 pagesMini DictionaryJames Clarenze VarronNo ratings yet

- 2.9 Week Summary and Graded Assessments - Week 2 - Time Value of Money - Corporate Finance - EdxDocument6 pages2.9 Week Summary and Graded Assessments - Week 2 - Time Value of Money - Corporate Finance - EdxDepanjan ChowdhuryNo ratings yet

- Biomedical Engineering - Revised - Handbook 082015Document37 pagesBiomedical Engineering - Revised - Handbook 082015Teja GuttiNo ratings yet