Professional Documents

Culture Documents

COA-chapter 3 - Assembly Language

Uploaded by

Desyilal0 ratings0% found this document useful (0 votes)

36 views49 pagescomputer organization and architecture power point for unifying concepts visualized at the specified level of accuracy for most students that are in a close relationship with the behavior and operating of computer systems involving core concepts under the likelihood of theorists.

Original Title

COA-chapter 3_Assembly Language

Copyright

© © All Rights Reserved

Available Formats

PPT, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Documentcomputer organization and architecture power point for unifying concepts visualized at the specified level of accuracy for most students that are in a close relationship with the behavior and operating of computer systems involving core concepts under the likelihood of theorists.

Copyright:

© All Rights Reserved

Available Formats

Download as PPT, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

36 views49 pagesCOA-chapter 3 - Assembly Language

Uploaded by

Desyilalcomputer organization and architecture power point for unifying concepts visualized at the specified level of accuracy for most students that are in a close relationship with the behavior and operating of computer systems involving core concepts under the likelihood of theorists.

Copyright:

© All Rights Reserved

Available Formats

Download as PPT, PDF, TXT or read online from Scribd

You are on page 1of 49

Computer Organization and Architectures

CoSc2021

Chapter Three: Assembly level Machine organization

Class Lecture

February 15, 2023

1

CoSc2021- Computer Organization and

Architectures HU Department of CS

The Computer System

At a top level, a computer consists : CPU , memory and I/O components, with one or more

modules of each type. These components are interconnected by buses.

System Buses : Interconnecting Basic Components

Computer Components

The von Neumann architecture is based on three key concepts:

• Data and instructions are stored in a single read-write memory

• The contents of this memory are addressable by location, without regard to the type of

data contained there

• Execution occurs in a sequential fashion (unless explicitly modified) from one

instruction to the next

Two approaches to programming

• hardwired programming - constructing a configuration of hardware logic components

to perform a particular set of arithmetic and logic operations on a set of data

• software - a sequence of codes or instructions, each of which supply the necessary

control signals to a general-purpose configuration of control and logic functions (which

may themselves be hardwired programs)

February 15, 2023 2

CoSc2021- Computer Organization

and Architectures

Computer Components (cont…)

Other components needed

I/O Components - a means to:

accept data and instructions in some form, and convert to an internal form of

signals report results

Main memory

distinguished from external storage/peripherals

a place to temporarily store both:

instructions - data interpreted as codes for generating control signals

data - data upon which computations are performed

Interactions among Computer Components

Memory Address Register – specifies address for next read or write

Memory Buffer Register – contains data to be written into or receives data read

from memory

I/O address register - specifies a particular I/O device

I/O buffer register - used for exchange of data between an I/O module and

CPU (or memory)

February 15, 2023 3

CoSc2021- Computer Organization

and Architectures

Computer Components (cont…)

Memory module - a set of locations with sequentially numbered addresses each

holds a binary number that can be either an instruction or data.

February 15, 2023 4

CoSc2021- Computer Organization

and Architectures

Instruction Cycle:- Fetch and Execute

A Program storing in the memory unit of the computer consists of a sequence of

instructions. The program is executed in the computer by going through a cycle for

each instruction.

Processing required for a single instruction is called an instruction cycle.

In its simplest form, instruction processing consists of two steps:

1. The processor reads ( fetches) instructions from memory one at a time

2. Executes each instruction

February 15, 2023 5

CoSc2021- Computer Organization

and Architectures

Instruction Cycle(cont…)

Fetch - CPU reads an instruction from a location in memory

Program counter (PC) register keeps track of which instruction executes next

Normally, CPU increments PC after each fetch, Unless told otherwise

Fetched instruction is loaded into the instruction register (IR)

Execute - CPU executes the instruction

May involve several operations

May utilize previously changed state of CPU and (indirectly) other devices

General categories:

CPU-Memory: Data may be transferred from CPU to memory or vice-versa

CPU-IO: Data may be transferred between CPU and an I/O module

Data Processing: CPU may perform some arithmetic or logic operation on the

data

Control: An instruction may specify that the sequence of execution be altered

eg. Jump.

February 15, 2023 6

CoSc2021- Computer Organization

and Architectures

Characteristics of a Hypothetical Machine

(a) Instruction format

(b) Integer format

(c) Internal CPU registers

Program counter (PC) _ Address of instruction

Instruction register (IR) _ Instruction being executed

Accumulator (AC) _ Temporary storage

(d) Partial list of opcodes

0001 _ Load AC from memory

0010 _ Store AC to memory

0101 _ Add to AC from memory

February 15, 2023 7

CoSc2021- Computer Organization

and Architectures

Example of Program Execution (contents of memory and registers in

hexadecimal)

February 15, 2023 8

CoSc2021- Computer Organization

and Architectures

Three instructions, which can be described as three fetch and three execute

cycles, are required:

1. The PC contains 300, the address of the first instruction. This instruction (the value 1940 in

hexadecimal) is loaded into the instruction register IR and the PC is incremented. Note that

this process involves the use of a memory address register (MAR) and a memory buffer register

(MBR). For simplicity, these intermediate registers are ignored.

2. The first 4 bits (first hexadecimal digit) in the IR indicate that the AC is to be loaded. The

remaining 12 bits (three hexadecimal digits) specify the address (940) from which data are to

be loaded.

3. The next instruction (5941) is fetched from location 301 and the PC is incremented.

4. The old contents of the AC and the contents of location 941 are added and the result is stored in

the AC.

5. The next instruction (2941) is fetched from location 302 and the PC is incremented.

6. The contents of the AC are stored in location 941.

February 15, 2023 9

CoSc2021- Computer Organization

and Architectures

Instruction Cycle State

The execution cycle for a particular instruction may involve more than one reference to

memory. Also, instead of memory references, an instruction may specify an I/O operation.

The states can be described as follows:

Instruction address calculation (iac): Determine the address of the next instruction to be

executed. This involves adding a fixed number to the address of the previous instruction

Instruction fetch (if): Read instruction from its memory location into the processor.

Instruction operation decoding (iod): Analyze instruction to determine type of operation to

be performed and operand(s) to be used.

Operand address calculation (oac): If the operation involves reference to an operand in

memory or available via I/O, then determine the address of the operand.

Operand fetch (of): Fetch the operand from memory or read it in from I/O.

Data operation (do): Perform the operation indicated in the instruction.

Operand store (os): Write the result into memory or out to I/O.

February 15, 2023 10

CoSc2021- Computer Organization

and Architectures

Instruction Cycle State Diagram

States in the upper part involve an exchange between the processor and either memory or an

I/O module.

States in the lower part of the diagram involve only internal processor operations.

The oac state appears twice, because an instruction may involve a read, a write, or both.

However, the action performed during that state is fundamentally the same in both cases, and so

only a single state identifier is needed.

February 15, 2023 11

CoSc2021- Computer Organization

and Architectures

Interrupts

Interrupts are the mechanism by which other modules (e.g. I/O, memory)

may interrupt the normal processing of the processor

Classes of Interrupts

Program :- Generated by some condition that occurs as a result of an instruction

execution, such as arithmetic overflow, division by zero, attempt to execute an

illegal machine instruction, or reference outside a user’s allowed memory space.

Timer :- Generated by a timer within the processor. This allows the operating

system to perform certain functions on a regular basis.

Used in pre-emptive multi-tasking

I/O :- Generated by an I/O controller to signal normal completion of an operation or

to signal a variety of error conditions.

Hardware failure:- Generated by a failure such as power failure or memory parity

error.

Interrupts are provided primarily as a way to improve processing efficiency.

For example, most external devices are much slower than the processor.

February 15, 2023 12

CoSc2021- Computer Organization

and Architectures

Program Flow Control without and with Interrupts

February 15, 2023 13

CoSc2021- Computer Organization

and Architectures

Interrupts and the interrupt cycle

With interrupts, the processor can be engaged in executing other instructions while an

I/O operation is in progress.

To accommodate interrupts, an interrupt cycle is added to the instruction cycle

Processor checks for interrupt

o Indicated by an interrupt signal

If no interrupts are pending the processor proceeds to the fetch cycle and fetches the

next instruction of the current program

If interrupt pending:

o It suspends execution of the current program being executed and saves its context. This

means saving the address of the next instruction to be executed (current contents of the PC)

and any other data relevant to the processor’s current activity.

o Set PC(program counter) to start address of interrupt handler routine

o Process interrupt

o Restore context and continue interrupted program

February 15, 2023 14

CoSc2021- Computer Organization

and Architectures

Transfer of Control via Interrupts

The user program does not have to contain any special code to accommodate

interrupts; the processor and the operating system are responsible for suspending the user

program and then resuming it at the same point.

February 15, 2023 15

CoSc2021- Computer Organization

and Architectures

Instruction Cycle with Interrupts

Fetch :- read next instruction from memory into CPU

Execute :- Interpret the opcode and perform the indicated operation

Interrupt :- if interrupts are enabled and one has occurred, save the current

process state and service the interrupt

February 15, 2023 16

CoSc2021- Computer Organization

and Architectures

Program Timing Short I/O Wait

February 15, 2023 17

CoSc2021- Computer Organization

and Architectures

Program Timing Long I/O Wait

February 15, 2023 18

CoSc2021- Computer Organization

and Architectures

Instruction Cycle (with Interrupts) - State Diagram

February 15, 2023 19

CoSc2021- Computer Organization

and Architectures

Multiple Interrupts

Two approaches can be taken to dealing with multiple interrupts.

a) Disable interrupts :- means that the processor can and will ignore that interrupt

request signal.

If an interrupt occurs during this time, it generally remains pending and will be

checked by the processor after the processor has enabled interrupts.

when a user program is executing and an interrupt occurs, interrupts are disabled

immediately. After the interrupt handler routine completes, interrupts are enabled

before resuming the user program, and the processor checks to see if additional

interrupts have occurred.

This approach is nice and simple, as interrupts are handled in strict sequential order.

The drawback to this approach is that it does not take into account relative priority

or time-critical needs.

b) Define priorities:-Low priority interrupts can be interrupted by higher priority

interrupts

When higher priority interrupt has been processed, processor returns to previous

interrupt

February 15, 2023 20

CoSc2021- Computer Organization

and Architectures

Multiple Interrupts - Sequential

Sequential interrupt processing:- it is nice and simple, as interrupts are handled

in strict sequential order

February 15, 2023 21

CoSc2021- Computer Organization

and Architectures

Multiple Interrupts – Nested

Nested interrupt processing:- to define priorities for interrupts and to allow an

interrupt of higher priority to cause a lower-priority interrupt handler to be itself

interrupted

February 15, 2023 22

CoSc2021- Computer Organization

and Architectures

Time Sequence of Multiple Interrupts

February 15, 2023 23

CoSc2021- Computer Organization

and Architectures

Interconnection Structures

A computer consists of a set of components or modules of three basic types

(processor, memory, I/O) that communicate with each other.

All the units must be connected

There must be paths for connecting the modules.

The collection of paths connecting the various modules is called the interconnection

structure.

The design of this structure will depend on the exchanges that must be made among

modules

Different type of connection for different type of unit

Memory

Input/Output

CPU

February 15, 2023 24

CoSc2021- Computer Organization

and Architectures

Computer Modules

February 15, 2023 25

CoSc2021- Computer Organization

and Architectures

Computer Modules(cont…)

Memory Connection

Receives and sends data

Receives addresses (of locations)

Receives control signals

• Read

• Write

• Timing

CPU Connection

Reads instruction and data

Writes out data (after processing)

Sends control signals to other units

Receives (& acts on) interrupts

February 15, 2023 26

CoSc2021- Computer Organization

and Architectures

Computer Modules(cont…)

Input/Output Connection

Similar to memory from computer’s viewpoint

Output

o Receive data from computer

o Send data to peripheral

Input

o Receive data from peripheral

o Send data to computer

Receive control signals from computer

Send control signals to peripherals

o e.g. spin disk

Receive addresses from computer

o e.g. port number to identify peripheral

Send interrupt signals (control)

February 15, 2023 27

CoSc2021- Computer Organization

and Architectures

Computer Modules(cont…)

The preceding list defines the data to be exchanged. The interconnection structure

must support the following types of transfers:

Memory to processor: The processor reads an instruction or a unit of data from

memory.

Processor to memory: The processor writes a unit of data to memory.

I/O to processor: The processor reads data from an I/O device via an I/O module.

Processor to I/O: The processor sends data to the I/O device.

I/O to or from memory: For these two cases, an I/O module is allowed to exchange

data directly with memory, without going through the processor, using Direct

Memory Access (DMA).

February 15, 2023 28

CoSc2021- Computer Organization

and Architectures

Bus Interconnection

A bus is a communication pathway connecting two or more devices.

A key characteristic of a bus is that it is a shared transmission medium.

Multiple devices connect to the bus, and a signal transmitted by any one device is

available for reception by all other devices attached to the bus.

If two devices transmit during the same time period, their signals will overlap and

become garbled. Thus, only one device at a time can successfully transmit.

A bus consists of multiple communication pathways, or lines.

A bus that connects major computer components (processor, memory, I/O) is called a

system bus.

There are many different bus designs, on any bus the lines can be classified into three

functional groups :- data, address, and control lines.

In addition, there may be power distribution lines that supply power to the attached

modules

February 15, 2023 29

CoSc2021- Computer Organization

and Architectures

System bus(cont….)

1. Data Bus:- Carries data

• Remember that there is no difference between “data” and “instruction” at this

level

• Width is a key determinant of performance 8, 16, 32, 64 bit

2. Address bus:- Identify the source or destination of data

• e.g. CPU needs to read an instruction (data) from a given location in memory

• Bus width determines maximum memory capacity of system

• e.g. 8080 has 16 bit address bus giving 64k address space

3. Control Bus:- Control and timing information

• Memory read/write signal

• Interrupt request

• Clock signals

February 15, 2023 30

CoSc2021- Computer Organization

and Architectures

Bus Interconnection Scheme

If one module wishes to send data to another , it must do two things:

(1) obtain the use of the bus, and (2) transfer data via the bus.

If one module wishes to request data from another module, it must (1) obtain the use of the

bus, and (2) transfer a request to the other module over the appropriate control and address lines.

It must then wait for that second module to

send the data.

February 15, 2023 31

CoSc2021- Computer Organization

and Architectures

Physical Realization of Bus Architecture

Physically, the system bus is actually a number of parallel electrical conductors.

In the following example, the bus consists of two vertical columns of conductors. At

regular intervals along the columns, there are attachment points in the form of slots that

extend out horizontally to support a printed circuit board.

February 15, 2023 32

CoSc2021- Computer Organization

and Architectures

Single Bus Problems

Lots of devices on one bus leads to:

Propagation delays:

• The more devices attached to the bus, the greater the bus length and hence the

greater the propagation delay. This delay determines the time it takes for

devices to coordinate the use of the bus. When control of the bus passes from

one device to another frequently, these propagation delays can noticeably

affect performance

• The bus may become a bottleneck as the aggregate data transfer demand

approaches the capacity of the bus. This problem can be countered to some

extent by increasing the data rate that the bus can carry and by using wider

buses (e.g., increasing the data bus from 32 to 64 bits). However, because the

data rates generated by attached devices (e.g., graphics and video controllers,

network interfaces) are growing rapidly, this is a race that a single bus is

ultimately destined to lose.

• Most systems use multiple buses to overcome these problems

February 15, 2023 33

CoSc2021- Computer Organization

and Architectures

Traditional (ISA) (with cache)

February 15, 2023 34

CoSc2021- Computer Organization

and Architectures

High Performance Bus

February 15, 2023 35

CoSc2021- Computer Organization

and Architectures

Elements of Bus Design Issues

Bus designers need to consider several issues to get the desired cost-performance

tradeoff. here is a list of the bus design issues:

Bus Width: Bus width refers to the data and address bus widths. System

performance improves with a wider data bus as we can move more bytes in parallel.

We increase the addressing capacity of the system by adding more address lines.

Bus Type: there are two basic types of buses: dedicated and multiplexed.

Bus Operations: Bus systems support several types of operations to transfer data.

These include the read, write, block transfer, read-modify-writ, and interrupt.

Bus Arbitration: Bus arbitration can be done in one of two ways: centralized or

distributed.

Bus Timing: buses can be designed as either synchronous or asynchronous.

February 15, 2023 36

CoSc2021- Computer Organization

and Architectures

Bus Types

Bus lines can be separated into two generic types:

a)Dedicated:- Separate data & address lines

b)Multiplexed:- Shared lines

• For example, address and data information may be transmitted over the same set

of lines using an Address Valid control line.

• Address valid or data valid control line

• Advantage - is the use of fewer lines, which saves space and, usually, cost.

• Disadvantages

• More complex circuitry is needed within each module.

• There is a potential reduction in performance because certain events that share the

same lines cannot take place in parallel.

February 15, 2023 37

CoSc2021- Computer Organization

and Architectures

Bus Arbitration

• In all but the simplest systems, more than one module may need control of the bus.

• For example, an I/O module may need to read or write directly to memory, without

sending the data to the processor.

• Because only one unit at a time can successfully transmit over the bus, some method

of arbitration is needed.

• The methods can be classified as being either centralized or distributed.

a) centralized scheme:- a single hardware device, referred to as a bus controller or

arbiter, is responsible for allocating time on the bus.

• The device may be a separate module or part of the processor(CPU)

a) distributed scheme:- there is no central controller. Rather, each module contains

access control logic and the modules act together to share the bus.

With both methods of arbitration, the purpose is to designate one device, either the

processor or an I/O module, as master. The master may then initiate a data transfer

(e.g., read or write) with some other device, which acts as slave for this particular

exchange.

February 15, 2023 38

CoSc2021- Computer Organization

and Architectures

Timing

Timing refers to the way in which events are coordinated on the bus.

Buses use either synchronous timing or asynchronous timing.

Synchronous

o Events determined by clock signals

o Control Bus includes clock line

o A single 1-0 is a bus cycle

o All devices can read clock line

o Usually sync on leading edge

o Usually a single cycle for an event

Synchronous timing is simpler to implement and test. However, it is less

flexible than asynchronous timing. Because all devices on a synchronous bus are

tied to a fixed clock rate, the system cannot take this advantage in device

performance.

With asynchronous timing, a mixture of slow and fast devices, using older

and newer technology, can share a bus.

February 15, 2023 39

CoSc2021- Computer Organization

and Architectures

Synchronous Timing Diagram

February 15, 2023 40

CoSc2021- Computer Organization

and Architectures

Asynchronous Timing – Read Diagram

Asynchronous timing :- the occurrence of one event on a bus follows and depends on the

occurrence of a previous event.

February 15, 2023 41

CoSc2021- Computer Organization

and Architectures

Asynchronous Timing – Write Diagram

Shows a simple asynchronous write operation. In this case, the master places the

data on the data line at the same time that is puts signals on the status and address lines.

February 15, 2023 42

CoSc2021- Computer Organization

and Architectures

PCI (Peripheral Component Interconnection) Bus

It is a popular high-bandwidth, processor-independent bus that can function as a

mezzanine or peripheral bus.

Compared with other common bus specifications, PCI delivers better system

performance for high-speed I/O subsystems (e.g., graphic display adapters, network

interface controllers, disk controllers, and so on).

The current standard allows the use of up to 64 data lines at 66 MHz, for a raw

transfer rate of 528 MByte/s, or 4.224 Gbps. But it is not just a high speed that makes

PCI attractive.

PCI is specifically designed to meet economically the I/O requirements of modern

systems; it requires very few chips to implement and supports other buses attached to

the PCI bus.

Intel released to public domain

32 or 64 bit

50 lines

February 15, 2023 43

CoSc2021- Computer Organization

and Architectures

PCI Bus Lines (required)

These are divided into the following functional groups:

System pins: Include the clock and reset pins.

Address and data pins: Include 32 lines that are time multiplexed for addresses and

data. The other lines in this group are used to interpret and validate the signal lines that

carry the addresses and data.

Interface control pins: Control the timing of transactions and provide coordination

among initiators and targets.

Arbitration pins: Unlike the other PCI signal lines, these are not shared lines. Rather,

each PCI master has its own pair of arbitration lines that connect it directly to the PCI

bus arbiter.

Error reporting pins: Used to report parity and other errors.

February 15, 2023 44

CoSc2021- Computer Organization

and Architectures

PCI Bus Lines (Optional)

The PCI specification defines 51 optional signal lines divided into the following

functional groups

•Interrupt pins: These are provided for PCI devices that must generate requests for

service. As with the arbitration pins, these are not shared lines.

Each PCI device has its own interrupt line or lines to an interrupt controller.

•Cache support pins: These pins are needed to support a memory on PCI that can be

cached in the processor or another device.

•64-bit bus extension pins: Include 32 lines that are time multiplexed for addresses and

data and that are combined with the mandatory address/data lines to form a 64-bit

address/data bus. Other lines in this group are used to interpret and validate the signal

lines that carry the addresses and data. Finally, there are two lines that enable two PCI

devices to agree to the use of the 64-bit capability.

• JTAG/boundary scan pins: For testing procedures defined in IEEE Standard 1149.1.

February 15, 2023 45

CoSc2021- Computer Organization

and Architectures

PCI Commands

Bus activity occurs in the form of transactions between an initiator, or master and a

target.

When a bus master acquires control of the bus, it determines the type of transaction

that will occur next.

Determine type of transaction

e.g. I/O read/write

Address phase

One or more data phases

February 15, 2023 46

CoSc2021- Computer Organization

and Architectures

PCI Read Timing Diagram

February 15, 2023 47

CoSc2021- Computer Organization

and Architectures

PCI Bus Arbiter

February 15, 2023 48

CoSc2021- Computer Organization

and Architectures

PCI Bus Arbitration

February 15, 2023 49

CoSc2021- Computer Organization

and Architectures

You might also like

- Arch&org - Chapter 3Document14 pagesArch&org - Chapter 3Adam Lawrence TolentinoNo ratings yet

- CS8493 OPERATING SYSTEM 1Document36 pagesCS8493 OPERATING SYSTEM 1alexb072002No ratings yet

- Computer Architecture CSC 303Document36 pagesComputer Architecture CSC 303Gboti100% (1)

- KTU CST202 Computer Organization Module 1Document22 pagesKTU CST202 Computer Organization Module 1Akhil KrishnaNo ratings yet

- Introduction to Computer Organization Components and FunctionsDocument14 pagesIntroduction to Computer Organization Components and FunctionsAmey KurdikarNo ratings yet

- Lecture Note - Top Level View of ComputerDocument6 pagesLecture Note - Top Level View of Computertesfu zewduNo ratings yet

- KTU - CST202 - Computer Organization and ArchitectureDocument22 pagesKTU - CST202 - Computer Organization and ArchitectureJoel K SanthoshNo ratings yet

- The Computer System: Function & InterconnectionsDocument46 pagesThe Computer System: Function & Interconnectionsjulius opolotNo ratings yet

- Computer Org - L4Document36 pagesComputer Org - L4محمد العموديNo ratings yet

- Computer Organization and Assembly Language: Lecture 1 & 2 Introduction and BasicsDocument33 pagesComputer Organization and Assembly Language: Lecture 1 & 2 Introduction and Basicsdarwinvargas2011No ratings yet

- Intisar'sComputer Organization and Architecture NotesDocument110 pagesIntisar'sComputer Organization and Architecture NotesRajput RishavNo ratings yet

- Cpu OrganizationDocument5 pagesCpu OrganizationNavis Nayagam100% (2)

- Computer System Architecture Overview: Functions, Components & InterconnectionDocument40 pagesComputer System Architecture Overview: Functions, Components & InterconnectionTawki BakiNo ratings yet

- CA Notes Chapter1Document28 pagesCA Notes Chapter1Nithyan NithyaNo ratings yet

- CompArch 01 IntroductionDocument80 pagesCompArch 01 Introductionmilkii kasayeNo ratings yet

- Assignment Analysis: Computer Architecture FundamentalsDocument10 pagesAssignment Analysis: Computer Architecture FundamentalsRoohul BayanNo ratings yet

- Lecture 5 - CPU DesignDocument20 pagesLecture 5 - CPU Designnoberth nikombolweNo ratings yet

- COA Mod 1 UpdatedDocument22 pagesCOA Mod 1 UpdatedMirror LeechNo ratings yet

- 3.0 Central Processing Unit: ITE 1922 - ICT ApplicationsDocument7 pages3.0 Central Processing Unit: ITE 1922 - ICT ApplicationsShine InstituteNo ratings yet

- Week 3 - The Processing Unit and Input Output OrganizationsDocument18 pagesWeek 3 - The Processing Unit and Input Output OrganizationsGame AccountNo ratings yet

- Digital Electronics & Computer OrganisationDocument17 pagesDigital Electronics & Computer Organisationabhishek125No ratings yet

- computer organization Questions and answersDocument14 pagescomputer organization Questions and answerspreethivmadappaNo ratings yet

- Von Neumann model and fetch-decode cycleDocument1 pageVon Neumann model and fetch-decode cyclePatuan TampuolonNo ratings yet

- Computer Organization and Architecture: William StallingsDocument78 pagesComputer Organization and Architecture: William StallingsNITHIYA PAUL 1847244No ratings yet

- Computer Organization 2022-23Document156 pagesComputer Organization 2022-23Kakashi Hatake100% (1)

- Computer Architecture Assignment AnalysisDocument15 pagesComputer Architecture Assignment AnalysisRoohul BayanNo ratings yet

- Computer OrgnisationDocument138 pagesComputer OrgnisationmadhuNo ratings yet

- The Basic Architecture of Computer SystemDocument30 pagesThe Basic Architecture of Computer SystemAnnie GloryNo ratings yet

- Computer Systems: Huong NguyenDocument19 pagesComputer Systems: Huong NguyenDoski MorebundleNo ratings yet

- Component of A Digital ComputerDocument15 pagesComponent of A Digital Computerreginaamondi133No ratings yet

- Computer System Hardware ComponentsDocument10 pagesComputer System Hardware ComponentsalexpiusNo ratings yet

- Sec 1.3.2 Computer Architecture & Fetch Execute Cycle: Computer Science 2210 With Majid TahirDocument9 pagesSec 1.3.2 Computer Architecture & Fetch Execute Cycle: Computer Science 2210 With Majid TahirFiyazul HaqueNo ratings yet

- Co Module1Document22 pagesCo Module1Ashika RajNo ratings yet

- COA Chapter 1 NotesDocument14 pagesCOA Chapter 1 NotesAmitesh ki class For engineeringNo ratings yet

- Co-2 - CoaDocument46 pagesCo-2 - CoaDAVU REVANTH NAGNo ratings yet

- Computer Organization & Architecture: Instructor Engr. Zeeshan RazaDocument35 pagesComputer Organization & Architecture: Instructor Engr. Zeeshan RazaMeena ShahNo ratings yet

- Module 1 Chapter 1 Introduction to Basic Computer Structure and CPU Instruction ExecutionDocument24 pagesModule 1 Chapter 1 Introduction to Basic Computer Structure and CPU Instruction Executionyashu JNo ratings yet

- Jerome S. Del Castillo: BS ECE: 17-21514 Week 8:: Figure 1. Fetch-Execute CycleDocument4 pagesJerome S. Del Castillo: BS ECE: 17-21514 Week 8:: Figure 1. Fetch-Execute CycleJeromeDelCastilloNo ratings yet

- Chapter 5Document53 pagesChapter 5binaboss24No ratings yet

- Computer Organization & Architecture: Instructor Engr. Zeeshan RazaDocument33 pagesComputer Organization & Architecture: Instructor Engr. Zeeshan RazaRana Gulraiz HassanNo ratings yet

- Computer Organization and Architecture Module 1Document46 pagesComputer Organization and Architecture Module 1Assini Hussain100% (1)

- Computer Organization and Architecture Module 1 (Kerala University) NotesDocument30 pagesComputer Organization and Architecture Module 1 (Kerala University) NotesAssini Hussain100% (11)

- Chapter 2 Basic Computer OrganisationDocument5 pagesChapter 2 Basic Computer OrganisationHimanshu GamingNo ratings yet

- 2 Von Neumann Architecture: Registers. The Control Unit Determines The Order in Which Instructions Should Be Executed andDocument66 pages2 Von Neumann Architecture: Registers. The Control Unit Determines The Order in Which Instructions Should Be Executed andLoser IdiotNo ratings yet

- Control UnitDocument2 pagesControl UnitFarhan CkNo ratings yet

- 7 ProcessorDocument5 pages7 ProcessorMuhammad HassanNo ratings yet

- Computer Architecture and Organization FundamentalsDocument13 pagesComputer Architecture and Organization FundamentalsYassin umetaNo ratings yet

- Cpu and Its Working MechanismDocument9 pagesCpu and Its Working MechanismBais JumaniNo ratings yet

- Computer Organisation ExplainedDocument39 pagesComputer Organisation Explainedarunbalaji2020No ratings yet

- Puter OrganisationDocument27 pagesPuter Organisationluynaaaaa75No ratings yet

- Activity 1 EE60Document5 pagesActivity 1 EE60Jayvon Flores CampañaNo ratings yet

- Parisutham Institute of Technology & Science, Thanjavur - Embedded System Memory ManagementDocument6 pagesParisutham Institute of Technology & Science, Thanjavur - Embedded System Memory ManagementgallantprakashNo ratings yet

- COA Fall 2022 Lec01Document23 pagesCOA Fall 2022 Lec01Abdallateef ShohdyNo ratings yet

- Module 3Document34 pagesModule 3DennisNo ratings yet

- Chapter - 2 Computer Architecture Notes EnglishDocument4 pagesChapter - 2 Computer Architecture Notes EnglishAshish SharmaNo ratings yet

- Module 1 of Computer OrganizationDocument27 pagesModule 1 of Computer OrganizationNimmymolManuelNo ratings yet

- Computer Organization and ArchitectureDocument48 pagesComputer Organization and Architecturefreedom mutepfeNo ratings yet

- ComponentsDocument5 pagesComponentsderry6271No ratings yet

- All Chapters (Data Starcture)Document205 pagesAll Chapters (Data Starcture)DesyilalNo ratings yet

- Data Structure and AlgoritmsDocument86 pagesData Structure and AlgoritmsasratNo ratings yet

- Chapter 3 - Simple Searching and SortingDocument47 pagesChapter 3 - Simple Searching and SortingDesyilalNo ratings yet

- Data Structure and AlgoritmsDocument86 pagesData Structure and AlgoritmsasratNo ratings yet

- Chapter OneDocument44 pagesChapter OneDesyilalNo ratings yet

- Chapter 4.1 - ListDocument47 pagesChapter 4.1 - ListDesyilalNo ratings yet

- Chapter 6 - RecursionDocument37 pagesChapter 6 - RecursionDesyilalNo ratings yet

- Chapter 2 - Elementary Searching and Sorting AlgorithmsDocument39 pagesChapter 2 - Elementary Searching and Sorting AlgorithmsDesyilalNo ratings yet

- Theory of AlgorithmsDocument57 pagesTheory of AlgorithmsDesyilalNo ratings yet

- DsaDocument112 pagesDsadgbooklover0766571100% (3)

- Chapter 1Document18 pagesChapter 1DesyilalNo ratings yet

- Dsa 1Document55 pagesDsa 1DesyilalNo ratings yet

- COA MODULE - Memory OrganizationDocument43 pagesCOA MODULE - Memory OrganizationDesyilalNo ratings yet

- Introduction To DatastruactureDocument22 pagesIntroduction To DatastruactureDesyilalNo ratings yet

- COA MODULE Input Output OrganizationDocument40 pagesCOA MODULE Input Output OrganizationDesyilalNo ratings yet

- Chapter3 DCDocument22 pagesChapter3 DCDesyilalNo ratings yet

- Chpater 2 Basic in Java ProgrammingDocument60 pagesChpater 2 Basic in Java ProgrammingDesyilalNo ratings yet

- COA CH 1Document33 pagesCOA CH 1DesyilalNo ratings yet

- Chapter 1 Digital Systems and Binary NumbersDocument40 pagesChapter 1 Digital Systems and Binary NumbersDesyilalNo ratings yet

- Chapter One - IntroductionDocument33 pagesChapter One - IntroductionDesyilalNo ratings yet

- Chapter 1 Introduction To Computer Organization and ArchitectureDocument58 pagesChapter 1 Introduction To Computer Organization and ArchitectureDesyilalNo ratings yet

- Chapter TwoDocument23 pagesChapter TwoDesyilalNo ratings yet

- Chapter 2 - Lecture Data RepresentationDocument34 pagesChapter 2 - Lecture Data RepresentationDesyilalNo ratings yet

- Adama STU Java Final Exam Object-Oriented ProgrammingDocument8 pagesAdama STU Java Final Exam Object-Oriented ProgrammingDesyilalNo ratings yet

- Ma Unit 2Document24 pagesMa Unit 2DesyilalNo ratings yet

- Chapter OneDocument22 pagesChapter OneDesyilalNo ratings yet

- Chapter One - IntroductionDocument56 pagesChapter One - IntroductionDesyilalNo ratings yet

- Chapter ThreeDocument10 pagesChapter ThreeDesyilalNo ratings yet

- Recurrence RelationDocument18 pagesRecurrence RelationDesyilalNo ratings yet

- CXO 7050 Rev 14.3.13 PDFDocument1 pageCXO 7050 Rev 14.3.13 PDFrajaramghoshNo ratings yet

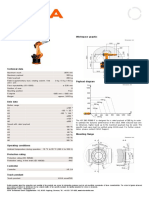

- KR 280 R3080 F technical specificationsDocument1 pageKR 280 R3080 F technical specificationsDorobantu CatalinNo ratings yet

- Weekly TestDocument12 pagesWeekly Testrossana rondaNo ratings yet

- Impromtu Speech Covid 19Document7 pagesImpromtu Speech Covid 19ESWARY A/P VASUDEVAN MoeNo ratings yet

- Listado 2 4ghzDocument4 pagesListado 2 4ghzRogerNo ratings yet

- Vivekananda's Role as Revivalist Reformer and His Ideas of Equality and Spiritual RevolutionDocument2 pagesVivekananda's Role as Revivalist Reformer and His Ideas of Equality and Spiritual RevolutionMartin VanlalhlimpuiaNo ratings yet

- Kuruk Etra:: Dharma-K Etra Śalya-ParvaDocument1 pageKuruk Etra:: Dharma-K Etra Śalya-ParvaRavinder Khullar100% (1)

- The University of QueenslandDocument2 pagesThe University of Queenslandimmanuel nauk elokpereNo ratings yet

- Google Wakeword Detection 1 PDFDocument5 pagesGoogle Wakeword Detection 1 PDFÖzgür Bora GevrekNo ratings yet

- 2 Corinthians: Workbook OnDocument18 pages2 Corinthians: Workbook OnJhon Ray OtañesNo ratings yet

- Saberry ® - Cosmeceutical Applications of SaberryDocument2 pagesSaberry ® - Cosmeceutical Applications of SaberryGopalaKrishnan SivaramanNo ratings yet

- WRBS Quarter 1 Modules WEEK-1-8Document32 pagesWRBS Quarter 1 Modules WEEK-1-8Sir Kindred VillaruzNo ratings yet

- How English Works - A Grammar Handbook With Readings - Answer Key PDFDocument38 pagesHow English Works - A Grammar Handbook With Readings - Answer Key PDFAlessio Bocco100% (1)

- Company Introduction PT GEADocument8 pagesCompany Introduction PT GEABegawan Half DoneNo ratings yet

- Case3: What's in A Car 1. What Kind of Research Study Should Shridhar Undertake? Define TheDocument2 pagesCase3: What's in A Car 1. What Kind of Research Study Should Shridhar Undertake? Define TheRoshan kumar Rauniyar0% (3)

- Excerpts From The Way of The Samurai (Shīdo) : Primary Source Document With Questions (DBQS)Document2 pagesExcerpts From The Way of The Samurai (Shīdo) : Primary Source Document With Questions (DBQS)Valeria MontalvaNo ratings yet

- Dip HIV Man (SA) Past Papers - 2015 2nd Semester 24-1-2017Document2 pagesDip HIV Man (SA) Past Papers - 2015 2nd Semester 24-1-2017matenten100% (1)

- Deutz td2011 l04w Service Manual PDFDocument7 pagesDeutz td2011 l04w Service Manual PDFLuis Carlos RamosNo ratings yet

- Inergen Order Data SheetDocument31 pagesInergen Order Data Sheetkarim3samirNo ratings yet

- The Bourne Identity ReviewDocument3 pagesThe Bourne Identity ReviewBoldizsár Zeyk AnnaNo ratings yet

- PDF DocumentDocument10 pagesPDF DocumentNIKHIL DASARINo ratings yet

- Review of Dr. Mark Cheng's "Prehab-Rehab 101" SeriesDocument6 pagesReview of Dr. Mark Cheng's "Prehab-Rehab 101" SeriesWilliam TortorielloNo ratings yet

- Quarter 1 - Module 1: (Traditions and Locations: The Filipino Poem (A Long History of Poetry)Document31 pagesQuarter 1 - Module 1: (Traditions and Locations: The Filipino Poem (A Long History of Poetry)Sicnarf Rolag0% (1)

- LP Lab ManuelDocument23 pagesLP Lab ManuelRavi Kumar LankeNo ratings yet

- 4 A CompiledDocument167 pages4 A CompiledArjun MiddhaNo ratings yet

- Second Travel of Rizal: Week 8 Unit 3Document22 pagesSecond Travel of Rizal: Week 8 Unit 3John Russell GasangNo ratings yet

- Technical Information No. 12 Vermicular Graphite Cast Iron: MicrostructureDocument1 pageTechnical Information No. 12 Vermicular Graphite Cast Iron: MicrostructureVelina MilevaNo ratings yet

- Template PharmaconDocument4 pagesTemplate PharmaconDanang RaharjoNo ratings yet

- Rubber Conveyor Belt Wear ResistanceDocument5 pagesRubber Conveyor Belt Wear ResistanceBelt Power LLCNo ratings yet