Professional Documents

Culture Documents

Irf 1404

Irf 1404

Uploaded by

itamar_jrOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Irf 1404

Irf 1404

Uploaded by

itamar_jrCopyright:

Available Formats

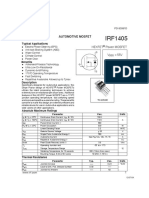

IRF1404

HEXFET

Power MOSFET

Seventh Generation HEXFET

Power MOSFETs from

International Rectifier utilize advanced processing

techniques to achieve extremely low on-resistance per

silicon area. This benefit, combined with the fast

switching speed and ruggedized device design that

HEXFET power MOSFETs are well known for, provides

the designer with an extremely efficient and reliable

device for use in a wide variety of applications including

automotive.

The TO-220 package is universally preferred for all

automotive-commercial-industrial applications at power

dissipation levels to approximately 50 watts. The low

thermal resistance and low package cost of the TO-220

contribute to its wide acceptance throughout the industry.

S

D

G

Absolute Maximum Ratings

Parameter Typ. Max. Units

R

JC

Junction-to-Case 0.45

R

CS

Case-to-Sink, Flat, Greased Surface 0.50 C/W

R

JA

Junction-to-Ambient 62

Thermal Resistance

V

DSS

= 40V

R

DS(on)

= 0.004

I

D

= 202A

Advanced Process Technology

Ultra Low On-Resistance

Dynamic dv/dt Rating

175C Operating Temperature

Fast Switching

Fully Avalanche Rated

Automotive Qualified (Q101)

Description

10/10/03

www.irf.com 1

TO-220AB

Parameter Max. Units

I

D

@ T

C

= 25C Continuous Drain Current, V

GS

@ 10V 202

I

D

@ T

C

= 100C Continuous Drain Current, V

GS

@ 10V 143 A

I

DM

Pulsed Drain Current C 808

P

D

@T

C

= 25C Power Dissipation 333 W

Linear Derating Factor 2.2 W/C

V

GS

Gate-to-Source Voltage 20 V

E

AS

Single Pulse Avalanche EnergyC 620 mJ

I

AR

Avalanche Current See Fig.12a, 12b, 15, 16 A

E

AR

Repetitive Avalanche EnergyC mJ

dv/dt Peak Diode Recovery dv/dt C 1.5 V/ns

T

J

Operating Junction and -55 to + 175

T

STG

Storage Temperature Range -55 to + 175

Soldering Temperature, for 10 seconds 300 (1.6mm from case )

C

Mounting Torque, 6-32 or M3 screw 10 lbfin (1.1Nm)

PD-91896F

IRF1404

2 www.irf.com

Parameter Min. Typ. Max. Units Conditions

V

(BR)DSS

Drain-to-Source Breakdown Voltage 40 V V

GS

= 0V, I

D

= 250A

V(BR)DSS/TJ Breakdown Voltage Temp. Coefficient 0.039 V/C Reference to 25C, I

D

= 1mA

R

DS(on)

Static Drain-to-Source On-Resistance 0.0035 0.004 V

GS

= 10V, I

D

= 121A C

V

GS(th)

Gate Threshold Voltage 2.0 4.0 V V

DS

= 10V, I

D

= 250A

g

fs

Forward Transconductance 76 S V

DS

= 25V, I

D

= 121A

20

A

V

DS

= 40V, V

GS

= 0V

250 V

DS

= 32V, V

GS

= 0V, T

J

= 150C

Gate-to-Source Forward Leakage 200 V

GS

= 20V

Gate-to-Source Reverse Leakage -200

nA

V

GS

= -20V

Q

g

Total Gate Charge 131 196 I

D

= 121A

Q

gs

Gate-to-Source Charge 36 nC V

DS

= 32V

Q

gd

Gate-to-Drain ("Miller") Charge 37 56 V

GS

= 10VC

t

d(on)

Turn-On Delay Time 17 V

DD

= 20V

t

r

Rise Time 190 I

D

= 121A

t

d(off)

Turn-Off Delay Time 46 R

G

= 2.5

t

f

Fall Time 33 R

D

= 0.2 C

Between lead,

6mm (0.25in.)

from package

and center of die contact

C

iss

Input Capacitance 5669 V

GS

= 0V

C

oss

Output Capacitance 1659 pF V

DS

= 25V

C

rss

Reverse Transfer Capacitance 223 = 1.0MHz, See Fig. 5

C

oss

Output Capacitance 6205 V

GS

= 0V, V

DS

= 1.0V, = 1.0MHz

C

oss

Output Capacitance 1467 V

GS

= 0V, V

DS

= 32V, = 1.0MHz

C

oss

eff. Effective Output Capacitance C 2249 V

GS

= 0V, V

DS

= 0V to 32V

nH

Electrical Characteristics @ T

J

= 25C (unless otherwise specified)

L

D

Internal Drain Inductance

L

S

Internal Source Inductance

S

D

G

I

GSS

ns

4.5

7.5

I

DSS

Drain-to-Source Leakage Current

Repetitive rating; pulse width limited by

max. junction temperature. (See fig. 11)

I

SD

121A, di/dt 130A/s, V

DD

V

(BR)DSS

,

T

J

175C

Notes:

Starting T

J

= 25C, L = 85H

R

G

= 25, I

AS

= 121A. (See Figure 12)

Pulse width 400s; duty cycle 2%.

S

D

G

Parameter Min. Typ. Max. Units Conditions

I

S

Continuous Source Current MOSFET symbol

(Body Diode)

showing the

ISM Pulsed Source Current integral reverse

(Body Diode) C

p-n junction diode.

V

SD

Diode Forward Voltage 1.5 V T

J

= 25C, I

S

= 121A, V

GS

= 0V C

t

rr

Reverse Recovery Time 78 117 ns T

J

= 25C, I

F

= 121A

Q

rr

Reverse RecoveryCharge 163 245 nC di/dt = 100A/s

C

t

on

Forward Turn-On Time Intrinsic turn-on time is negligible (turn-on is dominated by L

S

+L

D

)

Source-Drain Ratings and Characteristics

202

808

A

C

oss

eff. is a fixed capacitance that gives the same charging time

as C

oss

while V

DS

is rising from 0 to 80% V

DSS

Calculated continuous current based on maximum allowable

junction temperature. Package limitation current is 75A.

IRF1404

www.irf.com 3

Fig 4. Normalized On-Resistance

Vs. Temperature

Fig 2. Typical Output Characteristics Fig 1. Typical Output Characteristics

Fig 3. Typical Transfer Characteristics

1

10

100

1000

0.1 1 10 100

20s PULSE WIDTH

T = 25 C J

TOP

BOTTOM

VGS

15V

10V

8.0V

7.0V

6.0V

5.5V

5.0V

4.5V

V , Drain-to-Source Voltage (V)

I

,

D

r

a

i

n

-

t

o

-

S

o

u

r

c

e

C

u

r

r

e

n

t

(

A

)

DS

D

4.5V

1

10

100

1000

0.1 1 10 100

20s PULSE WIDTH

T = 175 C J

TOP

BOTTOM

VGS

15V

10V

8.0V

7.0V

6.0V

5.5V

5.0V

4.5V

V , Drain-to-Source Voltage (V)

I

,

D

r

a

i

n

-

t

o

-

S

o

u

r

c

e

C

u

r

r

e

n

t

(

A

)

DS

D

4.5V

10

100

1000

4 5 6 7 8 9 10 11 12

V = 25V

20s PULSE WIDTH

DS

V , Gate-to-Source Voltage (V)

I

,

D

r

a

i

n

-

t

o

-

S

o

u

r

c

e

C

u

r

r

e

n

t

(

A

)

GS

D

T = 25 C

J

T = 175 C

J

-60 -40 -20 0 20 40 60 80 100 120 140 160 180

0.0

0.5

1.0

1.5

2.0

2.5

T , Junction Temperature ( C)

R

,

D

r

a

i

n

-

t

o

-

S

o

u

r

c

e

O

n

R

e

s

i

s

t

a

n

c

e

(

N

o

r

m

a

l

i

z

e

d

)

J

D

S

(

o

n

)

V =

I =

GS

D

10V

202A

IRF1404

4 www.irf.com

Fig 8. Maximum Safe Operating Area

Fig 6. Typical Gate Charge Vs.

Gate-to-Source Voltage

Fig 5. Typical Capacitance Vs.

Drain-to-Source Voltage

Fig 7. Typical Source-Drain Diode

Forward Voltage

0 50 100 150 200

0

4

8

12

16

20

Q , Total Gate Charge (nC)

V

,

G

a

t

e

-

t

o

-

S

o

u

r

c

e

V

o

l

t

a

g

e

(

V

)

G

G

S

FOR TEST CIRCUIT

SEE FIGURE

I =

D

13

121A

V = 20V

DS

V = 32V

DS

0.1

1

10

100

1000

0.0 0.5 1.0 1.5 2.0 2.5 3.0 3.5

V ,Source-to-Drain Voltage (V)

I

,

R

e

v

e

r

s

e

D

r

a

i

n

C

u

r

r

e

n

t

(

A

)

SD

S

D

V = 0 V

GS

T = 25 C

J

T = 175 C

J

1

10

100

1000

10000

1 10 100

OPERATION IN THIS AREA LIMITED

BY R

DS(on)

Single Pulse

T

T

= 175 C

= 25 C

J

C

V , Drain-to-Source Voltage (V)

I

,

D

r

a

i

n

C

u

r

r

e

n

t

(

A

)

I

,

D

r

a

i

n

C

u

r

r

e

n

t

(

A

)

DS

D

10us

100us

1ms

10ms

1 10 100

V

DS

, Drain-to-Source Voltage (V)

0

2000

4000

6000

8000

10000

C

,

C

a

p

a

c

i

t

a

n

c

e

(

p

F

)

Coss

Crss

Ciss

V

GS

= 0V, f = 1 MHZ

C

iss

= C

gs

+ C

gd

, C

ds

SHORTED

C

rss

= C

gd

C

oss

= C

ds

+ C

gd

IRF1404

www.irf.com 5

Fig 11. Maximum Effective Transient Thermal Impedance, Junction-to-Case

Fig 9. Maximum Drain Current Vs.

Case Temperature

Fig 10a. Switching Time Test Circuit

V

DS

90%

10%

V

GS

t

d(on)

t

r

t

d(off)

t

f

Fig 10b. Switching Time Waveforms

V

DS

Pulse Width 1 s

Duty Factor 0.1 %

R

D

V

GS

R

G

D.U.T.

10V

+

-

V

DD

25 50 75 100 125 150 175

0

20

40

60

80

100

120

140

160

180

200

220

T , Case Temperature ( C)

I

,

D

r

a

i

n

C

u

r

r

e

n

t

(

A

)

C

D

LIMITED BY PACKAGE

0.001

0.01

0.1

1

0.00001 0.0001 0.001 0.01 0.1

Notes:

1. Duty factor D = t / t

2. Peak T =P x Z + T

1 2

J DM thJC C

P

t

t

DM

1

2

t , Rectangular Pulse Duration (sec)

T

h

e

r

m

a

l

R

e

s

p

o

n

s

e

(

Z

)

1

t

h

J

C

0.01

0.02

0.05

0.10

0.20

D = 0.50

SINGLE PULSE

(THERMAL RESPONSE)

IRF1404

6 www.irf.com

Fig 12c. Maximum Avalanche Energy

Vs. Drain Current

Q

G

Q

GS

Q

GD

V

G

Charge

D.U.T.

V

DS

I

D

I

G

3mA

V

GS

.3F

50K

.2F

12V

Current Regulator

Same Type as D.U.T.

Current Sampling Resistors

+

-

10 V

Fig 13b. Gate Charge Test Circuit

Fig 13a. Basic Gate Charge Waveform

Fig 12b. Unclamped Inductive Waveforms

Fig 12a. Unclamped Inductive Test Circuit

t

p

V

(BR)DSS

I

AS

R

G

I

AS

0.01 t

p

D.U.T

L

V

DS

+

-

V

DD

DRIVER

A

15V

20V

Fig 14. Threshold Voltage Vs. Temperature

-75 -50 -25 0 25 50 75 100 125 150

T

J

, Temperature ( C )

1.0

2.0

3.0

4.0

-

V

G

S

(

t

h

)

G

a

t

e

t

h

r

e

s

h

o

l

d

V

o

l

t

a

g

e

(

V

)

I

D

= -250A

25 50 75 100 125 150 175

0

300

600

900

1200

1500

Starting T , Junction Temperature( C)

E

,

S

i

n

g

l

e

P

u

l

s

e

A

v

a

l

a

n

c

h

e

E

n

e

r

g

y

(

m

J

)

J

A

S

I

D

TOP

BOTTOM

49A

101A

121A

IRF1404

www.irf.com 7

Fig 15. Typical Avalanche Current Vs.Pulsewidth

Fig 16. Maximum Avalanche Energy

Vs. Temperature

Notes on Repetitive Avalanche Curves , Figures 15, 16:

(For further info, see AN-1005 at www.irf.com)

1. Avalanche failures assumption:

Purely a thermal phenomenon and failure occurs at a

temperature far in excess of T

jmax

. This is validated for

every part type.

2. Safe operation in Avalanche is allowed as long asT

jmax

is not exceeded.

3. Equation below based on circuit and waveforms shown

in Figures 12a, 12b.

4. P

D (ave)

= Average power dissipation per single

avalanche pulse.

5. BV = Rated breakdown voltage (1.3 factor accounts for

voltage increase during avalanche).

6. I

av

= Allowable avalanche current.

7. T = Allowable rise in junction temperature, not to exceed

T

jmax

(assumed as 25C in Figure 15, 16).

t

av =

Average time in avalanche.

D = Duty cycle in avalanche = t

av

f

Z

thJC

(D, t

av

) = Transient thermal resistance, see figure 11)

P

D (ave)

= 1/2 ( 1.3BVI

av

) = DT/ Z

thJC

I

av

=

2DT/ [1.3BVZ

th

]

E

AS (AR)

= P

D (ave)

t

av

25 50 75 100 125 150 175

Starting T

J

, Junction Temperature (C)

0

50

100

150

200

250

300

350

400

E

A

R

,

A

v

a

l

a

n

c

h

e

E

n

e

r

g

y

(

m

J

)

TOP Single Pulse

BOTTOM 10% Duty Cycle

I

D

= 121A

1.0E-08 1.0E-07 1.0E-06 1.0E-05 1.0E-04 1.0E-03 1.0E-02 1.0E-01

tav (sec)

1

10

100

1000

A

v

a

l

a

n

c

h

e

C

u

r

r

e

n

t

(

A

)

0.05

Duty Cycle = Single Pulse

0.10

Allowed avalanche Current vs

avalanche pulsewidth, tav

assuming Tj = 25C due to

avalanche losses

0.01

IRF1404

8 www.irf.com

P.W.

Period

di/dt

Diode Recovery

dv/dt

Ripple 5%

Body Diode Forward Drop

Re-Applied

Voltage

Reverse

Recovery

Current

Body Diode Forward

Current

V

GS

=10V

V

DD

I

SD

Driver Gate Drive

D.U.T. I

SD

Waveform

D.U.T. V

DS

Waveform

Inductor Curent

D =

P.W.

Period

+

-

+

+

+ -

-

-

Fig 17. For N-channel HEXFET

Power MOSFETs

* V

GS

= 5V for Logic Level Devices

Peak Diode Recovery dv/dt Test Circuit

R

G

V

DD

dv/dt controlled by R

G

Driver same type as D.U.T.

I

SD

controlled by Duty Factor "D"

D.U.T. - Device Under Test

D.U.T

Circuit Layout Considerations

Low Stray Inductance

Ground Plane

Low Leakage Inductance

Current Transformer

*

IRF1404

www.irf.com 9

IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, USA Tel: (310) 252-7105

TAC Fax: (310) 252-7903

Visit us at www.irf.com for sales contact information.01/01

Data and specifications subject to change without notice.

This product has been designed and qualified for the automotive [Q101] market.

Qualification Standards can be found on IRs Web site.

TO-220AB Package Outline

Dimensions are shown in millimeters

TO-220AB Part Marking Information

LEAD ASSIGNMENTS

1 - GATE

2 - DRAIN

3 - SOURCE

4 - DRAIN

- B -

1.32 (.052)

1.22 (.048)

3X

0.55 (.022)

0.46 (.018)

2.92 (.115)

2.64 (.104)

4.69 (.185)

4.20 (.165)

3X

0.93 (.037)

0.69 (.027)

4.06 (.160)

3.55 (.140)

1.15 (.045)

MIN

6.47 (.255)

6.10 (.240)

3.78 (.149)

3.54 (.139)

- A -

10.54 (.415)

10.29 (.405)

2.87 (.113)

2.62 (.103)

15.24 (.600)

14.84 (.584)

14.09 (.555)

13.47 (.530)

3X

1.40 (.055)

1.15 (.045)

2.54 (.100)

2X

0.36 (.014) M B A M

4

1 2 3

NOTES:

1 DIMENSIONING & TOLERANCING PER ANSI Y14.5M, 1982. 3 OUTLINE CONFORMS TO JEDEC OUTLINE TO-220AB.

2 CONTROLLING DIMENSION : INCH 4 HEATSINK & LEAD MEASUREMENTS DO NOT INCLUDE BURRS.

EXAMPLE:

IN THE ASSEMBLY LINE "C"

THIS IS AN IRF1010

LOT CODE 1789

ASSEMBLED ONWW19, 1997

PART NUMBER

ASSEMBLY

LOT CODE

DAT E CODE

YEAR 7 = 1997

LINE C

WEEK 19

LOGO

RECTIFIER

INTERNAT IONAL

Note: "P" in assembly line

position indicates "Lead-Free"

TO-220AB package is not recommended for Surface Mount Application.

For GB Production

EXAMPLE: THIS IS AN IRF1010

LOT CODE 1789

ASSEMBLEDON WW19, 1997

INT HE ASSEMBLY LINE "C"

INTERNATIONAL

RECTIFIER

LOGO

LOT CODE

PART NUMBER

DATE CODE

Note: For the most current drawings please refer to the IR website at:

http://www.irf.com/package/

You might also like

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsRating: 5 out of 5 stars5/5 (1)

- Irf1404 HEXFET (R) Power MOSFET DatasheetDocument8 pagesIrf1404 HEXFET (R) Power MOSFET DatasheetMeatheadMerlinNo ratings yet

- Irfz 34 NDocument9 pagesIrfz 34 NVitorio LogoNo ratings yet

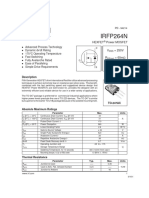

- Advanced Process Technology Ultra Low On-Resistance Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching P-Channel Fully Avalanche RatedDocument8 pagesAdvanced Process Technology Ultra Low On-Resistance Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching P-Channel Fully Avalanche RatedMokh TarNo ratings yet

- Advanced Process Technology Ultra Low On-Resistance Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching Fully Avalanche RatedDocument8 pagesAdvanced Process Technology Ultra Low On-Resistance Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching Fully Avalanche RatedDarwin Coronado AparicioNo ratings yet

- F1010NDocument8 pagesF1010Nangel sulvaranNo ratings yet

- IRFP054N PowerMOSFETDocument8 pagesIRFP054N PowerMOSFETcostelcnNo ratings yet

- Irfz24n PDFDocument9 pagesIrfz24n PDFSergio ReyesNo ratings yet

- Infineon IRF3205 DataSheet v01 01 EN-3362740Document10 pagesInfineon IRF3205 DataSheet v01 01 EN-3362740janof1No ratings yet

- Irf3808Pbf: Automotive MosfetDocument10 pagesIrf3808Pbf: Automotive Mosfetejdigger ejNo ratings yet

- Irf 3205 PBFDocument8 pagesIrf 3205 PBFVova KozlovNo ratings yet

- Irfz48npbf PDFDocument8 pagesIrfz48npbf PDFAntony BurgersNo ratings yet

- Advanced Process Technology Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching Fully Avalanche RatedDocument8 pagesAdvanced Process Technology Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching Fully Avalanche Ratedjohan elian whiteNo ratings yet

- Advanced Process Technology Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching Fully Avalanche RatedDocument9 pagesAdvanced Process Technology Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching Fully Avalanche RatedMilton OrtegaNo ratings yet

- DatasheetDocument8 pagesDatasheetOscarito VázquezNo ratings yet

- Irf5210 100V 40aDocument9 pagesIrf5210 100V 40aReneNo ratings yet

- Advanced Process Technology Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching P-Channel Fully Avalanche RatedDocument8 pagesAdvanced Process Technology Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching P-Channel Fully Avalanche RatedMax RenanNo ratings yet

- Mosfet IRFZDocument8 pagesMosfet IRFZFlavin MedinaNo ratings yet

- Infineon IRFZ44N DataSheet v01 - 01 ENDocument9 pagesInfineon IRFZ44N DataSheet v01 - 01 ENIkram RidhoNo ratings yet

- Irf 3205 SDocument10 pagesIrf 3205 SfingersoundNo ratings yet

- Irl 3705 NDocument9 pagesIrl 3705 NMeunome99No ratings yet

- Mosfet Irf 2204Document10 pagesMosfet Irf 2204Milagros Mendieta VegaNo ratings yet

- Dgdlirfp2907pbf PdffileidDocument10 pagesDgdlirfp2907pbf PdffileidLeonardo NascimentoNo ratings yet

- Irfp150npdf 231209 185343Document9 pagesIrfp150npdf 231209 185343Denilson BonifacioNo ratings yet

- Irf 3205Document12 pagesIrf 3205Bristhian LezanoNo ratings yet

- Irf 3808Document9 pagesIrf 3808mustajabali250No ratings yet

- Automotive Mosfet: Typical ApplicationsDocument10 pagesAutomotive Mosfet: Typical ApplicationsSaikumarNo ratings yet

- IRFZ 34N - International RectifierDocument8 pagesIRFZ 34N - International RectifierStevenNo ratings yet

- IRFZ46NDocument8 pagesIRFZ46NAbel RodriguezNo ratings yet

- Irfiz 34 NDocument8 pagesIrfiz 34 NBase de DatosNo ratings yet

- DatasheetDocument8 pagesDatasheetAndrianarimananaNo ratings yet

- Irfp 250 NDocument9 pagesIrfp 250 NjozzemarNo ratings yet

- Datasheet f1010Document8 pagesDatasheet f1010shobu21100% (1)

- IRF1405Document9 pagesIRF1405Francisco MadridNo ratings yet

- Infineon IRF1010E Aplication - ENDocument9 pagesInfineon IRF1010E Aplication - ENlaciNo ratings yet

- Ir53h420 Mosfet1Document9 pagesIr53h420 Mosfet1Gilson Mendes SilvaNo ratings yet

- Irfp250n PDFDocument9 pagesIrfp250n PDFEdison RamirezNo ratings yet

- Irf 530Document8 pagesIrf 53021524002No ratings yet

- Advanced Process Technology Ultra Low On-Resistance Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching Fully Avalanche RatedDocument8 pagesAdvanced Process Technology Ultra Low On-Resistance Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching Fully Avalanche RatedwilltorNo ratings yet

- IRF6215 DatasheetzDocument9 pagesIRF6215 DatasheetzBoniface AsuvaNo ratings yet

- IRFZ44N 60V 55A 16.5mo Vth4.0 PDFDocument9 pagesIRFZ44N 60V 55A 16.5mo Vth4.0 PDFVolodiyaNo ratings yet

- IRF3710Z: Automotive MosfetDocument9 pagesIRF3710Z: Automotive Mosfetgorgor1No ratings yet

- IRF1010E NmosfetDocument11 pagesIRF1010E NmosfettariqNo ratings yet

- Irf3710 Datasheet PDFDocument8 pagesIrf3710 Datasheet PDFMiguel Gutierréz CasillasNo ratings yet

- Datasheet PDFDocument8 pagesDatasheet PDFSaad LehlouNo ratings yet

- Advanced Process Technology Ultra Low On-Resistance Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching Fully Avalanche RatedDocument8 pagesAdvanced Process Technology Ultra Low On-Resistance Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching Fully Avalanche RatedLiver Haro OrellanesNo ratings yet

- Irf540ns PDFDocument11 pagesIrf540ns PDFJustDataNo ratings yet

- Irfz34Npbf: Hexfet Power MOSFET V 55V R 0.040 I 29ADocument9 pagesIrfz34Npbf: Hexfet Power MOSFET V 55V R 0.040 I 29Achermy025No ratings yet

- Irf3710 PDFDocument8 pagesIrf3710 PDFJose M PeresNo ratings yet

- Irl3303 (Nmos)Document8 pagesIrl3303 (Nmos)c8831116No ratings yet

- Irfp 260 NPBFDocument8 pagesIrfp 260 NPBFadamdwaldropNo ratings yet

- DatasheetDocument10 pagesDatasheettariqNo ratings yet

- Irfp 264 NDocument8 pagesIrfp 264 Nhernan luzardoNo ratings yet

- Expandir MenteDocument11 pagesExpandir MenteyormanNo ratings yet

- IRF9Z24NDocument8 pagesIRF9Z24NnoahkrpgNo ratings yet

- 64 2096pbf KNHuDWrv 2j6YLvwomDocument10 pages64 2096pbf KNHuDWrv 2j6YLvwomCh Jameel SidhuNo ratings yet

- Irfp264n PDFDocument8 pagesIrfp264n PDFAdah BumbonNo ratings yet

- Unit 2 CAPE ALKANE NOTESDocument4 pagesUnit 2 CAPE ALKANE NOTESiramkissoonNo ratings yet

- Piling2020 Morrison Et Al FinalDocument7 pagesPiling2020 Morrison Et Al Finalstromek2006No ratings yet

- Thomas Rexnord Spacer CouplingsDocument6 pagesThomas Rexnord Spacer CouplingsAnonymous ieWpd823Lg100% (1)

- Quantum MEchanicsDocument33 pagesQuantum MEchanicsRehan KhanNo ratings yet

- Pilot Product Catalogue 18Document28 pagesPilot Product Catalogue 18veerraju tvNo ratings yet

- Chapter 4 - Probability - The Study of RandomnessDocument2 pagesChapter 4 - Probability - The Study of Randomnessyakamoto1No ratings yet

- UNIT - I Zeroth and First Law of ThermodynamicsDocument17 pagesUNIT - I Zeroth and First Law of ThermodynamicsCHANDRASEKARANNo ratings yet

- Trig MsDocument33 pagesTrig MsHappybabyNo ratings yet

- Practice Problems For NeetDocument359 pagesPractice Problems For NeetPrudhvi Nath0% (2)

- List of NDT & Inspection Approved Training Organisations: Rev A 4 January 2016Document24 pagesList of NDT & Inspection Approved Training Organisations: Rev A 4 January 2016edwinlcsNo ratings yet

- Exp 3Document8 pagesExp 3ValentinoDullSatinNo ratings yet

- 1830 - Fea Fatigue Analysis Report PDFDocument19 pages1830 - Fea Fatigue Analysis Report PDFGabbar SinghNo ratings yet

- T3HQDocument9 pagesT3HQNkemzi Elias NzetengenleNo ratings yet

- Rampas Casting Instructionspost TreatmentDocument3 pagesRampas Casting Instructionspost TreatmentWagner GarciaNo ratings yet

- Common Fourier Transforms Questions and Answers - SanfoundryDocument11 pagesCommon Fourier Transforms Questions and Answers - SanfoundrykshambelmekuyeNo ratings yet

- CEV452 Experiment 1 (Gas Absorption)Document22 pagesCEV452 Experiment 1 (Gas Absorption)Roger Fernandez100% (1)

- ELECTROPHRESISDocument66 pagesELECTROPHRESISM.PRASAD NAIDU100% (1)

- Region VI Awards Grades 1-6: Project Class 1Document10 pagesRegion VI Awards Grades 1-6: Project Class 1AnandNo ratings yet

- Stepien KfullpaperDocument5 pagesStepien KfullpaperRahul ChavanNo ratings yet

- Discovery: CG4 Molecular CloudDocument2 pagesDiscovery: CG4 Molecular Cloudrpraj3135No ratings yet

- Dial GaugeDocument21 pagesDial GaugeRaghavendra KilariNo ratings yet

- Aristarchus of Samos - Wikipedia, The Free EncyclopediaDocument2 pagesAristarchus of Samos - Wikipedia, The Free Encyclopediadonodoni00080% (1)

- Schunk Sealing RingsDocument20 pagesSchunk Sealing Ringspeach5No ratings yet

- M.R.Barakat CVDocument2 pagesM.R.Barakat CVMohammad Rashad BarakatNo ratings yet

- The Acoustics of Wind InstrumentsDocument10 pagesThe Acoustics of Wind InstrumentsagjNo ratings yet

- Unit Test-2Document18 pagesUnit Test-2Reshma ANo ratings yet

- Studies in The Synthesis of ZSM-5 ZeolitesDocument6 pagesStudies in The Synthesis of ZSM-5 ZeolitesTriếtMinhNo ratings yet

- Material Analisis Estructural II PDFDocument6 pagesMaterial Analisis Estructural II PDFMilapalomaNo ratings yet

- AP Calculus NotebookDocument3 pagesAP Calculus NotebooksamuelsparkNo ratings yet

- Journal of Applied Polymer Science Volume 98 Issue 2 2005 (Doi 10.1002 - App.22097) Kishore Ravi Shankar S. Sankaran - Short-Beam Three-Point Bend Tests in Syntactic Foams. Part II - Effect of MicroDocument7 pagesJournal of Applied Polymer Science Volume 98 Issue 2 2005 (Doi 10.1002 - App.22097) Kishore Ravi Shankar S. Sankaran - Short-Beam Three-Point Bend Tests in Syntactic Foams. Part II - Effect of MicroPablo OrtegaNo ratings yet