Professional Documents

Culture Documents

Fixed Bias PDF

Fixed Bias PDF

Uploaded by

sasikalasivakumarOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Fixed Bias PDF

Fixed Bias PDF

Uploaded by

sasikalasivakumarCopyright:

Available Formats

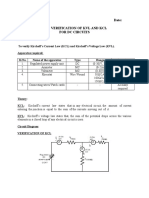

ENGI 242/ELEC 222 January 2004

Fixed Bias 1

BJT Fixed Bias

ENGI 242

ELEC 222

January 2004 ENGI 242/ELEC 222 2

BJT Biasing 1

For Fixed Bias Configuration:

Draw Equivalent Input circuit

Draw Equivalent Output circuit

Write necessary KVL and KCL Equations

Determine the Quiescent Operating Point

Graphical Solution using Loadlines

Computational Analysis

Design and test design using a computer simulation

ENGI 242/ELEC 222 January 2004

Fixed Bias 2

January 2004 ENGI 242/ELEC 222 3

Complete CE Amplifier with Fixed Bias

January 2004 ENGI 242/ELEC 222 4

Fixed Bias and Equivalent DC Circuit

ENGI 242/ELEC 222 January 2004

Fixed Bias 3

January 2004 ENGI 242/ELEC 222 5

Fixed-Bias Circuit

January 2004 ENGI 242/ELEC 222 6

DC Equivalent Circuit

ENGI 242/ELEC 222 January 2004

Fixed Bias 4

January 2004 ENGI 242/ELEC 222 7

Base-Emitter (Input) Loop

Using Kirchoffs voltage law: V

CC

+ I

B

R

B

+ V

BE

= 0

Solving for IB:

CC BE

B

B

V - V

I =

R

January 2004 ENGI 242/ELEC 222 8

Collector-Emitter (Output) Loop

Since: IC = IB

Using Kirchoffs voltage law: VCC + IC RC + VCE = 0

Because: VCE = VC VE

Since VE = 0V, then: VC = VCE

And VCE = VCC - IC RC

Also: VBE = VB - VE

with VE = 0V, then: VB = VBE

ENGI 242/ELEC 222 January 2004

Fixed Bias 5

January 2004 ENGI 242/ELEC 222 9

BJT Saturation Regions

When the transistor is operating in the

Saturation Region, the transistor is

conducting at maximum collector

current (based on the resistances in

the output circuit, not the spec sheet

value) such that:

CC CE

Csat

C

CE where

V - V

I =

R

V = 0.2 V

January 2004 ENGI 242/ELEC 222 10

Determining Icsat

ENGI 242/ELEC 222 January 2004

Fixed Bias 6

January 2004 ENGI 242/ELEC 222 11

Determining ICSAT for the fixed-bias configuration

January 2004 ENGI 242/ELEC 222 12

Load Line Analysis

ENGI 242/ELEC 222 January 2004

Fixed Bias 7

January 2004 ENGI 242/ELEC 222 13

Load Line Analysis

The end points of the line are : I

Csat

and V

CE

cutoff

For load line analysis, use VCE = 0 for ICSAT, and IC = 0 for VCEcutoff

I

Csat

:

V

CEcutoff

:

Where IB intersects with the load line we have the Q point

Q-point is the particular operating point:

Value of R

B

Sets the value of I

B

Where I

B

and Load Line intersect

Sets the values of V

CE

and I

C

.

CE

C

CC

Csat

V 0V

C

CE CC

I 0mA

V

I =

R

V = V

|

|

=

=

January 2004 ENGI 242/ELEC 222 14

Circuit values effect Q-point

ENGI 242/ELEC 222 January 2004

Fixed Bias 8

January 2004 ENGI 242/ELEC 222 15

Circuit values effect Q-point (continued)

January 2004 ENGI 242/ELEC 222 16

Circuit values effect Q-point (continued)

ENGI 242/ELEC 222 January 2004

Fixed Bias 9

January 2004 ENGI 242/ELEC 222 17

Load-line analysis

January 2004 ENGI 242/ELEC 222 18

DC Fixed Bias Circuit Example

ENGI 242/ELEC 222 January 2004

Fixed Bias 10

January 2004 ENGI 242/ELEC 222 19

Loadline Example Family of Curves

Emitter Stabilized Bias

ENGI 242

ELEC 222

ENGI 242/ELEC 222 January 2004

Fixed Bias 11

January 2004 ENGI 242/ELEC 222 21

BJT Emitter Bias

For the Emitter Stabilized Bias Configuration:

Draw Equivalent Input circuit

Draw Equivalent Output circuit

Write necessary KVL and KCL Equations

Determine the Quiescent Operating Point

Graphical Solution using Loadlines

Computational Analysis

Design and test design using a computer simulation

January 2004 ENGI 242/ELEC 222 22

Improved Bias Stability

The addition of RE to the Emitter circuit improves the stability of a transistor

output

Stability refers to a bias circuit in which the currents and voltages will

remain fairly constant over a wide range of temperatures and transistor

forward current gain ()

The temperature (TA or ambient temperature) surrounding the transistor

circuit is not always constant

Therefore, the transistor is not a constant value

ENGI 242/ELEC 222 January 2004

Fixed Bias 12

January 2004 ENGI 242/ELEC 222 23

Emitter-Stabilized Bias Circuit

Adding an emitter resistor to the circuit between the emitter lead and ground stabilizes

the bias circuit over Fixed Bias

January 2004 ENGI 242/ELEC 222 24

Base-Emitter Loop

ENGI 242/ELEC 222 January 2004

Fixed Bias 13

January 2004 ENGI 242/ELEC 222 25

Equivalent Network

January 2004 ENGI 242/ELEC 222 26

Reflected Input impedance of RE

ENGI 242/ELEC 222 January 2004

Fixed Bias 14

January 2004 ENGI 242/ELEC 222 27

Base-Emitter Loop

Applying Kirchoffs voltage law: - VCC + IB RB + VBE +IE RE = 0

Since: IE = ( + 1) IB

We can write: - VCC + IB RB + VBE + ( + 1) IB RE = 0

Grouping terms and solving for I

B

:

Or we could solve for IE with:

CC BE

B

B E

V - V

I =

R + (+1)R

B

CC E BE E E

R

- V + I + V + I R = 0

( + 1)

January 2004 ENGI 242/ELEC 222 28

Collector-Emitter Loop

ENGI 242/ELEC 222 January 2004

Fixed Bias 15

January 2004 ENGI 242/ELEC 222 29

Collector-Emitter Loop

Applying Kirchoffs voltage law: - VCC + IC RC + VCE + IE RE = 0

Assuming that I

E

I

C

and solving for VCE: VCE = VCC IC (RC + RE)

If we can not use IE IC the IC = IE and: VCE = VCC IC (RC + RE)

Solve for V

E

: VE = IE RE

Solve for V

C

: VC = VCC - IC RC

or

VC = VCE + IE RE

Solve for V

B

: VB = VCC - IB RB

or

VB = VBE + IE RE

January 2004 ENGI 242/ELEC 222 30

Transistor Saturation

CC CE

CSAT

C E

V - V

I =

R + R

At saturation, VCE is at a minimum

We will find the value VCEsat = 0.2V

For load line analysis, we use VCE = 0

To solve for ICSAT, use the output KVL

equation:

ENGI 242/ELEC 222 January 2004

Fixed Bias 16

January 2004 ENGI 242/ELEC 222 31

Load Line Analysis

The load line end points can be calculated:

At cutoff:

At saturation:

C

CE CC

I = 0 mA

V V | =

CE

CC

C

V = 0V

C E

V

I =

R + R

|

January 2004 ENGI 242/ELEC 222 32

Emitter Stabilized Bias Circuit Example

ENGI 242/ELEC 222 January 2004

Fixed Bias 17

January 2004 ENGI 242/ELEC 222 33

Design of an Emitter Bias CE Amplifier

Where .1VCC VE .2VCC

And .4VCC VC .6VCC

January 2004 ENGI 242/ELEC 222 34

Emitter Bias with Dual Supply

ENGI 242/ELEC 222 January 2004

Fixed Bias 18

January 2004 ENGI 242/ELEC 222 35

Emitter Bias with Dual Supply

Input Output

You might also like

- 8085 Microprocessor ArchitectureDocument46 pages8085 Microprocessor ArchitectureJuhil H Patel100% (1)

- EDC Question-Papers Complete SetDocument13 pagesEDC Question-Papers Complete Setselvi04120% (1)

- Technology and Livelihood Education: Computer System Servicing Quarter 1-Module 4Document42 pagesTechnology and Livelihood Education: Computer System Servicing Quarter 1-Module 4Renny Romero LuzadaNo ratings yet

- Differential Amplifier Using BJTDocument11 pagesDifferential Amplifier Using BJTAssini HussainNo ratings yet

- DADocument40 pagesDAkrishneel sharmaNo ratings yet

- Lab Report 8Document8 pagesLab Report 8Nebil YisuNo ratings yet

- EC Chapter 01Document39 pagesEC Chapter 01Muhammad qamar100% (1)

- Group 2 Act 5Document6 pagesGroup 2 Act 5Quezza Phola S PatulinNo ratings yet

- SKEE 2742 Basic Electronics Lab: Experiment 2 BJT Small-Signal AmplifierDocument8 pagesSKEE 2742 Basic Electronics Lab: Experiment 2 BJT Small-Signal Amplifierمحمد ابو جرادNo ratings yet

- Transistor Biasing & Thermal Stability: Prepared By: Mr. Gaurav Verma Asst. Prof. ECE Dept. NiecDocument80 pagesTransistor Biasing & Thermal Stability: Prepared By: Mr. Gaurav Verma Asst. Prof. ECE Dept. NiecAbhishek abhishekNo ratings yet

- DC and AC Analysis BJTsDocument100 pagesDC and AC Analysis BJTsHasmizar Abd Halim (KTN)No ratings yet

- BJT BiasingDocument26 pagesBJT BiasingShafiul Huda Eraz100% (1)

- Chapter5 PDFDocument128 pagesChapter5 PDFTonmoyNo ratings yet

- Electronics Lab Report: Transistor As A SwitchDocument7 pagesElectronics Lab Report: Transistor As A SwitchshahzaibNo ratings yet

- Activity5 Group1Document24 pagesActivity5 Group1NicoNo ratings yet

- A C Circuit-II FinalDocument57 pagesA C Circuit-II FinalVaibhavNo ratings yet

- Experiment No. 6 Amplifier Frequency Response - JFETDocument4 pagesExperiment No. 6 Amplifier Frequency Response - JFETDan BautistaNo ratings yet

- Shockley Diode Working and AdvantagesDocument6 pagesShockley Diode Working and AdvantagesHaries GarciaNo ratings yet

- 6.BJT 6 (CH 8 Electronic Devices and Circuit Theory Robert Boylestad Louis Nashelsky 7th Edition)Document46 pages6.BJT 6 (CH 8 Electronic Devices and Circuit Theory Robert Boylestad Louis Nashelsky 7th Edition)shilaNo ratings yet

- Verification of KCL and KVLDocument3 pagesVerification of KCL and KVLCOLD FIRENo ratings yet

- Lesson 2 - BJT Small Signal Amp PDFDocument62 pagesLesson 2 - BJT Small Signal Amp PDFToánNo ratings yet

- PoEC 18 RLC Circuits and Resonance PDFDocument52 pagesPoEC 18 RLC Circuits and Resonance PDFAndrew Pontanal100% (1)

- Charging and Discharging A CapacitorDocument5 pagesCharging and Discharging A CapacitorRenalyn AblingNo ratings yet

- Classifications of Signals: ECE 593: Signal, Spectra and Signal Processing Course OutlineDocument6 pagesClassifications of Signals: ECE 593: Signal, Spectra and Signal Processing Course OutlinekoshaiNo ratings yet

- Investigation of Transistor Characteristics of N-P-N and P-N-PDocument9 pagesInvestigation of Transistor Characteristics of N-P-N and P-N-PMOKAYANo ratings yet

- ECE Experiment No 5Document11 pagesECE Experiment No 5GeeK GuYNo ratings yet

- Experiment 1Document12 pagesExperiment 1Jomar RosalesNo ratings yet

- ECE2201 Lab Report 7Document9 pagesECE2201 Lab Report 7Raihan JannatiNo ratings yet

- Lab 6 Combinational Logic and Boolean SimplificationDocument4 pagesLab 6 Combinational Logic and Boolean SimplificationRabah AmidiNo ratings yet

- Experiment 1Document6 pagesExperiment 1Jomel JomelNo ratings yet

- Basic BJT Operation and BiasingDocument59 pagesBasic BJT Operation and BiasingangenghuatNo ratings yet

- CKRT Breaker Report 123Document32 pagesCKRT Breaker Report 123soumya jpNo ratings yet

- Experiment 10 Kirchhoffs LawDocument8 pagesExperiment 10 Kirchhoffs Lawthomas melgarNo ratings yet

- EE212 Short Test 1 2016 SolDocument4 pagesEE212 Short Test 1 2016 SolkioneNo ratings yet

- Lab 6Document5 pagesLab 6par1vej2No ratings yet

- Group Study - Industrial Electronics and Robotics Answer KeyDocument6 pagesGroup Study - Industrial Electronics and Robotics Answer KeySheehan Kayne De CardoNo ratings yet

- EM308 Lab 001 Jan15Document7 pagesEM308 Lab 001 Jan15shakeeb mana0% (1)

- Home Assignment - 1Document2 pagesHome Assignment - 1chaitanyaNo ratings yet

- A Transistor May Be Operated in Three Different ConfigurationsDocument7 pagesA Transistor May Be Operated in Three Different ConfigurationsApurva NagdeoteNo ratings yet

- DC MotorDocument38 pagesDC MotorMarc Joshua MACATANGAYNo ratings yet

- MCQ in DC Biasing - BJTsDocument6 pagesMCQ in DC Biasing - BJTsPaolo PerezNo ratings yet

- Transistor CharacteristicsDocument44 pagesTransistor CharacteristicsNidhi PatelNo ratings yet

- Bef 23903 - Chapter 3 - DC Bridge - Wheatstone BridgeDocument19 pagesBef 23903 - Chapter 3 - DC Bridge - Wheatstone BridgeMuhammad Izz IzzuddinNo ratings yet

- ECE2120 Electrical Engineering Laboratory II Lab 3: Capacitors and Series RC CircuitsDocument12 pagesECE2120 Electrical Engineering Laboratory II Lab 3: Capacitors and Series RC CircuitsMuhammad AzeemNo ratings yet

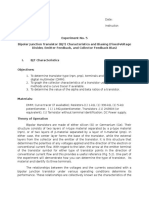

- CH 6 - Voltage Regulator PDFDocument46 pagesCH 6 - Voltage Regulator PDFsureshy-ee213No ratings yet

- UJTDocument7 pagesUJTReddyvari VenugopalNo ratings yet

- Transmission LinesDocument19 pagesTransmission LinesSherwin CatolosNo ratings yet

- Physics 09-Electric CircuitsDocument74 pagesPhysics 09-Electric CircuitsengrroyNo ratings yet

- Exp 1 Group 4 DraftDocument35 pagesExp 1 Group 4 DraftJERUSHA ANNE RETARDONo ratings yet

- Basic Electronics Lab Manual For BSCDocument15 pagesBasic Electronics Lab Manual For BSCGanesan KandasamyNo ratings yet

- Quadrature Phase Shift Keying (QPSK)Document41 pagesQuadrature Phase Shift Keying (QPSK)Luis Fernando Grueso-TenorioNo ratings yet

- Lab Manual All ExperimentDocument62 pagesLab Manual All ExperimentLIFE of PSNo ratings yet

- EEM328 Electronics Laboratory - Experiment 3 - Diode ApplicationsDocument3 pagesEEM328 Electronics Laboratory - Experiment 3 - Diode Applicationsdonatello84No ratings yet

- 2.3.2 Analysis of The Conversion Ratio M (D, K) PDFDocument10 pages2.3.2 Analysis of The Conversion Ratio M (D, K) PDFArmy Joel MarianoNo ratings yet

- Solved Problems On Transistor Biasing Excellent StuffDocument15 pagesSolved Problems On Transistor Biasing Excellent StuffStudent HelperNo ratings yet

- 5 Unit - 5 Field Effect Transistors: Review QuestionsDocument16 pages5 Unit - 5 Field Effect Transistors: Review Questionsashley correa100% (1)

- Experiment 3 Indiv. ReportDocument3 pagesExperiment 3 Indiv. ReportKyla Mae Arago100% (1)

- Magnetically Coupled CircuitDocument38 pagesMagnetically Coupled CircuitAlfred MoresNo ratings yet

- OSI Reference ModelDocument12 pagesOSI Reference ModelpavalbharathiNo ratings yet

- Analog Circuits SyllabusDocument5 pagesAnalog Circuits SyllabusVilayil jestinNo ratings yet

- Experiment 3 - Common Emitter AmplifierDocument6 pagesExperiment 3 - Common Emitter AmplifierAsyraf Norahairuzan100% (1)

- EDC Question BankDocument44 pagesEDC Question BankKRCT EEE HODNo ratings yet

- BJT Fixed Bias: ENGI 242 ELEC 222Document35 pagesBJT Fixed Bias: ENGI 242 ELEC 222Edward FahmiNo ratings yet

- Engi 242/elec 222Document7 pagesEngi 242/elec 222betteralwzNo ratings yet

- BJT Bias 2Document21 pagesBJT Bias 2kashi13No ratings yet

- FET BiasingDocument48 pagesFET Biasingbetteralwz100% (3)

- Introduction To BC558 - The Engineering ProjectsDocument11 pagesIntroduction To BC558 - The Engineering ProjectsAderinla OkeowoNo ratings yet

- GATE ECE 2011 Actual PaperDocument34 pagesGATE ECE 2011 Actual Paperkibrom atsbhaNo ratings yet

- LAB 1-PE-LabDocument10 pagesLAB 1-PE-LabLovely JuttNo ratings yet

- BC546 BC547 BC548 PDFDocument3 pagesBC546 BC547 BC548 PDFrrebollarNo ratings yet

- Service Manual 3Y18 Chassis: Design and Specifications Are Subject To Change Without Prior Notice. (Only Referrence)Document37 pagesService Manual 3Y18 Chassis: Design and Specifications Are Subject To Change Without Prior Notice. (Only Referrence)LUIS CASTRONo ratings yet

- DANFOSS Selection GuideDocument60 pagesDANFOSS Selection GuidemikcomiNo ratings yet

- ECE65 - W12 BJT Prob PDFDocument9 pagesECE65 - W12 BJT Prob PDFAccio MoraNo ratings yet

- Course SyllabusDocument56 pagesCourse SyllabusjigarspatelNo ratings yet

- PLC Wiring Q&aDocument59 pagesPLC Wiring Q&apascal sitanggangNo ratings yet

- w5bwc Rs35 RebuildDocument12 pagesw5bwc Rs35 RebuildLaurentiu IacobNo ratings yet

- bc458 PDFDocument7 pagesbc458 PDFKristy BarrettNo ratings yet

- Encoders KUBLERDocument156 pagesEncoders KUBLERBruno AdroverNo ratings yet

- Boost Converter Design 41Document19 pagesBoost Converter Design 41JRONo ratings yet

- 100 Watts OTL Amplifier Circuit Using Transistor MJ15003Document7 pages100 Watts OTL Amplifier Circuit Using Transistor MJ15003metinprivat01No ratings yet

- Oluwatimilehin Lokulo-Sodipe Lab 3Document13 pagesOluwatimilehin Lokulo-Sodipe Lab 3Oluwatimilehin Lokulo-SodipeNo ratings yet

- Data SheetDocument3 pagesData SheetEnrique Fernando Mamani ChirinoNo ratings yet

- r1858b89dd c8f6 41da b2d4 3a8c18e129a4 Gc1f Eng Designers Reference Handbook LDocument123 pagesr1858b89dd c8f6 41da b2d4 3a8c18e129a4 Gc1f Eng Designers Reference Handbook Lناجى ابوعورةNo ratings yet

- DTS 2500 1209 EngDocument4 pagesDTS 2500 1209 EngGopal HegdeNo ratings yet

- FL2Document7 pagesFL2Carlos MartínezNo ratings yet

- Automobile Sem 5Document7 pagesAutomobile Sem 5pravin23105921No ratings yet

- ECD Lab 2 PDFDocument12 pagesECD Lab 2 PDFMaryam MahmoodNo ratings yet

- Tutorial Sheet Analog ElectronicsDocument7 pagesTutorial Sheet Analog ElectronicsPraney KalraNo ratings yet

- Analog Electronic Circuits - Eurec-402 PDFDocument2 pagesAnalog Electronic Circuits - Eurec-402 PDFAKNo ratings yet

- Transistor BD139Document4 pagesTransistor BD139Rodrigo FuentesNo ratings yet

- Lecture05 Ee474 Layout PDFDocument77 pagesLecture05 Ee474 Layout PDFsridharNo ratings yet

- 2.electronic Devices & CircuitsDocument93 pages2.electronic Devices & CircuitsMuhammad AbdullahNo ratings yet

- (MWRF0211) Buffer Amplifiers Solve VCO ProblemsDocument2 pages(MWRF0211) Buffer Amplifiers Solve VCO ProblemsLuís Ki-llahNo ratings yet