Professional Documents

Culture Documents

Digital Electrinic Lab Source For Be 3sem Student

Digital Electrinic Lab Source For Be 3sem Student

Uploaded by

jgssb85Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Digital Electrinic Lab Source For Be 3sem Student

Digital Electrinic Lab Source For Be 3sem Student

Uploaded by

jgssb85Copyright:

Available Formats

DIGITAL LOGIC DESIGN AND APPLICATIONS

LAB MANUAL

SUBJECT:

DIGITAL LOGIC DESIGN

AND

APPLICATIONS

SE (COMPUTERS)

SEM III

DIGITAL LOGIC DESIGN AND APPLICATIONS

INDEX

Sr.

No

Title of the Experiment

Page

No.

Study of BASIC Gates

Universal Gates

Study of Full & Half Adder & Subtractor using Gates

Study of Magnitude Comparator

10

Study of Multiplexer

11

Study of Demultiplexer

13

Implementation of Flip-Flops using NAND & Study of

7476

15

Study of Shift Register

17

Design of Counter & Study of IC 7490

19

10 Vo V/S Vi Characteristic of TTL & CMOS

21

DIGITAL LOGIC DESIGN AND APPLICATIONS

TITLE

EXPT. NO. 1

STUDY OF BASIC GATES

AIM

To study basic gates.

APPARATUS

Power Supply, Breadboard, Connecting wires.

COMPONENTS ICs 7400, 7402, 7404, 7408, 7432, 7486, LED.

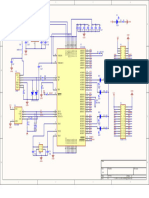

IC PINOUTS

TRUTH-TABLE

NAND

A

Y=A.B

NOR

A

Y=A+B

NOT

Y=A

DIGITAL LOGIC DESIGN AND APPLICATIONS

AND

A

Y=A.B

OR

A

Y=A+B

EX-OR

Y=AB+AB

DIGITAL LOGIC DESIGN AND APPLICATIONS

THEORY

Logic gates are the digital circuits with one output and one or

more inputs. They are the basic building blocks of any logic ckt.

Different logic gates are : AND, OR, NOT, NAND, NOR, EXOR. They work according to certain logic.

AND : Logic eqn. Y = A.B

The output of AND gate is true when the inputs A and B are

True.

OR : Logic eqn. Y = A+B.

The output of OR gate is true when one of the inputs A and B or

both the inputs are true.

NOT : Logic eqn. Y = .

The output of NOT gate is complement of the input.

NAND : Logic eqn. Y = A.B

The output of NAND gate is true when one of the inputs or both

the inputs are low level.

NOR : Logical eqn. Y = A+B.

The output of NOR gate is true when both the inputs are low.

EX-OR: Logic eqn. Y=AB+AB.

The output of EX-OR gate is true when both the inputs are low.

PROCEDURE

1)Give biasing to the IC and do necessary connections.

2) Give various combinations of inputs and note down the output

with help of LED for all gate ICs one by one.

CONCLUSION

Thus all basic gates are studied.

DIGITAL LOGIC DESIGN AND APPLICATIONS

TITLE

EXPT. NO. 2

UNIVERSAL GATES

AIM

To study the realization of basic gates using universal gates.

APPARATUS

Power supply, Breadboard.

COMPONENTS ICs 7400, 7402, LED.

CIRCUIT

DIAGRAM

Using NAND

Using NOR

DIGITAL LOGIC DESIGN AND APPLICATIONS

THEORY

AND, OR, NOT are called basic gates as their logical operation

cannot be simplified further.

NAND and NOR are called universal gates as using only NAND

or only NOR any logic function can be implemented. Using

NAND and NOR gates and De Morgans Theorems different

basic gates & EX-OR gates are realized.

PROCEDURE

1)Give biasing to the IC and do necessary connections as shown

in the ckt. diagram.

2)Give various combinations of inputs and notedown output

using LED.

3) Repeat the procedure for all gates.

OBSERVATION

TABLE

CONCLUSION

Thus universal gates are studied.

DIGITAL LOGIC DESIGN AND APPLICATIONS

TITLE

EXPT. NO. 3

ADDER AND SUBTRACTOR

AIM

To study adder and subtractor circuits using logic gates.

APPARATUS

Power supply, breadboard.

COMPONENTS ICs 7486, 7432, 7408, 7404, LEDs.

CIRCUIT

DIAGRAM

Half Adder

AND

OBSREVATION

TABLE

Full Adder

B Sum Carry

A B C Sum

Half Subtractor

Diff.

Carry

Bout

DIGITAL LOGIC DESIGN AND APPLICATIONS

Full Subtractor

Bout

THEORY

A digital adder circuit adds binary signals & a subtractor

subtracts binary signals. Half Adder/Subtractor is a basic ckt.

that adds / subtracts 2 bits and generates sum or difference along

with Carry / Borrow. Unlike half adder or subtractor a full adder

/ subtractor has the provision to take consideration of previous

carry / borrow also.

PROCEDURE

A digital adder circuit adds binary signals & a subtractor

subtracts binary signals. Half Adder / subtractor is a basic ckt.

that adds / subtracts 2 bits and generates sum or difference

along with Carry / Borrow. Unlike half adder or subtractor a full

adder / subtractor has the provision to take consideration of

previous carry / borrow also.

CONCLUSION

Thus half & full Adder / Subtractor is studied.

DIGITAL LOGIC DESIGN AND APPLICATIONS

TITLE

EXPT. NO. 4

MAGNITUDE COMPARATOR

AIM

To study magnitude comparator.

APPARATUS

Power supply, Breadboard.

COMPONENTS IC 7485, LEDs.

IC PINOUT

THEORY

Magnitude Comparator compares two binary data signals A & B

and generates the results of comparision in form of three output

signals A>B, A=B, A<B. IC 7485 is a 4-bit comparator. The

cascade inputs A>B, A=B, A<B can be used to construct a

comparator comparing more than 4 bits. The compare outputs

depend on both compare i/ps as well as cascade i/ps.

PROCEDURE

1)Give biasing to the IC .

2)Give various two 4-bit inputs and note down output.

3)Do connections for cascading and note down output for

various two 8-bit inputs.

OBSERVATION

TABLE

For 4-bit Comparator

A3 A2 A1 A0 B3 B2 B1 B0

CONCLUSION

A>B

Thus magnitude comparator is studied.

10

A=B

A<B

DIGITAL LOGIC DESIGN AND APPLICATIONS

TITLE

EXPT. NO. 5

MULTIPLEXER

AIM

To study multiplexer.

APPARATUS

Power supply, Breadboard.

COMPONENTS IC 74151, LEDs.

IC PINOUT

THEORY

Multiplexer is a combinational ckt. that is one of the most widely

used in digital design. The multiplexer is a data selector which

gates one out of several i/ps to a single o/p. It has n data i/ps &

one o/p line & m select lines where 2m = n. Depending upon the

digital code applied at the select inputs one out of n data input is

selected & transmitted to a single o/p channel. Normally

strobe(G) input is incorporated which is generally active low

which enables the multiplexer when it is LOW. Strobe i/p helps

in cascading. A 4:1 Mux. using NAND gate can be designed as

shown in dgm 1. No. of ICs are available such as 74157, 74158

(Quad 2:1 mux), 74352, 74153 (dual 4:1 Mux.), 74151A,

74152 (8:1 Mux.), 74150 (16:1 Mux). IC 74151A is a 8 : 1

multiplexer which provides two complementary o/ps Y & Y.

The o/p Y is same as the selected i/p & Y is its complement. The

n:1 multiplexer can be used to realize a m variable function. (2m

= n, m is no. of select inputs)

PROCEDURE

1)Give biasing to the IC.

2)Do necessary connections.

11

DIGITAL LOGIC DESIGN AND APPLICATIONS

OBSERVATION

TABLE

Inputs

Outputs

Select

C

Strobe

S

CONCLUSION

Thus multiplexer is studied.

ASSIGNMENT

1)Verify the truthtable of IC 74151, 8:1 Mux.

2)Connect two 74151 ICs in cascading & verify its operation as

a 16:1 Mux.

3)Implement the function Y = AB+BC using 74151 & verify the

truthtable.

12

DIGITAL LOGIC DESIGN AND APPLICATIONS

TITLE

EXPT. NO. 6

DEMULTIPLEXER

AIM

To study demultiplexer.

APPARATUS

Power supply, Breadboard.

COMPONENTS IC 74155, LEDs.

IC PINOUT

THEORY

Demux takes single i/p & distributes it over several o/ps. It has

one data line, n o/p lines & m select lines where 2 m = n.

The logic ckt. of 1:4 demux. using NAND gates is shown in the

dgm 1. The ckt. can also be used as binary to decimal decoder

with binary inputs applied at the select i/p lines & o/p will be

obtained on the corresponding line. MSI ICs available in TTL

family for demux. are 74138(3 line to 8 line decoder/demux.),

74139(dual 2 to 4 line decoder/driver.), 74154(4 to 16 line

decoder/demux), 74155(dual 2 to 4 line decoder) etc. IC 74155 is

a dual 2 to 4 line decoder. It has two sets of active low outputs

1Y0 to 1Y3 & 2Y0 to 2Y3. A & B are the select terminals

common for both the demux. C1, C2 & G1, G2 are the data lines

& strobe(enable) inputs for the two demux. C1 is active high, C2,

G1, G2 are active low. The two 2 line to 4 line demux. can be

combined to implement 3 line to 8 line demux.

PROCEDURE

1)Give biasing to the IC.

2)Do necessary connections.

13

DIGITAL LOGIC DESIGN AND APPLICATIONS

OBSERVATION 2-Line to 4-Line Decoder OR 1-Line to 4-Line Demultiplexer

TABLE

Inputs

Outputs

Select

B

Strobe Data

A G1/G2

C1/C2

3:8 Decoder OR 1:8 Demultiplexer

Inputs

Select

Strobe

(Data)

C B A

1Y0

2Y0

1Y1

2Y1

1Y2

2Y2

1Y3

2Y3

Outputs

2Y0 2Y1 2Y2 2Y3 1Y0

1Y1 1Y2 1Y3

C = I/P's C1 and C2 connected together

+

G = I/P's G1 and G2 connected together

CONCLUSION

Thus demultiplexer is studied.

ASSIGNMENT

1)Verify the operation of both the demux in IC 74155 as per the

truthtable.

2)Combine the two demux to give 3 line to 8 line demux &

verify

the operation.

14

DIGITAL LOGIC DESIGN AND APPLICATIONS

EXPT. NO. 7

TITLE

FLIP-FLOPS

AIM

To study R-S, J-K, D and T flip-flops using IC 7476.

APPARATUS

Breadboard, Power supply.

COMPONENTS ICs 7400, 7402, 7476, LED.

CIRCUIT

DIAGRAM

AND

TRUTHTABLE

I) SR FF using NAND

II) JK FF (IC 7476)

1)

2) III) T FF using JK

Clk

Clk

Clk

T

0

1

3)

4)

15

Qn

Qn

Qn

DIGITAL LOGIC DESIGN AND APPLICATIONS

5) IV) D FF using JK

6)

Clk

Qn

0

1

7)

THEORY

Flip-flops are the basic building blocks of sequential ckt. The

clocked FFs change their o/p state depending upon i/p's at

certain interval of time synchronized with the clock pulse

applied to it.

Different types of FFs are S-R, J-K, D & T . Their operations

are described by the respective truthtables. MSI chip 7476

incorporates two negative edge triggered MasterSlave JK

flipflops. The J-K flipflop can be converted to D & T flipflop.

PROCEDURE

1)Give biasing to the IC and do necessary connections.

2)For various combinations of i/p verify the truthtable.

CONCLUSION

Thus R-S, J-K, D & T Flip-Flops are studied.

ASSIGNMENTS 1)Construct clocked S-R FF using only NAND gates & verify

the truthtable.

2)Verify the truthtable of J-K FF using IC 7476. Observe the

effect of Preset & Clear i/ps.

3)Convert the J-K FF to D & T FF.

16

DIGITAL LOGIC DESIGN AND APPLICATIONS

TITLE

EXPT. NO. 8

SHIFT REGISTER

AIM

To study shift registers.

APPARATUS

Power supply, Breadboard.

COMPONENTS

IC 7495, LEDs.

IC PINOUT

THEORY

A flip-flop stores 1-bit of digital information. It is also referred

to as 1-bit register. An array of flip-flops is required to store

the no. of bits. This is called register. The data can be entered

into or retrieved from the register. So depending on the way

how the data can be entered or retrieved there are four possible

modes of operation.

1)Serial in serial out (SISO)

2)Serial in parallel out (SIPO)

3)Parallel in serial out (PISO)

4)Parallel in parallel out (PIPO)

Registers can be designed using J-K or S-R as D-type flip-flops

and are also available as MSI devices.

The register which can be operated in all possible modes & also

the shifting of data is possible in both the directions is called

Universal register.

PROCEDURE

1)Give biasing to the IC

2)Do connections for SIPO, PIPO & Left Shift and notedown

corresponding o/p.

OBSERVATIONS I) PIPO : Parallel I/P Parallel O/P

M

Clk2

17

QA

QB

QC

QD

DIGITAL LOGIC DESIGN AND APPLICATIONS

II)SIPO : Serial I/P Parallel O/P

a) Shift Right

M

Clk1

Serial I / P

QA

QB

QC

QD

D I/P

QA

QB

QC

QD

b) Shift Left

M

Clk2

CONCLUSION

Thus shift register is studied.

18

DIGITAL LOGIC DESIGN AND APPLICATIONS

TITLE

EXPT. NO. 9

COUNTERS

AIM

To study the counters.

APPARATUS

Power supply, Breadboard.

COMPONENTS

ICs 7476, 7490, LEDs.

IC PINOUTS

CIRCUIT

DIAGRAM

19

DIGITAL LOGIC DESIGN AND APPLICATIONS

THEORY

A ckt. used for counting the pulses is known as counter.

Basically there are two types of counters.

1)Asynchronous counter (ripple counter).

2)Synchronous counter.

Asynchronous counter : In the case of an Asynchronous

Counter,all the flip-flops are not clocked simultaneously. This

counter is simple in operation & requires a min. of hardware.

But its speed is low. Each FF is triggered by a previous FF o/p.

Each FF takes its own time to give o/p (due to propagation

delay). So final settling time is high. They have the problem of

glitch.

Synchronous counter : In synchronous counters all the Ffs

are clocked simultaneously. It is complex in construction, but

speed is more. In this case since each FF is clocked

simultaneously thus settling time is the delay time of single FF.

No problem of glitch.

Asynchronous counter IC (7490) : It is a BCD counter. It

consists of four FFs internally connected to provide a mod-2

counter and a mod-5 counter. The mod-2 and mod-5 counters

can be used independently or in combination. FFA operates as

a mod2 counter whereas the combination of FFB, FFC and

FFD form a mod-5 counter. There are two reset inputs R1 &

R2 both of which are to be connected to logic 1 level for

clearing all the FFs. The two set inputs S1 & S2 when

connected to logic1 level are used for setting the counter to

1001.

PROCEDURE

1)Do connections as per the ckt. dgm.

2)Give biasing to the ICs.

3)Observe o/p using LEDs.

OBSERVATIONS

Counter State

0

:

:

7

CONCLUSION

Thus counters is studied.

20

Q0

Q1

Q2

DIGITAL LOGIC DESIGN AND APPLICATIONS

TITLE

EXPT. NO. 10

TRANSFER CHARACTERISTIC OF TTL AND CMOS

AIM

To study TTL & CMOS transfer characteristics.

APPARATUS

Dual Power supply, Breadboard, Multimeter.

COMPONENTS

ICs 74LS00, 74HC00.

CIRCUIT

DIAGRAM

THEORY

A group of compatible ICs with the same logic levels and

supply voltages for performing various logic functions have

been fabricated using a specific ckt. configuration which is

referred to as a logic family. TTL (Transistor-Transistor logic)

is one of the saturated Bipolar logic families. CMOS

(Complementary metal oxide semiconductor) is an unipolar

logic family. Various chars. of digital ICs are used to compare

their performances.

Current & Voltage parameters :High level i/p voltage VIH : This is the min. i/p voltage at

the o/p corresponding to logic1.

Low level i/p voltage VIL : This is the max. i/p voltage

which is recognized by the gate as logic0.

High level output voltage VOH : This is the min. voltage

available at the o/p corresponding to logic1.

Low level o/p voltage VOL : This is the max. voltage

available at the o/p corresponding to logic0.

PROCEDURE

1)Connect the ckt. as per ckt. dgm. for TTL IC.

2)Vary the i/p voltage in steps & notedown corresponding o/p

voltage.

3)Plot graph of Vi Vs Vo.

4)Repeat same procedure for CMOS IC.

21

DIGITAL LOGIC DESIGN AND APPLICATIONS

OBSERVATIONS

CONCLUSION

Vi

Vo

Thus transfer characteristics of TTL & CMOS ICs is studied.

22

You might also like

- 4 Bit Ripple Carry Adder VHDL CodeDocument5 pages4 Bit Ripple Carry Adder VHDL CodeSwifty SpotNo ratings yet

- 8255Document34 pages8255Manjula Bn100% (1)

- Part III 8051 General PgmsDocument7 pagesPart III 8051 General PgmsHEMANo ratings yet

- Introduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationFrom EverandIntroduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationNo ratings yet

- LD ManualDocument89 pagesLD ManualchaitanyaNo ratings yet

- EXP 6 Serial AdderDocument2 pagesEXP 6 Serial Adderubuntu 13.0450% (2)

- The D Flip FlopDocument7 pagesThe D Flip FlopAlinChanNo ratings yet

- Linear Circuit Analysis Lab ManualsDocument97 pagesLinear Circuit Analysis Lab ManualsAbdul Saboor KhanNo ratings yet

- Types of Micro OperationsDocument17 pagesTypes of Micro OperationsP Suresh Babu91% (11)

- 8086 Trainer Kit User and Technical Reference Manual PDFDocument71 pages8086 Trainer Kit User and Technical Reference Manual PDFJohn Johnston0% (1)

- Lab Manual ElectronicsDocument57 pagesLab Manual ElectronicsNaveen Rockzz Bhavans100% (2)

- Asynchronous and Synchronous CounterDocument10 pagesAsynchronous and Synchronous CounterNurul Fatihah ArdanNo ratings yet

- Lmele308 PDFDocument29 pagesLmele308 PDFAbhinit GauravNo ratings yet

- Digital System Module 4 PDFDocument52 pagesDigital System Module 4 PDFGeethanjali.pNo ratings yet

- VHDL Codes For Various Combinational CircuitsDocument6 pagesVHDL Codes For Various Combinational CircuitsKaranNo ratings yet

- Digital Logic Design Lab Manual: Department of Electrical Engineering, Fast-Nu, LahoreDocument115 pagesDigital Logic Design Lab Manual: Department of Electrical Engineering, Fast-Nu, LahoreQasim LodhiNo ratings yet

- RP Jain Adc DacDocument27 pagesRP Jain Adc DacAnand SinghNo ratings yet

- MP 8086 Lab Manual TRAINER KITDocument70 pagesMP 8086 Lab Manual TRAINER KITKavitha Subramaniam100% (1)

- Digital Electronics Lab ManualDocument93 pagesDigital Electronics Lab ManualAnoop MathewNo ratings yet

- LCDF3 Chap 03 P1Document54 pagesLCDF3 Chap 03 P1boymatterNo ratings yet

- Micro Controller Assignment 2 (All 24 From Shiva Prasad)Document88 pagesMicro Controller Assignment 2 (All 24 From Shiva Prasad)Shashank M ChanmalNo ratings yet

- Zxevo User Manual Revc EngDocument19 pagesZxevo User Manual Revc EngConrad RussoNo ratings yet

- Digital Electronics Circuits: Experiment: 9Document4 pagesDigital Electronics Circuits: Experiment: 9movabNo ratings yet

- Instruction Set of 8085 Microprocessor By, Er. Swapnil V. KawareDocument107 pagesInstruction Set of 8085 Microprocessor By, Er. Swapnil V. Kawareswapnil100% (1)

- 8086 ManualDocument45 pages8086 ManualGarima SinghalNo ratings yet

- Digital Logic Design Lab ManualDocument55 pagesDigital Logic Design Lab ManualEngr Zaryab WarraichNo ratings yet

- Lab 5 Binary ArithmeticDocument5 pagesLab 5 Binary ArithmeticRifah Shanjida Momo100% (1)

- 1-Introduction To Semiconductor MaterialsDocument43 pages1-Introduction To Semiconductor MaterialsStevie AdrielNo ratings yet

- Microprocessor All Experiment IT PDFDocument22 pagesMicroprocessor All Experiment IT PDFSuraj KumarNo ratings yet

- 8086 Microprocessor For ScientistDocument21 pages8086 Microprocessor For ScientistRam Kishore RoyNo ratings yet

- Mda 8086Document3 pagesMda 8086Shuvro Chowdhury0% (1)

- Sequential Logic CircuitsDocument10 pagesSequential Logic CircuitsNaveen Madusha100% (1)

- Memory and Programmable LogicDocument47 pagesMemory and Programmable Logicdewantosatrio50% (2)

- Digital Open EndedDocument13 pagesDigital Open EndedudayNo ratings yet

- Chapter 3 - Serial Interfacing With Microprocessor Based SystemDocument28 pagesChapter 3 - Serial Interfacing With Microprocessor Based SystemAarav PoudelNo ratings yet

- Cjmcu 2232HLDocument1 pageCjmcu 2232HLr5fzqmrprvNo ratings yet

- AIC Lab ManualDocument36 pagesAIC Lab ManualSangamesh V AngadiNo ratings yet

- Avionics - Decoders & EncodersDocument5 pagesAvionics - Decoders & EncoderskrishnamurthyVishNo ratings yet

- 7 Segment N LCDDocument38 pages7 Segment N LCDBaishakhi Bose100% (1)

- PIC Microcontrollers: Chapter 7: Addressing Modes, Bank Switching, Table ProcessingDocument42 pagesPIC Microcontrollers: Chapter 7: Addressing Modes, Bank Switching, Table ProcessingBernard Maacaron100% (1)

- Chapter 4 Programmable Peripheral InterfaceDocument49 pagesChapter 4 Programmable Peripheral InterfacetesfayebbNo ratings yet

- Digital CounterDocument18 pagesDigital CounterbotakezuNo ratings yet

- MSDFFDocument20 pagesMSDFFShweta KumariNo ratings yet

- Parity Generator Checker PDFDocument3 pagesParity Generator Checker PDFSujesh P Lal67% (3)

- Study of Flip-Flops Submitted To: Submitted byDocument10 pagesStudy of Flip-Flops Submitted To: Submitted byIrene SultanaNo ratings yet

- Veilog HDL Module 3Document62 pagesVeilog HDL Module 3Mallik KglNo ratings yet

- Sequential CircuitsDocument22 pagesSequential CircuitsBaeNo ratings yet

- 32-Bit Microprocessor - Student Manual PDFDocument502 pages32-Bit Microprocessor - Student Manual PDFSilver Magday JrNo ratings yet

- 5- CH 5 Arithmetic and Logic Instructions - ١٢٢٠١٩Document44 pages5- CH 5 Arithmetic and Logic Instructions - ١٢٢٠١٩Boy azNo ratings yet

- Unit 5 - NotesDocument9 pagesUnit 5 - Notesbidhukes100% (1)

- Random Number Generator Using 8051Document3 pagesRandom Number Generator Using 8051Umar Nawaz50% (2)

- Interfacing Analog To Digital Data ConvertersDocument16 pagesInterfacing Analog To Digital Data ConvertersPrabin123No ratings yet

- Alu 32 BitDocument6 pagesAlu 32 Bitsachin_bhingareNo ratings yet

- VHDL Very High Speed Integrated Language: Unit VDocument41 pagesVHDL Very High Speed Integrated Language: Unit VB. MeenakshiNo ratings yet

- DLD Lab Manual 7 FlipFlopsDocument6 pagesDLD Lab Manual 7 FlipFlopsHanzala NasirNo ratings yet

- Lab Report Electronics 5thDocument18 pagesLab Report Electronics 5thMuhammad kawish iqbal100% (1)

- Experiment - 1 Addition of Two 8 Bit NumbersDocument20 pagesExperiment - 1 Addition of Two 8 Bit NumbersMadhur AswaniNo ratings yet

- ADEC LabDocument16 pagesADEC LabPraveen TPNo ratings yet

- De Lab PDFDocument36 pagesDe Lab PDFNaveen Yallapu100% (1)

- De ManualDocument56 pagesDe ManualBhuvanesh Kakarla AP21110010593No ratings yet

- Digital Logic CircuitsDocument20 pagesDigital Logic Circuitssreekanthreddy peramNo ratings yet

- K.Ramakrishnan College of Engineering: Samayapurm, Trichy-621 112Document2 pagesK.Ramakrishnan College of Engineering: Samayapurm, Trichy-621 112ManimegalaiNo ratings yet

- 4/42018 1 Dr. K Riyazuddin, Asso - Prof, AITS RajampetDocument44 pages4/42018 1 Dr. K Riyazuddin, Asso - Prof, AITS RajampetAnonymous otC0SjNo ratings yet

- Aligarh Muslim UniversityDocument35 pagesAligarh Muslim UniversityvtechvishnuNo ratings yet

- 1985 C03 Philips LoudspeakersDocument444 pages1985 C03 Philips LoudspeakersMontxo100% (1)

- Description of TTL, ECL and CMOS Glue Logic FamiliesDocument2 pagesDescription of TTL, ECL and CMOS Glue Logic Familiesapi-26100966No ratings yet

- 74LS00 Datasheet, Circuit, PDF, & Application Note Results: Price & Availability byDocument14 pages74LS00 Datasheet, Circuit, PDF, & Application Note Results: Price & Availability byKebba A K SanyangNo ratings yet

- Dem 22421Document15 pagesDem 22421Payal VeerNo ratings yet

- Syllabus DCRUSTDocument38 pagesSyllabus DCRUSTSachin MalikNo ratings yet

- Co Lab ManualDocument81 pagesCo Lab ManualShiva KumarNo ratings yet

- SRM Valliammai Engineering College: Department of Electronics and Communication EngineeringDocument11 pagesSRM Valliammai Engineering College: Department of Electronics and Communication EngineeringRamaNo ratings yet

- Eie - Ee6301 DLC - Unit 1 NotesDocument82 pagesEie - Ee6301 DLC - Unit 1 Notesmoney_kandan2004No ratings yet

- Digitals Electronics Important MCQ With SolutionDocument20 pagesDigitals Electronics Important MCQ With SolutionPradeep Singh ThakurNo ratings yet

- Experiment 1 Basic Logic Gates: ObjectivesDocument10 pagesExperiment 1 Basic Logic Gates: Objectivesasdf lkjNo ratings yet

- Department of Electronics & Communication Engineering: Mini ProjectDocument12 pagesDepartment of Electronics & Communication Engineering: Mini ProjectNagarajNo ratings yet

- Logic FamiliesDocument29 pagesLogic FamiliesSid SinhaNo ratings yet

- Dynamic Combinational Circuits: - Dynamic Circuits - Domino Logic - np-CMOS (Zipper CMOS)Document15 pagesDynamic Combinational Circuits: - Dynamic Circuits - Domino Logic - np-CMOS (Zipper CMOS)himanshu chandrakarNo ratings yet

- Digital Electronics: B.Sc. Electronics Syllabus Under CBCSDocument4 pagesDigital Electronics: B.Sc. Electronics Syllabus Under CBCSJawed ZafriNo ratings yet

- Electronics Syllabus Plus Other InformationDocument10 pagesElectronics Syllabus Plus Other InformationCutry CarryNo ratings yet

- 2005-2006 B.SC Syllabus (RU) CSEDocument21 pages2005-2006 B.SC Syllabus (RU) CSEHel GalibNo ratings yet

- MCQ EdugripDocument109 pagesMCQ EdugripArasanfiveStevenNo ratings yet

- The Mizoram Engineering Service Regulations 2013Document22 pagesThe Mizoram Engineering Service Regulations 2013Lalbiakkima RokhumNo ratings yet

- Fuzzy RelationsDocument23 pagesFuzzy RelationsdinkarbhombeNo ratings yet

- Syllabus DU NewDocument48 pagesSyllabus DU NewANKIT CHAKRABORTYNo ratings yet

- Bhagwant University Electrical and Electronics Engg. B.Tech Course Semester IiiDocument41 pagesBhagwant University Electrical and Electronics Engg. B.Tech Course Semester IiiMegala DhasarathanNo ratings yet

- 74HC194N PDFDocument7 pages74HC194N PDFOsman KoçakNo ratings yet

- B.tech Cse SyllabusDocument121 pagesB.tech Cse Syllabusapi-3782519100% (20)

- Digital Electronics RK Kanodia & Ashish Murolia PDFDocument487 pagesDigital Electronics RK Kanodia & Ashish Murolia PDFshashank gupta75% (8)

- Digital Electronics Sample Chapter PDFDocument106 pagesDigital Electronics Sample Chapter PDFRokiniKumarasamyNo ratings yet

- DSD Module 1 - Notes 1Document95 pagesDSD Module 1 - Notes 1Abinesh RNo ratings yet