Professional Documents

Culture Documents

Lecture12 PDF

Lecture12 PDF

Uploaded by

Subhash Chandra SahuOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Lecture12 PDF

Lecture12 PDF

Uploaded by

Subhash Chandra SahuCopyright:

Available Formats

12

CMOS Layout

Mask Layers

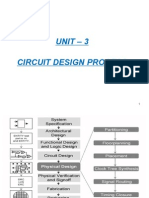

IC design procedure:

Layer

system specifications

Representation

Color Convention (EECS 105)

circuit design

layout

n-well

purple

active

green

select (p+)

brown

polysilicon

red

metal

blue

contact

black

post-layout extraction and simulation

IC fabrication

testing

Layout considerations:

mask layers

devices

electrical connectivity (interconnect)

layout (design) rules

EE 105 Fall 1998

Lecture 12

EE 105 Fall 1998

Lecture 12

MOSFET Layout

Electrical Connectivity

active, polysilicon, and metal can be used for interconnects (wires)

metal has much lower resistivity than either active or polysilicon

metal is separated from active or polysilicon by an (insulating) oxide; a contact

is needed for electrical connections between these layers

active and polysilicon cannot be connected directly (without metal)

use p-doped active (select mask) as contact to the bulk

polysilicon crossing active results in an NMOS device:

L

gate

W

source / drain (symmetric)

PMOS devices are placed in n-wells:

use n-doped active (no select mask) as a contact to n-wells

select

n-well

contact to bulk

EE 105 Fall 1998

Lecture 12

contact to well

EE 105 Fall 1998

Lecture 12

Layout Example

Layout Rules (EECS 105 Technology)

minimum dimensions and separations (in mm, not to scale):

n-well

polysilicon

4

VDD

VDD

active

metal

2

2

contact

2

10 12

select

14 16

18 20 m

metal

contact-topoly

2

VSS

VSS

active

polysilicon

polysilicon

active

10 12

14 16

18 20 m

n-well

EE 105 Fall 1998

Lecture 12

EE 105 Fall 1998

Lecture 12

Circuit Extraction

Circuit Extraction

1) Find all transistors and sizes

1) Find all transistors and sizes

2) Extract wiring

2) Extract wiring

3) Calculate (parasitic) capacitance and resistance

3) Calculate (parasitic) capacitance and resistance

VSS

VSS

VSS

10 12 14 16 18 20 m

VSS

VDD

10 12 14 16 18 20 m

VDD

EE 105 Fall 1998

Lecture 12

VDD

10 12 14 16 18 20 m

VDD

10 12 14 16 18 20 m

EE 105 Fall 1998

Lecture 12

Extracted Schematic

Circuit Simulation

fabricating an IC costs $1000 ... $100,000 per run

VDD

CA-DD

(4.5/1)

Objectives:

---> nice to get it right the first time

CB-DD

check results from hand-analysis

(4.5/1)

(e.g. validity of assumptions)

F

evaluate functionality, speed, accuracy, ... of large circuit blocks or entire chips

Cw

(3/1)

CB-SS

Simulators:

SPICE: invented at UC Berkeley circa 1970-1975

commercial versions: HSPICE, PSPICE, I-SPICE, ... (same core as Berkeley

SPICE, but add functionality, improved user interface, ...)

(3/1)

A

CA-SS

EECS 105: student version of PSPICE on PC, limited to 10 transistors

VSS

other simulators for higher speed, special needs (e.g. SPLICE, RSIM)

Wire capacitance Cw is found from its capacitance per unit length - ox

C w = -----------W w L w

t

thox

Interconnect capacitances CA-SS and CA-DD are the sum of polysilicon and metal

capacitances to the substrate (connected to VSS ) or the well (connected to VDD)

Could add resistances of polysilicon and metal interconnects

EE 105 Fall 1998

Lecture 12

Limitations:

simulation results provide no insight (e.g. how to increase speed of circuit)

results sometimes wrong (errors in input, effect not modeled in SPICE)

===> always do hand-analysis first and COMPARE RESULTS

EE 105 Fall 1998

Lecture 12

You might also like

- EP 95-0230 HSE Manual PDFDocument134 pagesEP 95-0230 HSE Manual PDFFrzan Ali100% (1)

- MathCad in Structural Design - STEEL PDFDocument16 pagesMathCad in Structural Design - STEEL PDFMilutin Zizic100% (4)

- MOS Integrated Circuit DesignFrom EverandMOS Integrated Circuit DesignE. WolfendaleNo ratings yet

- Design Rules: Bridges Between Technology Capability and Design ConsiderationsDocument7 pagesDesign Rules: Bridges Between Technology Capability and Design ConsiderationsutpalwxyzNo ratings yet

- Application of Rogowski CoilsDocument6 pagesApplication of Rogowski CoilscatalinccNo ratings yet

- Diode, Transistor & Fet Circuits Manual: Newnes Circuits Manual SeriesFrom EverandDiode, Transistor & Fet Circuits Manual: Newnes Circuits Manual SeriesRating: 4.5 out of 5 stars4.5/5 (7)

- CHP 2 - Mos Design and LayoutDocument104 pagesCHP 2 - Mos Design and Layoutkkece41No ratings yet

- Ch. 7 Lecture Slides For Chenming Hu Book: Modern Semiconductor Devices For ICsDocument43 pagesCh. 7 Lecture Slides For Chenming Hu Book: Modern Semiconductor Devices For ICsChenming Hu100% (1)

- Irwin 5 Chapter - 10thDocument257 pagesIrwin 5 Chapter - 10thMarcelo Eduardo Benencase100% (1)

- EI2403 - VLSI Design 2 Marks With AnswersDocument23 pagesEI2403 - VLSI Design 2 Marks With AnswersAnand GvphNo ratings yet

- Overseas Road Note 15 - Design and Operation of Road Management SystemsDocument82 pagesOverseas Road Note 15 - Design and Operation of Road Management SystemsIulia Golubova100% (1)

- Implementation of Components and Circuits: OutlineDocument26 pagesImplementation of Components and Circuits: OutlineTarundeep SinghNo ratings yet

- CMOS VLSI Design - A Circuits and Systems UNKNOWN - 2021Document170 pagesCMOS VLSI Design - A Circuits and Systems UNKNOWN - 2021Ngô Trọng NguyênNo ratings yet

- Analog Layout Design: Kanazawa University Microelectronics Research Lab. Akio KitagawaDocument48 pagesAnalog Layout Design: Kanazawa University Microelectronics Research Lab. Akio Kitagawaaminkhan83No ratings yet

- PCIRF 3 1 LayoutDocument61 pagesPCIRF 3 1 LayoutMarius FerdyNo ratings yet

- Analog ICDocument38 pagesAnalog ICRAJAMOHANNo ratings yet

- Lecture05 Ee474 Layout PDFDocument74 pagesLecture05 Ee474 Layout PDFKesani Venkat Narsimha ReddyNo ratings yet

- Layout ExamplesDocument13 pagesLayout Examplesnazibhd786No ratings yet

- Circuit Characterization and Performance Estimation: Instructor Dr. İsmail Enis UnganDocument36 pagesCircuit Characterization and Performance Estimation: Instructor Dr. İsmail Enis UnganyousufnetNo ratings yet

- Peter H ChenDocument10 pagesPeter H ChenYunping HuangNo ratings yet

- 01 EE6306 - MOS Transistor TheoryDocument74 pages01 EE6306 - MOS Transistor TheoryononahjNo ratings yet

- Ece-V-fundamentals of Cmos Vlsi (10ec56) - SolutionDocument41 pagesEce-V-fundamentals of Cmos Vlsi (10ec56) - SolutionSanthosh Chandu C100% (2)

- Key Words: Rogowski Coil, Relay Protection, Electric Arc Furnace TransformerDocument16 pagesKey Words: Rogowski Coil, Relay Protection, Electric Arc Furnace TransformerKartik SamantaNo ratings yet

- Chap4 Lect13 WireDocument18 pagesChap4 Lect13 Wirejubincb2No ratings yet

- Microelectronic CircuitDocument696 pagesMicroelectronic CircuitImtiaz AhmedNo ratings yet

- NMOS ProcessingDocument41 pagesNMOS ProcessingwizardvenkatNo ratings yet

- Vlsi Design: Time: 3 Hours Total Marks: 100Document4 pagesVlsi Design: Time: 3 Hours Total Marks: 100Shivani VarshneyNo ratings yet

- 2016 Ch1-Intro PDFDocument16 pages2016 Ch1-Intro PDFTrần Anh TânNo ratings yet

- Layout Design: 18-322 Fall 2003Document40 pagesLayout Design: 18-322 Fall 2003Sai SadiqNo ratings yet

- EE447 Lecture6Document36 pagesEE447 Lecture6lipun12ka4100% (1)

- VLSI CAT2 SolvedDocument13 pagesVLSI CAT2 SolvedTrinayan PathakNo ratings yet

- KIK614441 IC Part1Document49 pagesKIK614441 IC Part1Hafid FajriNo ratings yet

- Cad Asic Extra QuestionDocument18 pagesCad Asic Extra QuestionDin_skyDNo ratings yet

- Assignment 2 E5163 Sesi Jun 2011 Answer PDFDocument6 pagesAssignment 2 E5163 Sesi Jun 2011 Answer PDFsenyadnoireNo ratings yet

- Power ElectronicsDocument37 pagesPower ElectronicsMohammad Tabrez AlamNo ratings yet

- Design MarginsDocument17 pagesDesign MarginsRapolu SushmaNo ratings yet

- Microelectronics Devices: Yao-Joe YangDocument17 pagesMicroelectronics Devices: Yao-Joe YangŞemsettin karakuşNo ratings yet

- Chp1-2 Print BookDocument40 pagesChp1-2 Print Bookbalaji_gawalwad9857No ratings yet

- Experiment No. 1: Aim: Study of Tanner Tools THEORY: Tanner ToolsDocument24 pagesExperiment No. 1: Aim: Study of Tanner Tools THEORY: Tanner ToolsVarun GargNo ratings yet

- Class Presentation On CH 6 Interconnect: ECE 525 Digital Integrated Circuit Design-1 Presenter Zahed Reza KhurasaniDocument27 pagesClass Presentation On CH 6 Interconnect: ECE 525 Digital Integrated Circuit Design-1 Presenter Zahed Reza KhurasaniGuru VelmathiNo ratings yet

- (NAAC Accredited "A++" Grade University) : Koneru Lakshmaiah Education FoundationDocument13 pages(NAAC Accredited "A++" Grade University) : Koneru Lakshmaiah Education FoundationLakshmi JagupillaNo ratings yet

- Unit - 3 Circuit Design ProcessDocument30 pagesUnit - 3 Circuit Design ProcessNagarjun RajputNo ratings yet

- Lecture06 Wire Lect14 WiresDocument35 pagesLecture06 Wire Lect14 WiresKhánh TrầnNo ratings yet

- Electronic Devices Lab - Exp - 9 - Student - Manual (Summer 18-19)Document3 pagesElectronic Devices Lab - Exp - 9 - Student - Manual (Summer 18-19)MD MONIM ISLAMNo ratings yet

- Vlsi Design 17EC63: Chetan S, Dept of ECE, SJMIT, ChtradurgaDocument226 pagesVlsi Design 17EC63: Chetan S, Dept of ECE, SJMIT, ChtradurgaShivaprasad B KNo ratings yet

- Inverter LayoutDocument22 pagesInverter LayoutPriyal PatelNo ratings yet

- Engineered Substrates: Options at The 45nm Node IncludeDocument4 pagesEngineered Substrates: Options at The 45nm Node IncludeAnkit PawarNo ratings yet

- CMOS Devices BookDocument37 pagesCMOS Devices Bookteddy leeNo ratings yet

- FINDER Catalogue 2014-15Document564 pagesFINDER Catalogue 2014-15Yiannis MinoglouNo ratings yet

- PassivesDocument18 pagesPassivesbabadfeNo ratings yet

- Stick DiagramDocument72 pagesStick DiagramBhanu Bond0% (1)

- Introduction To CMOS VLSI Design: Credits: David HarrisDocument62 pagesIntroduction To CMOS VLSI Design: Credits: David HarrisYashNo ratings yet

- Vlsi Design 1 Mark QuestionsDocument7 pagesVlsi Design 1 Mark QuestionsVallabh JNo ratings yet

- JavaDocument88 pagesJavaAnu SNo ratings yet

- Design of CMOS Analog Integrated Circuits: Franco MalobertiDocument25 pagesDesign of CMOS Analog Integrated Circuits: Franco MalobertiKesani Venkat Narsimha ReddyNo ratings yet

- Monolithic IC-Component FabricationDocument6 pagesMonolithic IC-Component FabricationThamaraikannan Loganathan100% (2)

- Features: 36 Series - Miniature PCB Relays 10 ADocument4 pagesFeatures: 36 Series - Miniature PCB Relays 10 AAsim PedicNo ratings yet

- Unit 3Document70 pagesUnit 3Mahendra BabuNo ratings yet

- VLSIDocument140 pagesVLSINiranjan ReddyNo ratings yet

- Presentasi Sempro Part 47 by Ms. ChanDocument17 pagesPresentasi Sempro Part 47 by Ms. Chanwidyasagita27No ratings yet

- Designing & Developing Social Advocacy in An ICT ProjectDocument21 pagesDesigning & Developing Social Advocacy in An ICT ProjectMharc Nyvhie GuillermoNo ratings yet

- Tally Prime Course GST Bill EntryDocument8 pagesTally Prime Course GST Bill EntryElakiyaaNo ratings yet

- Issue 4 106 111 PDFDocument6 pagesIssue 4 106 111 PDFpuppyarav2726No ratings yet

- Shigley 9E SI Chap01Document16 pagesShigley 9E SI Chap01Ana100% (1)

- RIA Post Grad Book FINALDocument7 pagesRIA Post Grad Book FINALMarvin Lee Hsien-HoongNo ratings yet

- VLSI Physical Design - STA Interview Question Part 3Document2 pagesVLSI Physical Design - STA Interview Question Part 3srinathNo ratings yet

- Modeling of Structural Systems: Technical Knowledge Base CSIDocument2 pagesModeling of Structural Systems: Technical Knowledge Base CSIJesus Jaimes ManceraNo ratings yet

- Design, Modeling and Analysis of Conveyor System Used For Transportation of CartonsDocument10 pagesDesign, Modeling and Analysis of Conveyor System Used For Transportation of CartonsAditya BadveNo ratings yet

- Chapter 15 Structural Design Requirements For Design-Build ContractsDocument106 pagesChapter 15 Structural Design Requirements For Design-Build Contractsmark limNo ratings yet

- The Concept of Surface EngineeringDocument7 pagesThe Concept of Surface EngineeringPRASAD326100% (1)

- ForewordDocument170 pagesForewordTomyNo ratings yet

- Sadp Unit-1Document43 pagesSadp Unit-1vasavisai kNo ratings yet

- Introduction To Biomedical Engineering DesignDocument17 pagesIntroduction To Biomedical Engineering DesignEmad TalebNo ratings yet

- Spray & Pray R4G3 v11 - Iniuria ConfigDocument27 pagesSpray & Pray R4G3 v11 - Iniuria ConfigvsdvsdvafrasdfNo ratings yet

- Language From CompetitorsDocument19 pagesLanguage From CompetitorsScott NiedfeldtNo ratings yet

- ESE 570 Cadence Lab Assignment 2: Introduction To Spectre, Manual Layout Drawing and Post Layout Simulation (PLS)Document7 pagesESE 570 Cadence Lab Assignment 2: Introduction To Spectre, Manual Layout Drawing and Post Layout Simulation (PLS)Parul TrivediNo ratings yet

- The Future of 3D Printing Technology in The Construction Industry: A Systematic Literature ReviewDocument16 pagesThe Future of 3D Printing Technology in The Construction Industry: A Systematic Literature ReviewSamuel Coquilla Solis Jr.No ratings yet

- Rvce Ipre NotesDocument39 pagesRvce Ipre Notesnoah52No ratings yet

- The Role of Technology in Sustainable Architecture PDFDocument9 pagesThe Role of Technology in Sustainable Architecture PDFThilluNo ratings yet

- Design Logic ProgramableDocument126 pagesDesign Logic ProgramableMinh PhạmNo ratings yet

- Modern Product Catalog BookletDocument12 pagesModern Product Catalog BookletGame TwistersNo ratings yet

- WB Ultra-Poor Graduation HandbookDocument140 pagesWB Ultra-Poor Graduation Handbookathancox5837No ratings yet

- SH Radha BhandariDocument4 pagesSH Radha BhandariToni JeloNo ratings yet

- Lecture2 PDFDocument60 pagesLecture2 PDFindranilhNo ratings yet

- 프리즌라이프 한글화 핵Document16 pages프리즌라이프 한글화 핵클로버No ratings yet