Professional Documents

Culture Documents

מבוא למחשבים תרגול 7

Uploaded by

Shahar MizrahiCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

מבוא למחשבים תרגול 7

Uploaded by

Shahar MizrahiCopyright:

Available Formats

" " 163-3-1213

"

:

13.31.3. :

2-Bus SRC Processor Design :7

:

.3 SRC 2-BUS

RTN ..

.1

Abstract RTN .4

: .

:

.

. ,

( ) ( ) clock period

/ .

SRC concrete RTN

. , Trade-off (

) , .clock

2-bus

"

" " 163-3-1213

:2-bus

1-bus Gra, Grb, Grc .

Register file :A

( Sra,Srb,Src 5-32).

:C ALU A Bus

, : A .file register

( C B ?)

T ( 2T .)1-bus

:1.3

A ?B Bus RTN

.

MA A Bus fetch 1.

. . 1 Bus.

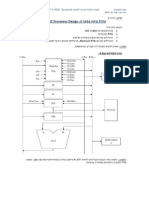

2-Bus

Step Concrete RTN Control Sequence

Grb, Rout, C=B, Ain

Grc, Rout, ADD, Sra, Rin,

End.

]AR[rb

T3

]R[ra]A+R[rc

T4

1-Bus

Concrete

Control

Step

RTN

Sequence

]AR[rb

Grb, Rout, Ain

CA+R[rc] Grc, Rout, ADD, Cin

R[ra]C

Cout, Gra, Rin, End.

T3

T4

T5

: concrete RTN ADD :

2-bus ( ,fetch )

1-bus 1.

..

: concrete RTN ld T4

2-bus T4+T5

.1-bus

2-Bus

Control

Sequence

Grb, BAout, C=B, Ain

C2out, ADD, MAin

Read, Wait

MDout, C=B, Sra,

Rin, End.

1-Bus

Concrete RTN

Step

Control

Sequence

Concrete RTN

Step

)(rb=0)(A0

)](rb0)(AR[rb

MAA+C2{Sign

}Ext

]MDM[MA

)(rb=0)(A0

)](rb0)(AR[rb

T3

T4

CA+C2{Sign Ext} C2out, ADD, Cin

T4

T5

Cout, MAin

MAC

T5

R[ra]MD

T6

Read, Wait

]MDM[MA

T6

MDout, Gra, Rin,

End.

R[ra]MD

T7

T3

Grb, BAout, Ain

163-3-1213 " "

"

:

2.7

Abstract RTN : R ra R rb R rc

: Mult ra , rb , rc

0 R rc 31

:

:2-bus SRC

Step

T0

MA PC

PCout,C=B,Main

Concrete RTN

T1

PC PC 4; MD M MA

PCout,INC4,PCin,Read,Wait

T2

IR MD

MDout,C=B,IRin

T3

n R rc

Grc,Rout,ld

T4

A R rb

Grb,Rout, C=B ,Ain

T5

R ra 0

BAout,C=B,Sra,Rin

: n 0 R ra R ra A

mult

: n n 1; mult

Gra, Rout , ADD, Sra,

n 0

Rin , Decr , Goto6

n 0 End

T6

:1-bus SRC

Step

T0 T2

Concrete RTN

fetch

T3

n R rc

Grc,Rout,ld

T4

A R rb

Grb,Rout, C=B ,Ain

T5

C 0

BAout,C=B,Cin

T6

: n 0 C C A

mult

: n n 1; mult

R ra C

Gra, Rout , ADD, Cin ,

n 0

Decr , Goto6

T7

Cout , Gra, Rin , End

, clock ) 1-bus SRC (:

.)T6- : ? (clock- ?

:

Execution Time=Clock Count

" " 163-3-1213

"

:

:Clock Count -Clock / RTN.

: (.)clock period

. 1.21bus 2bus

:IC ,6+(R[rc]+3( :2-bus 1+(R[rc]+3( :1-bus

:

T1bus T2bus

(7 ( R[rc ] 1)) (6 ( R[rc ] 1))1.2

100

100

T2bus

(6 ( R[rc ] 1))1.2

2.7

Speedup

( , " , ' )

2-bus SRC- poly :

.poly ra,rb,rc , f ( x) a0 x b0 x c0 ,. .x

2

ALU .Neg

rc x ..- . 15 x 15

rb : .

:

c0

5 bit

b0

5 bit

a0

5 bit

, f ( x) , ra ..

ra .100...00b

17 bit

...

:

o

consta ,constb, constc BUS-b<4..0>- 5

,)constc( 34..31 ,(constb) 9..5 ,)consta) 4..1 ,

LSB .

: Grb, Rout, constb > 0@28#R[rb]<9..5.Bus-b

Goto6 Gotoy y.

data path- ,2-bus SRC- -

.fetch

) ( .') . Gotoy ?

: 5( opcode=7) , ra,rb,rc 5 , 1- lsb ,cond( 311

).

.

163-3-1213 " "

"

:

.goto12

.2-Bus SRC- RTN ') .5( )

)? a0,b0,c0,x ( .fetch-

?(a0,b0,c0,x(=(31,31,31,-15)

. ' 31 ( ) a0,b0,c0,x(=(31,31,31,-15) (11

step

RTN

0-2

3 n R[rb] 4..0 ;

fetch

Ld,Grb,consta,Ro a

ut

n a0

4

5

6

A R[rc];

R[ra] 0;

multa(: (n 0)

R[ra] R[ra] A : n n 1; multa

n 0 A 0@ 28 # R[rb] 9..5 );

R[ra] R[ra] A;

CON cond ( R[rc]);

CON R[rc] Neg ( R[rc]);

10

n R[rc];

11

(n 0) n n 1, A R[ra];

(n 0) R[ra] 0;

12multb(: (n 0)

R[ra] R[ra] A : n n 1; multb

(n 0) A 0@ 28# R[rb] 14..10 );

13

CON R[ra] Neg ( R[ra]);

14

R[ra] R[ra] A;

Grc,Rout,B=C,Ain

A<-x

BAout,Sra,Rin,B=

C

n!=0->

Gra,Rout,ADD,Sra b0

,Rin,dec,Goto6

n=0->

Grb,constb,Rout

a0 x

A

Gra,Rout,ADD,Sra

,Rin

a0 x b0

CONin,Grc,Rout

!CON-> x

Grc,Rout,NEG,Src,

Rin

Grc,Rout,ld

n x

n!=0-> dec,

Gra,Rout,B=C,Ain.

n=0->

BAout,B=C,Sra,Ri

n.

A a0 x b0

n!=0->

Gra,Rout,ADD,Sra

3.,Rin,dec,Goto

n=0->

Grb,constc,Rout

x (a0 x b0 )

A c0

!CON->

Gra,Rout,NEG,Sra

,Rin

.

Gra,Rout,ADD,Sra

,Rin,END

" " 163-3-1213

"

:

1

4

5

6

n a0

a0 x

1

a0 x b0

( A )b0 Ra A

..

,x x 5 13,...,4,5

Rc ( ).

, n Rc

31

33

x , A a0 x b0

] [0,15 13,...,4,5 Rc .

Rc >.Rc<4..0

) abs(x .n ) abs(x 5 . x

-36 neg +36 5 ( .).

x!=0 : Ra x-1

n-1.

x=0 .Ra

3.

) x (a0 x b0

31

34

c0A

sign( x) x (a0 x b0 ) c0

.c0

a0 x b0 x c0 a0 x b0 x c0 a0 x b0 x c0 3115 3115 31 747110

2

1D716

1413

:

6 : , a0+1 ,

5 , abs(x)+1 , . ."

x a0 :

15 .

) (a0,b0,c0,x(=(31,31,31,-15.63=35+35+13 :

Abstract RTN

RTN : SRC

. :

() ()

" " 163-3-1213

"

:

.

: .

2.7

RTN- SRC- little -

? endian

, RTN SRC:

Main Memory State

Mem[0..232 - 1]<7..0>:

232 addressable bytes of memory

M[x]<31..0> := Mem[x]#Mem[x+1]#Mem[x+2]#Mem[x+3]:

M :

]M[x]<31..0>:=Mem[x+3]#Mem[x+2]#Mem[x+1]#Mem[x

2.7

RTN- SRC

36 ( 1. ).

Mem[0..232-1]<15..0>:

M[x]<31..0>:=Mem[x]#Mem[x+1]:

2.7

RTN- SRC- instruction_interpretaion

:

( =instruction_interpretation :

Run ^ Start Run 1 :

Run ( instruction_execution ; IR M[PC] : PC PC + 4 ) ) :

,

,Start=1 SRC?

, :

( =(instruction-interpretation :

Run Strt -> Run <- 1; instruction-interpretation):

"

" " 163-3-1213

Run (IR <-- M[PC]: PC PC + 4; instruction-execution):

nop .

2.2

SRC- auto-decrement :

) -(Ra , 4 Ra

]] M[R[Ra . , ) ld r1, -(r0:

R[0] R[0]-4

]]R[1] M[R[0

,r0

. .ld, st, la

.

.3 RTN- .SRC-

disp<31..0>:=((rb=0) (R[rb]R[rb]-4 ; R[rb]) :

(rb!=0) R[rb]+c2<16..0>{sign extend, 2's comp.}):

.. RTN 1-BUS SRC - ld .

,Data-path- .Fetch- 9

( )fetch- 5 .

rb=0 3 5 rb

1 . ALU- DEC4 ALU-

4 B .ALU- .Fetch-

Grb, Rout, Ain, DEC4, Cin

A R[rb] : C R[rb]-4

T3

(rb=0)Grb, Rin, Cout

(rb=0) R[rb] C :

T4

(rb!=0)c2out, ADD, Cin

}(rb!=0) C A+c2<16..0> {sign ext.

MAin, Cout, READ

MA C

T5

Wait

]MD M[MA

T6

MDout, Gra, Rin, End

R[ra] MD

T7

.1 SRC- (

) : .51

,.- 1.- , .1

. .3111

"

" " 163-3-1213

. 36 5 .

stop .

:5 ( )program loader

(.)executable code

( : ).

( #define

Cost: .equ 200

)C

.org 1000

(

- X .)311110

() ( Y )3=Y

X: .dw 1

X

EQUate

.equ

ORiGin

.org

Define

Word

.dw

.org 1000

r0, -4

lar

r1, 0

lar

)r2, -(r0

ld

r2, r2

neg

r3, r0, 0

addi

)r2, 0(r3

st

r1, r0

brnz

stop

You might also like

- מבוא למחשבים תרגול 5Document13 pagesמבוא למחשבים תרגול 5Shahar MizrahiNo ratings yet

- מבוא למחשבים תרגול 6Document16 pagesמבוא למחשבים תרגול 6Shahar MizrahiNo ratings yet

- מבוא למחשבים תרגול 8Document11 pagesמבוא למחשבים תרגול 8Shahar MizrahiNo ratings yet

- תכן חומרה- סיכום הרצאות - שי יידרמן 2013Document23 pagesתכן חומרה- סיכום הרצאות - שי יידרמן 2013RonNo ratings yet

- מבוא למחשבים תרגול 9 חלק אDocument2 pagesמבוא למחשבים תרגול 9 חלק אShahar MizrahiNo ratings yet

- הרצאה 03 - מבוא לחומרהDocument10 pagesהרצאה 03 - מבוא לחומרהMoran KupferNo ratings yet

- דף נוסחאות גליםDocument2 pagesדף נוסחאות גליםGilad ShreibshteinNo ratings yet

- מעגלים אנלוגיים טכניון סיכוםDocument19 pagesמעגלים אנלוגיים טכניון סיכוםbarrayal100% (1)

- נוסחאות אנלוגיםDocument3 pagesנוסחאות אנלוגיםshahar_mizNo ratings yet

- מדריך ארדואינו למתחילים חלק א' - האקסטור - אלקטרוניכאן - ארדואינו PDFDocument41 pagesמדריך ארדואינו למתחילים חלק א' - האקסטור - אלקטרוניכאן - ארדואינו PDFnags0% (1)

- מצגת מבואDocument72 pagesמצגת מבואgvgvgcNo ratings yet

- פריויריטי מדריך מקוצר למשתמשDocument12 pagesפריויריטי מדריך מקוצר למשתמשDawit David ZeruNo ratings yet

- חוברת תקשוב א פרק 1-2Document50 pagesחוברת תקשוב א פרק 1-2hilik tNo ratings yet

- תכן לוגי מועד א 2022 מתוקןDocument7 pagesתכן לוגי מועד א 2022 מתוקןLior BarNo ratings yet

- עבודת בית 2- אלי רועי ומיכאלDocument4 pagesעבודת בית 2- אלי רועי ומיכאלelad0% (1)

- Class 5 - 1-Bus SRCDocument7 pagesClass 5 - 1-Bus SRCAmit ShiloNo ratings yet

- מעבדה למיקרו מחשבים- מועד א ופתרון - 2009Document4 pagesמעבדה למיקרו מחשבים- מועד א ופתרון - 2009RonNo ratings yet

- Loops - לולאותDocument44 pagesLoops - לולאותMichaelNo ratings yet

- Matlab BookDocument87 pagesMatlab Bookvada1980No ratings yet

- דפי עזר מבחן ספרתיות טכניוןDocument10 pagesדפי עזר מבחן ספרתיות טכניוןiluvhuggiesNo ratings yet

- מערכות ספרתיות - דפי עזר לבחינהDocument10 pagesמערכות ספרתיות - דפי עזר לבחינהMaya Shahar100% (1)

- Spice Task 2Document6 pagesSpice Task 2Hassan AliNo ratings yet

- נומרית- מבחן לדוגמאDocument2 pagesנומרית- מבחן לדוגמאRonNo ratings yet

- פתרונות תרגיל חובה מספר 1 בארכיטקטורה 2022בDocument5 pagesפתרונות תרגיל חובה מספר 1 בארכיטקטורה 2022בKoral LeviNo ratings yet

- מבוא להנדסת חשמל- מועד א ופתרון - 2011Document11 pagesמבוא להנדסת חשמל- מועד א ופתרון - 2011RonNo ratings yet

- Digital Logic Systems 5Document33 pagesDigital Logic Systems 5Noam ShemlaNo ratings yet

- Sol CPP 182 ADocument6 pagesSol CPP 182 AShiri NeisserNo ratings yet

- מבוא לתק"מ- תרגיל כיתה 6 - Slotted Aloha & CSMADocument45 pagesמבוא לתק"מ- תרגיל כיתה 6 - Slotted Aloha & CSMARonNo ratings yet

- Tutorial 2 Nicols GraphDocument10 pagesTutorial 2 Nicols GraphhahahaNo ratings yet

- Relational AlgebraDocument35 pagesRelational AlgebraOmerNo ratings yet

- 0512.3543.2021b2 FormDocument4 pages0512.3543.2021b2 FormSapir HarelNo ratings yet

- ריכוז-תרגילי- PEMICDocument36 pagesריכוז-תרגילי- PEMICxyoavxNo ratings yet

- תרגילים באלקטרוניקה ספרתיתDocument33 pagesתרגילים באלקטרוניקה ספרתיתMichael Weisbrit100% (2)

- מערכות הפעלה 2022 מועד אDocument8 pagesמערכות הפעלה 2022 מועד אEliav MenachiNo ratings yet

- מערכות הפעלה 2022 מועד ג פתרוןDocument10 pagesמערכות הפעלה 2022 מועד ג פתרוןEliav MenachiNo ratings yet

- DSP- הצעת דף נוסחאותDocument7 pagesDSP- הצעת דף נוסחאותRonNo ratings yet

- HW2Document13 pagesHW2avraham_elkaNo ratings yet

- אותות ומערכות- תרגיל בית 2Document3 pagesאותות ומערכות- תרגיל בית 2RonNo ratings yet

- מערכות הפעלה 2022 מועד ב. פתרוןDocument10 pagesמערכות הפעלה 2022 מועד ב. פתרוןEliav MenachiNo ratings yet

- תרגיל חובה מספר 1 בארכיטקטורה 2022בDocument2 pagesתרגיל חובה מספר 1 בארכיטקטורה 2022בKoral LeviNo ratings yet

- אלקטרוניקה לפיזיקאים מעבדה 3Document1 pageאלקטרוניקה לפיזיקאים מעבדה 3danielseriogin007No ratings yet

- Arch Course Sum TKDocument32 pagesArch Course Sum TKfosto2No ratings yet

- פתרון לדוגמא תרגיל 7Document8 pagesפתרון לדוגמא תרגיל 7hkabesaNo ratings yet

- מבחנים לינאריותDocument42 pagesמבחנים לינאריותShiri NeisserNo ratings yet

- מערכות הפעלה 2022 מועד בDocument7 pagesמערכות הפעלה 2022 מועד בEliav MenachiNo ratings yet

- חוברת ניסוי DSPDocument12 pagesחוברת ניסוי DSPItay GelNo ratings yet

- קובץ מצורף - הנחיות מרצה להגשת עבודות 16726Document8 pagesקובץ מצורף - הנחיות מרצה להגשת עבודות 16726יגאל אקרמןNo ratings yet

- סיכום אלגוריתמים בגרפיםDocument11 pagesסיכום אלגוריתמים בגרפיםElior BenaimNo ratings yet

- Class 3 - SRCDocument6 pagesClass 3 - SRCAmit ShiloNo ratings yet

- Class 6 - Concrete RTNDocument7 pagesClass 6 - Concrete RTNAmit ShiloNo ratings yet

- ׳"׳ - ׳- ׳׳¢׳‘׳"׳" ׳׳¡׳₪׳¨ 3Document16 pages׳"׳ - ׳- ׳׳¢׳‘׳"׳" ׳׳¡׳₪׳¨ 3Shlomi AbukaratNo ratings yet

- הרצאה 2Document55 pagesהרצאה 2Omer LeviNo ratings yet

- ממן 14Document6 pagesממן 14rivkaNo ratings yet

- Malah DSP Grad - 048745 - W 2005 - Book HebDocument242 pagesMalah DSP Grad - 048745 - W 2005 - Book HebDor Ben LavyNo ratings yet

- מעגלים ספרתיים- תרגיל בית 3 - 2012Document6 pagesמעגלים ספרתיים- תרגיל בית 3 - 2012RonNo ratings yet

- מעגלים ספרתיים- תרגיל בית 4 - 2012Document4 pagesמעגלים ספרתיים- תרגיל בית 4 - 2012RonNo ratings yet

- פתרונות תרגיל חובה מספר 4 מעבד חד מחזורי בארכיטקטורה 2022בDocument6 pagesפתרונות תרגיל חובה מספר 4 מעבד חד מחזורי בארכיטקטורה 2022בKoral LeviNo ratings yet

- 0512.3543.2022a1 FormDocument4 pages0512.3543.2022a1 FormSapir HarelNo ratings yet

- פוטנציאל חשמלי 2 תרגיל 3Document2 pagesפוטנציאל חשמלי 2 תרגיל 3Ron ElbaumNo ratings yet

- תרגיל 11Document40 pagesתרגיל 11Amir YassoNo ratings yet

- סיכום קורס אותות אקראיים ורעשDocument20 pagesסיכום קורס אותות אקראיים ורעשShahar MizrahiNo ratings yet

- מבוא לעיבוד אותות דף נוסחאות PDFDocument4 pagesמבוא לעיבוד אותות דף נוסחאות PDFShahar MizrahiNo ratings yet

- בקרה אופטימליתDocument82 pagesבקרה אופטימליתShahar MizrahiNo ratings yet

- Job Interview WWW - Underwar.co - IlDocument55 pagesJob Interview WWW - Underwar.co - IlKOMBINANo ratings yet