Professional Documents

Culture Documents

Ee141 HW8

Ee141 HW8

Uploaded by

Vidhya DsOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Ee141 HW8

Ee141 HW8

Uploaded by

Vidhya DsCopyright:

Available Formats

UNIVERSITY OF CALIFORNIA, BERKELEY

College of Engineering

Department of Electrical Engineering and Computer Sciences

Elad Alon Homework #8 EECS141

Due Tuesday, Nov. 24th @ 240 Cory

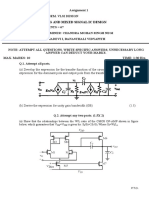

PROBLEM 1: DOMINO LOGIC AND CHARGE SHARING

a) Implement the logic shown below as a single complex, dynamic gate (with four

inputs) followed by an inverter.

A

B

C

X

D

b) What pattern of the inputs P1, G0, and G1 results in the worst-case drop in voltage

on node G1:0_b due to charge sharing for the gate shown below? Assuming VDD =

1.2V, CG = 2fF/m, and CD = 1.5fF/m, what is this worst-case voltage?

PROBLEM 2: DOMINO SIZING AND DELAY

Consider the domino circuit shown on the next page. Assume long-channel transistors,

CL = 300fF, Cin = 5fF, CG = 2fF/m, CD = 1.5fF/m, and that input signal C is the last

one to arrive.

a) Find the logical effort of each stage in the critical path for the evaluation edge

(rising edge of Out).

b) Find WN1 and WN2 to give minimal delay.

c) Estimate the delay of the critical path in F04. Include the worst-case parasitic

delay terms. Recall that 1FO4 is equal to (4+)tinv.

d) From the standpoint of minimum delay, is this the optimum number of stages? If

not, how many stages would you use to minimize the delay?

VDD VDD

CLK 2/3*WN1 4WN2

Out

CL

A WN1 C WN1 WN2

B WN1 D WN1

CLK WN1

You might also like

- English Paper 1 Mark Scheme: Stage 9Document10 pagesEnglish Paper 1 Mark Scheme: Stage 9Hiede Rodil64% (14)

- Forecasting Urban Water DemandDocument367 pagesForecasting Urban Water DemandTri WahyuningsihNo ratings yet

- EE 577A Spring 2022 - VLSI System Design Homework 1: TH TH THDocument4 pagesEE 577A Spring 2022 - VLSI System Design Homework 1: TH TH THvedeshNo ratings yet

- Identify The Structure Implemented in The Following Layout Diagram and Draw Its Equivalent CMOS ImplementationDocument2 pagesIdentify The Structure Implemented in The Following Layout Diagram and Draw Its Equivalent CMOS Implementationrishika chhibberNo ratings yet

- Exercise EEE418Document5 pagesExercise EEE418Mohammad Zakir AlamNo ratings yet

- Analog Circuit Design Volume Three: Design Note CollectionFrom EverandAnalog Circuit Design Volume Three: Design Note CollectionRating: 3 out of 5 stars3/5 (2)

- Assignment No. 6Document3 pagesAssignment No. 6aditya nagrajanNo ratings yet

- EC3058D-VLSI Circuits and Systems Winter Semester-2020-21Document2 pagesEC3058D-VLSI Circuits and Systems Winter Semester-2020-21Gamer AnonymousNo ratings yet

- Analysis and Design of Digital Integrated CircuitsDocument14 pagesAnalysis and Design of Digital Integrated CircuitsfjwoemcuNo ratings yet

- EE 330 Exam 2 Spring 2015 PDFDocument10 pagesEE 330 Exam 2 Spring 2015 PDFeng2011techNo ratings yet

- Questions On Small Signal Model of AmpDocument2 pagesQuestions On Small Signal Model of AmpdevsrivastavaNo ratings yet

- Sheet 3 - SolutionDocument10 pagesSheet 3 - SolutionMajid HelmyNo ratings yet

- Analog Guide RajaReddyDocument30 pagesAnalog Guide RajaReddyKirti Susan VargheseNo ratings yet

- Assignment IDocument2 pagesAssignment Ivaishnavi priyaNo ratings yet

- Analog and Digital Electronics PDFDocument34 pagesAnalog and Digital Electronics PDFJatinNo ratings yet

- Cat1Document3 pagesCat1Manoharan KandasamyNo ratings yet

- iNVERTER aSSIGN6 1Document6 pagesiNVERTER aSSIGN6 1Rohan ChopraNo ratings yet

- Exercise 2Document3 pagesExercise 2momolololilo4No ratings yet

- Analog CircuitsDocument33 pagesAnalog Circuitsafireon80% (1)

- Chapter7 Ex PDFDocument5 pagesChapter7 Ex PDFSathish Kumar100% (1)

- Electronics Design MOSFETDocument14 pagesElectronics Design MOSFETbhanuNo ratings yet

- Sheet 5 PDFDocument3 pagesSheet 5 PDFMajid HelmyNo ratings yet

- Analog ElectronicsDocument77 pagesAnalog ElectronicsramyaranganayakiNo ratings yet

- Rabaey Dig ElectronicsDocument4 pagesRabaey Dig ElectronicsRahul AgarwalNo ratings yet

- Solution ECE-438, MOS Transistor: W V I K V V V V L Min (V - VDocument10 pagesSolution ECE-438, MOS Transistor: W V I K V V V V L Min (V - Vneeno2013No ratings yet

- Analog Integrated Circuits Exercise 4: Common-Source and Differential AmplifiersDocument9 pagesAnalog Integrated Circuits Exercise 4: Common-Source and Differential Amplifiersubuntu 13.04No ratings yet

- General Instructions To The CandidateDocument4 pagesGeneral Instructions To The Candidateapurv shuklaNo ratings yet

- Chapter03 ExDocument10 pagesChapter03 ExKarthikeya VemparalaNo ratings yet

- Lab10 2011Document5 pagesLab10 2011Venkat RamananNo ratings yet

- R09-Cmos Analog and Mixed Signal DesignDocument2 pagesR09-Cmos Analog and Mixed Signal DesignbalashyamuNo ratings yet

- Solution Gates 2 SamplesDocument9 pagesSolution Gates 2 SamplesluqmansulymanNo ratings yet

- Tutorial 5 MosDocument3 pagesTutorial 5 MosomerNo ratings yet

- Subject: Analog and Mixed Signal Ic DesignDocument2 pagesSubject: Analog and Mixed Signal Ic DesignchandravinitaNo ratings yet

- Jntu Hyd 2 2ece PDC Set 2Document18 pagesJntu Hyd 2 2ece PDC Set 2Krishna RamaNo ratings yet

- An-9014-Fairchild QFET For Synchronous Rectification DC To DC Converters - ImpDocument16 pagesAn-9014-Fairchild QFET For Synchronous Rectification DC To DC Converters - ImpbmmostefaNo ratings yet

- Application of Z-Source Converter in Photovoltaic Grid-Connected Transformer-Less InverterDocument5 pagesApplication of Z-Source Converter in Photovoltaic Grid-Connected Transformer-Less InverterPaolo ProspNo ratings yet

- Ee270 HW2Document7 pagesEe270 HW2saiedali2005No ratings yet

- Question BankDocument4 pagesQuestion BankKetan SalviNo ratings yet

- Chapter02 - Logic Design With MOSFETsDocument51 pagesChapter02 - Logic Design With MOSFETsbal3xNo ratings yet

- Analog - RF VLSI Design (ECE 503) (Makeup) PDFDocument2 pagesAnalog - RF VLSI Design (ECE 503) (Makeup) PDFRahul PinnamaneniNo ratings yet

- Q. 1 - Q. 25 Carry One Mark Each.: X A X AADocument14 pagesQ. 1 - Q. 25 Carry One Mark Each.: X A X AAGauravArjariaNo ratings yet

- HW 1Document5 pagesHW 1BrimwoodboyNo ratings yet

- 7.sheet OutputstagesDocument6 pages7.sheet OutputstagesAyman ElAshmawyNo ratings yet

- Sura Group of Institutions, Lucknow: Q-2.2 Determine The Following For The Given NetworkDocument2 pagesSura Group of Institutions, Lucknow: Q-2.2 Determine The Following For The Given NetworkSaurabh SinghNo ratings yet

- I. Instructional Objectives: D S G D GDocument4 pagesI. Instructional Objectives: D S G D Gcokelat_kNo ratings yet

- Design of CMOS OpAmp For A D/A Converter Buffer by Manraj Singh GujralDocument22 pagesDesign of CMOS OpAmp For A D/A Converter Buffer by Manraj Singh GujralManraj GujralNo ratings yet

- ECE 410 Homework 7 - Solution Spring 2008Document4 pagesECE 410 Homework 7 - Solution Spring 2008ET onlineNo ratings yet

- Singh 2018Document5 pagesSingh 2018Tshering Sangmoo SherpaNo ratings yet

- Answers FinalDocument20 pagesAnswers FinalMario HanyNo ratings yet

- EE 5311 Digital IC Design Tutorial 3 - Sep 25, 2015: N Ox 2 P Ox 2 Min Min T T Dsat Dsat DDDocument2 pagesEE 5311 Digital IC Design Tutorial 3 - Sep 25, 2015: N Ox 2 P Ox 2 Min Min T T Dsat Dsat DDHarshithNo ratings yet

- Sheet 1Document4 pagesSheet 1MohamedAlyNo ratings yet

- Ec3058D-Vlsi Circuits and Systems Winter Semester-2020-21: DD Ton TopDocument2 pagesEc3058D-Vlsi Circuits and Systems Winter Semester-2020-21: DD Ton TopGamer AnonymousNo ratings yet

- HW1 2023fallDocument4 pagesHW1 2023fallapplebao1022No ratings yet

- Fundamentals of Electronics 1: Electronic Components and Elementary FunctionsFrom EverandFundamentals of Electronics 1: Electronic Components and Elementary FunctionsNo ratings yet

- VSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsFrom EverandVSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsNo ratings yet

- Power System Transient Analysis: Theory and Practice using Simulation Programs (ATP-EMTP)From EverandPower System Transient Analysis: Theory and Practice using Simulation Programs (ATP-EMTP)No ratings yet

- Electrical and Electronic Principles 3 Checkbook: The Checkbook SeriesFrom EverandElectrical and Electronic Principles 3 Checkbook: The Checkbook SeriesNo ratings yet

- Exercises in Electronics: Operational Amplifier CircuitsFrom EverandExercises in Electronics: Operational Amplifier CircuitsRating: 3 out of 5 stars3/5 (1)

- Audio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsFrom EverandAudio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsNo ratings yet

- Power Systems-On-Chip: Practical Aspects of DesignFrom EverandPower Systems-On-Chip: Practical Aspects of DesignBruno AllardNo ratings yet

- Summary Box For The Natwest Credit Card: Our Pricing PolicyDocument2 pagesSummary Box For The Natwest Credit Card: Our Pricing PolicylftmadNo ratings yet

- DX DiagDocument33 pagesDX DiagJhon Edisson DueñasNo ratings yet

- Fitness Is The Condition of Being Physically Fit and HealthyDocument2 pagesFitness Is The Condition of Being Physically Fit and HealthyCyhra Diane MabaoNo ratings yet

- English Paper 1 UPSRDocument20 pagesEnglish Paper 1 UPSRCynthia Theseira100% (2)

- New City Catering PackageDocument1 pageNew City Catering PackageThirdy Quibranza SimanganNo ratings yet

- Degree DayDocument17 pagesDegree DayWaqar HassanNo ratings yet

- Robin Kuckyr Selling Your Accounting Practice NewsletterDocument16 pagesRobin Kuckyr Selling Your Accounting Practice NewsletterWard WichtNo ratings yet

- Qsen Competencies 2Document4 pagesQsen Competencies 2api-2691700450% (1)

- Spoon Catalog66web 1Document44 pagesSpoon Catalog66web 1Tariq Zuhluf100% (1)

- CG ProgrammingDocument429 pagesCG ProgrammingAdi Nouashcinci100% (1)

- RFC 3193 - Securing L2TP Using IPsecDocument28 pagesRFC 3193 - Securing L2TP Using IPsecAlphariusNo ratings yet

- Ground Floor Plan: General NotesDocument1 pageGround Floor Plan: General NotesChaturbhuj Ikat FabricsNo ratings yet

- SESAMEDocument5 pagesSESAMEGanpat Lal SharmaNo ratings yet

- Snapshot - Pre-Intermediate - Ex 1 / Page 57Document4 pagesSnapshot - Pre-Intermediate - Ex 1 / Page 57Asiu Mihaela RodicaNo ratings yet

- Cameroon - A New Investment Destination in AfricaDocument102 pagesCameroon - A New Investment Destination in Africafuh patrickNo ratings yet

- Catalogo Geral Precisao InglesDocument144 pagesCatalogo Geral Precisao InglesBruno TudeiaNo ratings yet

- Himesh Koul: ExperienceDocument1 pageHimesh Koul: ExperienceTuhin ChakrabortyNo ratings yet

- Saksham Samiksha Updated Logins MasterDocument39 pagesSaksham Samiksha Updated Logins MasterSarvan KhokkharNo ratings yet

- Videocon Industries LTDDocument19 pagesVideocon Industries LTDRitika SharmaNo ratings yet

- PPA StructuringDocument34 pagesPPA StructuringRaj Tha100% (1)

- MakinenDocument89 pagesMakinenGMR TEIMNo ratings yet

- TL-WR841HP - V5 - Datasheet PDFDocument6 pagesTL-WR841HP - V5 - Datasheet PDFJhair Michele Andree Díaz AranaNo ratings yet

- Multiplexing With Arduino and The 74HC595Document17 pagesMultiplexing With Arduino and The 74HC595luberiesNo ratings yet

- Acs JPCC 8b06841Document13 pagesAcs JPCC 8b06841Septian Perwira YudhaNo ratings yet

- Complete ProjectDocument74 pagesComplete Projectyung JayceNo ratings yet

- Ice ScrambbleDocument15 pagesIce ScrambbleJay ArNo ratings yet

- 3bet Pot HeuristicsDocument21 pages3bet Pot HeuristicsJeremiah Bailey-HooverNo ratings yet

- What Was The Nature of The War of 1914-18? The First World War Was A New Type of War, It Took Place FromDocument3 pagesWhat Was The Nature of The War of 1914-18? The First World War Was A New Type of War, It Took Place FromStephen CarterNo ratings yet