Professional Documents

Culture Documents

Digital Ic Applications: B.Tech II Year II Semester (R07) Supplementary Examinations, April/May 2013

Digital Ic Applications: B.Tech II Year II Semester (R07) Supplementary Examinations, April/May 2013

Uploaded by

Mahaboob SubahanOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Digital Ic Applications: B.Tech II Year II Semester (R07) Supplementary Examinations, April/May 2013

Digital Ic Applications: B.Tech II Year II Semester (R07) Supplementary Examinations, April/May 2013

Uploaded by

Mahaboob SubahanCopyright:

Available Formats

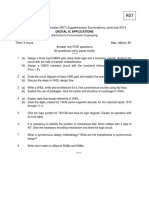

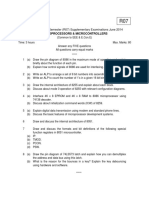

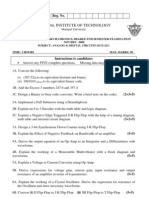

Code: R7221004 R07

B.Tech II Year II Semester (R07) Supplementary Examinations, April/May 2013

DIGITAL IC APPLICATIONS

(Electronics & Instrumentation Engineering)

Time: 3 hours Max. Marks: 80

Answer any FIVE questions

All questions carry equal marks

*****

1. (a) Design CMOS transistor circuit for 3-input AND gate with the help of function table, the

operation of the circuit diagram. Explain.

(b) Discuss dynamic electrical behavior of CMOS logic.

2. (a) Design a 3-input NAND gate using diode logic and a transistor inverter. Analyze the circuit with

the help of transfer characteristics.

(b) Write a VHDL entity and architecture for the following function

Also draw the relevant logic diagram.

3. (a) Explain low voltage CMOS logic and interfacing.

(b) Explain about functions and procedures with examples in VHDL.

4. (a) Explain data flow design elements of VHDL.

(b) Design a logic circuit to detect prime number of a 4 bit input. Write VHDL program for the

same in structural style of modeling.

5. (a) Explain the operation of 4 to 2 priority encoder and write VHDL program for it.

(b) Realize the following expression using 74 X 151 IC

6. (a) Design a 4 X 4 combinational multiplier and write a VHDL program in data flow model.

(b) With the help of logic diagram explain 74 X 157 multiplexer.

7. (a) Distinguish between latch and flip-flop. Show the logic diagram for both. Explain the operation

with the help of function table.

(b) Draw the logic diagram of 74 X 163 binary counters and explain its operation.

8. (a) Discuss in detail ROM access mechanism with the help of timing waveforms.

(b) Explain the internal structure of 64 K X 1 DRAM. With the help of timing waveforms discuss

DRAM access.

*****

You might also like

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (2)

- 12D20102 Advanced Structural AnalysisDocument2 pages12D20102 Advanced Structural AnalysissubbuNo ratings yet

- 12d20106a Prestressed ConcreteDocument1 page12d20106a Prestressed ConcretesubbuNo ratings yet

- R7310404 Digital IC Applications2Document1 pageR7310404 Digital IC Applications2subbuNo ratings yet

- 9A04504 Digital IC Applications6Document4 pages9A04504 Digital IC Applications6subbuNo ratings yet

- Rr310403-Digital Ic ApplicationsDocument1 pageRr310403-Digital Ic ApplicationssivabharathamurthyNo ratings yet

- R7221004 Digital IC Applications7Document1 pageR7221004 Digital IC Applications7subbuNo ratings yet

- R7310404 Digital IC ApplicationsDocument1 pageR7310404 Digital IC ApplicationssubbuNo ratings yet

- Code: 07A4041 B.Tech III Year I Semester (R07) Supplementary Examinations June 2015Document1 pageCode: 07A4041 B.Tech III Year I Semester (R07) Supplementary Examinations June 2015subbuNo ratings yet

- SS07A4041 Digital IC ApplicationsDocument1 pageSS07A4041 Digital IC ApplicationsMahaboob SubahanNo ratings yet

- Digital Nov 07Document6 pagesDigital Nov 07skssushNo ratings yet

- R7310404 Digital IC ApplicationsDocument1 pageR7310404 Digital IC ApplicationssivabharathamurthyNo ratings yet

- Rr210504-Linear and Digital Ic ApplicationsDocument1 pageRr210504-Linear and Digital Ic ApplicationssivabharathamurthyNo ratings yet

- R7320202 Microprocessors & Microcontrollers12Document1 pageR7320202 Microprocessors & Microcontrollers12subbuNo ratings yet

- NR-221103 - Digital Circuits Design and ApplictionDocument5 pagesNR-221103 - Digital Circuits Design and ApplictionSrinivasa Rao G100% (1)

- R7310404 Digital IC ApplicationsDocument1 pageR7310404 Digital IC ApplicationssivabharathamurthyNo ratings yet

- 9A04504 Digital IC ApplicationsDocument1 page9A04504 Digital IC ApplicationssubbuNo ratings yet

- SS 9A04602 Microprocessors & Microcontrollers6Document1 pageSS 9A04602 Microprocessors & Microcontrollers6subbuNo ratings yet

- Code: R7221004 B.Tech II Year II Semester (R07) Supplementary Examinations May/June 2015Document1 pageCode: R7221004 B.Tech II Year II Semester (R07) Supplementary Examinations May/June 2015subbuNo ratings yet

- R7320202-Microprocessors and MicrocontrollersDocument1 pageR7320202-Microprocessors and MicrocontrollerseltpgroupNo ratings yet

- Campusexpress - Co.in: Set No. 1Document8 pagesCampusexpress - Co.in: Set No. 1skssushNo ratings yet

- 9A04602 Microprocessors & Microcontrollers5Document1 page9A04602 Microprocessors & Microcontrollers5subbuNo ratings yet

- 9A04504 Digital IC Applications4Document1 page9A04504 Digital IC Applications4subbuNo ratings yet

- 9A04504 Digital IC ApplicationsDocument4 pages9A04504 Digital IC ApplicationssivabharathamurthyNo ratings yet

- R7310404 Digital IC ApplicationsDocument1 pageR7310404 Digital IC ApplicationssivabharathamurthyNo ratings yet

- 1 Semester Model Question PapersDocument17 pages1 Semester Model Question PapersBalaji MohantyNo ratings yet

- R7310201-Computer System OrganizationDocument4 pagesR7310201-Computer System OrganizationsivabharathamurthyNo ratings yet

- R7220203 Linear Digital IC ApplicationsDocument2 pagesR7220203 Linear Digital IC ApplicationssivabharathamurthyNo ratings yet

- ETC Raisoni Endsem PaperDocument14 pagesETC Raisoni Endsem PaperYogesh Jounjalkar100% (1)

- NR Computer OrganizationDocument1 pageNR Computer Organizationsarathy1231No ratings yet

- Microcontoller and Applications-Sample-Question-Paper (Msbte-Study-Resources)Document5 pagesMicrocontoller and Applications-Sample-Question-Paper (Msbte-Study-Resources)surajmore2368No ratings yet

- Switching Theory and Logic Design April 2019 PDFDocument4 pagesSwitching Theory and Logic Design April 2019 PDFTulasi LassiNo ratings yet

- 9A04306 Digital Logic Design2Document1 page9A04306 Digital Logic Design2Mahaboob SubahanNo ratings yet

- Embedded Systems 9168 - Sample Paper of MSBTE For Sixth Semester Final Year Computer Engineering Diploma (80 Marks)Document2 pagesEmbedded Systems 9168 - Sample Paper of MSBTE For Sixth Semester Final Year Computer Engineering Diploma (80 Marks)Sanjay DudaniNo ratings yet

- 9A12301 Digital Logic Design and Computer OrganizationDocument4 pages9A12301 Digital Logic Design and Computer OrganizationsivabharathamurthyNo ratings yet

- RT 21053112016Document4 pagesRT 21053112016RaunaqNo ratings yet

- MPMC by GodseDocument5 pagesMPMC by GodseJAYA CHANDRA AKULANo ratings yet

- NR 311402 Digital ElectronicsDocument8 pagesNR 311402 Digital ElectronicsSrinivasa Rao G100% (2)

- r05220202 Linear and Digital Ic ApplicationDocument4 pagesr05220202 Linear and Digital Ic ApplicationSRINIVASA RAO GANTANo ratings yet

- Advanced Digital Signal ProcessingDocument6 pagesAdvanced Digital Signal ProcessingnzaeqwdhqswjhvNo ratings yet

- Code: 1 3A04504 Set 1 R13 Ravindra College of Engineering For Women: KurnoolDocument1 pageCode: 1 3A04504 Set 1 R13 Ravindra College of Engineering For Women: KurnoolShafiullaShaikNo ratings yet

- Cs6201-Digital Principles and System DesignDocument6 pagesCs6201-Digital Principles and System DesignAnonymous L4iu94ZIlwNo ratings yet

- Dec 2009Document8 pagesDec 2009Viswa ChaitanyaNo ratings yet

- Linear and Digital Ic ApplicatonsDocument4 pagesLinear and Digital Ic ApplicatonsViswa ChaitanyaNo ratings yet

- Scheme - I Sample Question Paper: I. Instruction Set Ii. Applications Iii. Memory Organization. I/O CompatibilityDocument5 pagesScheme - I Sample Question Paper: I. Instruction Set Ii. Applications Iii. Memory Organization. I/O CompatibilityC052 Diksha PawarNo ratings yet

- EES 311 - Digital Electronics MuranDocument4 pagesEES 311 - Digital Electronics MuranEusie JewelNo ratings yet

- r05321404 Linear and Digital Ic ApplicationsDocument7 pagesr05321404 Linear and Digital Ic ApplicationsSRINIVASA RAO GANTANo ratings yet

- Rr320501-Advanced Computer ArchitectureDocument4 pagesRr320501-Advanced Computer ArchitectureSRINIVASA RAO GANTANo ratings yet

- Analog & Digital CircuitsDocument1 pageAnalog & Digital CircuitsAkhil GuptaNo ratings yet

- R5310404 Digital IC Applications12Document1 pageR5310404 Digital IC Applications12subbuNo ratings yet

- Set No: 1: Code No: V3224/R07Document4 pagesSet No: 1: Code No: V3224/R07jitendra28No ratings yet

- DEC Lab Experiments - 2017aDocument5 pagesDEC Lab Experiments - 2017aManjeet SinghNo ratings yet

- R7221004 Digital IC Applications1Document1 pageR7221004 Digital IC Applications1subbuNo ratings yet

- Sample-Question-Paper - Digital Electronics and Microcontroller ApplicationsDocument5 pagesSample-Question-Paper - Digital Electronics and Microcontroller ApplicationsAbhishek ManeNo ratings yet

- Zeal Polytechnic, PuneDocument53 pagesZeal Polytechnic, Punetest877929No ratings yet

- Intelligent Manufacturing SystemsDocument5 pagesIntelligent Manufacturing SystemsVenkata RamuduNo ratings yet

- CRC of BCA (2) Assignment (Revised Syllabus)Document17 pagesCRC of BCA (2) Assignment (Revised Syllabus)BshrinivasNo ratings yet

- Computer Organization Nov 2020Document1 pageComputer Organization Nov 2020Sai BabaNo ratings yet

- Jntuworld: R07 Set No. 2Document4 pagesJntuworld: R07 Set No. 2Ram KrishnaNo ratings yet

- VI Sem, Jan, Feb 2005Document4 pagesVI Sem, Jan, Feb 2005Veeresh NicolyteNo ratings yet

- COA Assignment of Unit-1 and Unit-2Document4 pagesCOA Assignment of Unit-1 and Unit-2Shruti JhaNo ratings yet

- 9A04306 Digital Logic DesignDocument4 pages9A04306 Digital Logic DesignsivabharathamurthyNo ratings yet

- BT BP AcDocument1 pageBT BP AcsubbuNo ratings yet

- 12D86103 Materials For NanotechnologyDocument1 page12D86103 Materials For NanotechnologysubbuNo ratings yet

- 12D86102 Microelectronic Technology & IC FabricationDocument1 page12D86102 Microelectronic Technology & IC FabricationsubbuNo ratings yet

- 12D86101 Advanced Computing MethodsDocument1 page12D86101 Advanced Computing MethodssubbuNo ratings yet

- 12D75104b Advanced Instrumentation SystemsDocument1 page12D75104b Advanced Instrumentation SystemssubbuNo ratings yet

- 12d20105a Experimental Stress AnalysisDocument1 page12d20105a Experimental Stress AnalysissubbuNo ratings yet

- Jntuworld: (Common To Vlsies, Esvlsi & Vlsiesd)Document1 pageJntuworld: (Common To Vlsies, Esvlsi & Vlsiesd)subbuNo ratings yet

- 12D20105c Low Cost Housing TechniquesDocument1 page12D20105c Low Cost Housing TechniquessubbuNo ratings yet

- 9d58106a Advances in DatabasesDocument1 page9d58106a Advances in DatabasessubbuNo ratings yet

- 9D61103 Computer Communication NetworksDocument1 page9D61103 Computer Communication NetworkssubbuNo ratings yet

- 9D58203 Advanced Computer NetworksDocument1 page9D58203 Advanced Computer NetworkssubbuNo ratings yet

- 9D57106c ASIC DesignDocument1 page9D57106c ASIC DesignsubbuNo ratings yet

- 9D57102 Analog IC DesignDocument1 page9D57102 Analog IC DesignsubbuNo ratings yet

- 9D57105 Hardware Software Co-DesignDocument1 page9D57105 Hardware Software Co-DesignsubbuNo ratings yet