Professional Documents

Culture Documents

R7310404 Digital IC Applications

Uploaded by

sivabharathamurthyCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

R7310404 Digital IC Applications

Uploaded by

sivabharathamurthyCopyright:

Available Formats

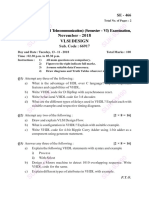

Code: R7310404

R07

(Electronics and Communication Engineering)

B.Tech III Year I Semester (R07) Supplementary Examinations December/January 2013/14 DIGITAL IC APPLICATIONS Time: 3 hours Answer any FIVE questions All questions carry equal marks *****

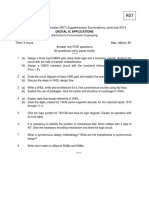

1 (a) (b) 2 (a) (b) Draw the logic diagram equivalent to the internal structure of an 8-input CMOS NAND gate. Show the transistor circuit for this gate and explain the operation with the help of function table. Draw the circuit diagram of a two-input LS-TTL NOR gate and explain the functional behavior. Design a three input NAND gate using diode logic and a transistor inverter. Analyze the circuit with the help of transfer characteristics. Explain the behavioral design model of VHDL. Design the logic circuit and write a data-flow style VHDL program for the following function: F (X) = A,B,C,D (3, 5, 6, 7, 13) + d(1, 2, 4, 12, 15) Explain data-flow design elements of VHDL. Write a data-flow style VHDL program for the following functions: F(S) = A B CI F(C0) = AB + ACI + BCI Draw the structure of a 4-bit comparator and briefly explain about it. Write a structural VHDL code for it. Discuss about a 4-bit comparator with the relevant equations. Give the logic symbol for 74X85and write a VHDL. Determine fmax for the 4 bit synchronous counter if tpd for each flip-flop is 50 ns and tpd for AND gate is 20 ns. Compare this with fmax for a MOD 16 ripple counter. Draw the basic structure of a ROM and explain the operation with a truth table. Briefly explain 2-4 decoder using an 8X4 ROM.

Max Marks: 80

3 (a) (b)

4 (a) (b)

8 (a) (b)

*****

You might also like

- 9A04504 Digital IC ApplicationsDocument4 pages9A04504 Digital IC ApplicationssivabharathamurthyNo ratings yet

- Embedded Software Design and Programming of Multiprocessor System-on-Chip: Simulink and System C Case StudiesFrom EverandEmbedded Software Design and Programming of Multiprocessor System-on-Chip: Simulink and System C Case StudiesNo ratings yet

- R7310404 Digital IC ApplicationsDocument1 pageR7310404 Digital IC ApplicationssivabharathamurthyNo ratings yet

- R7310404 Digital IC ApplicationsDocument1 pageR7310404 Digital IC ApplicationssivabharathamurthyNo ratings yet

- 9A04306 Digital Logic DesignDocument4 pages9A04306 Digital Logic DesignsivabharathamurthyNo ratings yet

- Digital System Design Using VHDL PaperDocument2 pagesDigital System Design Using VHDL PaperlambajituNo ratings yet

- 9A04504 Digital IC Applications6Document4 pages9A04504 Digital IC Applications6subbuNo ratings yet

- DLCDocument1 pageDLCrjvenkiNo ratings yet

- R7310404 Digital IC ApplicationsDocument1 pageR7310404 Digital IC ApplicationssubbuNo ratings yet

- 9A04401 Switching Theory and Logic DesignDocument4 pages9A04401 Switching Theory and Logic DesignsivabharathamurthyNo ratings yet

- Dica Question BankDocument4 pagesDica Question BankOmprakash KuswahaNo ratings yet

- 9A04306 Digital Logic DesignDocument2 pages9A04306 Digital Logic DesignsivabharathamurthyNo ratings yet

- VI Sem, Jan, Feb 2005Document4 pagesVI Sem, Jan, Feb 2005Veeresh NicolyteNo ratings yet

- Anna University Question PapersDocument2 pagesAnna University Question Papersmohan2777No ratings yet

- DLDM Question BankDocument8 pagesDLDM Question BankMayur PatilNo ratings yet

- DLD GTU Question Bank: Chapter-1 Binary SystemDocument129 pagesDLD GTU Question Bank: Chapter-1 Binary Systemnirav34No ratings yet

- DICSD Question BankDocument5 pagesDICSD Question Bankmunimunendra00No ratings yet

- Digital Ic Applications: B.Tech II Year II Semester (R07) Supplementary Examinations, April/May 2013Document1 pageDigital Ic Applications: B.Tech II Year II Semester (R07) Supplementary Examinations, April/May 2013subbuNo ratings yet

- Rr310403-Digital Ic ApplicationsDocument1 pageRr310403-Digital Ic ApplicationssivabharathamurthyNo ratings yet

- B.Tech Digital Principles and System Design Exam Question BankDocument24 pagesB.Tech Digital Principles and System Design Exam Question Bankdigital1206No ratings yet

- Embedded Systems 9168 - Sample Paper of MSBTE For Sixth Semester Final Year Computer Engineering Diploma (80 Marks)Document2 pagesEmbedded Systems 9168 - Sample Paper of MSBTE For Sixth Semester Final Year Computer Engineering Diploma (80 Marks)Sanjay DudaniNo ratings yet

- Digital Nov 07Document6 pagesDigital Nov 07skssushNo ratings yet

- DLD GTU Question Bank: Chapter-1 Binary SystemDocument5 pagesDLD GTU Question Bank: Chapter-1 Binary Systemnirav34No ratings yet

- Scheme E - Digital Techniques and Microprocessor Sample Question PaperDocument3 pagesScheme E - Digital Techniques and Microprocessor Sample Question PaperHarshal DevadeNo ratings yet

- 9A04306 Digital Logic DesignDocument4 pages9A04306 Digital Logic DesignsivabharathamurthyNo ratings yet

- Third Homework AssignmentDocument4 pagesThird Homework AssignmentTara Shankar ChakrabortyNo ratings yet

- DellDocument6 pagesDellamu_manuNo ratings yet

- Question Bank: Ec6302 Digital ElectronicsDocument14 pagesQuestion Bank: Ec6302 Digital ElectronicsBarry SmithNo ratings yet

- 9A12301 Digital Logic Design and Computer OrganizationDocument4 pages9A12301 Digital Logic Design and Computer OrganizationsivabharathamurthyNo ratings yet

- DTE Imp QuestionsDocument2 pagesDTE Imp QuestionsPushkar rane 1oth,B,ROLL NO.47No ratings yet

- Digital Techniques Sample Question PaperDocument5 pagesDigital Techniques Sample Question PaperAshutosh PatilNo ratings yet

- FAQs - CS1202 Digital Principles and System DesignDocument13 pagesFAQs - CS1202 Digital Principles and System DesignsridharanchandranNo ratings yet

- Subject Code/ Title: Ee6301 Digital Logic Circuits Year/ Sem/Branch: Ii/ Iii/ EeeDocument16 pagesSubject Code/ Title: Ee6301 Digital Logic Circuits Year/ Sem/Branch: Ii/ Iii/ EeePavithra ManiNo ratings yet

- 9A04401 Switching Theory & Logic DesignDocument4 pages9A04401 Switching Theory & Logic DesignsivabharathamurthyNo ratings yet

- r5410207 Vlsi DesignDocument1 pager5410207 Vlsi DesignsivabharathamurthyNo ratings yet

- Scheme - I Sample Question Paper: I. Instruction Set Ii. Applications Iii. Memory Organization. I/O CompatibilityDocument5 pagesScheme - I Sample Question Paper: I. Instruction Set Ii. Applications Iii. Memory Organization. I/O CompatibilityC052 Diksha PawarNo ratings yet

- R7221004 Digital IC Applications7Document1 pageR7221004 Digital IC Applications7subbuNo ratings yet

- 22323-2019-Winter-Question-Paper (Msbte Study Resources)Document3 pages22323-2019-Winter-Question-Paper (Msbte Study Resources)Parth patkarNo ratings yet

- DLCDocument4 pagesDLCramNo ratings yet

- 9a04306-Digital Logic DesignDocument1 page9a04306-Digital Logic DesignSheikh Noor MohammadNo ratings yet

- 9A04401 Switching Theory & Logic DesignDocument4 pages9A04401 Switching Theory & Logic DesignsivabharathamurthyNo ratings yet

- VLSI Design NOV 18Document2 pagesVLSI Design NOV 18Saurabh BhiseNo ratings yet

- Digital Principles and System DesignDocument24 pagesDigital Principles and System Designhelloworld1000% (3)

- R5310404 Digital IC Applications12Document1 pageR5310404 Digital IC Applications12subbuNo ratings yet

- 7th Sem Cse 2010 Scheme - Question PaperDocument8 pages7th Sem Cse 2010 Scheme - Question PaperReshma BJ67% (3)

- R5 210504 Digital Logic DesignDocument1 pageR5 210504 Digital Logic DesignsivabharathamurthyNo ratings yet

- CRC of BCA (2) Assignment (Revised Syllabus)Document17 pagesCRC of BCA (2) Assignment (Revised Syllabus)BshrinivasNo ratings yet

- DLD QuestionsDocument2 pagesDLD QuestionsUsama FaisalNo ratings yet

- R7310404 Digital IC Applications2Document1 pageR7310404 Digital IC Applications2subbuNo ratings yet

- 2019 Summer Question Paper (Msbte Study Resources)Document3 pages2019 Summer Question Paper (Msbte Study Resources)Ashutosh PatilNo ratings yet

- Sample-Question-Paper - Digital Electronics and Microcontroller ApplicationsDocument5 pagesSample-Question-Paper - Digital Electronics and Microcontroller ApplicationsAbhishek ManeNo ratings yet

- Question Bank For DLCDocument8 pagesQuestion Bank For DLCAvina AshNo ratings yet

- EC6302-Digital ElectronicsDocument14 pagesEC6302-Digital Electronicsmagy1989No ratings yet

- EC2203 U Q BankDocument12 pagesEC2203 U Q Bankvlsi_satheeshNo ratings yet

- Department of EceDocument8 pagesDepartment of Ecerajendr_46No ratings yet

- ME PAPER (SEM-1) For E.C. GTUDocument59 pagesME PAPER (SEM-1) For E.C. GTUGaurang RathodNo ratings yet

- Switching Theory and Logic DesignDocument8 pagesSwitching Theory and Logic DesignVenkat ChadalavadaNo ratings yet

- DSP Unit 1 To 5 QBDocument12 pagesDSP Unit 1 To 5 QBSamuel WhiteNo ratings yet

- 9A13701 Robotics and AutomationDocument4 pages9A13701 Robotics and AutomationsivabharathamurthyNo ratings yet

- SSC Telugu (FL) (AP)Document232 pagesSSC Telugu (FL) (AP)sivabharathamurthyNo ratings yet

- SSC Social Textbook (AP)Document100 pagesSSC Social Textbook (AP)sivabharathamurthyNo ratings yet

- Control Systems (CS) Notes As Per JntuaDocument203 pagesControl Systems (CS) Notes As Per Jntuasivabharathamurthy100% (3)

- 07A4EC01 Environmental StudiesDocument1 page07A4EC01 Environmental StudiessivabharathamurthyNo ratings yet

- 9A05707 Software Project ManagementDocument4 pages9A05707 Software Project ManagementsivabharathamurthyNo ratings yet

- R5410201 Neural Networks & Fuzzy LogicDocument1 pageR5410201 Neural Networks & Fuzzy LogicsivabharathamurthyNo ratings yet

- R7410506 Mobile ComputingDocument1 pageR7410506 Mobile ComputingsivabharathamurthyNo ratings yet

- R7410407 Operating SystemsDocument1 pageR7410407 Operating SystemssivabharathamurthyNo ratings yet

- R7310306 Heat TransferDocument1 pageR7310306 Heat Transfersivabharathamurthy100% (1)

- R7312301 Transport Phenomena in BioprocessesDocument1 pageR7312301 Transport Phenomena in BioprocessessivabharathamurthyNo ratings yet

- R7311506 Operating SystemsDocument1 pageR7311506 Operating SystemssivabharathamurthyNo ratings yet

- Code: R7311306: (Electronics & Control Engineering)Document1 pageCode: R7311306: (Electronics & Control Engineering)sivabharathamurthyNo ratings yet

- R7311205 Distributed DatabasesDocument1 pageR7311205 Distributed DatabasessivabharathamurthyNo ratings yet

- R7310506 Design & Analysis of AlgorithmsDocument1 pageR7310506 Design & Analysis of AlgorithmssivabharathamurthyNo ratings yet

- R7311006 Process Control InstrumentationDocument1 pageR7311006 Process Control InstrumentationsivabharathamurthyNo ratings yet

- R7310406 Digital CommunicationsDocument1 pageR7310406 Digital CommunicationssivabharathamurthyNo ratings yet

- 9A10505 Principles of CommunicationsDocument4 pages9A10505 Principles of CommunicationssivabharathamurthyNo ratings yet

- R7310206 Linear Systems AnalysisDocument1 pageR7310206 Linear Systems AnalysissivabharathamurthyNo ratings yet

- R5310204 Power ElectronicsDocument1 pageR5310204 Power ElectronicssivabharathamurthyNo ratings yet

- R5310406 Digital CommunicationsDocument1 pageR5310406 Digital CommunicationssivabharathamurthyNo ratings yet

- R7310106 Engineering GeologyDocument1 pageR7310106 Engineering GeologysivabharathamurthyNo ratings yet

- 9A15502 Digital System DesignDocument4 pages9A15502 Digital System Designsivabharathamurthy100% (1)

- 9A23501 Heat Transfer in BioprocessesDocument4 pages9A23501 Heat Transfer in BioprocessessivabharathamurthyNo ratings yet

- 9A14503 Principles of Machine DesignDocument8 pages9A14503 Principles of Machine DesignsivabharathamurthyNo ratings yet

- 9A05505 Operating SystemsDocument4 pages9A05505 Operating SystemssivabharathamurthyNo ratings yet

- 9A21506 Mechanisms & Mechanical DesignDocument8 pages9A21506 Mechanisms & Mechanical DesignsivabharathamurthyNo ratings yet

- 9A02505 Electrical Machines-IIIDocument4 pages9A02505 Electrical Machines-IIIsivabharathamurthyNo ratings yet

- 9A03505 Heat TransferDocument4 pages9A03505 Heat TransfersivabharathamurthyNo ratings yet